## MAX66242

# DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

### **General Description**

DeepCover<sup>®</sup> embedded security solutions cloak sensitive data under multiple layers of advanced physical security to provide the most secure key storage possible.

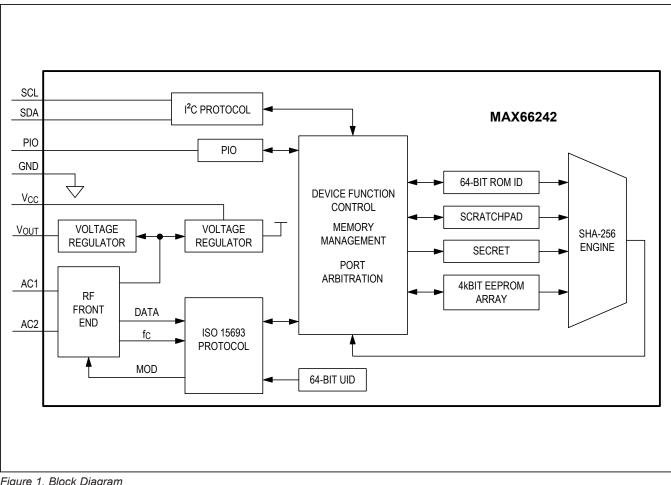

The DeepCover Secure Authenticator (MAX66242) is a transponder IC that combines an ISO/IEC 15693 and ISO 18000-3 Mode 1-compatible RF front-end, an I<sup>2</sup>C frontend, a FIPS 180-based SHA-256 engine and 4096 bits of user EEPROM in a single chip. A bidirectional security model enforces two-way authentication between a host system and the MAX66242. Each device has its own guaranteed unique 64-bit ROM ID that is factory programmed into the chip. This ROM ID is used as a fundamental input parameter for cryptographic operations and serves as an electronic serial number within the application.

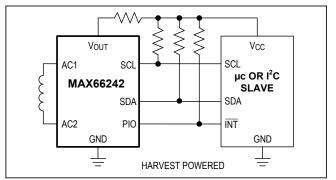

In addition to the RF interface, the MAX66242 also has an I<sup>2</sup>C interface, which can operate as a slave or master port. When acting as a master, the MAX66242 can gather information from a connected sensor or peripheral device and relay its data via the RF port. When acting as a slave, the device can serve as an intermediary between a connected host and an RF reader. The MAX66242 can harvest energy from an active RF field. The configurable supply output can deliver up to 5mA given adequate field strength.

### **Applications**

- Access Control

- Asset Tracking

- Printer Cartridge Configuration and Monitoring

- Medical Sensor Authentication and Calibration

- System Intellectual Property Protection

#### Ordering Information appears at end of data sheet.

DeepCover is a registered trademark of Maxim Integrated Products, Inc.

#### **Benefits and Features**

- Complete Counterfeit/Cloning/IP Protection Engine

- SHA-256 Engine Runs a Symmetric Key-Based Bidirectional Secure Authentication

- Strong Authentication Achieved with a High Bit Count, User-Programmable Secret, and Input Challenge

- Batteryless RF Communication

- 4096 Bits of User EEPROM with User-Programmable Memory

- Memory R/W Protection Options Including OTP/ EPROM Emulation Mode

- Unique Factory-Programmed 64-Bit Identification

Number

- Integrated 32-Byte SRAM Buffer Enables Faster HF-to-I<sup>2</sup>C Transactions

- Flexible Connection and Communication Capabilities Support a Wide Range of Applications

- Programmable I/O (PIO) Can Be Configured as a Wake-Up or Monitoring/Control Signal

- HF Standards ISO/IEC 15693 and 18000-3 MODE1 Compatible (13.56 MHz ±7kHz Carrier Frequency)

- I<sup>2</sup>C Interface—Master/Slave Port Eliminates Host Microcontroller for Sensor-Tag Applications

- Energy Harvesting V<sub>OUT</sub> Pin for Powering External Components

- Optional 3.3V Supply Voltage Fits Line and Battery-Powered Applications

- -40°C to +85°C Operating Temperature Range

- Enables Robust Design

- ±4kV HBM ESD Protection on PIO, ±2kV on All Other Pins

### **Typical Application Circuits**

Typical Application Circuits continued at end of data sheet.

### MAX66242

## DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

#### **Absolute Maximum Ratings**

| Voltage Range on Any Pin Relative to GND0.5V to +4.0V | Operating Temperature Range40°C to +85°C |

|-------------------------------------------------------|------------------------------------------|

| Maximum Current Into Any Pin Except AC1 or AC2 20mA   | Junction Temperature+150°C               |

| Maximum RMS Current, AC1 to AC2                       | Storage Temperature Range55°C to +125°C  |

| Maximum Incident Magnetic Field Strength              | Lead Temperature (soldering, 10s)+300°C  |

| (ISO/IEC 7810-compliant antenna)141.6dBµA/m           | Soldering Temperature (reflow)+260°C     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### Package Thermal Characteristics (Note 1)

| 0 | $\sim$ |  |

|---|--------|--|

| 5 | ()     |  |

|   |        |  |

TDFN

| Junction-to-Ambient Thermal Resistance (0JA)        | .60°C/W |

|-----------------------------------------------------|---------|

| Junction-to-Case Thermal Resistance $(\theta_{JC})$ | .30°C/W |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

### **Electrical Characteristics**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                                                                                   | SYMBOL              | CONDITIONS                               | MIN    | TYP    | MAX    | UNITS |

|---------------------------------------------------------------------------------------------|---------------------|------------------------------------------|--------|--------|--------|-------|

| Supply Voltage                                                                              | V <sub>CC</sub>     |                                          | 2.97   | 3.3    | 3.63   | V     |

| Active Supply Current                                                                       | I <sub>CCA</sub>    | (Note 3)                                 |        |        | 110    | μA    |

| Standby Supply Current                                                                      | I <sub>CCS</sub>    |                                          |        |        | 100    | μA    |

| Power-Up Time                                                                               | t <sub>POR</sub>    |                                          |        |        | 1      | ms    |

| SHA-256 ENGINE                                                                              |                     | · ·                                      |        |        |        |       |

| Computation Current                                                                         | ICSHA               | V <sub>CC</sub> = 3.63V (Note 4)         |        |        | 1.5    | mA    |

| Computation Time                                                                            | t <sub>CSHA</sub>   | (Note 5)                                 |        |        | 2      | ms    |

| EEPROM                                                                                      |                     |                                          |        |        |        |       |

| Programming Current                                                                         | IPROG               | V <sub>CC</sub> = 3.63V (Note 4)         |        |        | 1.5    | mA    |

| Programming Time for a 32-Bit<br>Page Block or Protection                                   | t <sub>PROG</sub>   | (Note 6)                                 |        |        | 10     | ms    |

| Write/Erase Cycling Endurance                                                               | N <sub>CY</sub>     | T <sub>A</sub> = +85°C (Notes 7, 8)      | 100k   |        |        | _     |

| Data Retention                                                                              | t <sub>DR</sub>     | T <sub>A</sub> = +85°C (Notes 9, 10, 11) | 10     |        |        | Years |

| PIO PIN                                                                                     |                     |                                          |        |        |        |       |

| Input Current with Input<br>Voltage Between 0.1V <sub>CC</sub> and<br>0.9V <sub>CCMAX</sub> | I <sub>L_PIO</sub>  |                                          |        |        | 1      | μA    |

| Input Low Voltage                                                                           | V <sub>IL_PIO</sub> |                                          | -0.3   |        | 0.4    | V     |

| Input High Voltage                                                                          | VIH PIO             |                                          | 1.62   |        |        | V     |

| Output Low Voltage                                                                          | V <sub>OL_PIO</sub> | 4mA sink current                         |        |        | 0.4    | V     |

| RF PORT                                                                                     |                     | · ·                                      | •      |        |        |       |

| Carrier Frequency                                                                           | f <sub>C</sub>      | (Note 12)                                | 13.553 | 13.560 | 13.567 | MHz   |

| Internal Tuning Cap                                                                         | C <sub>TUN</sub>    | f = 13.56 MHz (Note 13)                  |        | 27.5   |        | pF    |

## MAX66242

# DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

### **Electrical Characteristics (continued)**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                                                | SYMBOL                  | CONDITIONS                                         | MIN | TYP   | MAX  | UNITS  |

|----------------------------------------------------------|-------------------------|----------------------------------------------------|-----|-------|------|--------|

| Operating Field                                          | H <sub>ISO</sub>        | (Note 12)                                          | 150 |       | 5000 | mA/m   |

| Activation Field Strength                                | H <sub>MIN_10</sub>     | 10%–30% modulation index<br>(Note 13)              |     | 100   |      | dBµA/m |

| Activation Field Strength                                | H <sub>MIN_100</sub>    | 100% modulation index<br>(Note 13)                 |     | 101.2 |      | dBµA/m |

| Write/SHA Field Strength                                 | H <sub>WR</sub>         | (Notes 13, 14)                                     |     | 113   |      | dBµA/m |

| VOUT Field Strength                                      | H <sub>MINOUT</sub>     | (Note 13)                                          |     | 122   |      | dBµA/m |

| V <sub>OUT</sub> Transition Time                         | t <sub>VOUT</sub>       | (Notes 13, 15)                                     |     | 250   |      | μs     |

| RF Access In Progress Time                               | t <sub>RFAIP</sub>      | (Notes 16)                                         |     | 1.1   |      | ms     |

| 10% Carrier Modulation Index<br>Min MI = (A - B)/(A + B) | CMI_10 <sub>MIN</sub>   | (Notes 12, 13, 17)                                 |     | 10    |      | %      |

| 10% Carrier Modulation Index<br>Max MI = (A - B)/(A + B) | CMI_10 <sub>MAX</sub>   | (Notes 12, 13)                                     |     |       | 30   | %      |

| 100% Carrier Modulation Index<br>MI = (A - B)/(A + B)    | CMI_100                 | (Notes 12, 13)                                     | 95  |       | 100  | %      |

| 10% Modulation Min Pulse<br>Width                        | t <sub>1 MIN</sub>      | Refer to ISO 15693-2 Section<br>7.1 (Notes 13, 18) |     | 7.0   |      | μs     |

| 10% Modulation Max Pulse<br>Width                        | t <sub>1 MAX</sub>      | Refer to ISO 15693-2 Section<br>7.1 (Note 13)      |     |       | 9.44 | μs     |

| 10% Modulation Min Low Time                              | t2 MIN                  | Refer to ISO 15693-2 Section<br>7.1 (Notes 13, 18) |     | 7.0   |      | μs     |

| 10% Modulation Max Low Time                              | t <sub>2 MAX</sub>      | Refer to ISO 15693-2 Section<br>7.1 (Note 13)      |     |       | 9.44 | μs     |

| 10% Modulation Min Rise Time                             | t <sub>3 MIN</sub>      | Refer to ISO 15693-2 Section<br>7.1 (Note 13)      | 0   |       |      | μs     |

| 10% Modulation Max Rise Time                             | t <sub>3 MAX</sub>      | Refer to ISO 15693-2 Section<br>7.1 (Notes 13, 18) |     | 2.5   |      | μs     |

| 100% Modulation Min Pulse<br>Width                       | t <sub>1 MIN</sub>      | Refer to ISO 15693-2 Section<br>7.1 (Notes 13, 18) |     | 6.5   |      | μs     |

| 100% Modulation Max Pulse<br>Width                       | t <sub>1 MAX</sub>      | Refer to ISO 15693-2 Section<br>7.1 (Note 13)      |     |       | 9.44 | μs     |

| 100% Modulation Min Low<br>Time                          | t <sub>2</sub> MIN      | Refer to ISO 15693-2 Section<br>7.1 (Notes 13, 18) |     | 6.5   |      | μs     |

| 100% Modulation Max Low<br>Time                          | <sup>t</sup> 2 MAX      | Refer to ISO 15693-2 Section<br>7.1 (Note 13)      |     |       | 9.44 | μs     |

| 100% Modulation Min Rise<br>Time                         | t <sub>3 MIN</sub>      | Refer to ISO 15693-2 Section<br>7.1 (Note 13)      | 0   |       |      | μs     |

| 100% Modulation Max Rise<br>Time                         | t <sub>3 MAX</sub>      | Refer to ISO 15693-2 Section<br>7.1 (Notes 13, 18) |     | 3.0   |      | μs     |

| RF Timeout                                               | <sup>t</sup> RF_TIMEOUT | (Note 13)                                          |     | 45    |      | ms     |

## MAX66242

# DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

## **Electrical Characteristics (continued)**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                                                                                                         | SYMBOL              | C                      | ONDITIONS                                     | MIN                      | TYP | MAX                       | UNITS |

|-------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|-----------------------------------------------|--------------------------|-----|---------------------------|-------|

| SCL, SDA PINS (Note 21)                                                                                           | 1                   |                        |                                               |                          |     |                           |       |

| Low Level Input Voltage                                                                                           | VIL                 |                        |                                               | -0.3                     |     | 0.10 x<br>V <sub>CC</sub> | V     |

| High Level Input Voltage                                                                                          | VIH                 |                        |                                               | 0.8 x<br>V <sub>CC</sub> |     | V <sub>CC</sub> +<br>0.3  | V     |

| Hysteresis of Schmitt Trigger<br>Inputs                                                                           | V <sub>HYS</sub>    | (Note 13)              |                                               |                          | 0.3 |                           | V     |

| Output Low Voltage                                                                                                | V <sub>OL</sub>     | 4mA sink<br>current    | $T_A = -20^{\circ}C \text{ to } +85^{\circ}C$ |                          |     | 0.10 x<br>V <sub>CC</sub> | V     |

| Output Fall Time from<br>V <sub>IHMIN</sub> to V <sub>ILMAX</sub> with a Bus<br>Capacitance from 10pF to<br>400pF | tof                 | (Note 13)              | $T_A = -40^{\circ}C$ to $-20^{\circ}C$        |                          | 150 | 0.40                      | ns    |

| Input Current with Input<br>Voltage Between 0.1V <sub>CC</sub> and<br>0.9V <sub>CCMAX</sub>                       | Ц                   | (Note 20)              |                                               | -1                       |     | +1                        | μA    |

| SCL Clock Frequency                                                                                               | f <sub>SCL</sub>    | (Notes 13,             | 21)                                           |                          |     | 400                       | kHz   |

| Master Mode Frequency                                                                                             | fMSTR               | f <sub>C</sub> = 13.56 | MHz                                           |                          | 53  |                           | kHz   |

| I <sup>2</sup> C Timeout                                                                                          | ti2C_TIMEOUT        | (Note 21)              |                                               | 25                       |     | 50                        | ms    |

| Hold Time (Repeated) START Condition.                                                                             | <sup>t</sup> HD:STA |                        |                                               | 0.6                      |     |                           | μs    |

| Low Period of the SCL Clock                                                                                       | t <sub>LOW</sub>    |                        |                                               | 1.3                      |     | _                         | μs    |

| High Period of the SCL Clock                                                                                      | thigh               |                        |                                               | 0.6                      |     |                           | μs    |

| Setup Time for a Repeated<br>START Condition                                                                      | <sup>t</sup> SU:STA |                        |                                               | 0.6                      |     |                           | μs    |

| Data Hold Time                                                                                                    | t <sub>HD:DAT</sub> | (Notes 13,             | 22, 23)                                       |                          |     | 0.9                       | μs    |

| Data Setup Time                                                                                                   | t <sub>SU:DAT</sub> | (Notes 24)             | )                                             | 100                      |     |                           | ns    |

| Setup Time for STOP Condition                                                                                     | t <sub>SU:STO</sub> |                        |                                               | 0.6                      |     |                           | μs    |

| Bus Free Time Between a STOP and START Condition                                                                  | t <sub>BUF</sub>    |                        |                                               | 1.3                      |     |                           | μs    |

| Capacitive Load for Each Bus<br>Line                                                                              | CB                  | (Notes 12,             | 13)                                           |                          |     | 400                       | pF    |

MAX66242

## DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

### **Electrical Characteristics (continued)**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 2)

- **Note 2:** Limits are 100% production tested at  $T_A = +25^{\circ}$ C or  $T_A = +85^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are at 25°C.

- Note 3: Operating current continuously reading the Memory/MAC Read/Write Register at 400kHz with no RF power.

- **Note 4:** Refer to full data sheet.

- Note 5: Refer to full data sheet.

- **Note 6:** For commands where the t<sub>PROG</sub> interval occurs see the applicable Communication Examples sections. For RF commands, the interval begins after the EOF of a valid request frame. For I<sup>2</sup>C commands the interval begins after the Acknowledge bit of the last data byte. The interval ends once the device's self-timed EEPROM write cycle is complete.

- Note 7: Write-cycle endurance is tested in compliance with JESD47G.

- Note 8: Not 100% production tested; guaranteed by reliability qualification.

- Note 9: Data retention is tested in compliance with JESD47G.

Note 10: Guaranteed by 100% production test at elevated temperature for a shorter time; equivalence of this production test to the data sheet limit at operating temperature range is established by reliability testing.

- Note 11: EEPROM writes can become nonfunctional after the data-retention time is exceeded. Long-term storage at elevated temperatures is not recommended.

- Note 12: System requirement.

- Note 13: Guaranteed by design, and/or characterization only. Not production tested.

- Note 14: Applies to Read/Write Scratchpad (writing), Write Memory, Compute and Read Page MAC, Set Protection, Authenticated Write Memory RF Setup, Authenticated Write Memory RF Execute, Authenticated Set Protection RF Setup, Authenticated Set Protection RF Setup, Authenticated Write commands.

- Note 15: Measured from  $V_{OUT}$  = 1.8V to  $V_{OUT}$  = 3.3V at 2.5A/m with a 0.1µF load.

- Note 16: The t<sub>RFAIP</sub> interval begins immediately after an EOF for a valid ISO15693 request frame and ends before SOF of the response frame. A pulse of width t<sub>RFAIP</sub> will only occur only for Read/Write Scratchpad (writing) and Control Write.

- Note 17: CMI\_10 > 15% is suggested.

- Note 18: Field strength between 350mA/m and 5A/m.

- Note 19:All I<sup>2</sup>C timing values are referred to V<sub>IH MIN</sub> and V<sub>IL MAX</sub> levels.

- Note 20:1/O pins of the MAX66242 do not obstruct SDA and SCL lines if V<sub>CC</sub> and the RF fields are switched off.

- Note 21: The minimum SCL clock frequency is limited by the I<sup>2</sup>C timeout feature. If SCL remains low longer than this interval, the MAX66242 behaves as though it has sensed a STOP condition. SDA has no affect on this timeout condition.

- Note 22: The MAX66242 provides a hold time of at least 200ns for the SDA signal (referred to the V<sub>IHMIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 23: The master can provide a hold time of Ons minimum when writing to the device.

- Note 24: A fast-mode I<sup>2</sup>C-bus device can be used in a standard-mode I<sup>2</sup>C-bus system, but the requirement t<sub>SU:DAT</sub> ≥ 250ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>RMAX</sub> + t<sub>SU:DAT</sub> = 1000 + 250 = 1250ns (according to the standard-mode I<sup>2</sup>C-bus specification) before the SCL line is released.

MAX66242

## DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

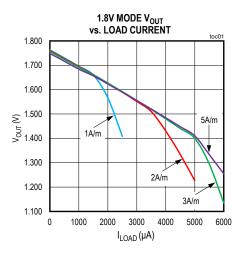

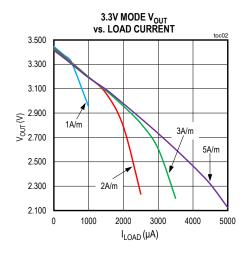

## **Typical Operating Characteristics**

## MAX66242

## DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

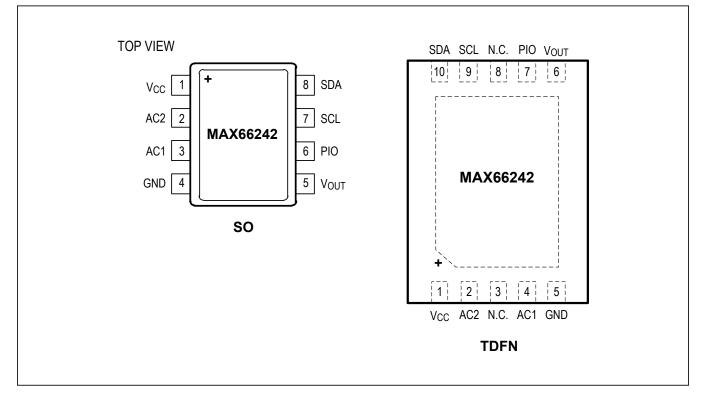

### **Pin Configurations**

#### **Pin Descriptions**

| F  | PIN  |      | FUNCTION                                                                       |

|----|------|------|--------------------------------------------------------------------------------|

| SO | TDFN | NAME | FUNCTION                                                                       |

| 1  | 1    | Vcc  | Power-Supply Input                                                             |

| 2  | 2    | AC2  | Antenna Connection                                                             |

| 3  | 4    | AC1  | Antenna Connection                                                             |

| 4  | 5    | GND  | Ground Reference                                                               |

| 5  | 6    | VOUT | Energy Harvesting Pin. See the PIO and Energy Harvesting Output section.       |

| 6  | 7    | PIO  | Multipurpose Open-Drain Pin. See the PIO and Energy Harvesting Output section. |

| 7  | 9    | SCL  | I <sup>2</sup> C Serial Clock Input                                            |

| 8  | 10   | SDA  | I <sup>2</sup> C Serial Data Input/Output                                      |

| _  | 3, 8 | N.C. | Not Connected                                                                  |

### MAX66242

### DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

#### **Detailed Description**

The MAX66242 transponder combines an ISO 15693 RF front-end, a SHA-256 engine, 4096 bits of user EEPROM organized as 16 256-bit pages, protection control, status memory, and a 64-bit ROM ID in a single chip. A 256-bit scratchpad assists when installing a new secret or stores the challenge when computing a page MAC. In addition to the RF interface, the part also has an  $I^2C$  interface, which can operate as slave port or as master port.

It is common for a secure authentication IC to be attacked using a variety of sophisticated die-level methods to extract secure data, reverse device settings, etc., in an effort to compromise a system security implementation. To provide the highest affordable protection against this inevitable malicious attack, the MAX66242 employs proprietary die-level physical techniques, circuits, and crypto methods to protect sensitive data, control signals, and control settings.

There are multiple programmable options for the 4Kb user array including unrestricted read/write and four protection modes: read protection, write protection, EPROM emulation mode, and authentication protection. Read protection prevents user read-access to the memory, which effectively extends the secret into the protected memory. The data remains accessible only for the SHA-256 engine. Write protection prevents changes to the memory data. EPROM emulation mode logically ANDs memory data with incoming new data, which allows changing bits from 1 to 0, but not vice versa. By changing one bit at a time, this mode could be used to create a nonvolatile, nonresettable counter. EPROM emulation mode requires that the memory is not write protected. Authentication protection, if activated, requires that the host prove itself as authentic (i.e., knows the MAX66242 secret) to modify the memory by supplying a correct MAC that is based on the device secret, its ROM ID, memory data, and the new data to be copied to EEPROM. If the authentication hurdle is

passed, the write protection and EPROM emulation mode protections still determine the effect of the write access. Any protection, if activated, applies to individual memory pages. As a factory default, none of the protections is activated. Once authentication protection is activated, the reader must authenticate itself for memory writes as well as for additional changes to the memory protection.

In addition to its important use as a unique data value in cryptographic SHA-256 computations, the device's 64-bit ROM ID can be used to electronically identify the object to which the MAX66242 is associated. Applications of the MAX66242 include, access control, asset tracking, printer cartridge configuration and monitoring, medical sensor authentication and calibration, and system intellectual property protection.

#### **Overview**

The block diagram in Figure 1 shows the relationships between the major control and memory sections of the MAX66242. The device has six main data components: 16 256-bit pages of user EEPROM, a 256-bit secret, protection control/status memory, 512-bit SHA-256 engine, 64-bit ROM ID, and a 256-bit scratchpad.

<u>Figure 2</u> shows the applicable commands and the affected data fields. The network function commands allow the reader to identify all transponders in its range and to change their state, e.g., to select one for further communication. The protocol required for these network function commands is described in the <u>Network Function</u> <u>Commands</u> section. The memory and control functions fall into seven categories: ISO 15693 generic commands, secret installation, memory access, protection setting, MAC computation, configuration and control with verification, and I<sup>2</sup>C master port operation. The protocol for these commands is described in the <u>Memory and Control Function</u> <u>Function Commands</u> section. All data is read and written least significant bit (LSb) first, starting with the least significant byte (LSB).

MAX66242

## DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

Figure 1. Block Diagram

## MAX66242

Г

## DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

| Command<br>Type:                        | AVAILABLE<br>COMMANDS:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DATA FIELD<br>AFFECTED:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NETWORK FUNCTION<br>COMMANDS            | INVENTORY<br>STAY QUIET<br>SELECT<br>RESET TO READY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | UID, AFI, DSFID<br>UID<br>UID<br>(N/A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MEMORY AND CONTROL<br>FUNCTION COMMANDS | GET SYSTEM INFORMATION<br>WRITE MEMORY<br>READ MEMORY<br>READ SINGLE BLOCK<br>READ MULTIPLE BLOCKS<br>SET PROTECTION<br>READ STATUS<br>READ/WRITE SCRATCHPAD<br>LOAD AND LOCK SECRET<br>COMPUTE AND LOCK SECRET<br>COMPUTE AND READ PAGE MAC<br>AUTHENTICATED WRITE<br>MEMORY RF SETUP<br>AUTHENTICATED WRITE<br>MEMORY RF SETUP<br>AUTHENTICATED WRITE<br>MEMORY RF SETUP<br>AUTHENTICATED WRITE<br>MEMORY RF SETUP<br>AUTHENTICATED SET<br>PROTECTION READ<br>CONTROL WRITE<br>CONTROL READ<br>GET 1-WIRE ROM ID<br>PERIPHERAL TRANSACTION<br>WRITE AFI<br>LOCK AFI<br>WRITE DSFID | <ul> <li>UID, AFI, DSFID, CONSTANTS</li> <li>MFGCODE, USER MEMORY, PROTECTION<br/>SETTINGS</li> <li>MFGCODE, USER MEMORY, PROTECTION<br/>SETTINGS</li> <li>SELECTED MEMORY BLOCK, PROTECTION<br/>SETTINGS</li> <li>SELECTED MEMORY BLOCKS, PROTECTION<br/>SETTINGS</li> <li>MFGCODE, PROTECTION SETTINGS</li> <li>MFGCODE, PROTECTION SETTINGS,<br/>PERSONALITY BYTES</li> <li>MFGCODE, SCRATCHPAD</li> <li>MFGCODE, SECRET AND LOCK STATUS,<br/>SCRATCHPAD</li> <li>MFGCODE, SECRET, ROM ID, USER MEMORY,<br/>SCRATCHPAD</li> <li>MFGCODE, USER MEMORY, PAGE BLOCK NUMBER,<br/>SECRET, PROTECTION SETTINGS</li> <li>MFGCODE, USER MEMORY, PAGE BLOCK NUMBER,<br/>SECRET, PROTECTION SETTINGS</li> <li>MFGCODE, USER MEMORY, PAGE BLOCK NUMBER,<br/>SECRET, PROTECTION SETTINGS</li> <li>MFGCODE, USER MEMORY</li> <li>MFGCODE, USER MEMORY</li> <li>MFGCODE, USER MEMORY</li> <li>MFGCODE, ROTECTION SETTINGS</li> <li>MFGCODE, PROTECTION SETTINGS</li> <li>MFGCODE, EEPROM CONFIGURATION BYTE<br/>MFGCODE, EEPROM CONFIGURATION BYTE<br/>MFGCODE, SRAM CONTROL BYTE, PIO PORTS<br/>MFGCODE, SRAM CONTROL BYTE, PIO PORTS<br/>MFGCODE, RAM CONTROL BYTE, PIO PORTS<br/>MFGCODE, ROM ID</li> <li>MFGCODE, I<sup>2</sup>C PORT MASTER MODE<br/>AFI BYTE</li> <li>AFI LOCK STATUS<br/>DSFID BYTE</li> </ul> |

Figure 2. Commands Overview

### MAX66242

## DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

#### **Memory Resources**

The memory of the MAX66242 consists of user EEPROM, secret memory, an SRAM scratchpad, personality registers, ROM ID, and two ISO 15693-specific bytes. <u>Table 1</u> shows the size, access mode, and purpose of the various memory areas. Brackets around an access mode indicate possible restrictions, such as write protection or read protection.

The user memory is organized as 16 pages of 32 bytes each (Figure 6). A page is divided into 8 page blocks of 32 bits each. With the MAX66242, the page protection applies to individual memory pages. The user memory is written in page blocks. If not read protected, the memory can be read starting at any page block of any page. The protocol allows reading multiple page blocks and pages up to the end of the memory in a single read command flow.

The secret is either directly written (loaded) or computed. This write access always encompasses the entire 32-byte secret. To protect against transmission errors, the new secret (loading) or a partial secret (computing) is first written to the scratchpad from where it can be read for verification. As the name implies, the secret memory is not user readable. To protect a secret from changes, it must be write protected (locked). Page protection control is activated through the Write Page Protection command. Besides write protection, read protection and EPROM emulation mode, the MAX66242 supports authentication protection. If authentication protection is activated, changes to the page protection settings as well as writing to the protected user memory require that the reader provide a valid MAC for the operation. Once a protection is activated, it cannot be reversed. The protection settings as well as the personality registers are read accessible through the Read Status command. See the <u>Memory and Control Function Commands</u> section for command flow details.

Depending on the command, the ROM ID may be required in the MAC computations. This makes the MAC generated by a MAX66242 or written to the MAX66242 (if authentication protection is activated) device-specific, even if the values of all other data elements are identical. Instead of requiring the reader to derive the ROM ID from the UID, the MAX66242 supports a special command to read the ROM ID directly.

Note that the ISO 15693 standard commands Read Single Block and Read Multiple Blocks do not address the user memory by page number and page block number. Instead, they use absolute block numbers counting from 0 to 127. Figure 7 shows how these absolute numbers map to the user memory.

| NAME                                      | SIZE<br>(BYTES) | ACCESS MODE                       | PURPOSE                                                                                                                                        |

|-------------------------------------------|-----------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| User Memory<br>(EEPROM)                   | 512             | (Read), (Write),<br>Internal Read | Application-specific data storage; also used for MAC computations.                                                                             |

| Scratchpad<br>(SRAM)                      | 32              | Read, Write,<br>Internal Read     | Intermediate data storage when installing a secret; also used to store the challenge for a MAC computation.                                    |

| Personality Registers                     | 4               | Read,<br>Internal Read            | Lock status indicator for the secret and read access to the device's manufacturer ID (factory preprogrammed parts).                            |

| ROM ID                                    | 8               | Read,<br>Internal Read            | Used for MAC computations.                                                                                                                     |

| Application Family<br>Identifier (AFI)    | 1               | Read, (Write), RF<br>port only    | Can be used during the inventory phase to narrow the number<br>of transponders that participate in the discovery or anti-collision<br>process. |

| Data Storage Format<br>Identifier (DSFID) | 1               | Read, (Write), RF<br>port only    | User byte that can provide details on how the data in the user memory is structured.                                                           |

#### Table 1. Memory Resources

MAX66242

# DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

|         | PG | . BL | 00 | K7 | PG | . BL | .OC | K 6 | PG | . BL | 00 | K 5 | PG | . BL | .OC | K 4 | PG | . BL | oc | K 3 | PG. | BL | 00 | K 2 | PG | . BL | 00 | K 1 | PG. | BL | СК | 0  |

|---------|----|------|----|----|----|------|-----|-----|----|------|----|-----|----|------|-----|-----|----|------|----|-----|-----|----|----|-----|----|------|----|-----|-----|----|----|----|

|         | B3 | B2   | B1 | BO | B3 | B2   | B1  | BO  | B3 | B2   | B1 | BO  | B3 | B2   | B1  | BO  | B3 | B2   | B1 | BO  | B3  | B2 | B1 | BO  | B3 | B2   | B1 | BO  | B3  | B2 | B1 | BO |

| Page 0  |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 1  |    |      |    |    |    |      |     |     |    |      |    |     |    | -    |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 2  |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 3  |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 4  |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 5  |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 6  |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 7  |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 8  |    |      |    |    |    |      |     |     |    |      | -  |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 9  |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 10 |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 11 |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 12 |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 13 |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 14 |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

| Page 15 |    |      |    |    |    |      |     |     |    |      |    |     |    |      |     |     |    |      |    |     |     |    |    |     |    |      |    |     |     |    |    |    |

Figure 6. User Memory Map

|         |             |             | 1           | 1           | 1           |             | 1           | 1           |

|---------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

|         | PG. BLOCK 7 | PG. BLOCK 6 | PG. BLOCK 5 | PG. BLOCK 4 | PG. BLOCK 3 | PG. BLOCK 2 | PG. BLOCK 1 | PG. BLOCK 0 |

| Page 0  | Block 7     | Block 6     | Block 5     | Block 4     | Block 3     | Block 2     | Block 1     | Block 0     |

| Page 1  | Block 15    | Block 14    | Block 13    | Block 12    | Block 11    | Block 10    | Block 9     | Block 8     |

| Page 2  | Block 23    | Block 22    | Block 21    | Block 20    | Block 19    | Block 18    | Block 17    | Block 16    |

| Page 3  | Block 31    | Block 30    | Block 29    | Block 28    | Block 27    | Block 26    | Block 25    | Block 24    |

| Page 4  | Block 39    | Block 38    | Block 37    | Block 36    | Block 35    | Block 34    | Block 33    | Block 32    |

| Page 5  | Block 47    | Block 46    | Block 45    | Block 44    | Block 43    | Block 42    | Block 41    | Block 40    |

| Page 6  | Block 55    | Block 54    | Block 53    | Block 52    | Block 51    | Block 50    | Block 49    | Block 48    |

| Page 7  | Block 63    | Block 62    | Block 61    | Block 60    | Block 59    | Block 58    | Block 57    | Block 56    |

| Page 8  | Block 71    | Block 70    | Block 69    | Block 68    | Block 67    | Block 66    | Block 65    | Block 64    |

| Page 9  | Block 79    | Block 78    | Block 77    | Block 76    | Block 75    | Block 74    | Block 73    | Block 72    |

| Page 10 | Block 87    | Block 86    | Block 85    | Block 84    | Block 83    | Block 82    | Block 81    | Block 80    |

| Page 11 | Block 95    | Block 94    | Block 93    | Block 92    | Block 91    | Block 90    | Block 89    | Block 88    |

| Page 12 | Block 103   | Block 102   | Block 101   | Block 100   | Block 99    | Block 98    | Block 97    | Block 96    |

| Page 13 | Block 111   | Block 110   | Block 109   | Block 108   | Block 107   | Block 106   | Block 105   | Block 104   |

| Page 14 | Block 119   | Block 118   | Block 117   | Block 116   | Block 115   | Block 114   | Block 113   | Block 112   |

| Page 15 | Block 127   | Block 126   | Block 125   | Block 124   | Block 123   | Block 122   | Block 121   | Block 120   |

Figure 7. User Memory Access Using Absolute Block Numbers

MAX66242

## DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

## ISO 15693 Transponder States and State Transitions

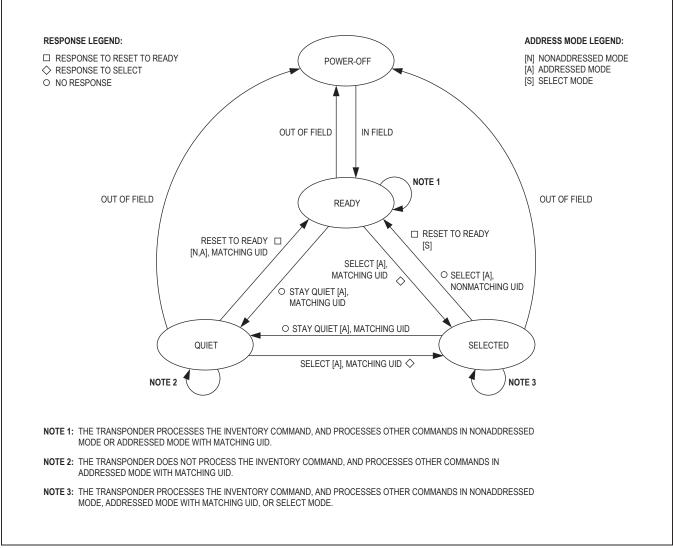

ISO 15693 defines four transponder states and three address modes. The states are power-off, ready, quiet, and selected. The address modes are nonaddressed, addressed, and select. The addressed mode requires that the reader include the transponder's UID in the request. Figure 23 shows how the Reset to Ready, Stay Quiet, and Select commands respond when changing the transponder's state. Table 4 shows how other commands respond depending on address mode and the transponder's state. Note that Stay Quiet never generates a response. For full details, refer to ISO 15693-2, Section 7.

#### **Power-Off State**

This state applies if the transponder is outside the reader's RF field. A transponder transitions to the power-off state when leaving the power-delivering RF field. When entering the RF field, the transponder automatically transitions to the ready state.

#### **Ready State**

In this state, a transponder has enough power to perform any of its functions. The purpose of the ready state is to have the transponder population ready to process the inventory command as well as other commands sent in the addressed or nonaddressed mode. A transponder can exit the ready state and transition to the quiet or the selected state upon receiving the Stay Quiet or Select command sent in addressed mode.

#### **Quiet State**

In this state, a transponder has enough power to perform any of its functions. The purpose of the quiet state is to silence transponders with which the reader does not want to communicate. Only commands sent with the addressed mode are processed. This way the reader can use the nonaddressed mode for communication with remaining transponders in the ready state. A transponder can exit the quiet state and transition to the ready state upon receiving the Reset to Ready command in addressed or nonaddressed mode. It can also transition to the selected state upon receiving Select commands sent in addressed mode.

#### **Selected State**

In this state, a transponder has enough power to perform any of its functions. The purpose of the selected state is to isolate the transponder with which the reader wants to communicate. Commands are processed regardless of the address mode in which they are sent, including the Inventory command. With multiple transponders in the RF field, the reader can put one transponder in the selected state, leaving all others in the ready state. For a transponder in the selected state, the reader can use the selected mode, which keeps the request data packets as short as with the nonaddressed mode. A new transponder entering the RF field will not disturb communication since it powers up in the ready state. A transponder can exit the selected state and transition to the ready state upon receiving the Reset to Ready command sent in nonaddressed or addressed mode. It can also transition to the quiet state upon receiving the Stay Quiet command sent in the addressed mode. A transponder also transitions from selected to ready upon receiving a Select command if the UID in the request is different from the transponder's own UID. In this case, the reader's intention is to transition another transponder with the matching UID to the selected state. If the transponder already in the selected state does not recognize the command, e.g., due to a bit error, two transponders could be in the selected state. To prevent this from happening, the reader should use the Reset to Ready or the Stay Quiet command to transition a transponder out of the selected state.

|                       | ADDRESS MODES                                               |                                                          |                                                       |  |  |  |  |  |  |  |  |  |  |

|-----------------------|-------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| TRANSPONDER<br>STATES | NONADDRESSED MODE<br>(ADDRESS_FLAG = 0;<br>SELECT_FLAG = 0) | ADDRESSED MODE<br>(ADDRESS_FLAG = 1;<br>SELECT_FLAG = 0) | SELECT MODE<br>(ADDRESS_FLAG = 0;<br>SELECT_FLAG = 1) |  |  |  |  |  |  |  |  |  |  |

| Power-Off             | (Inactive)                                                  | (Inactive)                                               | (Inactive)                                            |  |  |  |  |  |  |  |  |  |  |

| Ready                 | Respond                                                     | Respond                                                  | Do not respond                                        |  |  |  |  |  |  |  |  |  |  |

| Quiet                 | Do not respond                                              | Respond                                                  | Do not respond                                        |  |  |  |  |  |  |  |  |  |  |

| Selected              | Respond                                                     | Respond                                                  | Respond                                               |  |  |  |  |  |  |  |  |  |  |

### Table 4. Command Response vs. Transponder State and Address Mode Combinations

## MAX66242

## DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

Figure 23. ISO 15693 State Transition Diagram

MAX66242

## DeepCover Secure Authenticator with ISO 15693, I<sup>2</sup>C, SHA-256, and 4Kb User EEPROM

### I<sup>2</sup>C Interface Description

The block diagram in Figure 1 shows the relationships between the major control and memory sections of the MAX66242. The device has six main data components: 16 256-bit pages of user EEPROM, one 256-bit secret, protection-control/status memory, 512-bit SHA-256 engine, 64-bit ROM ID, and a 256-bit scratchpad. Figure 24 shows the applicable commands and the affected data fields.

#### Memory

The MAX66242 memory consists of three areas: 1) the directly accessible 256-byte address space with the scratchpad, protection status registers, ROM ID, and special function addresses, 2) the indirectly accessible user memory, and 3) the indirectly write-accessible secret memory of 32 bytes.

Figure 25 shows the organization of the directly accessible memory space, which begins at address 00h with the scratchpad. The register section begins at address 40h with the command register, which is followed by the MAC Read/Write Register. The protection status registers begin at address 50h (for memory pages) and 60h (secret). The ROM ID and several other factory programmable registers begin at address 68h. The scratchpad is implemented as volatile SRAM. The address range 50h and higher is nonvolatile.

The directly accessible memory space encompasses three types of memory: read/write, write-only, open read/ indirect write, and read-only. To write to or read from the volatile scratchpad, one must begin at address 00h. Writing must take place in block of 4 bytes. The command register is write-only. The protection status registers can be read openly, but require the use of special function commands for writing. The ROM ID, manufacturer ID, and factory byte are read-only.

The EEPROM of the MAX66242 can be programmed using a factory preprogramming service. If this service is used, the Manufacturer ID is different from the 0000h default of unprogrammed parts.

#### **Command Register (40h)**

To install the secret, to read from or write to the user memory, or to set the user memory protection, or to compute and read a page MAC, the MAX66242 needs to receive a command from the I<sup>2</sup>C host. Commands are written one at a time to the Command register. Most commands consist of a command code and a parameter byte. The command code indicates the type of instruction and the position of the read pointer for the next I<sup>2</sup>C read-access. See the Function Commands section for details.

#### MAC Read/Write Register (41h)

For authenticated writing (memory, protection), the I<sup>2</sup>C host must provide a MAC to prove its authenticity to the MAX66242. To verify the MAX66242 authenticity, the Compute and Read Page MAC command delivers a MAC for the host to read. The MAC Read/Write Register is the single address access point for MAC.

#### Memory Protection Status Registers (50h–5Fh)

Each individual user memory page can be protected in several ways. Protections are activated through the Set Protection command or Authenticated Set Protection command (see the Function Commands section). The Memory Protection Status Registers (Table 41), one for each user memory page, allow the I<sup>2</sup>C host to verify the protection status. The Memory protection status register at address 50h corresponds to user memory page 0, etc.

| AVAILABLE<br>COMMANDS:       | DATA FIELD<br>AFFECTED:                                | MAX66242                    |

|------------------------------|--------------------------------------------------------|-----------------------------|

| WRITE MEMORY                 | USER MEMORY, PROTECTION SETTINGS                       |                             |

| READ MEMORY                  | USER MEMORY, PROTECTION SETTINGS                       |                             |

| SET PROTECTION               | PROTECTION SETTINGS                                    |                             |

| NSTALL AND LOCK SECRET       | SECRET, USER MEMORY, S                                 | CRATCHPAD AND LOCK STATUS   |

| COMPUTE AND READ PAGE MAC    | SECRET, USER MEMORY, SCRATCHPAD, 64-BIT ROM ID         |                             |

| AUTHENTICATED WRITE MEMORY   | SECRET, USER MEMORY, 64-BIT ROM ID, PROTECTION SETTING |                             |

| AUTHENTICATED SET PROTECTION | SECRET, MEMORY PAGE N                                  | UMBER, PROTECTION SETTINGS, |

|                              | 64-BIT ROM ID                                          |                             |

| CONFIGURATION WRITE          | EEPROM CONFIGURATION BYTE                              |                             |

| CONFIGURATION READ           | EEPROM CONFIGURATION BYTE                              |                             |

| CONTROL WRITE                | SRAM CONTROL BYTE                                      |                             |

| ONTROL READ                  | SRAM CONTROL BYTE                                      |                             |

Figure 24. Commands Overview