### **General Description**

The MAX8625A PWM step-up/down regulator is intended to power digital logic, hard disk drives, motors, and other loads in portable, battery-powered devices such as PDAs, cell phones, digital still cameras (DSCs), and MP3 players. The MAX8625A provides either a fixed 3.3V or adjustable output voltage (1.25V to 4V) at up to 0.8A from a 2.5V to 5.5V input. The MAX8625A utilizes a 2A peak current limit.

Maxim's proprietary H-bridge topology provides a seamless transition through all operating modes without the glitches commonly seen with other devices. Four internal MOSFETs (two switches and two synchronous rectifiers) with internal compensation minimize external components. A SKIP input selects a low-noise, fixed-frequency PWM mode, or a high-efficiency skip mode where the converter automatically switches to PFM mode under light loads for best light-load efficiency. The internal oscillator operates at 1MHz to allow for a small external inductor and capacitors.

The MAX8625A features current-limit circuitry that shuts down the IC in the event of an output overload. In addition, soft-start circuitry reduces inrush current during startup. The IC also features True Shutdown which disconnects the output from the input when the IC is disabled. The MAX8625A is available in a 3mm x 3mm, 14-pin TDFN package.

### **Applications**

PDAs and Smartphones

DSCs and Camcorders

MP3 Players and Cellular Phones

Battery-Powered Hard Disk Drive (HDD)

### **Features**

- ♦ Four Internal MOSFET True H-Bridge Buck/Boost

- ♦ Glitch-Free, Buck-Boost Transitions

- ♦ Minimal Output Ripple Variation on Transitions

- ♦ Up to 92% Efficiency

- ♦ 37µA (typ) Quiescent Current in Skip Mode

- ♦ 2.5V to 5.5V Input Range

- ♦ Fixed 3.3V or Adjustable Output

- ♦ 1µA (max) Logic-Controlled Shutdown

- **♦ True Shutdown**

- ♦ Output Overload Protection

- **♦ Internal Compensation**

- ♦ Internal Soft-Start

- ♦ 1MHz Switching Frequency

- **♦ Thermal-Overload Protection**

- ♦ Small 3mm x 3mm, 14-Pin TDFN Package

### **Ordering Information**

| PART         | PIN-<br>PACKAGE | TOP MARK |  |

|--------------|-----------------|----------|--|

| MAX8625AETD+ | 14 TDFN-EP**    | ABQ      |  |

**Note:** The device is specified over the -40°C to +85°C extended temperature range.

+Denotes a lead(Pb)-free/RoHS-compliant package.

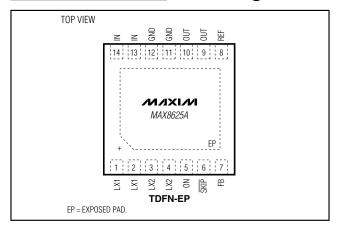

### Pin Configuration

True Shutdown is a trademark of Maxim Integrated Products, Inc.

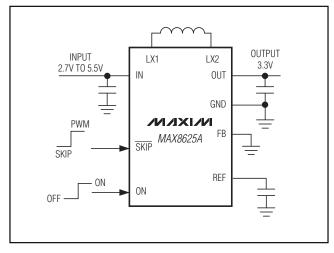

### \_Typical Operating Circuit

Maxim Integrated Products

<sup>\*\*</sup>EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| IN, OUT, SKIP, ON to GND0.3V to +6V            | Operating Temperature Range40°C to +85°C |

|------------------------------------------------|------------------------------------------|

| REF, FB to GND0.3V to (IN + 0.3V)              | Junction Temperature+150°C               |

| LX2, LX1 (Note 1)±1.5A <sub>RMS</sub>          | Storage Temperature Range65°C to +150°C  |

| Continuous Power Dissipation ( $T_A = +70$ °C) | Lead Temperature (soldering, 10s)+300°C  |

| Single-Layer Board (derate 18.5mW/°C           |                                          |

| above $T_A = +70^{\circ}C$ )                   |                                          |

**Note 1:** LX1 and LX2 have internal clamp diodes to IN, GND and OUT, GND, respectively. Applications that forward bias these diodes should take care not to exceed the device's power-dissipation limits.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 3.6V, ON = \overline{SKIP} = IN, FB = GND, V_{OUT} = 3.3V, LX_unconnected, C_{REF} = C5 = 0.1 \mu F to GND, Figure 4. T_A = -40 °C to +85 °C. Typical values are at T_A = +25 °C, unless otherwise noted.) (Note 2)$

| PARAMETER                                            | SYMBOL                                     | CONDITIONS                                                                       | MIN   | TYP  | MAX   | UNITS |

|------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------|-------|------|-------|-------|

| Supply Range                                         | V <sub>IN</sub>                            |                                                                                  | 2.5   |      | 5.5   | V     |

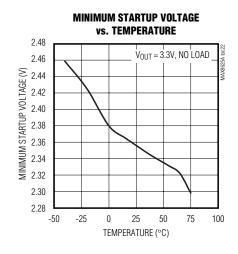

| UVLO Threshold                                       | UVLO                                       | V <sub>IN</sub> rising, 60mV hysteresis                                          | 2.20  |      | 2.49  | V     |

| Quiescent Supply Current, FPWM<br>Mode, Switching    | liN                                        | No load, V <sub>OUT</sub> = 3.2V                                                 |       | 15   | 22    | mA    |

| Quiescent Supply Current, Skip<br>Mode, Switching    | I <sub>IN</sub>                            | SKIP = GND, no load                                                              |       | 37   |       | μΑ    |

| Quiescent Supply Current, No<br>Switching, Skip Mode | I <sub>IN</sub>                            | SKIP = GND, FB = 1.3V                                                            |       | 35   | 45    | μΑ    |

| Claudalana Consolo Compani                           | 1                                          | ON = GND, T <sub>A</sub> = +25°C                                                 |       | 0.1  | 1     | μА    |

| Shutdown Supply Current                              | IIN                                        | T <sub>A</sub> = +85°C                                                           |       | 0.2  |       |       |

|                                                      |                                            | PWM mode, V <sub>IN</sub> = 2.5V to 5.5V                                         |       | 3.30 |       | V     |

| Output Voltage Accuracy                              |                                            | $I_{OUT} = 0$ to 0.5A, $V_{IN} = 2.5V$ to 5.5V, $T_A = -40$ °C to +85°C (Note 3) | -1    |      | +1    | %     |

| (Fixed Output)                                       |                                            | SKIP mode, valley regulation value                                               | 3.28  |      |       | V     |

|                                                      |                                            | Average skip voltage                                                             | 3.285 |      |       |       |

|                                                      |                                            | Load step +0.5A                                                                  |       | -3   |       | %     |

| Output Voltage Range<br>(Adjustable Output)          |                                            |                                                                                  | 1.25  |      | 4.00  | V     |

| Maximum Output Current                               |                                            | V <sub>IN</sub> = 3.6V                                                           |       | 0.80 |       | А     |

| Soft-Start                                           |                                            | L = 3.3µH; C <sub>OUT</sub> = C3 + C4 = 44µF                                     |       | 250  |       | mA/ms |

| Load Regulation                                      |                                            | I <sub>OUT</sub> = 0 to 500mA                                                    |       | 0.1  |       | %/A   |

| Line Regulation                                      |                                            | V <sub>IN</sub> = 2.5V to 5.5V                                                   | 0.03  |      |       | %/V   |

| OUT Bias Current                                     | t I <sub>OUT</sub> V <sub>OUT</sub> = 3.3V |                                                                                  |       | 3    |       | μΑ    |

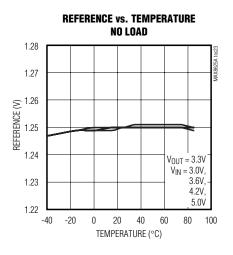

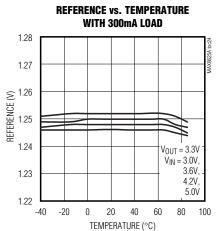

| REF Output Voltage                                   | V <sub>REF</sub>                           | V <sub>IN</sub> = 2.5V to 5.5V                                                   | 1.244 | 1.25 | 1.256 | V     |

| REF Load Regulation                                  |                                            | $I_{REF} = 10\mu A$                                                              |       | 1    |       | mV    |

| FB Feedback Threshold VFB                            |                                            | $I_{OUT}$ = 0 to full load, PWM mode; $V_{IN}$ = 2.5V to 5.5V                    | 1.244 | 1.25 | 1.258 | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=3.6V, ON=\overline{SKIP}=IN, FB=GND, V_{OUT}=3.3V, LX\_unconnected, C_{REF}=C5=0.1\mu F$  to GND, Figure 4.  $T_A=-40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $T_A=+25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                                      | SYMBOL              | CONDITIONS                                                                                                  | MIN  | TYP   | MAX  | UNITS |  |

|----------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------|------|-------|------|-------|--|

| FB Dual-Mode Threshold                                         | V <sub>FBDM</sub>   |                                                                                                             | 75   | 100   | 125  | mV    |  |

| FB Leakage Current                                             | I <sub>FB</sub>     | V <sub>FB</sub> = 1.3V, T <sub>A</sub> = +25°C                                                              |      | 0.001 | 0.1  | μА    |  |

| FB Leakage Current                                             | IFB                 | V <sub>FB</sub> = 1.3V, T <sub>A</sub> = +85°C                                                              |      | 0.01  |      |       |  |

| ON, SKIP Input High Voltage                                    | VIH                 | 2.5V < V <sub>IN</sub> < 5.5V                                                                               | 1.6  |       |      | V     |  |

| ON, SKIP Input Low Voltage                                     | VIL                 | 2.5V < V <sub>IN</sub> < 5.5V                                                                               |      |       | 0.45 | V     |  |

| ON Input Leakage Current                                       | lu u                | $2.5V < V_{IN} < 5.5V$ , $T_A = +25^{\circ}C$                                                               |      | 0.001 | 1    | μΑ    |  |

| ON Input Leakage Current                                       | lihl                | $T_A = +85^{\circ}C$                                                                                        |      | 0.01  |      | μΑ    |  |

| SKIP Input Leakage Current                                     | ISKIPH              | V <sub>SKIP</sub> = 3.6V                                                                                    |      | 3     | 12   |       |  |

| SKIF IIIput Leakage Current                                    | ISKIPL              | V <sub>SKIP</sub> = 0V                                                                                      | -2   | -0.2  |      | μΑ    |  |

| Peak Current Limit                                             | ILIMP               | LX1 PMOS                                                                                                    | 1700 | 2000  | 2300 | mA    |  |

| Fault Latch-Off Delay                                          |                     |                                                                                                             |      | 100   |      | ms    |  |

|                                                                | R <sub>ON</sub>     | Each MOSFET, T <sub>A</sub> = +25°C                                                                         |      | 0.05  | 0.1  | Ω     |  |

| MOSFET On-Resistance                                           |                     | Each MOSFET, $V_{IN} = 2.5V$ to 5.5V,<br>$T_A = -40$ °C to +85°C                                            |      |       | 0.2  |       |  |

| Rectifier-Off Current Threshold   I <sub>LX10FF</sub>   SKIP = |                     | SKIP = GND                                                                                                  |      | 125   |      | mA    |  |

| Idle-Mode Current Threshold                                    | ISKIP               | SKIP = GND, load decreasing                                                                                 |      | 100   |      | mA    |  |

| (Note 4)                                                       | ISKIP               | Load increasing                                                                                             |      | 300   |      | IIIA  |  |

| LX1, LX2 Leakage Current                                       | I <sub>LXLKG</sub>  | $V_{IN} = V_{OUT} = 5.5V$ , $V_{LX1} = 0V$ to $V_{IN}$ , $V_{LX2} = 0V$ to $V_{OUT}$ , $T_A = +25^{\circ}C$ |      | 0.01  | 1    | μΑ    |  |

|                                                                |                     | $T_A = +85^{\circ}C$                                                                                        |      | 0.2   |      | 1     |  |

| Out Reverse Current                                            | I <sub>LXLKGR</sub> | $V_{IN} = V_{LX1} = V_{LX2} = 0V$ , $V_{OUT} = 5.5V$ , measure I (LX2), $T_A = +25^{\circ}C$                |      | 0.01  | 1    | μΑ    |  |

|                                                                |                     | $T_A = +85^{\circ}C$                                                                                        |      | 0.5   |      |       |  |

| Minimum T <sub>ON</sub>                                        | TONMIN              |                                                                                                             |      | 25    |      | %     |  |

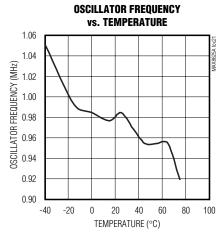

| OSC Frequency                                                  | Foscewm             |                                                                                                             | 850  | 1000  | 1150 | kHz   |  |

| Thermal Shutdown                                               |                     | 15°C hysteresis                                                                                             |      | +165  |      | °C    |  |

|                                                                | _                   |                                                                                                             | _    |       |      |       |  |

- Note 2: The device is production tested at  $T_A = +25$ °C. Specifications over the operating temperature range are guaranteed by design and characterization.

- Note 3: Limits are guaranteed by design and not production tested.

- Note 4: The idle-mode current threshold is the transition point between fixed-frequency PWM operation and idle-mode operation.

The specification is given in terms of output load current for an inductor value of 3.3µH. For the step-up mode, the idle-mode transition varies with input to the output-voltage ratios.

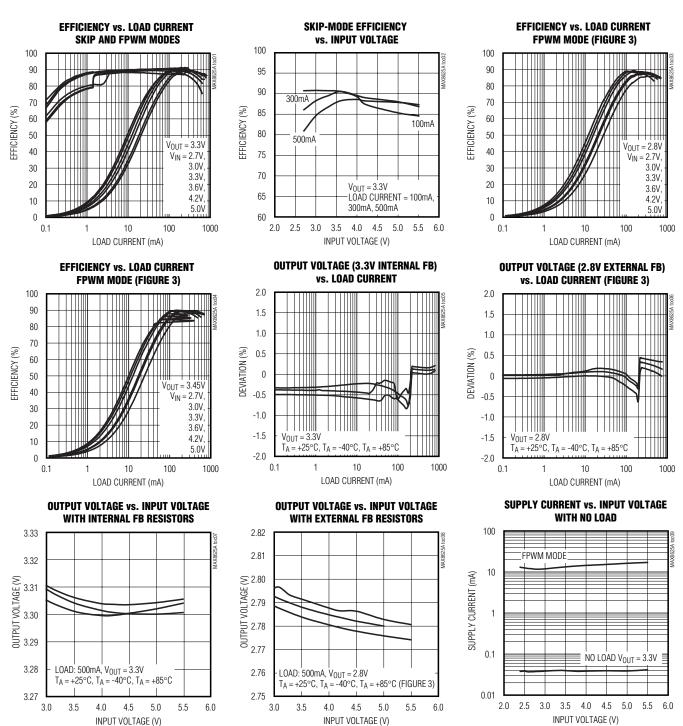

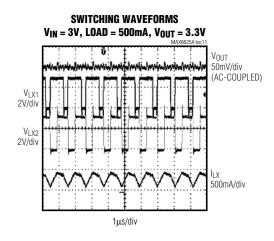

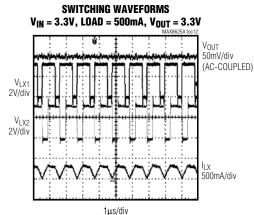

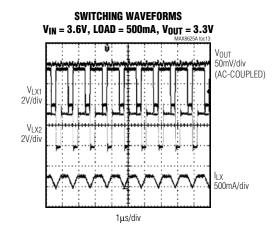

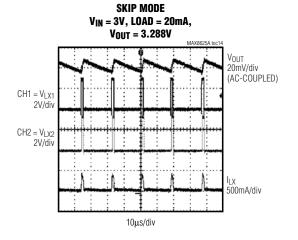

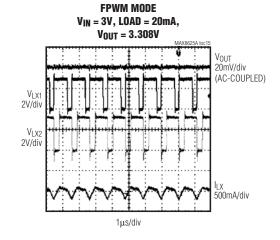

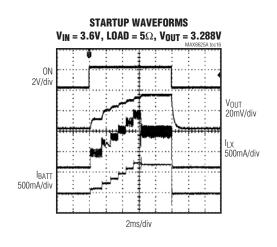

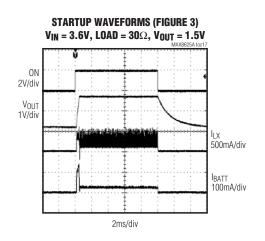

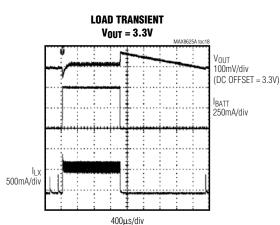

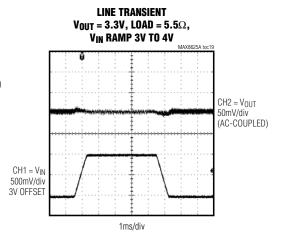

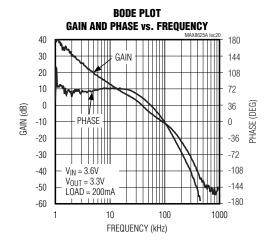

### **Typical Operating Characteristics**

## Typical Operating Characteristics (continued)

### Typical Operating Characteristics (continued)

### Typical Operating Characteristics (continued)

### **Pin Description**

| PIN                                             | NAME | FUNCTION                                                                                                                                                                                                                                                       |  |  |  |  |

|-------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1, 2                                            | LX1  | Inductor Connection 1. Connect the inductor between LX1 and LX2. Both LX1 pins must be connected together externally. LX1 is internally connected to GND during shutdown.                                                                                      |  |  |  |  |

| 3, 4                                            | LX2  | Inductor Connection 2. Connect the inductor between LX1 and LX2. Both LX2 pins must be connected together externally. LX2 is internally connected to GND during shutdown.                                                                                      |  |  |  |  |

| 5                                               | ON   | Enable Input. Connect ON to the input or drive high to enable the IC. Drive ON low to disable the IC.                                                                                                                                                          |  |  |  |  |

| 6                                               | SKIP | Mode Select Input. Connect SKIP to GND to enable skip mode. This mode provides the best overall efficiency curve.  Connect SKIP to IN to enable forced-PWM mode. This mode provides the lowest noise, but reduces light-load efficiency compared to skip mode. |  |  |  |  |

| 7                                               | FB   | Feedback Input. Connect to ground to set the fixed 3.3V output. Connect FB to the center tap of an external resistor-divider from the output to GND to set the output voltage to a different value. VFB regulates to 1.25V.                                    |  |  |  |  |

| 8                                               | REF  | Reference Output. Bypass REF to GND with a 0.1µF ceramic capacitor. V <sub>REF</sub> is 1.25V and is internally pulled to GND during shutdown.                                                                                                                 |  |  |  |  |

| 9, 10                                           | OUT  | Power Output. Bypass OUT to GND with two 22µF ceramic capacitors. Both OUT pins must be connected together externally.                                                                                                                                         |  |  |  |  |

| 11, 12                                          | GND  | Ground. Connect the exposed pad and GND directly under the IC.                                                                                                                                                                                                 |  |  |  |  |

| 1 1.3 14 1 IN 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |      | Power-Supply Input. Bypass IN to GND with two 22µF ceramic capacitors. Connect IN to a 2.5V to 5.5V supply. Both IN pins must be connected together externally.                                                                                                |  |  |  |  |

|                                                 | EP   | Exposed Pad. Connect to GND directly under the IC. Connect to a large ground plane for increased thermal performance.                                                                                                                                          |  |  |  |  |

### **Detailed Description**

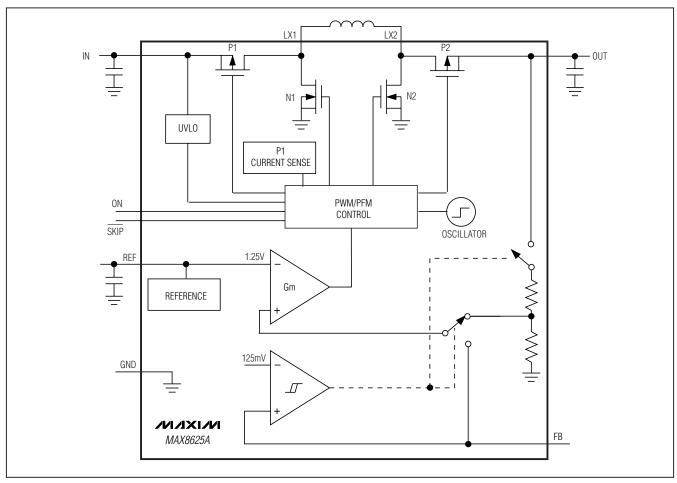

The MAX8625A step-up/down architecture employs a true H-bridge topology that combines a boost converter and a buck converter topology using a single inductor and output capacitor (Figure 1). The MAX8625A utilizes a pulse-width modulated (PWM), current-mode control scheme and operates at a 1MHz fixed frequency to minimize external component size. A proprietary H-bridge design eliminates mode changes when transitioning from buck to boost operation. This control scheme provides very low output ripple using a much smaller inductor than a conventional H-bridge, while avoiding glitches that are commonly seen during mode transitions with competing devices.

The MAX8625A switches at an internally set frequency of 1MHz, allowing for tiny external components. Internal compensation further reduces the external component count in cost- and space-sensitive applications. The MAX8625A is optimized for use in HDDs, DSCs, and other devices requiring low-quiescent current for optimal light-load efficiency and maximum battery life.

### **Control Scheme**

The MAX8625A basic noninverting step-up/down converter operates with four internal switches. The control logic determines which two internal MOSFETs operate to maintain the regulated output voltage. Unlike a traditional H-bridge, the MAX8625A utilizes smaller peakinductor currents, thus improving efficiency and lowering input/output ripple.

The MAX8625A uses three operating phases during each switching cycle. In phase 1 (fast-charge), the inductor current ramps up with a di/dt of V<sub>IN</sub>/L. In phase 2 (slow charge/discharge), the current either ramps up or down depending on the difference between the input voltage and the output voltage (V<sub>IN</sub> - V<sub>OUT</sub>)/L. In phase 3 (discharge), the inductor current discharges at a rate of V<sub>OUT</sub>/L through MOSFETs P2 and N1 (see Figure 1). An additional fourth phase (phase 4: hold) is entered when the inductor current falls to zero during phase 3. This fourth phase is only used during skip operation.

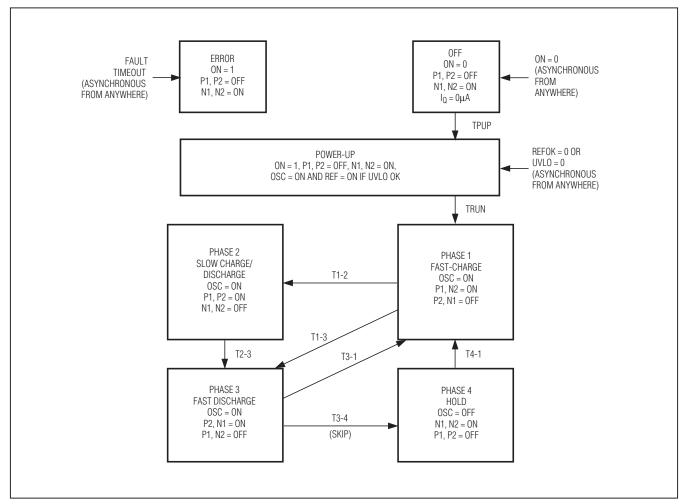

The state machine (Figure 2) decides which phase to use and when to switch phases. The converter goes through the first three phases in the same order at all

8 \_\_\_\_\_\_ NIXIM

Figure 1. Simplified Block Diagram

times. This reduces the ripple and removes any mode transitions from boost-only or buck-only to hybrid modes as seen in competing H-bridge converters.

The time spent in each phase is set by a PWM controller, using timers and/or peak-current regulation on a cycle-by-cycle basis. The heart of the PWM control block is a comparator that compares the output voltage-error feedback signal and the sum of the current-sense and slope compensation signals. The current-mode control logic regulates the inductor current as a function of the output error voltage signal. The current-sense signal is monitored across the MOSFETs (P1, N1, and N2). A fixed time delay of approximately 30ns occurs between turning the P1 and N2 MOSFETs off, and turning the N1 and P2 MOSFETs on. This dead time prevents efficiency loss by preventing "shoot-through" current.

#### Step-Down Operation (VIN > VOUT)

During medium and heavy loads and V<sub>IN</sub> > V<sub>OUT</sub>, MOSFETs P1 and N2 turn on to begin phase 1 at the clock edge and ramp up the inductor current. The duration of phase 1 is set by an internal timer. During phase 2, N2 turns off, and P2 turns on to further ramp up inductor current and also transfer charge to the output. This slow charge phase is terminated on a clock edge and P1 is turned off. The converter now enters the fast discharge phase (phase 3). In phase 3, N1 turns on and the inductor current ramps down to the valley current-regulation point set by the error signal. At the end of phase 3, both P2 and N1 turn off and another phase 1 is initiated and the cycle repeats.

With SKIP asserted low, during light loads when inductor current falls to zero in phase 3, the converter switches to phase 4 to reduce power consumption and avoid

Figure 2. State Diagram

shuttling current in and out of the output capacitor. If  $\overline{SKIP}$  is asserted high for forced-PWM mode, phase 4 is not entered and current shuttling is allowed (and is necessary to maintain the PWM operation frequency when no load is present).

#### Step-Up Operation (V<sub>IN</sub> < V<sub>OUT</sub>)

During medium and heavy loads when  $V_{IN} < V_{OUT}$ , MOSFETs P1 and N2 turn on at the clock edge to ramp up the inductor current. Phase 1 terminates when the inductor current reaches the peak target current set by the PWM comparator and N2 turns off. This is followed by a slow-discharge phase (phase 2) instead of a charge phase (since  $V_{IN}$  is less than  $V_{OUT}$ ) when P2 turns on. The slow-discharge phase terminates on a clock edge. The converter now enters the fast-discharge phase (phase 3). During phase 3, P1 turns off

and N1 turns on. At the end of the minimum time, both P2 and N1 turn off and the cycle repeats.

If  $\overline{\text{SKIP}}$  is asserted low, during light loads when inductor current falls to zero in phase 3, the converter switches to phase 4 (hold) to reduce power consumption and avoid shuttling current in and out of the output. If  $\overline{\text{SKIP}}$  is high to assert forced-PWM mode, the converter never enters phase 4 and allows negative inductor current.

## Step-Up/Down Transition-Zone Operation (VIN = VOUT)

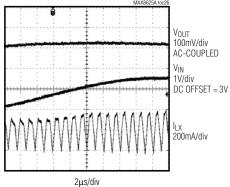

When  $V_{\text{IN}} = V_{\text{OUT}}$ , the converter still goes through the three phases for moderate to heavy loads. However, the maximum time is now spent in phase 2 where inductor current di/dt is almost zero, since it is proportional to  $(V_{\text{IN}} - V_{\text{OUT}})$ . This eliminates transition glitches

or oscillation between the boost and buck modes as seen in other step-up/down converters. See the switching waveforms for each of the three modes and transition waveforms in the *Typical Operating Characteristics* section.

#### **Forced-PWM Mode**

Drive SKIP high to operate the MAX8625A in forced-PWM mode. In this mode, the IC operates at a constant 1MHz switching frequency with no pulse skipping. This scheme is desirable in noise-sensitive applications because the output ripple is minimized and has a predictable noise spectrum. Forced PWM consumes higher supply current at light loads due to constant switching.

### **Skip Mode**

Drive  $\overline{SKIP}$  low to operate the MAX8625A in skip mode to improve light-load efficiency. In skip mode, the IC switches only as necessary to maintain the output at light loads, but still operates with fixed-frequency PWM at medium and heavy loads. This maximizes light-load efficiency and reduces the input quiescent current to  $37\mu A$  (typ).

Do not dynamically transition between skip and FPWM. The MAX8625A is not designed for dynamic transitions between FPWM and skip modes. Spikes of negative inductor current are possible when making these types of dynamic transitions. The magnitude of the spike depends on the load and output capacitance. The MAX8625A has no protection against these types of negative current spikes.

#### **Load Regulation and Transient Response**

During a load transient, the output voltage instantly changes due to the ESR of the output capacitors by an amount equal to their ESR times the change in load current ( $\Delta V_{OUT} = R_{ESR} \times \Delta I_{LOAD}$ ). The output voltage then deviates further based on the speed at which the loop compensates for the load step. Increasing the output capacitance reduces the output-voltage droop. See the *Capacitor Selection* section. The typical application circuit limits the output transient droop to less than 3%. See the *Typical Operating Characteristics* section.

#### Soft-Start

Soft-start prevents input inrush current during startup. Internal soft-start circuitry ramps the peak inductor current with an internal DAC in 8ms. Once the output reaches regulation, the current limit immediately jumps to the maximum threshold. This allows full load capability as soon as regulation is reached, even if it occurs before the 8ms soft-start time is complete.

When using the MAX8625A at low input voltages (close to UVLO and < 3V), it is recommended that the ON pin should not be tied to the BATT or supply voltage node directly. The ON pin should be held low for > 1ms after power to the MAX8625A is applied before it is driven high for normal operation.

#### Shutdown

Drive ON low to place the MAX8625A in shutdown mode and reduce supply current to less than  $1\mu A$ . During shutdown, OUT is disconnected from IN, and LX1 and LX2 are connected to GND. Drive ON high for normal operation.

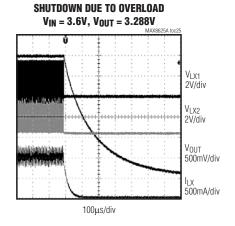

#### **Fault and Thermal Shutdown**

The MAX8625A contains current-limit and thermal shutdown circuitry to protect the IC from fault conditions. When the inductor current exceeds the current limit (2A for the MAX8625A), the converter immediately enters phase 3 and an internal 100ms timer starts. The converter continues to commutate through the three phases, spending most of its time in phase 1 and phase 3. If the overcurrent event continues and the output is out of regulation for the duration of the 100ms timer, the IC enters shutdown mode and the output latches off. ON must then be toggled to clear the fault. If the overload is removed before the 100ms timer expires, the timer is cleared and the converter resumes normal operation.

The thermal-shutdown circuitry disables the IC switching if the die temperature exceeds +165°C. The IC begins soft-start once the die temperature cools by 15°C.

### **Applications Information**

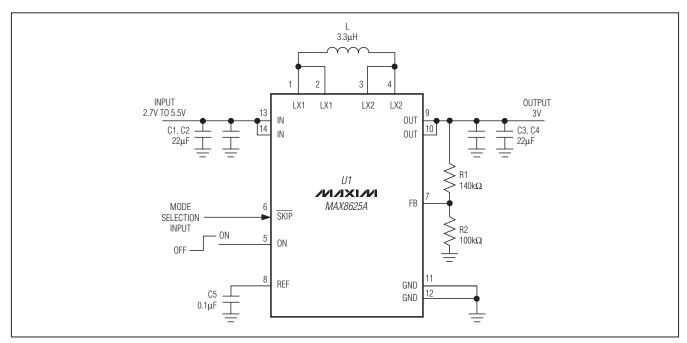

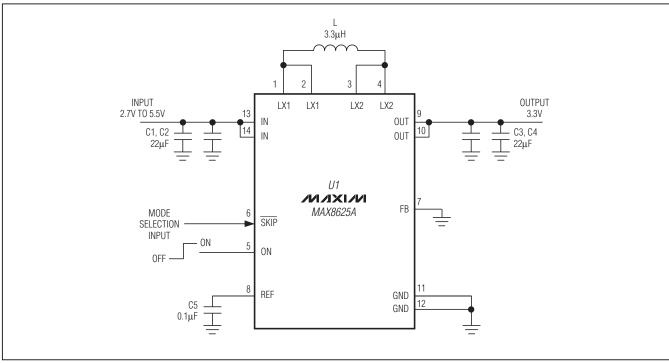

### Selecting the Output Voltage

The MAX8625A output is nominally fixed at 3.3V. Connect FB to GND to select the internally fixed-output voltage. For an adjustable output voltage, connect FB to the center tap of an external resistor-divider connected from the output to GND (R1 and R2 in Figure 3). Select  $100\text{k}\Omega$  for R2 and calculate R1 using the following equation:

$$R1 = 100k\Omega \times \left(\frac{V_{OUT}}{V_{FB}} - 1\right)$$

where  $V_{FB} = 1.25V$  and  $V_{OUT}$  is the desired output regulation voltage.  $V_{OUT}$  must be between 1.25V and 4V. Note that the minimum output voltage is limited by the minimum duty cycle.  $V_{OUT}$  cannot be below 1.25V.

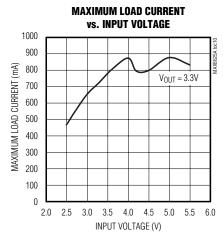

#### **Calculating Maximum Output Current**

The maximum output current provided by the MAX8625A circuit depends on the inductor value, switching frequency, efficiency, and input/output voltage.

See the *Typical Operating Characteristics* section for the Maximum Load Current vs. Input Voltage graph.

#### **Capacitor Selection**

The input and output ripple currents are both discontinuous in this topology. Therefore, select at least two

22μF ceramic capacitors at the input. Select two 22μF ceramic output capacitors. For best stability over a wide temperature range, use X5R or better dielectric.

#### **Inductor Selection**

The recommended inductance range for the MAX8625A is  $3.3\mu H$  to  $4.7\mu H$ . Larger values of L give a smaller ripple, while smaller L values provide a better transient response. This is because, for boost and step-up/down topologies, the crossover frequency is inversely proportional to the value of L for a given load and input voltage. The MAX8625A is internally compensated, and therefore, the choice of power components for stable operation is bounded. A  $3.3\mu H$  inductor with 2A rating is recommended for the 3.3V fixed output with 0.8A load.

### **PCB Layout and Routing**

Good PCB layout is important to achieve optimal performance from the MAX8625A. Poor design can cause excessive conducted and/or radiated noise. Conductors carrying discontinuous currents and any high-current path should be made as short and wide as possible. Keep the feedback network (R1 and R2) very close to the IC, preferably within 0.2 inches of the FB and GND pins. Nodes with high dv/dt (switching nodes) should be kept as small as possible and routed away from FB. Connect the input and output capacitors as close as possible to the IC. Refer to the MAX8625A evaluation kit for a PCB layout example.

Figure 3. Typical Application Circuit (Adjustable Output)

Figure 4. Typical Application Circuit (Fixed 3.3V Output)

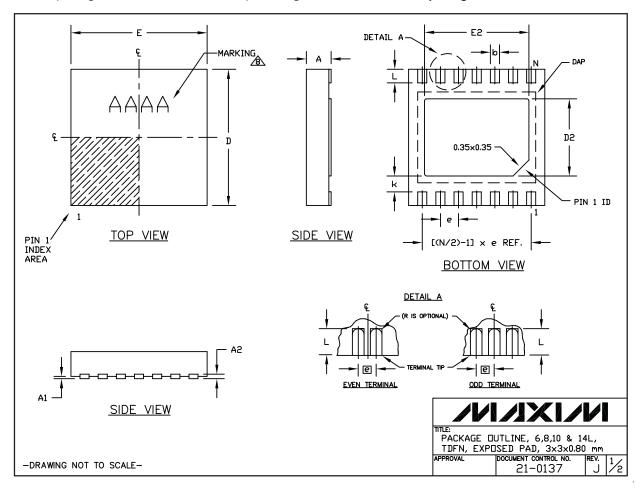

Package Information

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO. |  |

|--------------|--------------|--------------|--|

| 14 TDFN-EP   | T1433-2      | 21-0137      |  |

**Chip Information**

PROCESS: BICMOS

### Package Information (continued)

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

### Package Information (continued)

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

| COMMON DIMENSIONS |           |                      |  |  |  |

|-------------------|-----------|----------------------|--|--|--|

| SYMBOL            | MIN.      | MAX.                 |  |  |  |

| Α                 | 0.70      | 0.80                 |  |  |  |

| D                 | 2.90      | 3.10<br>3.10<br>0.05 |  |  |  |

| Е                 | 2.90      |                      |  |  |  |

| A1                | 0.00      |                      |  |  |  |

| L                 | 0.20      | 0.40                 |  |  |  |

| k                 | 0.25 MIN. |                      |  |  |  |

| A2                | 0.20      | REF.                 |  |  |  |

| PACKAGE VARIATIONS |    |           |           |          |                |           |               |  |

|--------------------|----|-----------|-----------|----------|----------------|-----------|---------------|--|

| PKG. CODE          | N  | D2        | E2        | е        | JEDEC SPEC     | b         | [(N/2)-1] x e |  |

| T633-2             | 6  | 1.50±0.10 | 2.30±0.10 | 0.95 BSC | MO229 / WEEA   | 0.40±0.05 | 1.90 REF      |  |

| T833-2             | 8  | 1.50±0.10 | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      |  |

| T833-3             | 8  | 1.50±0.10 | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      |  |

| T1033-1            | 10 | 1.50±0.10 | 2.30±0.10 | 0.50 BSC | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      |  |

| T1033MK-1          | 10 | 1.50±0.10 | 2.30±0.10 | 0.50 BSC | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      |  |

| T1033-2            | 10 | 1.50±0.10 | 2.30±0.10 | 0.50 BSC | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      |  |

| T1433-1            | 14 | 1.70±0.10 | 2.30±0.10 | 0.40 BSC |                | 0.20±0.05 | 2.40 REF      |  |

| T1433-2            | 14 | 1.70±0.10 | 2.30±0.10 | 0.40 BSC |                | 0.20±0.05 | 2.40 REF      |  |

| T1433-3F           | 14 | 1.70±0.10 | 2.30±0.10 | 0.40 BSC |                | 0.20±0.05 | 2.40 REF      |  |

- 1. ALL DIMENSIONS ARE IN mm. ANGLES IN DEGREES.

- COPLANARITY SHALL NOT EXCEED 0.08 mm.

WARPAGE SHALL NOT EXCEED 0.10 mm.

- 4. PACKAGE LENGTH/PACKAGE WIDTH ARE CONSIDERED AS SPECIAL CHARACTERISTIC(S).

- 5. DRAWING CONFORMS TO JEDEC MO229, EXCEPT DIMENSIONS "D2" AND "E2", AND T1433-1 & T1433-2.

- 6. "N" IS THE TOTAL NUMBER OF LEADS.

- 7. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- 9. ALL DIMENSIONS APPLY TO BOTH LEADED (-) AND PEFREE (+) PKG. CODES.

21-0137

TILE:

PACKAGE DUTLINE, 6,8,10 & 14L,

TDFN, EXPOSED PAD, 3x3x0.80 mm

PPROVAL | DOCUMENT CONTROL NO. | REV.

-DRAWING NOT TO SCALE-