#### **General Description**

The MAX9155 is a low-voltage differential signaling (LVDS) repeater, which accepts a single LVDS input and duplicates the signal at a single LVDS output. Its low-jitter, low-noise performance makes it ideal for buffering LVDS signals sent over long distances or noisy environments, such as cables and backplanes.

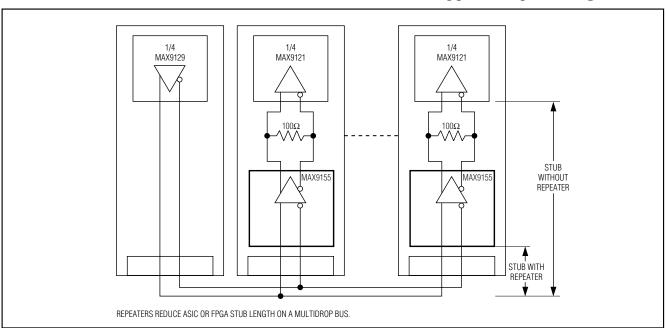

The MAX9155's tiny size makes it especially suitable for minimizing stub lengths in multidrop backplane applications. The SC70 package (half the size of a SOT23) allows the MAX9155 to be placed close to the connector, thereby minimizing stub lengths and reflections on the bus. The point-to-point connection between the MAX9155 output and the destination IC, such as an FPGA or ASIC, allows the destination IC to be located at greater distances from the bus connector.

Ultra-low, 23psp-p added deterministic jitter and 0.6ps<sub>RMS</sub> added random jitter ensure reliable communication in high-speed links that are highly sensitive to timing errors, especially those incorporating clock-anddata recovery, PLLs, serializers, or deserializers. The MAX9155's switching performance guarantees a 200Mbps data rate, but minimizes radiated noise by guaranteeing 0.5ns minimum output transition time.

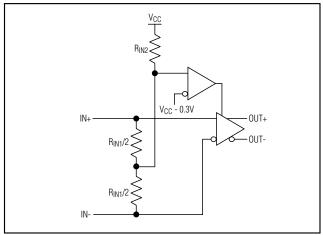

The MAX9155 has fail-safe circuitry that sets the output high for undriven open, short, or terminated inputs.

The MAX9155 operates from a single +3.3V supply and consumes only 10mA over a -40°C to +85°C temperature range. Refer to the MAX9129 data sheet for a guad bus LVDS driver, and to the MAX9156 data sheet for a low-jitter, low-noise LVPECL-to-LVDS level translator in an SC70 package.

#### Features

- ♦ Tiny SC70 Package

- ♦ Ultra-Low Jitter 23psp-p Added Deterministic Jitter (2<sup>23</sup>-1 PRBS)

- 0.6ps<sub>RMS</sub> Added Random Jitter

- ♦ 0.5ns (min) Transition Time Minimizes Radiated **Noise**

- ♦ 200Mbps Guaranteed Data Rate

- ◆ Fail-Safe Circuit Sets Output High for Undriven Inputs (Open, Terminated, or Shorted)

- ♦ Low 10mA Supply Current

- ♦ Low 6mA Supply Current in Fail-Safe

- ♦ Conforms to ANSI/EIA/TIA-644 LVDS Standard

- ♦ High-Impedance Inputs and Outputs in **Power-Down Mode**

#### **Ordering Information**

Pin Configuration

| PART         | TEMP. RANGE    | PIN-<br>PACKAGE | TOP<br>MARK |  |

|--------------|----------------|-----------------|-------------|--|

| MAX9155EXT-T | -40°C to +85°C | 6 SC70-6        | ABC         |  |

## **Applications**

Cellular Phone Base Stations

**DSLAMs**

Digital Cross-Connects

Add/Drop Muxes

Network Switches/Routers

Multidrop Buses

Cable Repeaters

Typical Operating Circuit appears at end of data sheet.

## TOP VIEW MAXIM OUT-6 OUT+ 5 V<sub>CC</sub> GND 2 IN- 3 IN+ SC70

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND                        | Storage Temperature Range65°C to +150°C  Junction Temperature+150°C  Operating Temperature Range40°C to +85°C  ESD Protection  Human Body Model, IN+, IN-, OUT+, OUT±8kV  Lead Temperature (soldering, 10s)+300°C |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6-Pin SC70 (derate 3.1mW/°C above +70°C)245mW | Lead Temperature (soldering, 10s)+300°C                                                                                                                                                                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, R_L = 100 \Omega \pm 1\%, |V_{ID}| = 0.05 \text{V to } 1.2 \text{V}, V_{CM} = |V_{ID}|/2| \text{ to } 2.4 \text{V} - |V_{ID}|/2|, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.3 \text{V}, T_A = +25 ^{\circ}\text{C}.)$  (Notes 1, 2)

| PARAMETER                                                        | SYMBOL                              |                                           | CONDITIONS                     | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------------------------------|-------------------------------------|-------------------------------------------|--------------------------------|-------|-------|-------|-------|

| LVDS INPUT                                                       |                                     |                                           |                                |       |       |       |       |

| Differential Input High Threshold                                | V <sub>TH</sub>                     |                                           |                                |       | 7     | 50    | mV    |

| Differential Input Low Threshold                                 | V <sub>TL</sub>                     |                                           |                                | -50   | -7    |       | mV    |

| Input Current                                                    | las las                             | 0.05V ≤  V <sub>ID</sub>   ≤ 0.6V         |                                | -15   | -2.5  | 15    | μΑ    |

| input Current                                                    | I <sub>IN+</sub> , I <sub>IN-</sub> | 0.6V<  V <sub>ID</sub>                    | -20                            | -3.5  | 20    |       |       |

| Power-Off Input Current                                          | I <sub>IN+</sub> , I <sub>IN-</sub> | $0.05V \le  V_{ID}  \le 0.6V, V_{CC} = 0$ |                                | -15   | 1.3   | 15    | μΑ    |

| 1 ower-on input current                                          |                                     | $0.6V <  V_{ D}  \le 1.2V, V_{CC} = 0$    |                                | -20   | 2.6   | 20    |       |

| Input Resistor 1                                                 | R <sub>IN1</sub>                    | $V_{CC} = +3.6$                           | SV or 0, Figure 1              | 67    | 232   |       | kΩ    |

| Input Resistor 2                                                 | R <sub>IN2</sub>                    | $V_{CC} = +3.6$                           | 6V or 0, Figure 1              | 267   | 1174  |       | kΩ    |

| LVDS OUTPUT                                                      |                                     |                                           |                                |       |       |       |       |

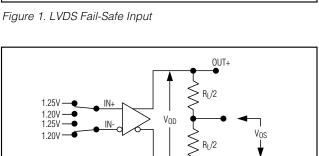

| Differential Output Voltage                                      | V <sub>OD</sub>                     | Figure 2                                  |                                | 250   | 360   | 450   | mV    |

| Change in V <sub>OD</sub> Between<br>Complementary Output States | ΔV <sub>OD</sub>                    | Figure 2                                  |                                |       | 0.008 | 25    | mV    |

| Offset (Common-Mode) Voltage                                     | Vos                                 | Figure 2                                  |                                | 1.125 | 1.25  | 1.375 | V     |

| Change in V <sub>OS</sub> for<br>Complementary Output States     | ΔV <sub>OS</sub>                    | Figure 2                                  |                                |       | 0.005 | 25    | mV    |

| Output High Voltage                                              | Voh                                 |                                           |                                |       | 1.44  | 1.6   | V     |

| Output Low Voltage                                               | V <sub>OL</sub>                     |                                           |                                | 0.9   | 1.08  |       | V     |

| Fail-Safe Differential Output<br>Voltage                         | V <sub>OD+</sub>                    | IN+, IN- sh<br>terminated                 | orted, open, or parallel       | +250  | +360  | +450  | mV    |

| Power-Off Output Leakage                                         | 10                                  | 1/0                                       | OUT+ = 3.6V, other output open | -10   | 0.02  | 10    |       |

| Current                                                          | IUOFF                               | IO <sub>OFF</sub> V <sub>CC</sub> = 0     | OUT- = 3.6V, other output open | -10   | 0.02  | 10    | μΑ    |

| Differential Output Resistance                                   | RODIFF                              | V <sub>CC</sub> = +3.6V or 0              |                                | 100   | 260   | 400   | Ω     |

|                                                                  | I <sub>SC</sub>                     | V <sub>ID</sub> = +50mV, OUT+ = GND       |                                |       | -5    | -15   | mA    |

| Output Short Current                                             |                                     | V <sub>ID</sub> = -50mV, OUT- = GND       |                                |       | -5    | -15   |       |

| POWER SUPPLY                                                     |                                     |                                           |                                |       |       |       |       |

| Supply Current                                                   | Icc                                 | Output load                               | ded                            |       | 10    | 15    | mA    |

| Supply Current in Fail-Safe                                      | ICCF                                | Output load                               | ded, input undriven            |       | 6     | 8     | mA    |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0V \text{ to } +3.6V, \ R_L = 100\Omega \pm 1\%, \ C_L = 10p\text{F}, \ |V_{ID}| = 0.15V \text{ to } 1.2V, \ V_{CM} = |V_{ID}| / 2| \text{ to } 2.4V - |V_{ID}| / 2|, \ T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \ \text{unless otherwise noted}.$  Typical values are at  $V_{CC} = +3.3V, \ T_A = +25^{\circ}\text{C}.$ ) (Notes 3, 4, 5) (Figures 3, 4)

| PARAMETER                                     | SYMBOL            | CONDITIONS                                   | MIN | TYP  | MAX | UNITS             |

|-----------------------------------------------|-------------------|----------------------------------------------|-----|------|-----|-------------------|

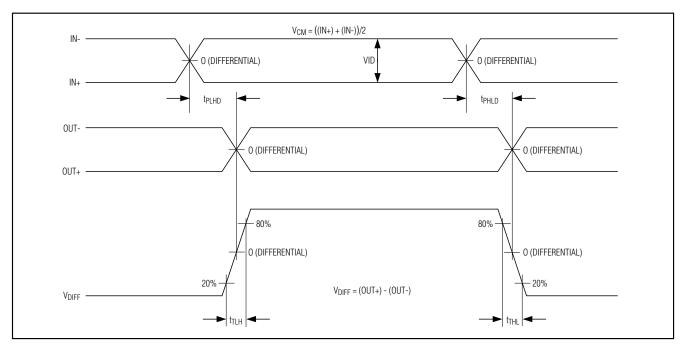

| Differential Propagation Delay High to Low    | <sup>t</sup> PHLD |                                              | 1.3 | 2.0  | 2.8 | ns                |

| Differential Propagation Delay Low to<br>High | t <sub>PLHD</sub> |                                              | 1.3 | 2.0  | 2.8 | ns                |

| Added Deterministic Jitter (Notes 6, 11)      | t <sub>D</sub> J  | 200Mbps 2 <sup>23</sup> -1 PRBS data pattern |     | 23   | 100 | ps <sub>p-p</sub> |

| Added Random Jitter (Notes 7, 11)             | t <sub>RJ</sub>   | $f_{IN} = 100MHz$                            |     | 0.6  | 2.9 | psrms             |

| Differential Part-to-Part Skew (Note 8)       | tSKPP1            |                                              |     | 0.17 | 0.6 | ns                |

| Differential Part-to-Part Skew (Note 9)       | tSKPP2            |                                              |     |      | 1.5 | ns                |

| Switching Supply Current                      | Iccsw             |                                              |     | 11.3 | 18  | mA                |

| Rise Time                                     | tTLH              |                                              | 0.5 | 0.66 | 1.0 | ns                |

| Fall Time                                     | t <sub>THL</sub>  |                                              | 0.5 | 0.64 | 1.0 | ns                |

| Input Frequency (Note 10)                     | f <sub>MAX</sub>  |                                              | 100 |      | •   | MHz               |

- Note 1: All devices are 100% tested at  $T_A = +25^{\circ}C$ . Limits over temperature are guaranteed by design and characterization.

- **Note 2:** Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground except V<sub>TH</sub>, V<sub>TL</sub>, V<sub>OD</sub>, and ΔV<sub>OD</sub>.

- Note 3: Guaranteed by design and characterization.

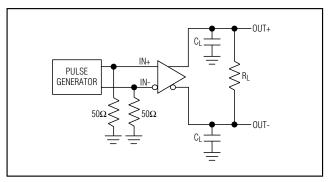

- **Note 4:** Signal generator output (unless otherwise noted): frequency = 100MHz, 50% duty cycle,  $R_O = 50\Omega$ ,  $t_R = 1.5$ ns, and  $t_F = 1.5$ ns (0% to 100%).

- Note 5: C<sub>L</sub> includes scope probe and test jig capacitance.

- **Note 6:** Signal generator output for  $t_{DJ}$ :  $V_{OD} = 150$ mV,  $V_{OS} = 1.2$ V,  $t_{DJ}$  includes pulse (duty-cycle) skew.

- **Note 7:** Signal generator output for  $t_{RJ}$ :  $V_{OD} = 150 \text{mV}$ ,  $V_{OS} = 1.2 \text{V}$ .

- **Note 8:** tskPP1 is the magnitude difference of any differential propagation delays between devices operating over rated conditions at the same supply voltage, input common-mode voltage, and ambient temperature.

- Note 9: tskpp2 is the magnitude difference of any differential propagation delays between devices operating over rated conditions.

- Note 10: Device meets VOD DC specification and AC specifications while operating at f<sub>MAX</sub>.

- Note 11: Jitter added to the input signal.

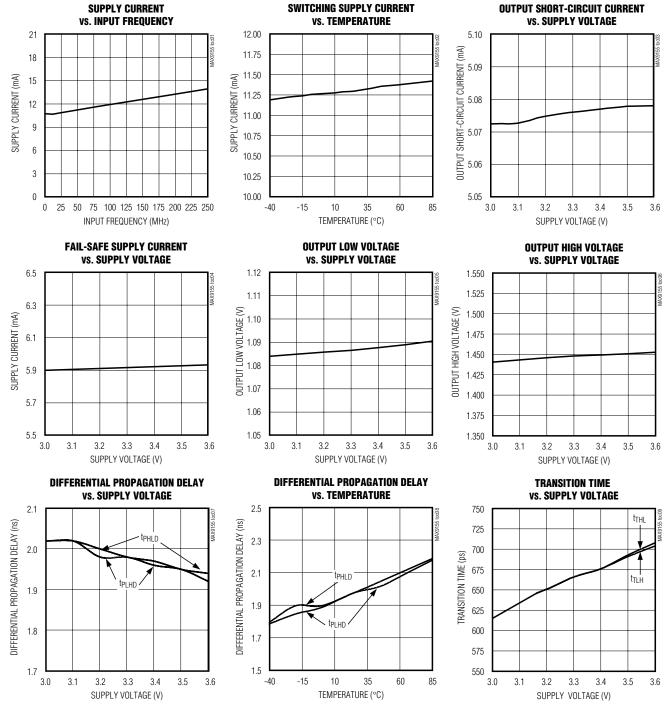

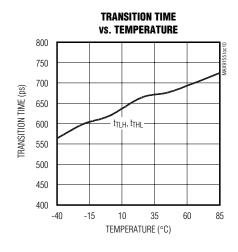

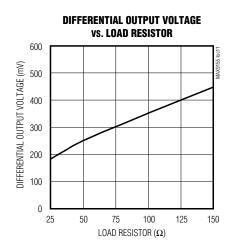

### **Typical Operating Characteristics**

$(V_{CC} = +3.3V, R_L = 100\Omega \pm 1\%, C_L = 10pF, |V_{ID}| = 0.2V, V_{CM} = 1.2V, T_A = +25^{\circ}C$ , unless otherwise noted. Signal generator output: frequency = 100MHz, 50% duty cycle,  $R_O = 50\Omega$ ,  $t_R = 1.5$ ns, and  $t_F = 1.5$ ns (0% to 100%), unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(V_{CC} = +3.3V, R_L = 100\Omega \pm 1\%, C_L = 10pF, |V_{ID}| = 0.2V, V_{CM} = 1.2V, T_A = +25$ °C, unless otherwise noted. Signal generator output: frequency = 100MHz, 50% duty cycle,  $R_O = 50\Omega$ ,  $t_R = 1.5$ ns, and  $t_F = 1.5$ ns (0% to 100%), unless otherwise noted.)

#### Pin Description

| PIN | NAME | FUNCTION                                                                   |  |

|-----|------|----------------------------------------------------------------------------|--|

| 1   | OUT- | Inverting LVDS Output                                                      |  |

| 2   | GND  | Ground                                                                     |  |

| 3   | IN-  | Inverting LVDS Input                                                       |  |

| 4   | IN+  | Noninverting LVDS Input                                                    |  |

| 5   | Vcc  | Power Supply. Bypass V <sub>CC</sub> to GND with 0.01µF ceramic capacitor. |  |

| 6   | OUT+ | Noninverting LVDS Output                                                   |  |

Table 1. Function Table for LVDS Fail-Safe Input (Figure 2)

| INPUT, V <sub>ID</sub>                              | OUTPUT, V <sub>OD</sub> |

|-----------------------------------------------------|-------------------------|

| ≥ 50mV                                              | High                    |

| ≤ -50mV                                             | Low                     |

| $50\text{mV} > \text{V}_{\text{ID}} > -50\text{mV}$ | Indeterminate           |

| Undriven open, short, or terminated                 | High                    |

**Note:**  $V_{ID} = (IN+ - IN-), \ V_{OD} = (OUT+ - OUT-)$   $High = 450mV \ge V_{OD} \ge 250mV$  $Low = -250mV \ge V_{OD} \ge -450mV$

### Detailed Description

The LVDS interface standard is a signaling method intended for point-to-point communication over a controlled-impedance medium, as defined by the ANSI/TIA/EIA-644 and IEEE 1596.3 standards. The LVDS standard uses a lower voltage swing than other common communication standards, achieving higher data rates with reduced power consumption while reducing EMI emissions and system susceptibility to noise.

The MAX9155 is a 200Mbps LVDS repeater intended for high-speed, point-to-point, low-power applications. The MAX9155 accepts an LVDS input and reproduces an LVDS signal at the output. This device is capable of detecting differential signals as low as 50mV and as high as 1.2V within a 0 to 2.4V input voltage range. The LVDS standard specifies an input voltage range of 0 to 2.4V referenced to ground.

#### Fail-Safe

Fail-safe is a feature that puts the output in a known logic state (differential high) under certain fault conditions. The MAX9155 outputs are differential high when the inputs are undriven and open, terminated, or shorted (Table 1).

### Applications Information

#### Supply Bypassing

Bypass VCC with a high-frequency surface-mount ceramic  $0.01\mu F$  capacitor as close to the device as possible.

#### **Differential Traces**

Input and output trace characteristics affect the performance of the MAX9155. Use controlled-impedance differential traces. Ensure that noise couples as common mode by running the traces within a differential pair close together.

Maintain the distance within a differential pair to avoid discontinuities in differential impedance. Avoid 90° turns and minimize the number of vias to further prevent impedance discontinuities.

#### **Cables and Connectors**

The LVDS standards define signal levels for interconnect with a differential characteristic impedance and termination of  $100\Omega$ . Interconnects with a characteristic impedance and termination of  $90\Omega$  to  $132\Omega$  impedance are allowed, but produce different signal levels (see *Termination*).

Use cables and connectors that have matched differential impedance to minimize impedance discontinuities.

Avoid the use of unbalanced cables, such as ribbon or coaxial cable. Balanced cables, such as twisted pair, offer superior signal quality and tend to generate less EMI due to canceling effects. Balanced cables tend to pick up noise as common mode, which is rejected by the LVDS receiver.

#### **Termination**

For point-to-point links, the termination resistor should be located at the LVDS receiver input and match the differential characteristic impedance of the transmission line.

For a multidrop bus driven at one end, terminate at the other end of the bus with a resistor that matches the loaded differential characteristic impedance of the bus. For a multidrop bus driven from a point other than the end, terminate each end of the bus with a resistor that matches the loaded differential characteristic impedance of the bus. When terminating at both ends, or for a large number of drops, a bus LVDS (BLVDS) driver is needed to drive the bus to LVDS signal levels. The MAX9155 is not intended to drive double-terminated multidrop buses to LVDS levels.

The differential output voltage level depends upon the differential characteristic impedance of the interconnect and the value of the termination resistance. The MAX9155 is guaranteed to produce LVDS output levels into  $100\Omega$ . With the typical 3.6mA output current, the MAX9155 produces an output voltage of 360mV when driving a  $100\Omega$  transmission line terminated with a  $100\Omega$  termination resistor (3.6mA x  $100\Omega$  = 360mV). For typical output levels with different loads, see the Differential Output Voltage vs. Load Resistor typical operating curve.

\_Chip Information

TRANSISTOR COUNT: 401

PROCESS: CMOS

## **Test Circuit and Timing Diagrams**

Figure 2. DC Load Test Circuit

Figure 3. Transition Time and Propagation Delay Test Circuit

## Test Circuit and Timing Diagrams (continued)

Figure 4. Transition Time and Propagation Delay Timing Diagram

## Typical Operating Circuit