### **General Description**

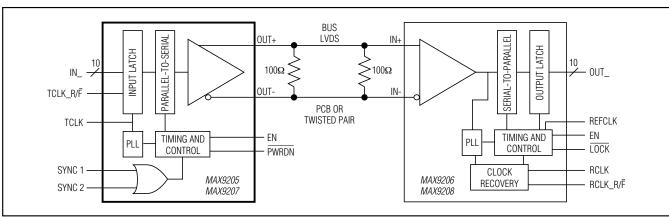

The MAX9205/MAX9207 serializers transform 10-bitwide parallel LVCMOS/LVTTL data into a serial highspeed bus low-voltage differential signaling (LVDS) data stream. The serializers typically pair with deserializers like the MAX9206/MAX9208, which receive the serial output and transform it back to 10-bit-wide parallel data.

The MAX9205/MAX9207 transmit serial data at speeds up to 400Mbps and 660Mbps, respectively, over PCB traces or twisted-pair cables. Since the clock is recovered from the serial data stream, clock-to-data and data-to-data skew that would be present with a parallel bus are eliminated.

The serializers require no external components and few control signals. The input data strobe edge is selected by TCLK\_R/F. PWRDN is used to save power when the devices are not in use. Upon power-up, a synchronization mode is activated, which is controlled by two SYNC inputs, SYNC1 and SYNC2.

The MAX9205 can lock to a 16MHz to 40MHz system clock, while the MAX9207 can lock to a 40MHz to 66MHz system clock. The serializer output is held in high impedance until the device is fully locked to the local system clock, or when the device is in powerdown mode.

Both the devices operate from a single +3.3V supply. are specified for operation from -40°C to +85°C, and are available in 28-pin SSOP packages.

### **Applications**

Cellular Phone Base Stations

Add Drop Muxes

Digital Cross-Connects

**DSLAMs**

Network Switches and Routers

Backplane Interconnect

#### **Features**

- ♦ Standalone Serializer (vs. SERDES) Ideal for **Unidirectional Links**

- **♦** Framing Bits for Deserializer Resync Allow Hot **Insertion Without System Interruption**

- ♦ LVDS Serial Output Rated for Point-to-Point and **Bus Applications**

- ♦ Wide Reference Clock Input Range 16MHz to 40MHz (MAX9205) 40MHz to 66MHz (MAX9207)

- ♦ Low 140ps (pk-pk) Deterministic Jitter (MAX9207)

- **♦ Low 34mA Supply Current (MAX9205)**

- **♦ 10-Bit Parallel LVCMOS/LVTTL Interface**

- ♦ Up to 660Mbps Payload Data Rate (MAX9207)

- ♦ Programmable Active Edge on Input Latch

- ♦ Pin-Compatible Upgrades to DS92LV1021 and DS92LV1023

## **Ordering Information**

| PART          | TEMP<br>RANGE  | PIN-<br>PACKAGE | REF CLOCK<br>RANGE<br>(MHz) |

|---------------|----------------|-----------------|-----------------------------|

| MAX9205EAI+   | -40°C to +85°C | 28 SSOP         | 16 to 40                    |

| MAX9205EAI/V+ | -40°C to +85°C | 28 SSOP         | 16 to 40                    |

| MAX9207EAI+   | -40°C to +85°C | 28 SSOP         | 40 to 66                    |

+Denotes a lead(Pb)-free/RoHS-compliant package. N denotes an automotive qualified part.

Pin Configuration and Functional Diagram appear at end of data sheet.

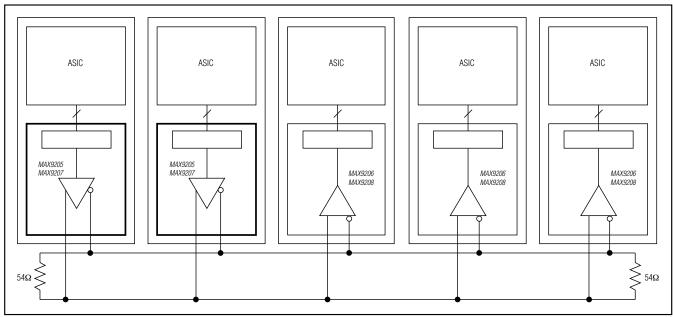

# **Typical Application Circuit**

#### **ABSOLUTE MAXIMUM RATINGS**

| AVCC, DVCC to GND0.3V to +4.0V                        | Storage Temperature Range65°C to +150°C           |

|-------------------------------------------------------|---------------------------------------------------|

| IN_, SYNC1, SYNC2, EN, TCLK_R/F, TCLK,                | Junction Temperature+150°C                        |

| PWRDN to GND0.3V to (V <sub>CC</sub> + 0.3V)          | Operating Temperature Range40°C to +85°C          |

| OUT+, OUT- to GND0.3V to +4.0V                        | ESD Protection (Human Body Model, OUT+, OUT-)±8kV |

| Output Short-Circuit DurationContinuous               | Lead Temperature (soldering, 10s)+300°C           |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) | Soldering Temperature (reflow)+260°C              |

| 28-Pin SSOP (derate 9.5mW/°C above +70°C)762mW        |                                                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

SSOP

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{AVCC} = V_{DVCC} = +3.0V \text{ to } +3.6V, R_L = 27\Omega \pm 1\% \text{ or } 50\Omega \pm 1\%, C_L = 10 \text{pF}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}.$  Typical values are at  $V_{AVCC} = V_{DVCC} = +3.3V$  and  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.) (Notes 2, 3, 4)

| PARAMETER                                                                       | SYMBOL           | CONDITIONS                                                                                                       |                           |           | MIN | TYP  | MAX | UNITS |  |

|---------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------|---------------------------|-----------|-----|------|-----|-------|--|

| LVCMOS/LVTLL LOGIC INPUTS (IN0 TO IN9, EN, SYNC1, SYNC2, TCLK, TCLK_R/F, PWRDN) |                  |                                                                                                                  |                           |           |     |      |     |       |  |

| High-Level Input Voltage                                                        | V <sub>IH</sub>  |                                                                                                                  |                           |           | 2.0 |      | Vcc | V     |  |

| Low-Level Input Voltage                                                         | V <sub>IL</sub>  |                                                                                                                  |                           |           | GND |      | 0.8 | V     |  |

| Input Current                                                                   | I <sub>IN</sub>  | V <sub>IN</sub> _ = 0V or V_VCC                                                                                  |                           |           | -20 |      | +20 | μΑ    |  |

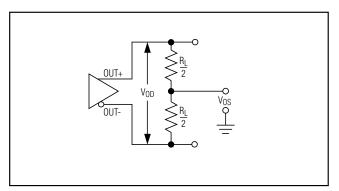

| BUS LVDS OUTPUTS (OUT+, OL                                                      | JT-)             |                                                                                                                  |                           |           |     |      |     |       |  |

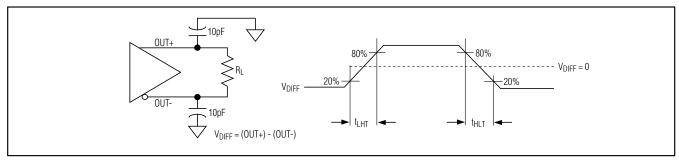

| Differential Output Voltage                                                     | Vop              | Figure 1                                                                                                         | $R_L = 27\Omega$          |           | 200 | 286  | 400 | mV    |  |

| Differential Output Voltage                                                     | VOD              | rigule i                                                                                                         | $R_L = 50\Omega$          |           | 250 | 460  | 600 | mV    |  |

| Change in V <sub>OD</sub> Between<br>Complementary Output States                | ΔV <sub>OD</sub> | Figure 1                                                                                                         | Figure 1                  |           |     | 1    | 35  | mV    |  |

| Output Offset Voltage                                                           | Vos              | Figure 1                                                                                                         |                           |           | 0.9 | 1.15 | 1.3 | V     |  |

| Change in V <sub>OS</sub> Between<br>Complementary Output States                | ΔVos             | Figure 1                                                                                                         | Figure 1                  |           |     | 3    | 35  | mV    |  |

| Output Short-Circuit Current                                                    | los              | $V_{OUT+}$ or $V_{OUT-} = 0V$ ,<br>$IN0$ to $IN9 = \overline{PWRDN} = EN = high$                                 |                           |           |     | -13  | -15 | mA    |  |

| Output High-Impedance Current                                                   | loz              | V <sub>PWRDN</sub> or V <sub>EN</sub> = 0.8V,<br>V <sub>OUT+</sub> or V <sub>OUT-</sub> = 0V or V <sub>VCC</sub> |                           | -10       |     | +10  | μΑ  |       |  |

| Power-Off Output Current                                                        | IOX              | V_VCC = 0V, VOUT+                                                                                                | or V <sub>OUT</sub> - = 0 | V or 3.6V | -10 |      | +10 | μΑ    |  |

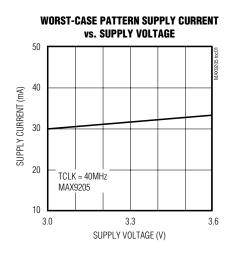

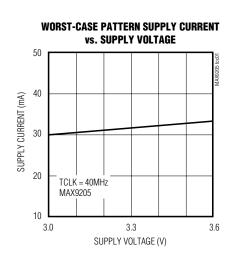

| POWER SUPPLY                                                                    |                  |                                                                                                                  |                           |           |     |      |     |       |  |

|                                                                                 |                  |                                                                                                                  | MANOOOF                   | 16MHz     |     | 23   | 35  |       |  |

|                                                                                 |                  | R <sub>L</sub> = 27_ or 50_                                                                                      | MAX9205                   | 40MHz     |     | 34   | 45  | ]     |  |

| Supply Current                                                                  | '   (F: 0 4)     | 1441/0007                                                                                                        | 40MHz                     |           | 32  | 50   | mA  |       |  |

|                                                                                 |                  | (1.1931.00 E, 1) MAX920                                                                                          | MAX9207                   | 66MHz     |     | 45   | 60  |       |  |

| Power-Down Supply Current                                                       | Iccx             | PWRDN = low                                                                                                      |                           |           |     | 8    | mA  |       |  |

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{AVCC} = V_{DVCC} = +3.0V \text{ to } +3.6V, \ R_L = 27\Omega \pm 1\% \text{ or } 50\Omega \pm 1\%, \ C_L = 10 \text{pF}, \ T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}. \ \text{Typical values are at } V_{AVCC} = V_{DVCC} = +3.3V \text{ and } T_A = +25^{\circ}\text{C}, \ \text{unless otherwise noted.}) \ (\text{Notes } 3, 5)$

| PARAMETER                                     | SYMBOL           | CONDITIONS   |                  | MIN                        | TYP                  | MAX                          | UNITS       |  |

|-----------------------------------------------|------------------|--------------|------------------|----------------------------|----------------------|------------------------------|-------------|--|

| TRANSMIT CLOCK (TCLK) TIMING REQUIREMENTS     |                  |              |                  |                            |                      |                              |             |  |

| TCLK Center Frequency                         | froor            |              | MAX9205          | 16                         |                      | 40                           | MHz         |  |

| TCLK Center Frequency                         | fTCCF            |              | MAX9207          | 40                         |                      | 66                           | MHz         |  |

| TCLK Frequency Variation                      | TCFV             |              |                  | -200                       |                      | 200                          | ppm         |  |

| TCLK Period                                   | trop             |              | MAX9205          | 25                         |                      | 62.5                         | ns          |  |

| TCLN Fellod                                   | tTCP             |              | MAX9207          | 15.15                      |                      | 25                           | 115         |  |

| TCLK Duty Cycle                               | TCDC             |              |                  | 40                         |                      | 60                           | %           |  |

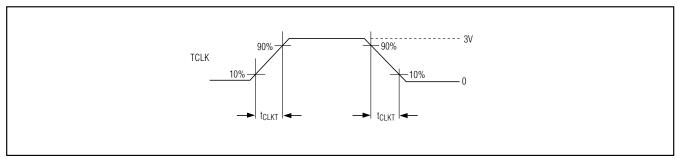

| TCLK Input Transition Time                    | tCLKT            | Figure 3     |                  |                            | 3                    | 6                            | ns          |  |

| TCLK Input Jitter                             | t∪IT             |              |                  |                            |                      | 150                          | ps<br>(RMS) |  |

| SWITCHING CHARACTERISTIC                      | S                |              |                  |                            |                      |                              |             |  |

| Low-to-High Transition Time                   | t <sub>LHT</sub> | Figure 4     | $R_L = 27\Omega$ | 150                        | 300                  | 400                          | ps          |  |

| Low-to-riigh fransition filme                 | LHI              | rigure 4     | $R_L = 50\Omega$ | 150                        | 350                  | 500                          | μδ          |  |

| High-to-Low Transition Time                   | t <sub>HLT</sub> | T Figure 4   | $R_L = 27\Omega$ | 150                        | 300                  | 400                          | ps          |  |

| Thigh to Low Hansition Time                   | 'HLI             | I iguic 4    | $R_L = 50\Omega$ | 150                        | 350                  | 500                          | ρ3          |  |

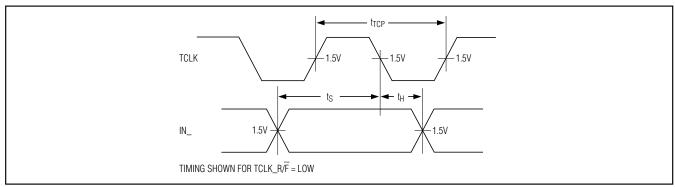

| IN_ Setup to TCLK                             | ts               | Figure 5     |                  | 1                          |                      |                              | ns          |  |

| IN_ Hold from TCLK                            | tH               | Figure 5     |                  | 3                          |                      |                              | ns          |  |

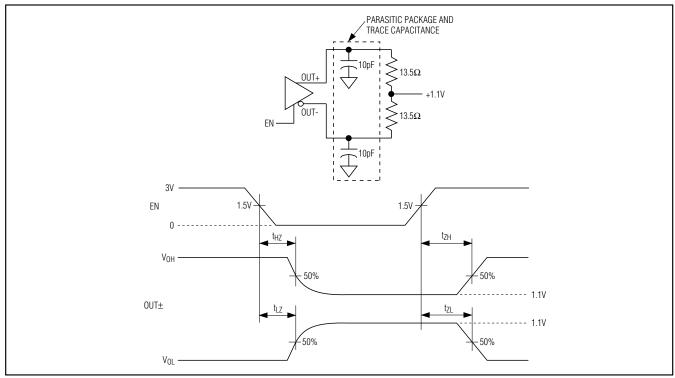

| OUTPUT High State to High-<br>Impedance Delay | tHZ              | Figures 6, 7 |                  |                            | 4.5                  | 10                           | ns          |  |

| OUTPUT Low State to High-<br>Impedance Delay  | t <sub>LZ</sub>  | Figures 6, 7 |                  |                            | 4.5                  | 10                           | ns          |  |

| OUTPUT High Impedance to<br>High-State Delay  | t <sub>ZH</sub>  | Figures 6, 7 |                  |                            | 4.5                  | 10                           | ns          |  |

| OUTPUT High Impedance to Low-State Delay      | t <sub>ZL</sub>  | Figures 6, 7 |                  |                            | 4.5                  | 10                           | ns          |  |

| SYNC Pulse Width                              | tspw             |              |                  | 6 x t <sub>TCP</sub>       |                      |                              | ns          |  |

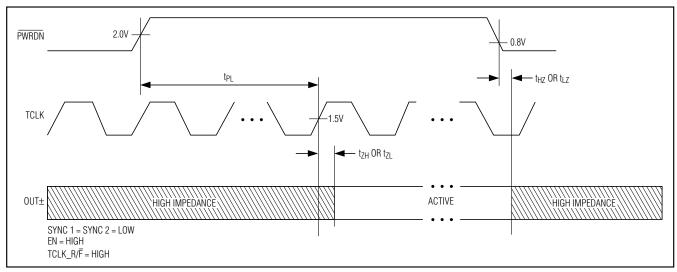

| PLL Lock Time                                 | tpL              | Figure 7     |                  | 2048 x<br>t <sub>TCP</sub> |                      | 2049 x<br>t <sub>TCP</sub>   | ns          |  |

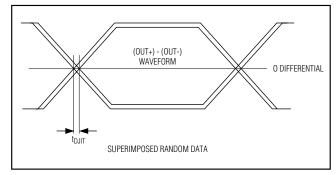

| Bus LVDS Bit Width                            | t <sub>BIT</sub> |              |                  |                            | t <sub>TCP</sub> /12 |                              | ns          |  |

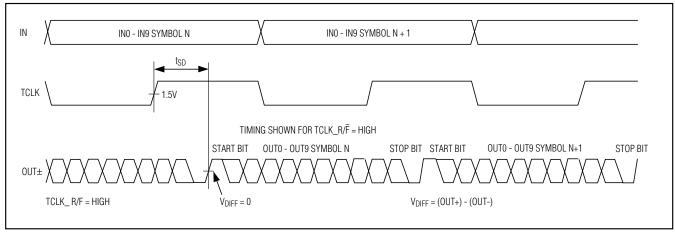

| Serializer Delay                              | t <sub>SD</sub>  | Figure 8     |                  | t <sub>TCP</sub> /6        |                      | (t <sub>TCP</sub> /6)<br>+ 5 | ns          |  |

## **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVCC} = V_{DVCC} = +3.0V \text{ to } +3.6V, R_L = 27\Omega \pm 1\% \text{ or } 50\Omega \pm 1\%, C_L = 10pF, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.$  Typical values are at  $V_{AVCC} = V_{DVCC} = +3.3V$  and  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Notes 3, 5)

| PARAMETER                       | SYMBOL            | CONDITIONS    |       | MIN | TYP | MAX | UNITS   |

|---------------------------------|-------------------|---------------|-------|-----|-----|-----|---------|

| 5                               |                   | MAYOOF        | 16MHz |     |     | 200 |         |

|                                 |                   | MAX9205 40MHz |       |     |     | 140 | ps      |

| Deterministic Jitter (Figure 9) | t <sub>DJIT</sub> | MAY0007       | 40MHz |     |     | 140 | (pk-pk) |

|                                 |                   | MAX9207       | 66MHz |     |     | 140 | 1       |

| Random Jitter (Figure 10)       | tRJIT             | MAX9205       | 16MHz |     |     | 13  |         |

|                                 |                   |               | 40MHz |     |     | 9   | ps      |

|                                 |                   | MAX9207       | 40MHz |     |     | 9   | (RMS)   |

|                                 |                   |               | 66MHz |     |     | 6   | ]       |

Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground except V<sub>OD</sub>, ΔV<sub>OD</sub>, and V<sub>OS</sub>.

Note 3: CL includes scope probe and test jig capacitance.

**Note 4:** Parameters 100% tested at  $T_A = +25$ °C. Limits over operating temperature range guaranteed by design and characterization.

Note 5: AC parameters are guaranteed by design and characterization.

## Typical Operating Characteristics

$(V_{AVCC} = V_{DVCC} = +3.3V, R_L = 27\Omega, C_L = 10pF, T_A = +25^{\circ}C, unless otherwise noted.)$

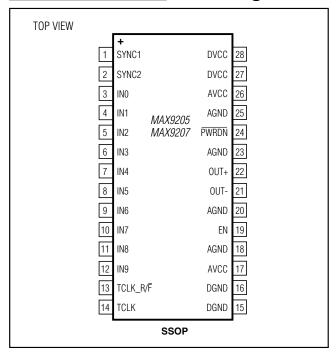

### **Pin Description**

| PIN               | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2              | SYNC 1,<br>SYNC 2 | LVCMOS/LVTTL Logic Inputs. The two SYNC pins are ORed. When at least one of the two pins are asserted high for at least six cycles of TCLK, the serializer initiates a transmission of 1024 SYNC patterns. If held high after 1024 SYNC patterns have been transmitted, SYNC patterns continue to be sent until the SYNC pin is asserted low. Toggling a SYNC pin after six TCLK cycles high and before 1024 SYNC patterns have been transmitted does not affect the output of the 1024 SYNC patterns. |

| 3–12              | IN0-IN9           | LVCMOS/LVTTL Data Inputs. Data is loaded into a 10-bit latch by the selected TCLK edge.                                                                                                                                                                                                                                                                                                                                                                                                                |

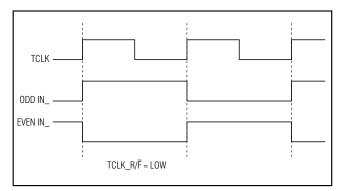

| 13                | TCLK_R/F          | LVCMOS/LVTTL Logic Input. High selects a TCLK rising-edge data strobe. Low selects a TCLK falling-edge data strobe.                                                                                                                                                                                                                                                                                                                                                                                    |

| 14                | TCLK              | LVCMOS/LVTTL Reference Clock Input. The MAX9205 accepts a 16MHz to 40MHz clock. The MAX9207 accepts a 40MHz to 66MHz clock. TCLK provides a frequency reference to the PLL and strobes parallel data into the input latch.                                                                                                                                                                                                                                                                             |

| 15, 16            | DGND              | Digital Circuit Ground. Connect to ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17, 26            | AVCC              | Analog Circuit Power Supply (Includes PLL). Bypass AVCC to ground with a 0.1µF capacitor and a 0.001µF capacitor. Place the 0.001µF capacitor closest to AVCC.                                                                                                                                                                                                                                                                                                                                         |

| 18, 20,<br>23, 25 | AGND              | Analog Circuit Ground. Connect to ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 19                | EN                | LVCMOS/LVTTL Logic Input. High enables serial data output. Low puts the bus LVDS output into high impedance.                                                                                                                                                                                                                                                                                                                                                                                           |

| 21                | OUT-              | Inverting Bus LVDS Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 22                | OUT+              | Noninverting Bus LVDS Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 24                | PWRDN             | LVCMOS/LVTTL Logic Input. Low puts the device into power-down mode and the output into high impedance.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 27, 28            | DVCC              | Digital Circuit Power Supply. Bypass DVCC to ground with a 0.1μF capacitor and a 0.001μF capacitor. Place the 0.001μF capacitor closest to DVCC.                                                                                                                                                                                                                                                                                                                                                       |

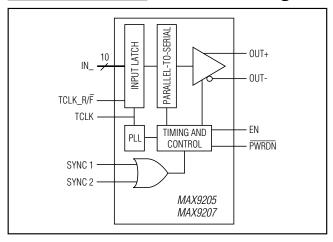

# **Detailed Description**

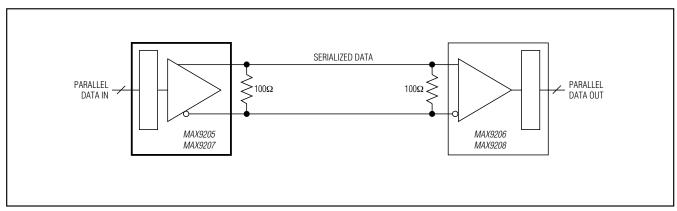

The MAX9205/MAX9207 are 10-bit serializers designed to transmit data over balanced media that may be a standard twisted-pair cable or PCB traces at 160Mbps to 660Mbps. The interface may be double-terminated point-to-point or a heavily loaded multipoint bus. The characteristic impedance of the media and connected devices can range from  $100\Omega$  for a point-to-point interface to  $54\Omega$  for a heavily loaded multipoint bus. A double-terminated point-to-point interface uses a  $100\Omega$ -termination resistor at each end of the interface, resulting in a load of  $50\Omega$ . A heavily loaded multipoint bus requires a termination as low as  $54\Omega$  at each end of the bus, resulting in a termination load of  $27\Omega$ . The serializer requires a deserializer such as the MAX9206/MAX9208 for a complete data transmission application.

A high-state start bit and a low-state stop bit, added internally, frame the 10-bit parallel input data and ensure a transition in the serial data stream. Therefore, 12 serial bits are transmitted for each 10-bit parallel input. The MAX9205 accepts a 16MHz to 40MHz reference clock, producing a serial data rate of 192Mbps (12 bits x 16MHz) to 480Mbps (12 bits x 40MHz). The MAX9207 accepts a 40MHz to 66MHz reference clock, producing 480Mbps to 792Mbps. However, since only 10 bits are from input data, the actual throughput is 10 times the TCLK frequency.

To transmit data, the serializers sequence through three modes: initialization mode, synchronization mode, and data transmission mode.

#### **Initialization Mode**

When VCC is applied, the outputs are held in high impedance and internal circuitry is disabled by on-chip power-on-reset circuitry. When the supply voltage reaches 2.35V, the PLL starts to lock to a local reference clock (16MHz to 40MHz for MAX9205 and 40MHz to 66MHz for MAX9207). The reference clock, TCLK, is provided by the system. A serializer locks within 2049 cycles of TCLK. Once locked, a serializer is ready to send data or SYNC patterns depending on the levels of SYNC 1 and SYNC 2.

#### **Synchronization Mode**

To rapidly synchronize with a deserializer, SYNC patterns can be sent. A SYNC pattern is six consecutive ones followed by six consecutive zeros repeating every TCLK period. When one or both SYNC inputs are asserted high for at least six cycles of TCLK, the serializer will initiate the transmission of 1024 SYNC patterns. The serializer will continue to send SYNC patterns if either of the SYNC input pins remains high. Toggling one SYNC input with the other SYNC input low before 1024 SYNC patterns are output does not interrupt the output of the 1024 SYNC patterns.

#### **Data Transmission Mode**

After initialization, both SYNC input pins must be set low by users or through a control signal from the deserializer before data transmission begins. Provided that SYNC inputs are low, input data at IN0–9 are clocked into the serializer by the TCLK input. Setting TCLK\_R/F high selects the rising edge of TCLK for data strobe and low selects the falling edge. If either of the SYNC inputs goes high for six TCLK cycles at any time during

data transmission, the data at IN0-9 are ignored and SYNC patterns are sent for at least 1024 TCLK cycles.

A start bit high and a stop bit low frame the 10-bit data and function as the embedded clock edge in the serial data stream. The serial rate is the TCLK frequency times the data and appended bits. For example, if TCLK is 40MHz, the serial rate is  $40 \times 12 (10 + 2 \text{ bits}) = 480\text{Mbps}$ . Since only 10 bits are from input data, the payload rate is  $40 \times 10 = 400\text{Mbps}$ .

#### **Power-Down**

Power-down mode is entered when the PWRDN pin is driven low. In power-down mode, the PLL of the serializer is stopped and the outputs (OUT+ and OUT-) are in high impedance, disabling drive current and also reducing supply current. When PWRDN is driven high, the serializer must reinitialize and resynchronize before data can be transferred. On power-up, in order for the MAX9205/MAX9207 to initialize correctly, PWRDN should remain below 0.7V until PCLK is stable and all power supplies are within specification.

#### **High-Impedance State**

The serializer output pins (OUT+ and OUT-) are held in high impedance when the supply voltage is first applied and while the PLL is locking to the local reference clock. Setting EN or PWRDN low puts the device in high impedance. After initialization, EN functions asynchronously. For example, the serializer output can be put into high impedance while SYNC patterns are being sent without affecting the internal timing of the SYNC pattern generation. However, if the serializer goes into high impedance, a deserializer loses PLL lock and needs to resynchronize before data transfer can resume.

Table 1. Input /Output Function Table

|    | IN    | PUTS         |                                                  | OUTPUTS                                                                                                                                             |  |

|----|-------|--------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EN | PWRDN | SYNC 1       | SYNC 2                                           | OUT+, OUT-                                                                                                                                          |  |

| Н  | Н     | and SYNC 2 a | r both SYNC 1<br>re held high for<br>ICLK cycles | Synchronization Mode. SYNC patterns of six 1s and six 0s are transmitted every TCLK cycle for at least 1024 TCLK cycles. Data at IN0–9 are ignored. |  |

| Н  | Н     | L            | L                                                | Data Transmission Mode. IN0–9 and 2 frame bits are transmitted every TCLK cycle.                                                                    |  |

| Х  | L     | X            | Х                                                | Output in high improduces                                                                                                                           |  |

| L  | Х     | Х            | Х                                                | Output in high-impedance.                                                                                                                           |  |

X = Don't care.

## **Applications Information**

#### **Power-Supply Bypassing**

Bypass AVCC with high-frequency surface-mount ceramic  $0.1\mu F$  and  $0.001\mu F$  capacitors in parallel as close to the device as possible, with the smaller valued capacitor closest to AVCC. Bypass DVCC with high-frequency surface-mount ceramic  $0.1\mu F$  and  $0.001\mu F$  capacitors in parallel as close to the device as possible, with the smaller valued capacitor closest to DVCC.

#### **Differential Traces and Termination**

Output trace characteristics affect the performance of the MAX9205/MAX9207. Use controlled-impedance media and terminate at both ends of the transmission line in the media's characteristic impedance. Termination with a single resistor at the end of a point-to-point link typically provides acceptable performance. However, the MAX9205/MAX9207 output levels are specified for double-terminated point-to-point and multipoint applications. With a single  $100\Omega$  termination, the output swing is larger.

Avoid the use of unbalanced cables such as ribbon or simple coaxial cable. Balanced cables such as twisted pair offer superior signal quality and tend to generate less EMI due to canceling effects. Balanced cables tend to pick up noise as common mode, which is rejected by a differential receiver.

Eliminate reflections and ensure that noise couples as common mode by running the differential traces close together. Reduce skew by matching the electrical length of the traces. Excessive skew can result in a degradation of magnetic field cancellation.

The differential output signals should be routed close to each other to cancel their external magnetic field. Maintain a constant distance between the differential traces to avoid discontinuities in differential impedance. Avoid 90° turns and minimize the number of vias to further prevent impedance discontinuities.

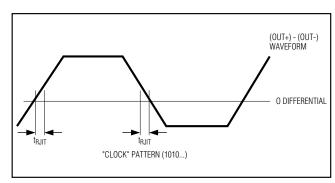

Figure 1. Output Voltage Definitions

Figure 2. Worst-Case I<sub>CC</sub> Test Pattern

Figure 3. Input Clock Transition Time Requirement

Figure 4. Output Load and Transition Times

Figure 5. Data Input Setup and Hold Times

Figure 6. High-Impedance Test Circuit and Timing

Figure 7. PLL Lock Time and PWRDN High-Impedance Delays

Figure 8. Serializer Delay

Figure 9. Definition of Deterministic Jitter (t<sub>DJIT</sub>)

Figure 10. Definition of Random Jitter (t<sub>RJIT</sub>)

### **Topologies**

The serializers can operate in a variety of topologies. Examples of double-terminated point-to-point, multidrop, point-to-point broadcast, and multipoint topologies are shown in Figures 11 through 14. Use 1% surface-mount termination resistors.

A point-to-point connection terminated at each end in the characteristic impedance of the cable or PCB traces is shown in Figure 11. The total load seen by the serializer is  $50\Omega$ . The double termination typically

reduces reflections compared to a single  $100\Omega$  termination. A single  $100\Omega$  termination at the deserializer input is feasible and will make the differential signal swing larger.

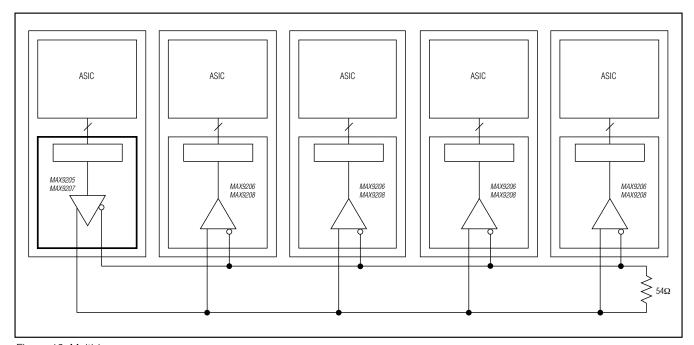

A serializer located at one end of a backplane bus driving multiple deserializers in a multidrop configuration is shown in Figure 12. A  $54\Omega$  resistor at the far end terminates the bus. This topology allows "broadcast" of data with a minimum of interconnect.

Figure 11. Double-Terminated Point-to-Point

Figure 12. Multidrop

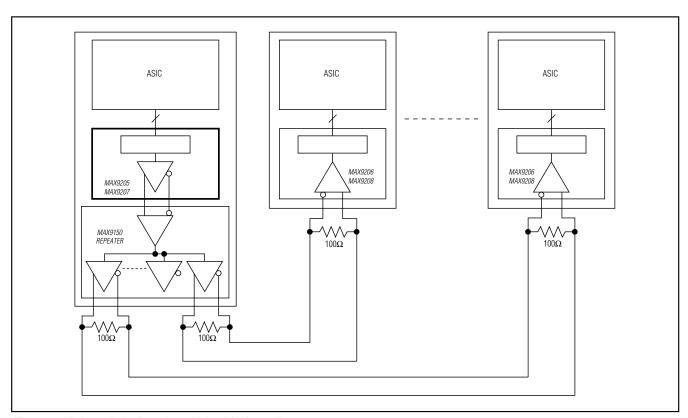

A point-to-point version of the multidrop bus is shown in Figure 13. The low-jitter MAX9150 10-port repeater is used to reproduce and transmit the serializer output over 10 double-terminated point-to-point links. Compared to the multidrop bus, more interconnect is traded for more robust hot-plug capability.

The repeater eliminates nine serializers compared to 10 individual point-to-point serializer-to-deserializer connections. Since repeater jitter subtracts from the serializer-deserializer timing margin, a low-jitter repeater is essential in most high data rate applications.

Multiple serializers and deserializers bused over a differential serial connection on a backplane are shown in Figure 14. The second serializer can be a backup to the primary serializer. The typical close spacing (1in or less) of cards on a backplane reduces the characteristic impedance by as much as half the initial, unloaded value. Termination resistors that match the loaded characteristic impedance are required at each end of the bus. The total loaded seen by the serializer is  $27\Omega$  in this case.

#### **Board Layout**

For bus LVDS applications, a four-layer PCB that provides separate power, ground, and input/output signals is recommended. Separate LVTTL/LVCMOS and bus LVDS signals from each other to prevent coupling into the bus LVDS lines.

Figure 13. Point-to-Point Broadcast Using MAX9150 Repeater

Figure 14. Multipoint

# **Pin Configuration**

# **Chip Information**

PROCESS: CMOS

# **Functional Diagram**

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/package">www.maximintegrated.com/package</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE NO.    | LAND<br>PATTERN NO. |  |

|-----------------|-----------------|----------------|---------------------|--|

| 28 SSOP         | A28+4           | <u>21-0056</u> | <u>90-0095</u>      |  |