#### MAX9650/MAX9651

# High-Current VCOM Drive Op Amps for TFT LCDs

#### **General Description**

The MAX9650/MAX9651 are single- and dual-channel VCOM amplifiers with rail-to-rail inputs and outputs. The MAX9650/MAX9651 can drive up to 1300mA of peak current per channel and operate up to 20V.

The MAX9650/MAX9651 are designed to source and sink a high current quickly to hold the VCOM voltage stable in large TFT-LCD panels.

The MAX9650/MAX9651 feature 40V/µs slew rate and 35MHz bandwidth to quickly settle outputs for 120Hz frame rate and full HD television.

The MAX9650/MAX9651 feature output short-circuit protection and thermal shutdown. These devices are available in exposed pad packages for excellent heat dissipation.

### **Applications**

- TFT-LCD Panels

- Instrument Control Voltage Sources

#### **Features**

- 1300mA Peak Output Current

- Rail-to-Rail Inputs and Outputs

- Operates Up to 20V

- 40V/µs Slew Rate

- 35MHz Bandwidth

- 5mA Quiescent Current per Channel

- Excellent Heat Dissipation (Exposed Pad)

<u>Pin Configurations</u> and <u>Ordering Information</u> appear at end of data sheet.

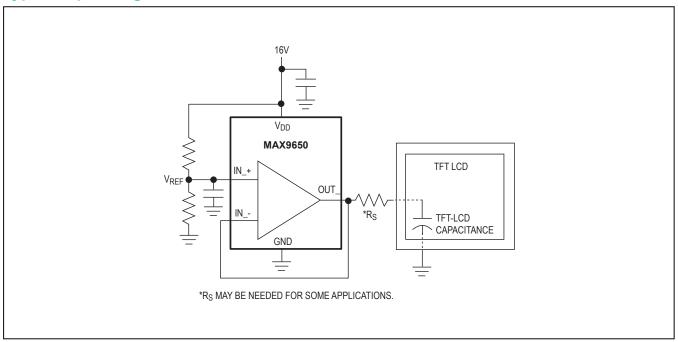

# **Typical Operating Circuit**

# MAX9650/MAX9651

# **High-Current VCOM Drive** Op Amps for TFT LCDs

# **Absolute Maximum Ratings**

| Supply Voltage (V <sub>DD</sub> to GND)0.3V to +22V   | Operating Temperature Range       | 40°C to +125°C |

|-------------------------------------------------------|-----------------------------------|----------------|

| Any Other Pin to GND0.3V to (V <sub>DD</sub> + 0.3V)  | Junction Temperature              | +150°C         |

| IN_+/IN (current)±20mA                                | Storage Temperature Range         | 65°C to +150°C |

| OUT_ (current)                                        | Lead Temperature (soldering, 10s) | +300°C         |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) | Soldering Temperature (reflow)    | +260°C         |

| SOT23 (derate 3.7mW/°C above +70°C)297.4mW            |                                   |                |

| μMAX-EP (derate 12.9mW/°C                             |                                   |                |

| above +70°C)1030.9mW                                  |                                   |                |

| TDFN-EP (derate 23.8mW/°C                             |                                   |                |

| above +70°C)1951.2mW                                  |                                   |                |

|                                                       |                                   |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Package Information**

#### SOT23

| Package Code                           | Z5+2A          |  |  |  |  |

|----------------------------------------|----------------|--|--|--|--|

| Outline Number                         | <u>21-0113</u> |  |  |  |  |

| Land Pattern Number                    | 90-0241        |  |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 146.4          |  |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 93.5           |  |  |  |  |

#### µMAX®-EP

| Package Code                            | U8E+2   |  |  |  |  |

|-----------------------------------------|---------|--|--|--|--|

| Outline Number                          | 21-0107 |  |  |  |  |

| Land Pattern Number                     | 90-0145 |  |  |  |  |

| Thermal Resistance, Single-Layer Board: |         |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 97      |  |  |  |  |

| Junction to Case $(\theta_{JC})$        | 5       |  |  |  |  |

| Thermal Resistance, Four-Layer Board:   |         |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 77.6    |  |  |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 5       |  |  |  |  |

$\mu\text{MAX}$  is a registered trademark of Maxim Integrated Products, Inc.

# **Package Information (continued)**

#### **TDFN-EP**

| Package Code                            | T833+2         |  |  |  |  |

|-----------------------------------------|----------------|--|--|--|--|

| Outline Number                          | <u>21-0137</u> |  |  |  |  |

| Land Pattern Number                     | 90-0059        |  |  |  |  |

| Thermal Resistance, Single-Layer Board: |                |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 54             |  |  |  |  |

| Junction to Case $(\theta_{JC})$        | 8              |  |  |  |  |

| Thermal Resistance, Four-Layer Board:   |                |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 41             |  |  |  |  |

| Junction to Case $(\theta_{JC})$        | 8              |  |  |  |  |

#### **Electrical Characteristics**

$(V_{DD} = 19V, V_{GND} = 0V, V_{CM} = V_{OUT} = V_{DD}/2, T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_A = +25^{\circ}C.) \ (Note \ 1)$

| PARAMETER                          | SYMBOL          | CONDITIO                                                 | MIN                       | TYP                       | MAX                      | UNITS |       |

|------------------------------------|-----------------|----------------------------------------------------------|---------------------------|---------------------------|--------------------------|-------|-------|

| Supply Voltage Range               | V <sub>DD</sub> | Guaranteed by PSRR                                       | 6                         |                           | 20                       | V     |       |

| Quiescent Current                  | I <sub>DD</sub> | Per channel                                              |                           |                           | 3.7                      | 8     | mA    |

| High Output Voltage                | V <sub>OH</sub> | I <sub>H</sub> = +5mA, V <sub>IN</sub> = V <sub>DD</sub> | V <sub>DD</sub> -<br>0.30 | V <sub>DD</sub> -<br>0.05 |                          | V     |       |

| Low Output Voltage                 | V <sub>OL</sub> | I <sub>L</sub> = -5mA, V <sub>IN</sub> = 0V              |                           |                           | 0.05                     | 0.30  | V     |

| L                                  | .,,             | T <sub>A</sub> = +25°C                                   |                           | -14                       | 3.5                      | +14   | mV    |

| Input Offset Voltage               | Vos             | T <sub>A</sub> = -40°C to +125°C                         | -17                       |                           | +17                      |       |       |

| Land Damilation                    |                 | I <sub>OUT</sub> = 0mA to -80mA                          |                           |                           | +0.2                     |       |       |

| Load Regulation                    | LR              | I <sub>OUT</sub> = 0mA to +80mA                          |                           |                           | -0.2                     |       | mV/mA |

| Input Bias Current                 | I <sub>FB</sub> | At V <sub>IN</sub> = 9.5V                                |                           |                           | 0.01                     | 1     | μA    |

| Voltage Gain                       | A <sub>V</sub>  | $R_L = 10k\Omega$ , $C_L = 50pF$                         |                           | 0.99                      |                          | 1.01  | V/V   |

| Power-Supply Rejection<br>Ratio    | PSRR            | $V_{DD} = 6V \text{ to } 20V, V_{CM} = V_{0}$            | 70                        | 95                        |                          | dB    |       |

| Common-Mode Input Voltage<br>Range | CMVR            | Inferred from CMRR test                                  | 0.5                       |                           | V <sub>DD</sub> -<br>0.5 | ٧     |       |

| Common-Mode Rejection<br>Ratio     | CMRR            | $0.5V \le V_{CM} \le V_{DD} - 0.5V$                      |                           | 60                        | 80                       |       | dB    |

|                                    |                 | V <sub>OUT</sub> = 9.5V (Note 2)                         | MAX9650AZK+               | 20                        |                          |       |       |

| Continuous Output Current          | I <sub>O</sub>  |                                                          | MAX9650AUA+               | 80                        |                          |       | mA    |

|                                    |                 | V <sub>DD</sub> = 15V, V <sub>OUT</sub> = 7.5V           | MAX9650ATA+               |                           | ±350                     |       |       |

| Transient Peak Output<br>Current   | I <sub>PK</sub> | (Note 3)                                                 |                           | ±1.3                      |                          | А     |       |

| Bandwidth                          | BW              | -3dB                                                     |                           | 35                        |                          | MHz   |       |

www.maximintegrated.com Maxim Integrated | 3

# **Electrical Characteristics (continued)**

$(V_{DD} = 19V, V_{GND} = 0V, V_{CM} = V_{OUT} = V_{DD}/2, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 1)

| PARAMETER                     | SYMBOL            | CONDITIONS                                                                                           | MIN | TYP  | MAX | UNITS |

|-------------------------------|-------------------|------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Slew Rate                     | SR                | 4V step, $C_L$ = 50pF, $R_L$ = 10kΩ, $A_V$ = +1V/V                                                   |     | 40   |     | V/µs  |

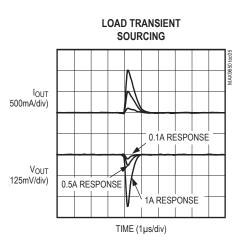

| Settling Time                 | t <sub>S</sub>    | Settling to 0.1% of $V_{OUT}$ , $I_L = 0$ to 1000mA, $R_S = 2.2\Omega$ , $C_S = 0.1\mu F$ (Figure 1) |     | 2.0  |     | μs    |

| Maximum Load Capacitance      | C <sub>LOAD</sub> | (Note 4)                                                                                             |     | 150  |     | nF    |

| Noninverting Input Resistance | R <sub>IN+</sub>  | (Note 5)                                                                                             |     | 100  |     | ΜΩ    |

| Inverting Input Resistance    | R <sub>IN-</sub>  | (Note 5)                                                                                             |     | 100  |     | ΜΩ    |

| Input Capacitance             | C <sub>IN</sub>   |                                                                                                      |     | 3    |     | pF    |

| Thermal Shutdown              |                   |                                                                                                      |     | +170 |     | °C    |

| Thermal Shutdown Hysteresis   |                   |                                                                                                      |     | 15   |     | °C    |

- Note 1: All devices are 100% production tested at  $T_A = +25$ °C. All temperature limits are guaranteed by design.

- Note 2: Continuous output current is tested with one output at a time.

- Note 3: See the Thermal Shutdown with Temperature Hysteresis section.

- Note 4: A series resistor can extend load capacitance range. The settling time can be optimized by a small series resistance. See the Applications Information section for more information.

- Note 5: Inputs are protected by back-to-back diodes.

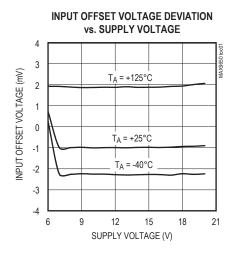

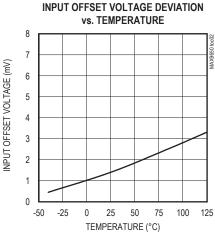

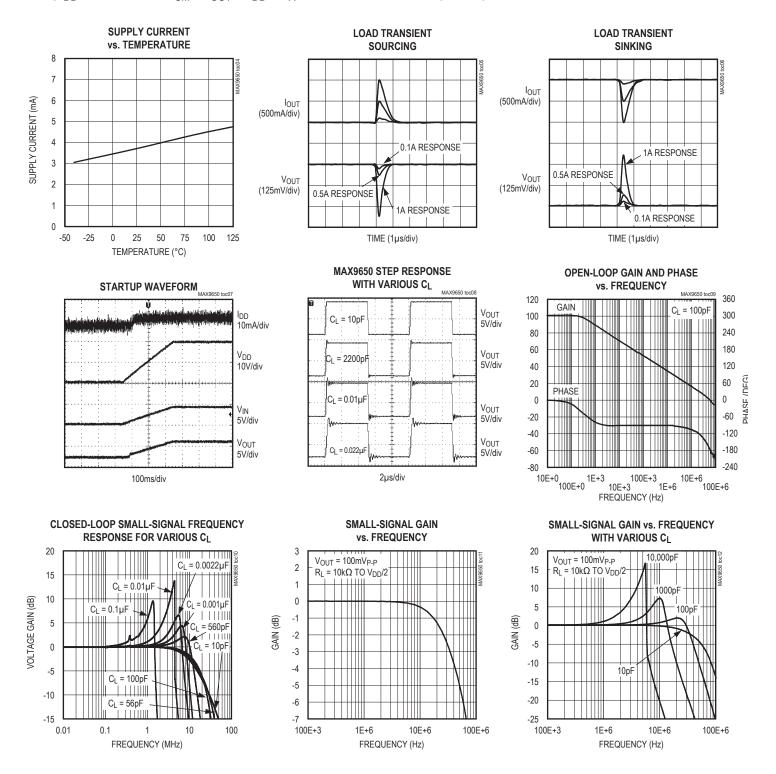

# **Typical Operating Characteristics**

$(V_{DD} = 19V, GND = 0, V_{CM} = V_{OUT} = V_{DD}/2, T_A = +25$ °C, unless otherwise specified.)

# **Typical Operating Characteristics (continued)**

$(V_{DD} = 19V, GND = 0, V_{CM} = V_{OUT} = V_{DD}/2, T_A = +25$ °C, unless otherwise specified.)

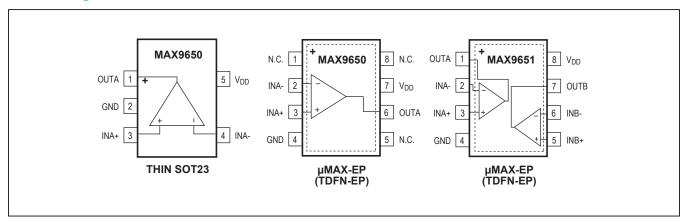

#### **Pin Description**

|       | PIN                 |                       |                 |                                                                                                                                                     |  |  |

|-------|---------------------|-----------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX   | MAX9650             |                       | NAME            | FUNCTION                                                                                                                                            |  |  |

| SOT23 | μΜΑΧ-ΕΡ,<br>TDFN-ΕΡ | (µMAX-EP,<br>TDFN-EP) | NAME.           | FUNCTION                                                                                                                                            |  |  |

| 1     | 6                   | 1                     | OUTA            | VCOM Output A                                                                                                                                       |  |  |

| 2     | 4                   | 4                     | GND             | Ground                                                                                                                                              |  |  |

| 3     | 3                   | 3                     | INA+            | Positive Input A                                                                                                                                    |  |  |

| 4     | 2                   | 2                     | INA-            | Negative Input A                                                                                                                                    |  |  |

| 5     | 7                   | 8                     | V <sub>DD</sub> | Positive-Supply Input. Bypass $V_{\mbox{\scriptsize DD}}$ to GND with a 0.1 $\mu\mbox{\scriptsize F}$ capacitor as close as possible to the device. |  |  |

| _     | _                   | 5                     | INB+            | Positive Input B                                                                                                                                    |  |  |

| _     | _                   | 6                     | INB-            | Negative Input B                                                                                                                                    |  |  |

| _     | _                   | 7                     | OUTB            | VCOM Output B                                                                                                                                       |  |  |

| _     | 1, 5, 8             | _                     | N.C.            | No Connection. Not internally connected.                                                                                                            |  |  |

| _     | _                   | _                     | EP              | Exposed Pad (µMAX and TDFN Only). EP is internally connected to GND. Connect EP to GND.                                                             |  |  |

## **Detailed Description**

The MAX9650/MAX9651 operational rail-to-rail input/output amplifiers hold the VCOM voltage stable while providing the ability to source and sink a high current quickly (1.3A) into a capacitive load such as the backplane of a TFT-LCD panel.

# Thermal Shutdown with Temperature Hysteresis

The MAX9650/MAX9651 are capable of high output currents and feature thermal-shutdown protection with temperature hysteresis. When the die temperature reaches +170°C, the device shuts down. When the die cools down by 15°C, the device turns on again. In a TFT-LCD application, the duty cycle is very low. Even with high values of voltage and current, the power dissipation is low and the chip does not shut down.

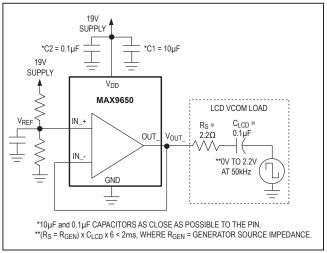

Figure 1. Settling Time Test Circuit

### **Applications Information**

#### **Output Load**

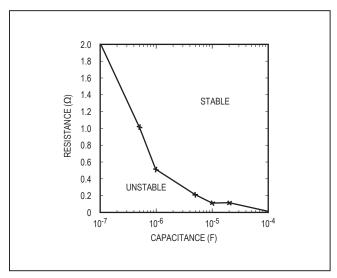

The MAX9650/MAX9651 are designed to drive capacitive loads. A small value of series resistance improves the performance of the device to ensure stability and fast settling with very large or very small capacitive loads. In many cases, this resistance is already present due to connection resistance in the wiring and no additional physical resistor is necessary. For minimum series resistance required for stability with capacitive loading, see Figure 2.

#### **Power Supplies and Bypass Capacitors**

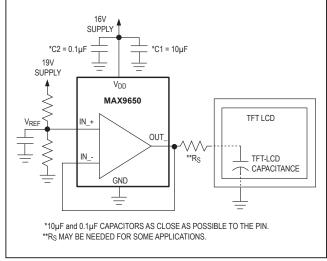

The MAX9650/MAX9651 operate from a 6V to 20V single supply or from ±4.5V to ±10V dual supplies. Proper supply bypassing ensures stability while driving high

transient loads. The MAX9650/MAX9651 require a minimum 10µF (C1) and 0.1µF (C2) power-supply bypass capacitors placed as close as possible to the power-supply pin (VDD). See Figure 3. For dual-supply operation, use 10µF and 0.1µF bypass capacitors on both supplies (VDD and GND) with each capacitor placed as close as possible to VDD and GND.

#### **Layout and Grounding**

The exposed pad on the µMAX and TDFN packages provides a low thermal resistance for heat dissipation. Solder the exposed pad to a ground plane for best thermal performance. Do not route traces under these packages. For dual-supply operation, the exposed pad (EP) can be electrically connected to the negative supply or it can be left unconnected.

Figure 2. Minimum Combined ESR/Series/Trace Resistance Required for Stability of the MAX9650 in Response to Capacitive Loads

Figure 3. Typical TFT-LCD Backplane Drive Circuit

# **Pin Configurations**

# **Ordering Information**

| PART          | AMPS PER<br>PACKAGE | PIN-<br>PACKAGE | TOP<br>MARK |

|---------------|---------------------|-----------------|-------------|

| MAX9650AZK+   | 1                   | 5 SOT23         | ADSI        |

| MAX9650AZK/V+ | 1                   | 5 SOT23         | ADSK        |

| MAX9650AUA+   | 1                   | 8 µMAX-EP*      | AABI        |

| MAX9650ATA+   | 1                   | 8 TDFN-EP*      | BKX         |

| MAX9651AUA+   | 2                   | 8 µMAX-EP*      | AABH        |

| MAX9651ATA+   | 2                   | 8 TDFN-EP*      | BKY         |

**Note:** All devices are specified over the -40°C to +125°C operating range.

# **Chip Information**

PROCESS: BICMOS

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

<sup>/</sup>V denotes an automotive qualified part.

<sup>\*</sup>EP = Exposed pad.