#

### **MAX9850 Evaluation System/Evaluation Kit**

### **General Description**

The MAX9850 evaluation system (EV system) consists of a MAX9850 evaluation kit (EV kit), a companion Maxim command module (CMOD232) interface board, and software.

The MAX9850 EV kit is a fully assembled and tested surface-mount printed circuit board (PCB) that evaluates the MAX9850 headphone stereo DAC with integrated headphone driver. The EV kit is designed to be driven by any digital audio Sony/Philips Digital Interface (S/PDIF) audio source and can be optionally configured to accept generic digital audio or I<sup>2</sup>S-compatible signals. The EV kit provides RCA jacks for connecting analog input signals. A 3.5mm headphone jack allows for easy connection of headphones to the PCB.

The Maxim command module interface board (CMOD232) allows a PC to use its serial port to emulate an I<sup>2</sup>C 2-wire interface. Windows<sup>®</sup> 98/2000/XP-compatible software, which can be downloaded from the Maxim website, provides a user-friendly interface to exercise the features of the MAX9850. The program is menu driven and offers a graphical user interface (GUI) with control buttons and a status display.

The MAX9850 EV system (MAX9850EVCMOD2#) includes both the EV kit and the CMOD232 interface board. Order the MAX9850 EV kit (MAX9850EVKIT#) if you already have a command module interface.

Windows is a registered trademark of Microsoft Corp.

### \_Features

- 1.8V to 3.6V Single-Supply Operation

- ♦ I<sup>2</sup>C-Compatible 2-Wire Serial Interface

- Selectable Optical/Electrical S/PDIF Input

- On-Board 12MHz Crystal Oscillator

- On-Board Digital Audio Receiver

- No Detectable Clicks or Pops

- ♦ Easy-to-Use Menu-Driven Software

- Assembled and Tested

- Includes Windows 98/2000/XP-Compatible Software and Demo PCB

### Ordering Information

| PART            | TEMP<br>RANGE                    | IC<br>PACKAGE | I <sup>2</sup> C<br>INTERFACE<br>TYPE |  |

|-----------------|----------------------------------|---------------|---------------------------------------|--|

| MAX9850EVKIT#   | $0^{\circ}$ C to $+70^{\circ}$ C | 28 TQFN       | Not included                          |  |

| MAX9850EVCMOD2# | $0^{\circ}$ C to +70°C           | 28 TQFN       | CMOD232                               |  |

#Denotes RoHS compliant.

**Note:** The CMOD232 board is required to interface the EV kit to the computer when using the software.

### Component Lists

### MAX9850 EV Kit (continued)

| DESIGNATION                                | QTY | DESCRIPTION                                                             |

|--------------------------------------------|-----|-------------------------------------------------------------------------|

| C5–C8                                      | 4   | 10μF ±20%, 6.3V X5R ceramic<br>capacitors (0805)<br>TDK C2012X5R0J106M  |

| C9–C12, C15–<br>C23, C30, C31,<br>C37, C43 | 17  | 1.0μF ±20%, 6.3V X5R ceramic<br>capacitors (0402)<br>TDK C1005X5R0J105M |

| C13                                        | 1   | 2.2µF ±20%, 6.3V X5R ceramic<br>capacitor (0603)<br>TDK C1608X5R0J225M  |

| C14                                        | 1   | 0.47µF ±20%, 16V X7R ceramic<br>capacitor (0603)<br>TDK C1608X7R1C474M  |

| C24–C29, C35,<br>C44, C45                  | 9   | 0.1µF ±20%, 10V X5R ceramic<br>capacitors (0402)<br>TDK C1005X5R1A104M  |

#### MAX9850 EV System

| PART          | QTY | DESCRIPTION                                 |

|---------------|-----|---------------------------------------------|

| MAX9850EVKIT# | 1   | MAX9850 EV kit                              |

| CMOD232+      | 1   | SMBus/I <sup>2</sup> C interface board      |

| AC Adapter    | 1   | 9VDC at 200mA<br>(powers the CMOD232 board) |

#Denotes RoHS compliant.

+Denotes lead-free and RoHS compliant.

#### MAX9850 EV Kit

| DESIGNATION | QTY | DESCRIPTION                                                                                         |

|-------------|-----|-----------------------------------------------------------------------------------------------------|

| C1, C2      | 2   | 220µF ±20%, 6.3V tantalum<br>capacitors (C-case)<br>AVX TPSC227M006R0070 or<br>AVX TPSC227M006R0100 |

| C3, C4      | 0   | Not installed, capacitors (C-case)                                                                  |

###

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

Evaluate: MAX9850

| DESIGNATION                     | QTY | DESCRIPTION                                                             |

|---------------------------------|-----|-------------------------------------------------------------------------|

| C32, C33, C34,<br>C36, C38, C39 | 6   | 0.01µF ±5%, 25V C0G ceramic<br>capacitors (0603)<br>TDK C1608C0G1E103J  |

| C40                             | 1   | 0.022µF ±10%, 25V X7R ceramic<br>capacitor (0402)<br>TDK C1005X7R1E223K |

| C41                             | 1   | 1000pF ±5%, 50V C0G ceramic<br>capacitor (0603)<br>TDK C1608C0G1H102J   |

| C42                             | 0   | Not installed (0603)                                                    |

| J1                              | 1   | 2 x 10 right-angle female receptacle                                    |

| J2                              | 1   | Digital audio optical receiver<br>Toshiba TORX147L                      |

| J3, J5                          | 2   | Phono jacks, red                                                        |

| J4, J6                          | 2   | Phono jacks, white                                                      |

| J7                              | 1   | Phono jack, yellow                                                      |

| J8                              | 1   | Switched stereo headphone jack<br>(3.5mm dia)                           |

| J9                              | 1   | SMA PC-mount connector                                                  |

| J10                             | 1   | 8-pin header                                                            |

| JU1                             | 1   | Dual-row 6-pin header                                                   |

| JU2                             | 1   | 2-pin header                                                            |

| JU3                             | 1   | 3-pin header                                                            |

| L1                              | 1   | 3.3µH ±10%, 270mA inductor (1812)<br>Coilcraft 1812CS-332XKL            |

| L2                              | 1   | 47μH ±10%, 200mA inductor (1812)<br>Coilcraft 1812LS-473XKL             |

| R1, R2, R3, R13                 | 4   | $1k\Omega \pm 5\%$ resistors (0603)                                     |

| R4                              | 1   | 47k $\Omega$ ±5% resistor (0603)                                        |

| R5                              | 1   | $75\Omega \pm 5\%$ resistor (0603)                                      |

| R6, R7, R8,<br>R12              | 0   | Not installed, resistors (0603)                                         |

| R9, R10                         | 2   | 1k $\Omega$ ±5% resistors (0402)                                        |

### Component Lists (continued)

| DESIGNATION | QTY | DESCRIPTION                                                                                          |

|-------------|-----|------------------------------------------------------------------------------------------------------|

| R11         | 1   | $3.01$ k $\Omega \pm 1$ % resistor (0603)                                                            |

| R14         | 0   | Not installed, resistor—short (PC trace) (1206)                                                      |

| R15         | 1   | $4.7$ k $\Omega \pm 5\%$ resistor (0603)                                                             |

| SW1         | 0   | Not installed                                                                                        |

| U1          | 1   | Stereo audio DAC (28 TQFN)<br>Maxim MAX9850ETI+                                                      |

| U2          | 1   | 192kHz digital audio receiver<br>(28 TSSOP)<br>Cirrus Logic CS8416-CZZ                               |

| U3          | 1   | Level translator (10 µMAX <sup>®</sup> )<br>Maxim MAX1840EUB+                                        |

| U4          | 1   | 16-bit, dual-supply bus transceiver<br>(48 TSSOP)<br>Texas Instruments<br>SN74AVCAH164245GR          |

| U5          | 1   | Dual/triple voltage microprocessor<br>supervisor (5 SC70)<br>(Top Mark: AFS)<br>Maxim MAX6736XKTGD3+ |

| U6, U7      | 2   | 2:1 noninverting multiplexers<br>(6 SC70)<br>Fairchild Semi NC7SV157P6X_NL<br>(Top Mark: VF7)        |

| U8          | 1   | Schmitt trigger buffer (5 SC70)<br>Fairchild Semi NC7SV17P5X_NL<br>(Top Mark: V17)                   |

| Y1          | 1   | Low-jitter crystal clock oscillator<br>CTS Frequency Controls<br>CB3LV-3C-12.0000-T                  |

|             | 3   | Shunts                                                                                               |

|             | 1   | PCB: MAX9850 Evaluation Kit#                                                                         |

#Denotes RoHS compliant.

### **Component Suppliers**

| SUPPLIER        | PHONE        | FAX          | WEBSITE               |

|-----------------|--------------|--------------|-----------------------|

| AVX Corp.       | 843-946-0238 | 843-626-3123 | www.avxcorp.com       |

| Coilcraft, Inc. | 847-639-6400 | 847-639-1469 | www.coilcraft.com     |

| TDK Corp.       | 847-803-6100 | 847-390-4405 | www.component.tdk.com |

Note: Indicate that you are using the MAX9850 when contacting these component suppliers.

$\mu$ MAX is a registered trademark of Maxim Integrated Products, Inc.

### MAX9850 EV Kit Files

| FILE        | DESCRIPTION                                |

|-------------|--------------------------------------------|

| INSTALL.EXE | Installs the EV kit files on your computer |

| MAX9850.EXE | Application program                        |

| UNINST.INI  | Uninstalls the EV kit software             |

### \_\_\_Quick Start

#### **Recommended Equipment**

- Computer running Windows 98, 2000, or XP

- Serial port (this is a 9-pin socket on the back of the computer)

- Standard 9-pin, straight-through, male-to-female cable (serial extension cable) to connect the computer's serial port to the Maxim command module interface board

- CMOD232 command module with included wall cube power source

- Two 3.0V/100mA DC power supplies

- One pair of headphones (16 $\Omega$  or greater)

- One digital audio S/PDIF signal source

#### Procedure

The MAX9850 EV kit is fully assembled and tested. Follow the steps below to verify board operation. **Caution: Do not turn on the power supply until all connections are completed.**

#### Command Module Setup

- 1) Enable the SDA/SCL pullup resistors on the command module by setting both switches (SW1) to the on position.

- Set the command module working voltage to 3.3V by placing a shunt across pins 1-2 of the VDD select jumper.

- 3) Connect a cable from the computer's serial port to the command module (CMOD232) interface board. Use a straight-through 9-pin male-to-female cable. To avoid damaging the EV kit or your computer, do not use a 9-pin null-modem cable or any other proprietary interface cable that is physically similar to the straight-through cable.

- 4) Connect the provided wall cube power supply to the CMOD232 board.

### EV Kit Setup

- Visit <u>www.maxim-ic.com/evkitsoftware</u> to download the latest version of the EV kit software, 9850Rxx.ZIP. Save the EV kit software to a temporary folder and uncompress the ZIP file.

- Install the EV kit software on your computer by running the INSTALL.EXE program inside the temporary folder. The program files are copied and icons are created in the Windows <u>Start I Programs</u> menu.

- Ensure that the I<sup>2</sup>C address of the MAX9850 is set to 0x20h by verifying that a shunt is placed across pins 1-2 of jumper JU1.

- 4) Ensure that a shunt is installed on jumper JU2

- 5) Connect the first 3.0V power supply to the DVDD and corresponding GND pads.

- 6) Connect the second 3.0V power supply to the PVDD and corresponding GND pads.

- 7) Connect the S/PDIF signal source to either J2 (optical) or J7 (electrical)

- 8) Insert a pair of  $16\Omega$  headphones into the headphone jack J8.

- 9) Carefully align the 20-pin connector of the MAX9850 EV kit with the 20-pin header of the CMOD232 interface board. Gently press them together.

- 10) Plug the CMOD232 wall cube into an electrical outlet.

- 11) Turn on both of the 3.3V power supplies

- 12) Enable the stereo audio sources.

- 13) Start the MAX9850 program by opening its icon in the **Start I Programs** menu.

- 14) Normal device operation can be verified by the "Status: MAX9850 Operational" text in the Interface box.

- 15) To autoconfigure the MAX9850 in a functional state, use the "auto setup" feature in the MAX9850 software.

| MAX9850 Evalua       | tion Software                                    |                                         | - 🗆 ×                          |  |  |  |

|----------------------|--------------------------------------------------|-----------------------------------------|--------------------------------|--|--|--|

| Options <u>H</u> elp |                                                  |                                         |                                |  |  |  |

| Headphones Power     | Clock Setup Digital Audio/Configuration Receiver | Interface<br>Device Address: 0x20h      | <b>न</b>                       |  |  |  |

| Volume Control       | Headphone Features                               | Status: MAX9850 Operational             | -                              |  |  |  |

| +6.0 dB -            | Enable Slew Rate Control                         | Register Address Sent = AUTC            |                                |  |  |  |

|                      | Slew Rate 0                                      | Data Sent/Received = SUCCE              |                                |  |  |  |

| +1.5 dB              | Debounce Delay (cycles)                          | MAX9850 Status                          |                                |  |  |  |

| -1.5 dB              | Enable Zero Crossing Detection                   |                                         | Interrupt<br>Enable            |  |  |  |

|                      | Force Headphone Mono Mode                        | GPIO State High                         |                                |  |  |  |

|                      |                                                  | PLL Lock Locked<br>Headphones Detected  |                                |  |  |  |

|                      |                                                  | Volume Normal                           |                                |  |  |  |

|                      |                                                  | Overload Normal                         |                                |  |  |  |

|                      |                                                  | Output Mode Stereo                      | N IXV N                        |  |  |  |

| :                    |                                                  | Headphone Operational                   |                                |  |  |  |

| -41.5 dB -           |                                                  | Line Output Operational                 |                                |  |  |  |

|                      |                                                  | Line Inputs Shutdown<br>DAC Operational |                                |  |  |  |

|                      |                                                  | Interrupt Status None                   | - 7                            |  |  |  |

| -73.5 dB             |                                                  |                                         |                                |  |  |  |

| -3.5 dB              |                                                  | Read Status Automatic S                 |                                |  |  |  |

| Mute 🗖               |                                                  | POR <u>R</u> eset Automatic I           | ilobal Shutdown<br>)iagnostics |  |  |  |

|                      |                                                  | Silence 120                             | -bus Activity                  |  |  |  |

|                      |                                                  | Auto Setup Receiver E                   |                                |  |  |  |

|                      | Disconnect Receiver                              |                                         |                                |  |  |  |

| Master Clock: 11.    | 294 MHz Internal Clock: 11.294 MHz               | Charge Pump Clock = 6                   | 666.7 kHz                      |  |  |  |

Figure 1. MAX9850 EV Kit Software Main Window

### **Detailed Description** of Software

Note: Words in bold are user-selectable features and status flags in the software.

#### **User-Interface Panel**

The user interface (Figure 1) is easy to operate; use the mouse, or a combination of the Tab and Arrow keys to manipulate the software. Each of the buttons corresponds to bits in the command and configuration bytes. By clicking on them, the correct I<sup>2</sup>C write operation is generated to update the internal registers of the MAX9850 or the on-board S/PDIF receiver.

The software divides EV kit functions into logical blocks. The Interface box indicates the current Device Address, the Register Address Sent, and the Data Sent/Received for the last read/write operation. This data is used to confirm proper device operation. Headphone, Power, Clock Setup, Digital Audio/ Configuration, and Receiver functions are accessed through tab sheets. MAX9850 status and interrupt control are accessed through the MAX9850 Status box.

The status bar displays vital MAX9850 clock information.

Return the EV kit to its power-on-reset state by clicking the **POR Reset** button. Power up the MAX9850 by clearing the **MAX9850 Global Shutdown** checkbox. Power up the receiver (U2) by selecting the **Receiver Enabled** checkbox.

The MAX9850 EV kit software features additional functions to simplify operation. **Automatic Diagnostics** probes the command module board and the MAX9850 EV kit to make sure that all connections are made, and all devices are working. This will create some activity on the I<sup>2</sup>C bus. The **Silence I2C-bus Activity** checkbox will reduce I<sup>2</sup>C bus activity to allow easy triggering of an oscilloscope.

The **Auto Setup** button further reduces user input. When this button is pressed, the software will do the following:

- 1) Search both EV kit S/PDIF inputs for a valid signal and then set the on-board multiplexer accordingly.

- 2) Power up the receiver IC as well as vital sections of the MAX9850.

- 3) Set internal clock dividers based on the incoming master clock frequency.

| MAX9850 Status                                             |                                                    | Interrupt<br>Enable |

|------------------------------------------------------------|----------------------------------------------------|---------------------|

| GPIO State<br>PLL Lock<br>Headphones<br>Volume<br>Overload | High<br>Locked<br>Detected<br>Normal<br>Left/Right |                     |

| Output Mode                                                | Mono                                               |                     |

| Headphone<br>Line Output<br>Line Inputs<br>DAC             | Operational<br>Shutdown<br>Shutdown<br>Shutdown    |                     |

| Interrupt Status                                           | None                                               |                     |

Figure 2. MAX9850 EV Kit Software Status Window

- 4) Set the MSB(14:8) and LSB(7:0) bits based on the desired mode of operation.

- 5) Set the charge-pump clock division bits if the MAX9850 is not using the internal oscillator.

The **Auto Setup** button is intended to simplify user interaction by placing the EV kit into a known-good mode of operation.

#### MAX9850 Status/Interrupt

The MAX9850 EV kit software defaults to a state that continually polls the device for new status data and monitors the alert conditions. The contents of the status register are displayed in the **MAX9850 Status** group box (Figure 2). Changes in the GPIO state, PLL lock, headphones present, volume, and output overload can be set to trigger an interrupt by checking the checkbox next to the desired information.

To disable continuous polling of data, uncheck the **Automatic Status Read** checkbox (Figure 1). Force a manual status register read by clicking the **Read Status** button.

If an interrupt condition is generated, the message **INTERRUPT** appears next to the interrupt status label. If enabled, the program will disable automatic reading of the status register.

#### **Status Bar**

The status bar (Figure 3) displays the MAX9850 master clock, internal clock, and charge-pump clock frequencies. By default it is updated automatically; however, this feature can be turned off (see the *Clock Setup* section).

#### **Headphone Control**

The Headphones tab (Figure 1) allows access to the MAX9850 headphone-related controls.

Headphone volume can be adjusted in dB increments by adjusting the **Volume Control** slider. The dB increments are not evenly spaced and are detailed further in the MAX9850 data sheet. Alternatively, a number can be entered in the box below the **Volume Control** slider. If a number that does not match a predefined dB increment is entered, the software automatically rounds the number to the nearest valid dB increment and sends the appropriate I<sup>2</sup>C data to the MAX9850. Mute the HP output by selecting the **Mute** checkbox.

Additional headphone control is also provided through the **Headphone Features** box. **Slew Rate Control** is controlled through the respective check and drop-

| Master Clock: 11.294 MHz | Internal Clock: 11.294 MHz | Charge Pump Clock = 666.7 kHz |

|--------------------------|----------------------------|-------------------------------|

|                          |                            |                               |

Figure 3. MAX9850 EV Kit Software Status Bar

Interface-Headphones Power Clock Setup Digital Audio/Configuration Receiver Device Address: 0x20h • Status: MAX9850 Operational Register Address Sent = AUTO SETUP Data Sent/Received = SUCCESS -MAX9850 Status-Interrupt Enable GPIO State High PLL Lock Locked Headphones Detected Volume Normal Overload Normal XV Output Mode Stereo Headphone Operational Operational Line Output Shutdown Line Inputs DAC Operational Interrupt Status None Read Status ✓ Automatic Status Read MAX9850 Global Shutdown POR Reset Automatic Diagnostics Silence I2C-bus Activity Auto Setup Receiver Enabled Disconnect Receiver Internal Clock: 11.294 MHz Master Clock: 11.294 MHz Charge Pump Clock = 666.7 kHz

Figure 4. MAX9850 EV Kit Software Power Tab

down boxes. Zero-Crossing Detection and Debounce **Delay** are also controlled through the interface. For a detailed description of zero-crossing detection and debounce delay, refer to the MAX9850 data sheet. Clicking the Force Headphone Mono Mode checkbox mutes the right channel and outputs a left/right-channel mix on the left channel.

#### **Power Management**

Power-management features of the MAX9850 are accessed through the **Power** tab (Figure 4).

Power enables for the MCLK input, charge pump, line out, line in, DAC input, and headphone output are accessed through the **Power Management** box.

The MAX9850 charge pump can operate either an internal 666.7kHz oscillator or frequency derived from the master clock. Force the MAX9850 to use the internal oscillator by checking the Use Internal Oscillator checkbox. When the Use Internal Oscillator checkbox is unchecked, set the charge-pump clock divider by adjusting the Clock Division Ratio slider. Refer to the

6

| <u>Options H</u> elp                                                                   |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                        | - 🗆 ×                                                                           |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

|                                                                                        | Digital Audio/Configuration Receiver<br>MAX9850 Mode Setup<br>Master (Non-Integer)<br>Master (Integer)<br>Slave (Non-Integer)<br>Slave (Integer)<br>MSB and LSB values<br>have no effect on<br>MAX9850 functionality<br>in Slave (Non-Integer)<br>Mode | Status: MAX9850 Operational<br>Register Address Sent = AUTO<br>Data Sent/Received = SUCCES                                                                                                                                                                                                                                                             |                                                                                 |

| Update Clocks in Status Bar<br>Automatically Update Clocks<br>Master Clock: 11.294 MHz | Internal Clock: 11.294 MHz                                                                                                                                                                                                                             | Headphone       Operational         Line Output       Operational         Line Inputs       Shutdown         DAC       Operational         Interrupt Status       None         Read Status       ✓         POR Reset       ✓         Automatic Di         Silence I2C-t         Auto Setup       ✓         Disconnect F         Charge Pump Clock = 66 | tatus Read<br>lobal Shutdown<br>iagnostics<br>bus Activity<br>abled<br>Receiver |

Figure 5. MAX9850 EV Kit Software Clock Setup Tab

MAX9850 data sheet for further details about clockdivider operation.

By default, the MAX9850 EV kit software writes to the registers when a control is activated. To shut down more that one item during the same I<sup>2</sup>C write operation, click the **Simultaneous Shutdown** checkbox. Adjust the other power-control checkboxes to the desired mode of operation and click the **GO** button. The proper register contents for the new selections will be sent in one I<sup>2</sup>C write command.

#### **Clock Setup**

Clock configuration features of the MAX9850 are accessed through the **Clock Setup** tab (Figure 5).

On-board multiplexers route a high-frequency square wave to the MAX9850 MCLK input. Select **Recovered Master Clock** to use the S/PDIF master clock. Select **On-Board Crystal Oscillator** to use the 12MHz crystal oscillator. Alternatively, a **User Provided Clock** can be applied to J9 of the MAX9850 EV kit. Enter the correct frequency in the **Frequency** box just below the **User**

| MAX9850 Mode Setup                                                 |

|--------------------------------------------------------------------|

| <ul> <li>Master (Non-Integer)</li> <li>Master (Integer)</li> </ul> |

| O Slave (Non-Integer)<br>O Slave (Integer)                         |

| O Manual Control<br>MSB/LSB 15429 0x3C 0x45<br>Update              |

| Automatic                                                          |

| Desired LRCLK Freq: 48 kHz                                         |

| Actual LRCLK Freq: 48.001 kHz                                      |

Figure 6. Master (Non-Integer) Mode

**Provided Clock** selection. Depending on the desired mode of operation (see the *MAX9850 Mode Setup* section) digital audio data can be synchronized to the master clock signal. The on-board S/PDIF receiver performs the synchronization of the digital audio data to the chosen MAX9850 master clock signal. To synchronize the digital audio to the MAX9850 master clock, check the **Synchronize Data with Clock** checkbox.

**Note:** When using the **Recovered Master Clock** as the master clock frequency, the digital audio data will always be synchronized.

The MAX9850 uses a frequency-divided master clock signal throughout the IC (see the *MAX9850 Mode Setup* section). Select the desired internal clock-divider ratio from the **Internal Clock Divide Ratio** pulldown.

The MAX9850 EV kit software is capable of calculating the master clock, internal clock, and charge-pump clock frequencies. Press the **Update Clocks in Status Bar** button to display the calculated values. Checking the **Automatically Update Clocks** checkbox will update the calculated values on a regular basis.

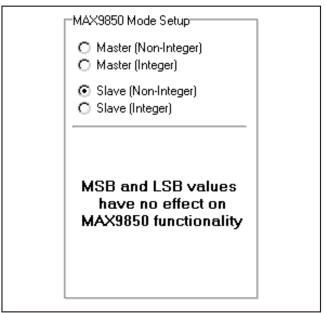

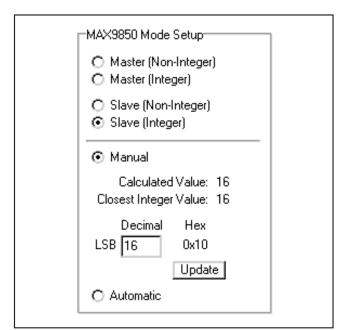

#### MAX9850 Mode Setup

The **MAX9850 Mode Setup** window alters its appearance depending on which mode is selected. Figures 6–9 show the different appearances of these windows.

Both Master (Non-Integer) and Master (Integer) modes of the MAX9850 EV kit software (Figures 6 and

| MAX9850 Mode Setup                                                 |

|--------------------------------------------------------------------|

| <ul> <li>Master (Non-Integer)</li> <li>Master (Integer)</li> </ul> |

| <ul> <li>Slave (Non-Integer)</li> <li>Slave (Integer)</li> </ul>   |

| O Manual Control<br>LSB 16 0x10                                    |

| Update<br>• Automatic                                              |

| Desired LRCLK Freq: 48 kHz                                         |

| Actual LRCLK Freq: 47.059 kHz                                      |

|                                                                    |

Figure 7. Master (Integer) Mode

Figure 8. Slave (Non-Integer) Mode

7) are similar in operation. Select **Manual Control** to write directly to the MAX9850 registers. Enter the number in the **MSB/LSB** edit box in **Master (Non-Integer)** and **LSB** in **Master (Integer)** mode and press the **Update** button to write to the MAX9850. Alternatively, the **Automatic** mode can be selected and a desired

Figure 9. Slave (Integer) Mode

Left/Right Clock frequency can be entered into the **Desired LRCLK Freq** edit box. The EV kit software will automatically calculate the correct MSB/LSB values and write them to the MAX9850 registers.

The **Slave (Non-Integer)** mode (Figure 8) of the MAX9850 does not rely on the MSB or LSB registers for operation. **Slave (Integer)** mode (Figure 9) can be operated manually by entering a number in the **LSB** edit box. When using the **Automatic** mode, the MAX9850 EV kit software calculates the correct LSB value and writes it to the appropriate IC register.

#### **Digital Audio/Configuration**

Digital audio control and miscellaneous configuration options are accessed through the **Digital Audio/Configuration** tab (Figure 10).

In addition to a serial data delay, the MAX9850 can also accept an inverted bit clock (BCLK) or left/right clock (LRCLK). Configure the MAX9850 by checking the desired **Invert** or **Delay** checkboxes. Choose the desired **Data Format** and **Justification** from the pulldowns.

The MAX9850 EV kit software is designed to control both the on-board S/PDIF receiver chip as well as the MAX9850. To maintain a valid digital link between the two ICs, the MAX9850 EV kit software features a **Lock** checkbox in both the **Signals** and **Word Size** group boxes. When the **Signals/Lock** checkbox is checked, the EV kit software will ensure that **BCLK Invert**,

**LRCLK Invert, SDIN/OUT Delay**, and **Justification** settings for both the MAX9850 and the on-board S/PDIF receiver match. When the **Word Size/Lock** checkbox is checked, the EV kit software will ensure that the word size settings for both the MAX9850 and the on-board S/PDIF receiver match.

For example, if the **MAX9850 BCLK Invert** checkbox is altered, the MAX9850 EV kit software automatically changes the **Receiver BCLK Invert** checkbox to match. All appropriate I<sup>2</sup>C data will be sent to both ICs and the system will continue to function properly.

**Note:** Unchecking either of the lock checkboxes will allow the software to operate in a state that may not be functional. Undesirable results may occur.

The GPIO of the MAX9850 is also configured on this tab. Click the desired radio button to alter the **Pin Direction** or the **GPIO Output State**. To route the MAX9850 internal interrupt signal to the GPIO pin, check the **Enable Interrupt on GPIO** checkbox.

#### Receiver

The MAX9850 EV kit software also controls the onboard S/PDIF receiver. Receiver control and status are divided into two tabs.

#### Receiver Main Control

Receiver control is accessed through the **Main Control** sub-tab, which is located under the **Receiver** tab (Figure 11).

Choose the desired S/PDIF input (**Optical** or **Electrical**) in the **Digital Audio Input Selection** box. Mute the receiver output by checking the **Mute Receiver Output** checkbox. Activate the receiver's de-emphasis filter by choosing the desired option in the **Receiver De-Emphasis Filter** box. The on-board digital receiver features programmable error handling. Choose the desired method for handling S/PDIF errors in the **Audio Error Handling** box.

#### **Receiver Status**

Receiver status is accessed through the **Status** subtab, which is under the **Receiver** tab (Figure 12). This tab serves as an invaluable diagnostic tool when evaluating the MAX9850 EV kit.

Read the error status by clicking the **Read Status** button in the **Receiver Error Status** window. The **Monitor** checkboxes must be selected for the status bits to be valid.

Click the **Read Status** button in the **Status** box to read the receiver status. To have the software automatically read the receiver status at constant time intervals, check the **Automatic Read** checkbox.

| _     |                          |              |

|-------|--------------------------|--------------|

| 0     | MAX98                    | 50 E va      |

| 82    | Options                  | <u>H</u> elp |

| 6X    | Headphone                | es Po        |

| Z     | Signals                  |              |

| 2     | 🛛 🔽 Lock                 | BCL          |

|       | MAX9850                  | 🗌 Ir         |

| luate | Receiver                 | □ Ir         |

| Evalu | Word Size<br>MAX98<br>16 |              |

|       |                          |              |

| MAX9850 Evaluation Software                                     |                                                                              |                                                               |                                                                                     | - 🗆 ×                                                                 |

|-----------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Options <u>H</u> elp                                            |                                                                              |                                                               |                                                                                     |                                                                       |

| Headphones Power Clock Setup Digital Aud                        | lio/Configuration Receiver                                                   | Interface<br>Device Address:<br>Status: MAX985                |                                                                                     | •                                                                     |

| I Lock BCLK LRCLK SDIN/OUT<br>MAX9850 □ Invert □ Invert □ Delay | Data Format Justification<br>MSB First 💌 Left 💌                              | Register Address<br>Data Sent/Recei                           |                                                                                     |                                                                       |

| Receiver 🔲 Invert 🗖 Invert 🗖 Delay                              | Left 💌                                                                       | MAX9850 Status                                                |                                                                                     | Interrupt<br>Enable                                                   |

| Word Size<br>MAX9850 Receiver<br>16 ▼ 16 ▼ Bits ▼ Lock          | GPIO Setup<br>Pin Direction<br>Input<br>O Output                             | GPIO State<br>PLL Lock<br>Headphones<br>Volume<br>Overload    | High<br>Locked<br>Detected<br>Normal<br>Normal                                      |                                                                       |

|                                                                 | GPI0 Output State<br>○ High (Hi-Z)<br>④ Low<br>□ Enable Interrupt<br>on GPI0 | Output Mode<br>Headphone<br>Line Output<br>Line Inputs<br>DAC | Stereo<br>Operational<br>Operational<br>Shutdown<br>Operational                     |                                                                       |

|                                                                 |                                                                              | POR <u>R</u> eset                                             | Automatic S<br>MAX9850 G<br>Automatic D<br>Silence 12C<br>Receiver Er<br>Disconnect | ilobal Shutdown<br>)iagnostics<br>•bus Activity<br>nabled<br>Receiver |

| Master Clock: 11.294 MHz In                                     | ternal Clock: 11.294 MHz                                                     | Charge Pu                                                     | ump Clock = 6                                                                       | 66.7 kHz                                                              |

Figure 10. MAX9850 EV Kit Software Digital Audio/Configuration Tab

#### Simple I<sup>2</sup>C Commands

There are two methods for communicating with the MAX9850: through the normal user-interface panel or through the I<sup>2</sup>C commands available by selecting the 2-Wire Interface Diagnostic item from the Options pulldown menu. A window is displayed that allows I<sup>2</sup>C operations, such as read byte and write byte, to be executed. To stop normal user-interface execution so that it does not override the manually set values, turn off the update timer by deselecting the Automatic Status Read and Automatic Diagnostics checkboxes.

The I<sup>2</sup>C dialog boxes accept numeric data in binary, decimal, or hexadecimal. Hexadecimal numbers should be prefixed by \$ or 0x. Binary numbers must be exactly eight digits. See Figure 13 for an example of this control method.

| MAX9850 Evaluation Softw                                                                                                                                                                                                                                                                                                                                              | vare                                                                                                                                                              | _ 🗆 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Options       Help         Headphones       Power       Clock Sett         Main Control       Status         Digital Audio Input Selection <ul> <li>Optical (TOSLINK)</li> <li>Electrical (RCA)</li> </ul> Receiver De-Emphasis Filter <ul> <li>De-emphasis filter off</li> <li>32 kHz</li> <li>44.1 kHz</li> <li>48 kHz</li> <li>50µs / 15 µs Auto-Select</li> </ul> | up Digital Audio/Configuration Receiver<br>Audio Error Handing<br>Upon error:<br>Repeat Last Audio Sample<br>Insert Silence<br>Do Nothing<br>Mute Receiver Output | Interface Device Address: 0x20h Status: MAX9850 Operational Register Address Sent = 0x09 Data Sent/Received = 0x0F  MAX9850 Status  MAX9850 Status  MAX9850 Status  MAX9850 Status  Interrupt Enable GPI0 State High PLL Lock Locked Headphones Detected Volume Normal Overload Normal Overload Normal Overload Normal Output Mode Stereo Headphone Operational Line Inputs Shutdown DAC Operational Line Inputs Shutdown DAC Operational Interrupt Status None  Read Status  POR Reset Automatic Status Read POR Reset Silence I2C-bus Activity |

|                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                   | Auto Setup     Receiver Enabled     Disconnect Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Master Clock: 11.294 MHz                                                                                                                                                                                                                                                                                                                                              | Internal Clock: 11.294 MHz                                                                                                                                        | Charge Pump Clock = 666.7 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Figure 11. MAX9850 EV Kit Software Receiver (Main Control) Tab

**Note:** In places where the slave address asks for an 8bit value, it must be the 7-bit slave address of the MAX9850 as determined by ADD with the last bit set to 1 for a read operation or a 0 for a write. Refer to the MAX9850 data sheet for a complete list of registers and functions.

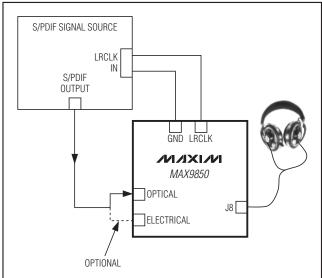

### Detailed Description \_\_\_\_\_\_of Hardware

The MAX9850 EV kit is a complete digital-audio headphone-driver evaluation system. The EV kit is driven by either an optical or electrical S/PDIF digital audio source. The S/PDIF signal is converted through onboard circuitry to compatible digital audio signals. The MAX9850 interfaces with the digital audio signals and drives a pair of headphones.

| leadphones Power Clock Setup<br>Main Control Status                                                                                                | Digital Audio/Config                                                                                        | uration Rec                                                | eiver [  | Interface<br>Device Address:<br>Status: MAX985                                    |                                                                 | •                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|

| Receiver Error Status<br>Monitor                                                                                                                   | -Status<br>Chip ID                                                                                          | 0x02                                                       | Receiver | Register Address<br>Data Sent/Recei                                               |                                                                 |                    |

| Q-subcode CRC Normal<br>Channel CRC Normal<br>PLL Locked Valid<br>AES3 Valid Valid<br>Confidence Normal<br>Bi-Phase Coding Normal<br>Parity Normal | Version<br>AUX Bit Length<br>PRO Format<br>SMCS Copyright<br>SCMS Generation<br>Format Status               | Revision D<br>4 bits<br>Consumer<br>None<br>Original       |          | MAX9850 Status<br>GPIO State<br>PLL Lock<br>Headphones<br>Volume<br>Overload      | High<br>Locked<br>Detected<br>Normal<br>Normal                  | Interrup<br>Enable |

|                                                                                                                                                    | PCM Data<br>IEC61937 Data<br>DTS_LD Data<br>DTS_CD Data<br>Digital Silence<br>96 kHz Sample<br>Pre-emphasis | Detected<br>Absent<br>Absent<br>Absent<br>Absent<br>Absent |          | Output Mode<br>Headphone<br>Line Output<br>Line Inputs<br>DAC<br>Interrupt Status | Stereo<br>Operational<br>Operational<br>Shutdown<br>Operational |                    |

Internal Clock: 11.294 MHz

Figure 12. MAX9850 EV Kit Software Receiver (Status) Tab

Master Clock: 11.294 MHz

Access to the MAX9850 analog inputs and outputs, is provided through RCA jacks J3-J6. Access the MAX9850 headphone outputs through the headphone jack J8 or the provided LEFT, RIGHT, and GND pads. The EV kit also features on-board level translators that allow the on-board S/PDIF receiver to communicate with the MAX9850 over the entire MAX9850 VDD voltage range (1.8V to 3.6V). The CMOD232 command module powers half of the on-board level translators.

For optimum performance, digital audio systems require a stable frequency source. The MAX9850 EV kit features an on-board 12MHz crystal oscillator. In addition, the MAX9850 EV kit can also use a user-provided signal source that is connected to J9. Alternatively, the S/PDIF recovered clock can be used. The MAX9850 ev kit software controls which clock signal is routed to the MCLK input (see the Clock Setup section for more details).

Auto Setup

M/IXI/N

Silence I2C-bus Activity

**Receiver Enabled**

Disconnect Receiver

Charge Pump Clock = 666.7 kHz

ŧ

| COM Port Conne              | ection 2-wire in                    | terface Lo | gging      |              |           |                    |

|-----------------------------|-------------------------------------|------------|------------|--------------|-----------|--------------------|

| Device Address<br>Target De | vice Address:                       | 0x20       | ▼ 00       | 10000r/w     | Hunt fo   | r active listeners |

| General comma               | nds EEPROM                          | data dump  | SMBus re   | gister watch | Low Level | commands           |

| · · · · ·                   | Bus Protocols, P<br>teByte(addr,cmd |            | ead/Write, |              | ecute     | PASS               |

| Command byte                | 0x02 🔻                              | Data Out:  | 0x00       |              |           | •                  |

| Byte count:                 | 1 4                                 | Data In:   | ?          |              |           |                    |

|                             |                                     |            |            |              |           |                    |

|                             |                                     |            |            |              |           |                    |

|                             |                                     |            |            |              |           |                    |

|                             |                                     |            |            |              |           |                    |

|                             |                                     |            |            |              |           |                    |

Figure 13. The above example shows a simple SMBusWriteByte operation using the included Two-Wire Interface Diagnostics. In this example, the software is writing data (0x00h) to Device Address 0x20h, Register Address 0x02h. The above data sequence will set the volume of the MAX9850 to max.

#### **Address Selection**

Jumper JU1 sets the MAX9850  $I^2C$  slave address. The default address is 0010 000Y (ADD = GND). See Table 1 for a complete list of addresses.

**Note:** The first 7 bits shown are the address. Y (bit 0) is the  $I^2C$  read/write bit. This bit is a 1 for a read operation or a 0 for a write.

#### Manual Headphone Sense Control

To simulate a pair of headphones being inserted into the headphone jack J8, remove the shunt from jumper JU2. Connect the load to the LEFT, RIGHT, and GND pads located by the headphone jack J8. See Table 2 for jumper settings.

# Table 1. JU1 Shunts Settings for I<sup>2</sup>C Address (JU1)

| SHUNT    | T MAX9850 MAX9850<br>ADDRESS |           | 0 ADDRESS   |  |

|----------|------------------------------|-----------|-------------|--|

| POSITION | PIN                          | BINARY    | HEXADECIMAL |  |

| 1-2*     | GND                          | 0010 000Y | 0x20h       |  |

| 3-4      | AV <sub>DD</sub>             | 0010 001Y | 0x22h       |  |

| 5-6      | SDA                          | 0010 011Y | 0x26h       |  |

\*Default Configuration: JU1 (1-2)

# Table 2. Manual Headphones SenseControl (JU2)

| SHUNT<br>POSITION | DESCRIPTION                                                              |

|-------------------|--------------------------------------------------------------------------|

| Installed*        | MAX9850 EVKIT headphone sense controlled by the insertion of headphones. |

| Not Installed     | MAX9850 EVKIT headphone sense switch forced open.                        |

\*Default Configuration: JU2 (Installed)

### Table 3. GPIO Pullup Register (JU3)

| SHUNT<br>POSITION | DESCRIPTION                                                                                                           |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|

| 1-2*              | GPIO pin pulled up to 3.3V. Monitor GPIO signal at the GPIO pad.                                                      |

| 2-3               | GPIO pin left open. Connect a pullup resistor<br>to the desired voltage. Monitor GPIO signal at<br>the GPIO_OPEN pad. |

\*Default Configuration: JU3 (1-2)

#### **GPIO** Interface

The MAX9850 EV kit features an on-board pullup resistor on the MAX9850 GPIO pin. Jumper JU3 can disconnect this pin from the pullup resistor.

#### Using an Alternative I<sup>2</sup>C Interface

The MAX9850 EV kit provides pads and pullup resistor placeholders that allow an alternative I<sup>2</sup>C-compatible interface to be used. Connect the interface through the SCL, SDA, and GND pads. Install pullup resistors at positions R7 and R8, if required.

If the on-board digital receiver IC is to be used with an alternative I<sup>2</sup>C interface, connect a 3.3V power supply between the VMOD and GND pads on the MAX9850 EV kit. The I<sup>2</sup>C address of the digital receiver is fixed at 0x28.

#### Using an Alternative Digital Audio Interface

The MAX9850 EV kit features a digital receiver that converts readily available S/PDIF signals to the required digital audio signals needed for the MAX9850. If an alternative digital audio interface is to be used, connect the interface to header J10, check **Disconnect Receiver**. Header pin names are clearly marked on the EV kit silkscreen. Ensure that the command module is disconnected from the EV kit during this mode of operation.

#### Synchronizing the EV Kit (Master Modes)

While in master mode, the MAX9850 supplies the LRCLK signal and thus controls the digital audio sample rate. To allow synchronization between the MAX9850 and the S/PDIF sample source, the LRCLK signal is buffered and output to a set of pads on the EV kit. Connect the synchronization input of the S/PDIF sample source to the LRCLK and GND pads (Figure 14). The LRCLK signal is 3.3V CMOS compatible.

Figure 14. Synchronized MAX9850 EV Kit Diagram

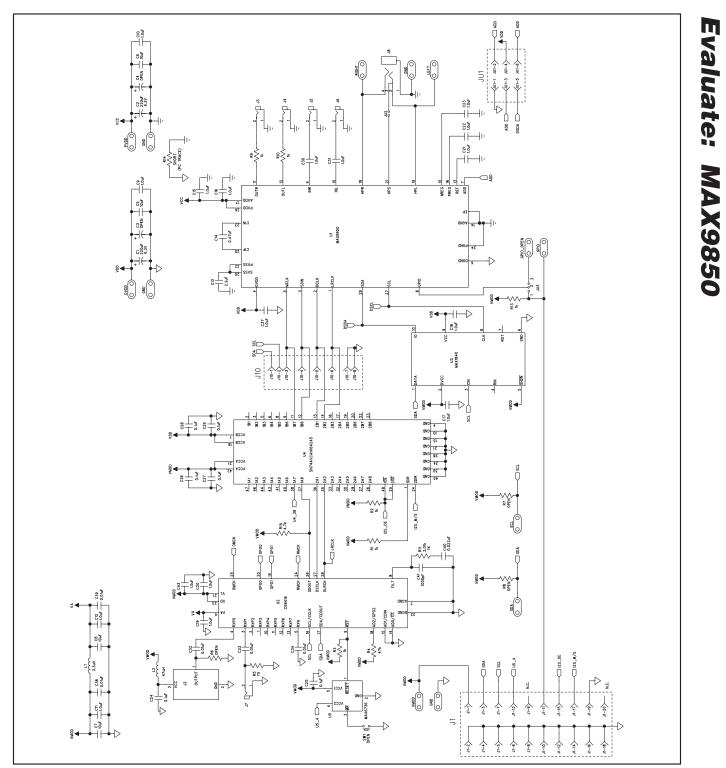

Figure 15a. MAX9850 EV Kit Schematic (Sheet 1 of 2)

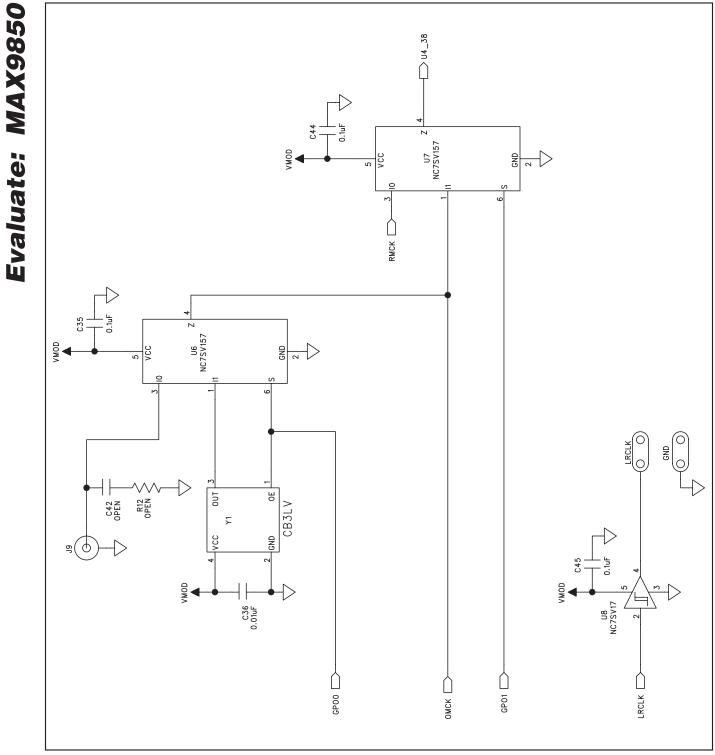

Figure 15b. MAX9850 EV Kit Schematic (Sheet 2 of 2)

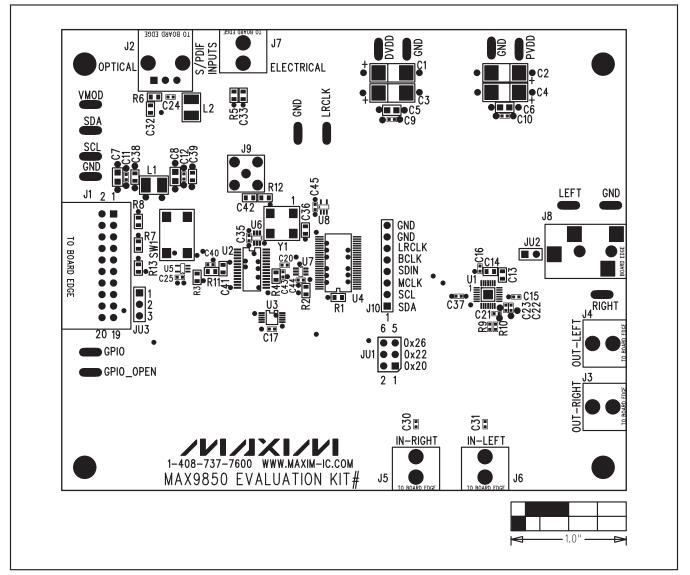

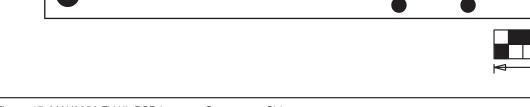

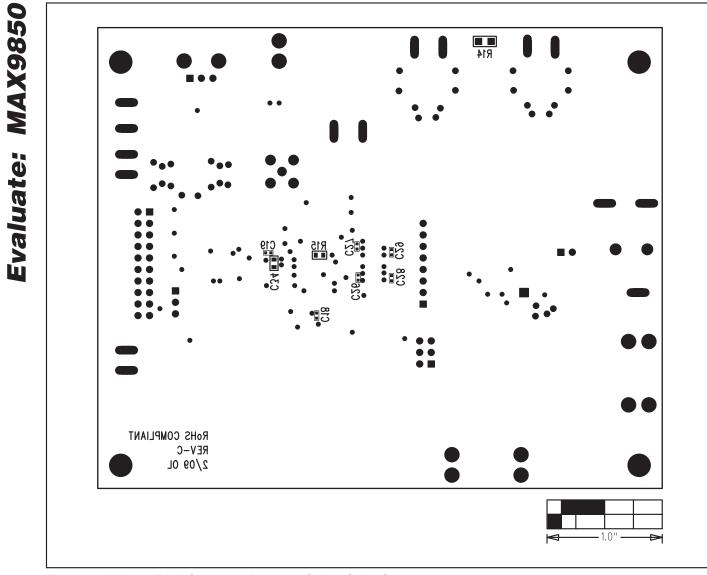

Figure 16. MAX9850 EV Kit Component Placement Guide—Component Side

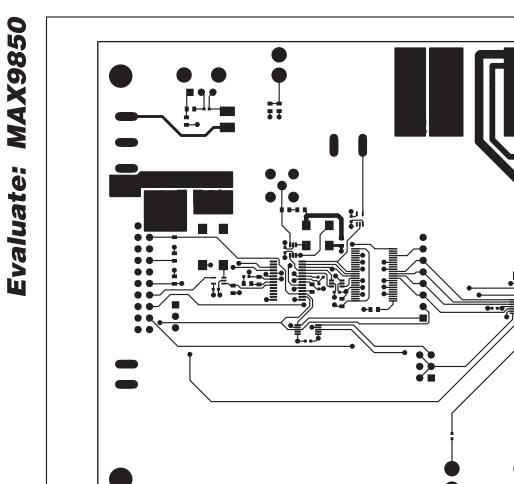

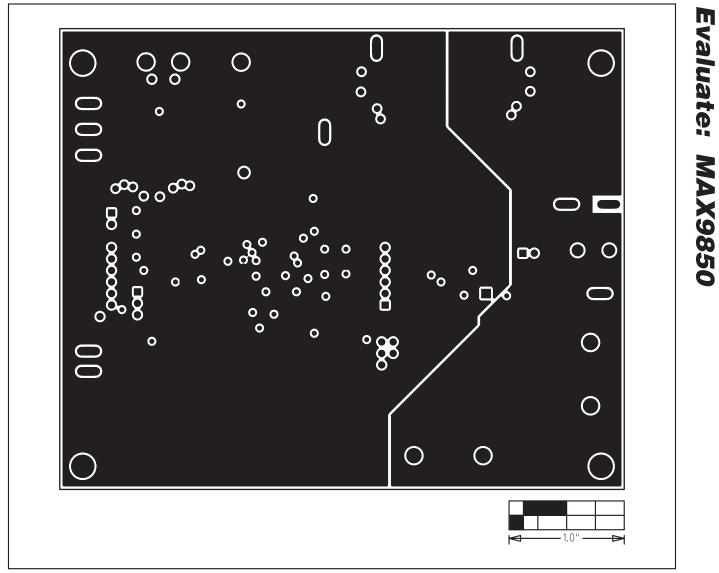

Figure 17. MAX9850 EV Kit PCB Layout—Component Side

·1.0"

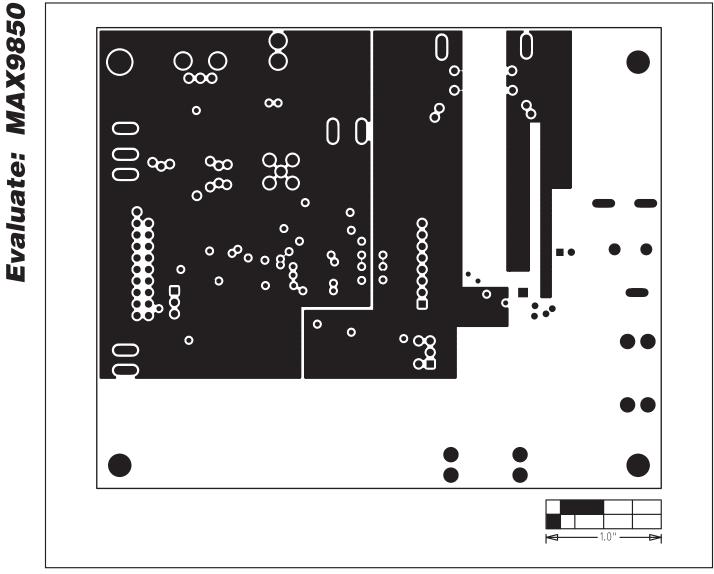

Figure 18. MAX9850 EV Kit PCB Layout—Inner Layer 2

Figure 19. MAX9850 EV Kit PCB Layout—Inner Layer 3

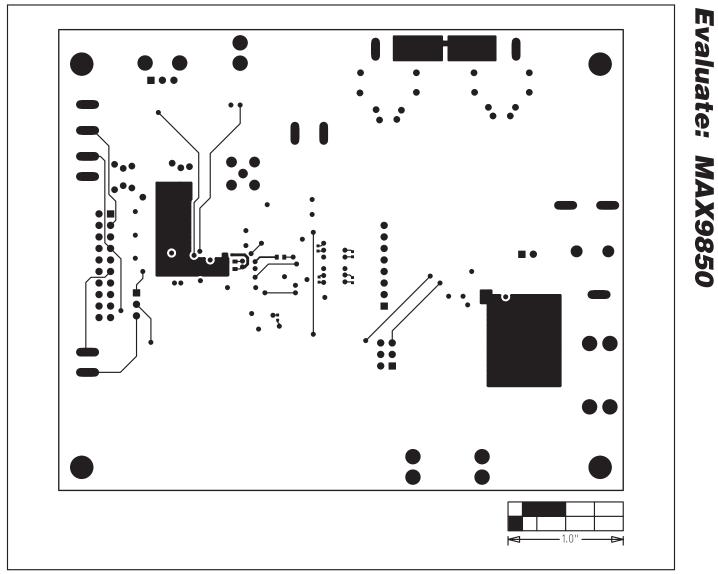

Figure 20. MAX9850 EV Kit PCB Layout—Solder Side

Figure 21. MAX9850 EV Kit Component Placement Guide—Solder Side