## 1 General description

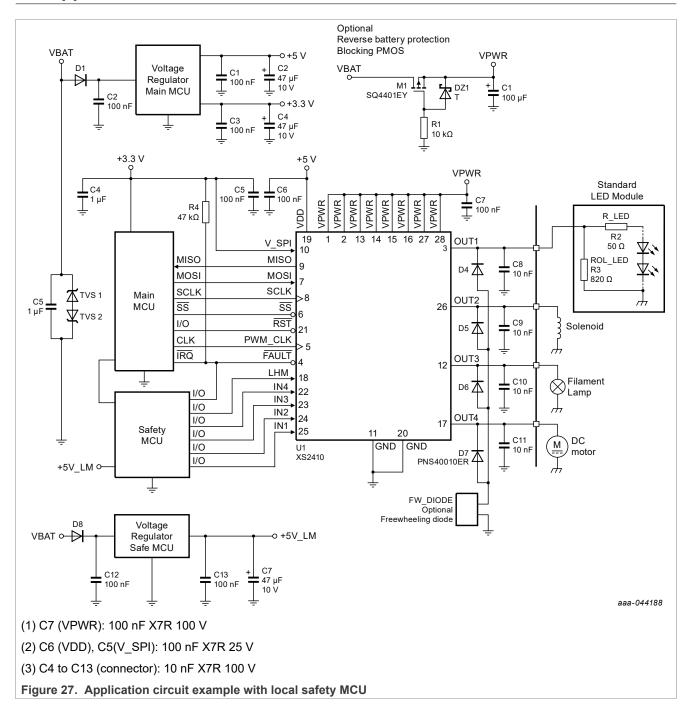

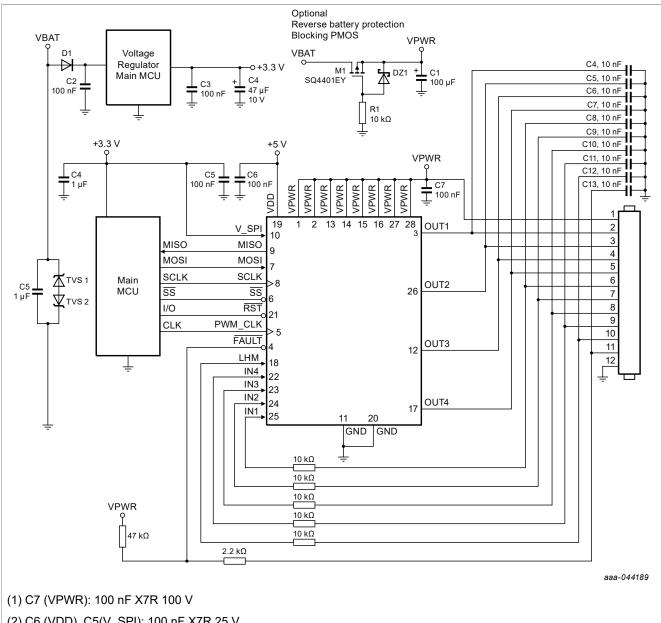

The MC33XS2410 is a four channel self-protected high-side switch. Featuring advanced digital monitoring and control function, the device is operational from 3.0 V to 60 V. As a result of high-level integration, the embedded 12-bit analog-to-digital converter enables a drastically simplified hardware design and MCU software control. The device is controlled by SPI port for configuration, monitoring and diagnostics of the outputs. Whenever communication with the MCU is lost, the device enters a safe operation mode, but remains operational, controllable and protected.

This product has been qualified to the appropriate Automotive Electronics Council (AEC) standard Q100 and is suitable for use in automotive applications.

## 2 Features and benefits

- Four fully protected 100 m $\Omega$  / dual 50 m $\Omega$  (at 25 °C) high-side switches

- Active current limitation is 5 A

- · Configurable parallel mode to double current capability

- 16-bit SPI port communication 3.3 V / 5.0 V compatible with daisy chain capability

- Outputs controllable via SPI-bus or direct inputs

- Diagnostic status reported via SPI-bus

- Watchdog for invalid commands or inactive SPI, with programmable timeout

- Programmable interrupt generator that reports to FAULT pin or SPI-bus

- Four independent PWM modules programmable from 0.5 Hz to 2.0 kHz with internal or external clock

- Protection for battery transient overvoltage and reversed polarity battery connection

- · Configurable safe mode

- Standby mode with very low power consumption

- Digital PI PWM closed loop current regulation

- External FAULTB pin for warning or IRQ reporting

- 10 mA open load detection in ON state

- · Latch off with configurable auto retry

- Configurable severe short-circuit and overload protection

- Programmable active current limit threshold to minimize short-circuit effect

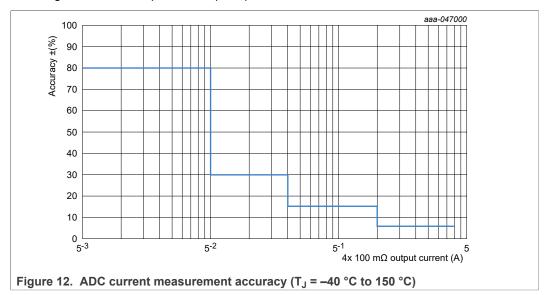

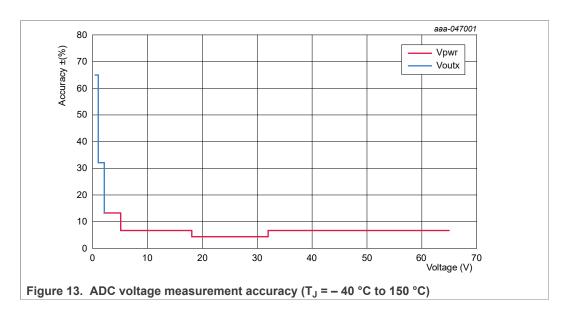

- 12 bits ADC:

- Current from 5.0 mA to 5.0 A with ± 6 % above 1 A

- Voltage from 0.5 V to 65 V with ± 6.5 % above 5.0 V

- Temperature warning for each channel and central die monitoring

- Qualified in accordance with AEC Q100 grade 1

- Electrical transient disturbance immunity according of ISO 7637-2 and ISO 16750-2

#### **Applications** 3

- 12 V automotive, truck, and off-highway equipment

- 12 V and 24 V systems as well as industrial applications up to 60 V

- LED modules

- Solenoids valve and solenoid valve proportional with PI regulation

- DC motor up to 20 W with PWM control

- · Incandescent bulbs up to 21 W

- ECU module with large input bypass capacitor, 470 µF and above

## Quick reference data

Table 1. Quick reference data

| Symbol               | Parameter Conditions            |                      | Min. | Тур.    | Max.              | Unit |

|----------------------|---------------------------------|----------------------|------|---------|-------------------|------|

| V <sub>PWR</sub>     | Power supply voltage            | operating [1]        | 3.0  | 14 / 28 | 60 <sup>[2]</sup> | V    |

| I <sub>OUT_4DC</sub> | Nominal load current            | 4 outputs [3] active | _    | 1.8     | _                 | А    |

| I <sub>OUT_2DC</sub> | Parallel mode load              | 2 outputs [3] active | _    | 3.6     | _                 | А    |

| TJ                   | Junction temperature            | _                    | -40  | _       | +150              | °C   |

| I <sub>VDD_STB</sub> | Stand-by current (Disable mode) | `                    |      | _       | 1                 | μΑ   |

| F <sub>SPI</sub>     | SPI frequency                   | [4]                  | _    | _       | 10                | MHz  |

When  $V_{PWR}$  < 4.0 V, full device operation is guaranteed if  $V_{DD} \geq$  4.0 V.

#### **Ordering information** 5

Table 2. Ordering information

| Part number [1] | Package  |                                                                                                                              |           |  |  |

|-----------------|----------|------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

|                 | Name     | Description                                                                                                                  | Version   |  |  |

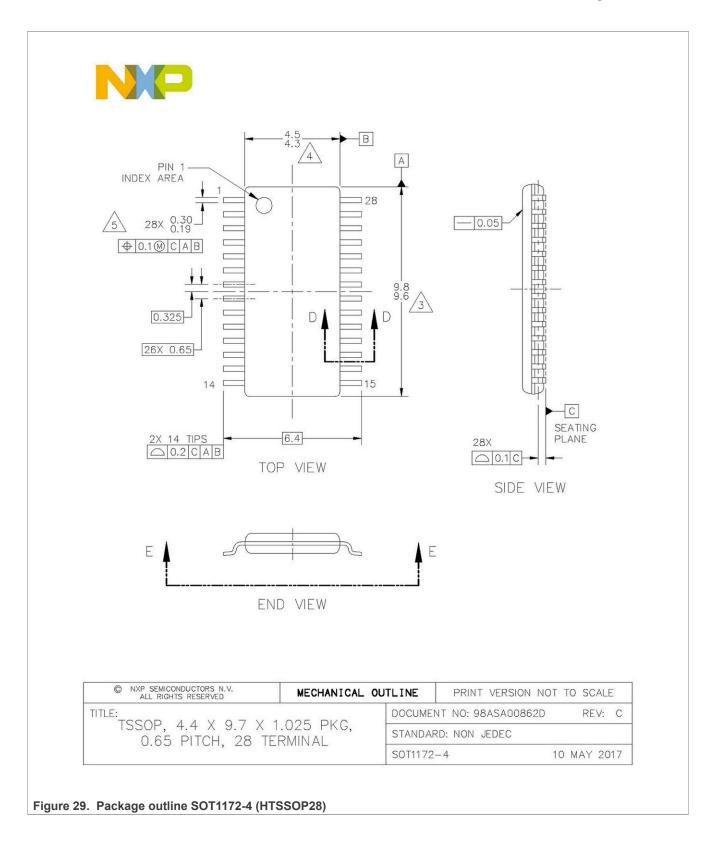

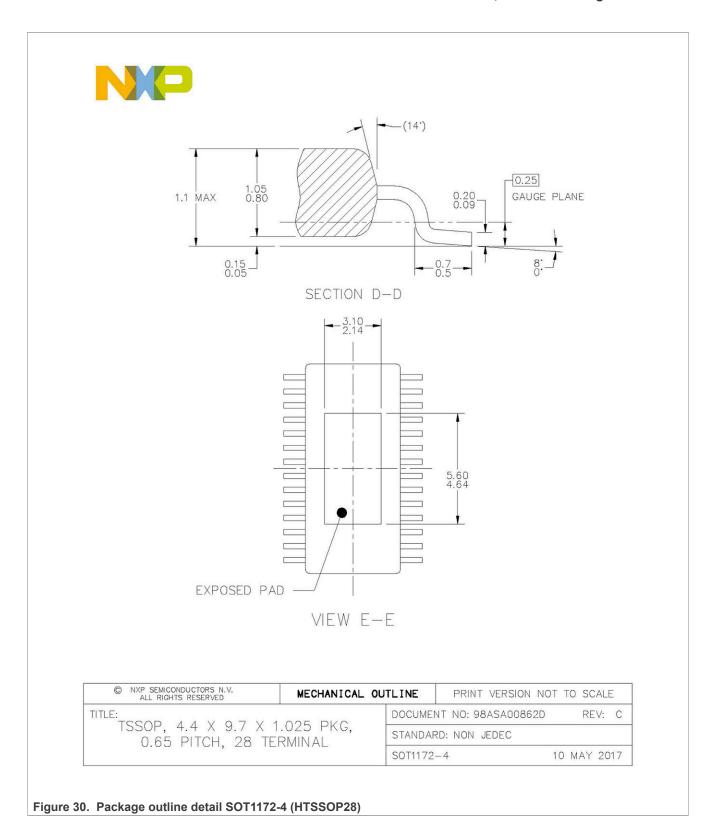

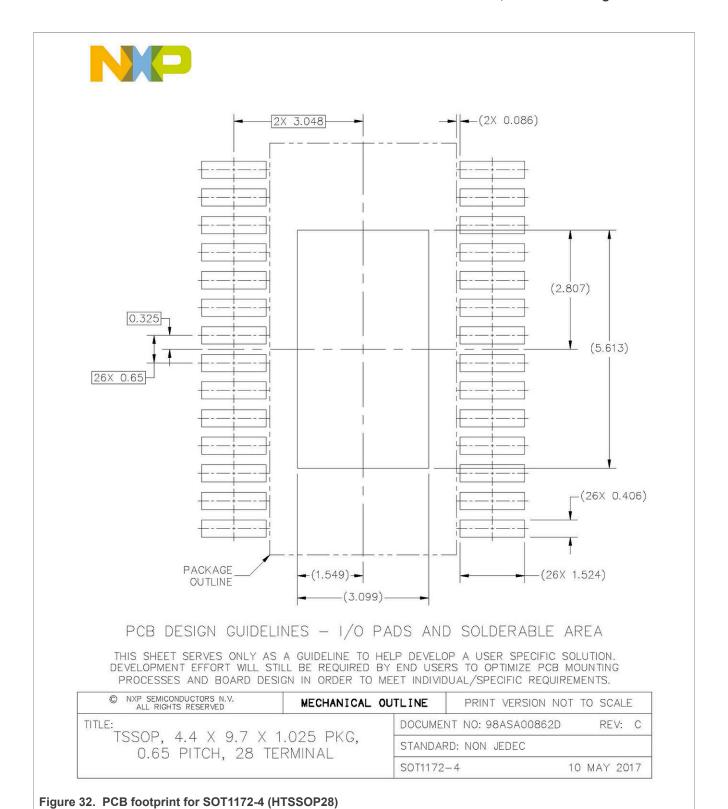

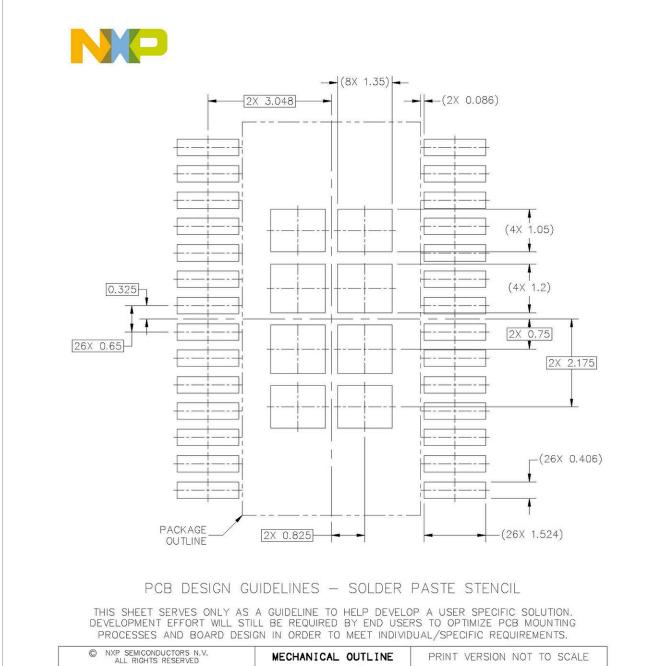

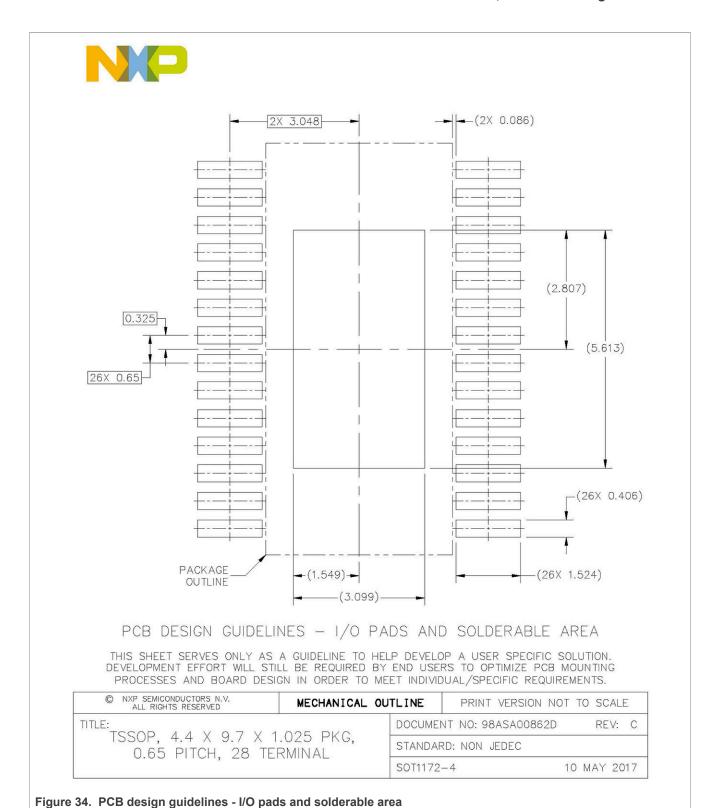

| MC33XS2410EL    | HTSSOP28 | Plastic thermal enhanced thin shrink small outline package; 28 leads; body width 4.4 mm; lead pitch 0.65 mm; exposed die pad | SOT1172-4 |  |  |

To order parts in tape and reel, add the R2 suffix to the part number.

Device is designed to operate with 12 V and 24 V bus/truck mission profiles. Maximum continuous voltage depends on application mission profile. PCB JEDEC 2s2p,  $T_{amb} \le 85$  °C,  $R_{th(j-a)} = 24$  °C/W (see thermal characteristics). Maximum SPI frequency can be reduced depending on output buffer configuration.

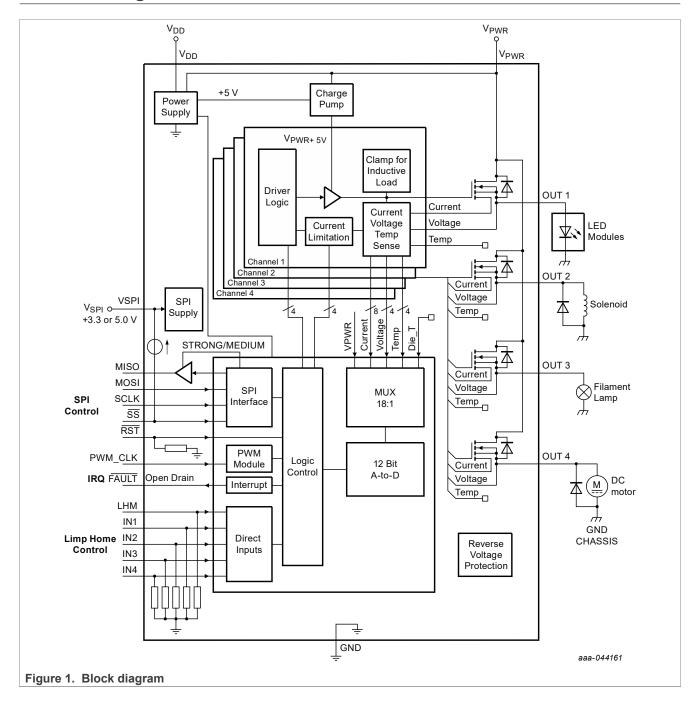

# 6 Block diagram

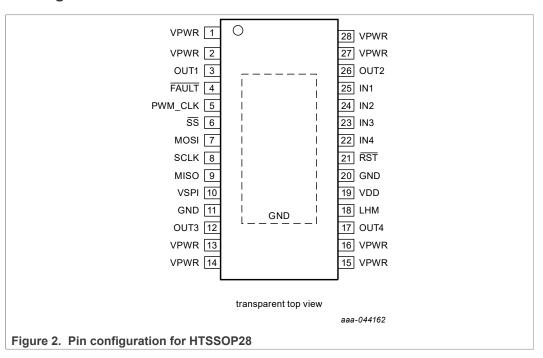

# 7 Pinning information

## 7.1 Pinning

## 7.2 Pin description

Table 3. Pin description

| Table 3. Pin description |                                    |        |                                                    |  |

|--------------------------|------------------------------------|--------|----------------------------------------------------|--|

| Symbol                   | Pin                                | Туре   | Description                                        |  |

| Supplies                 |                                    |        |                                                    |  |

| VPWR                     | 1, 2, 13,<br>14, 15, 16,<br>27, 28 | Power  | Power switch supply                                |  |

| VDD                      | 19                                 | Power  | Logic supply voltage                               |  |

| VSPI                     | 10                                 | Power  | Supply voltage for SPI                             |  |

| GND                      | 11, 20                             | Power  | Device ground                                      |  |

| Digital                  |                                    |        |                                                    |  |

| RST                      | 21                                 | Input  | Reset input; pulldown resistor                     |  |

| FAULT                    | 4                                  | Output | Interrupt output; open-drain output                |  |

| PWM_CLK                  | 5                                  | Input  | PWM module clock; internal pulldown current source |  |

| Serial peripheral        | interface                          |        |                                                    |  |

| SCLK                     | 8                                  | Input  | SPI clock; internal pulldown current source        |  |

| SS                       | 6                                  | Input  | SPI client select; pullup current source           |  |

| MOSI                     | 7                                  | Input  | SPI data input; pulldown current source            |  |

| MISO                     | 9                                  | Output | SPI data output; high-Z when inactive              |  |

|                          |                                    |        |                                                    |  |

NXP Semiconductors MC33XS2410

## Quad 100 m $\Omega$ / dual 50 m $\Omega,$ 3.0 V to 60 V high-side switch

Table 3. Pin description...continued

| Symbol            | Pin | Туре  | Description                               |

|-------------------|-----|-------|-------------------------------------------|

| Direct input pins |     |       |                                           |

| LHM               | 18  | Input | Limp home mode; active direct input       |

| IN1               | 25  | Input | Direct input 1; pulldown resistor         |

| IN2               | 24  | Input | Direct input 2; pulldown resistor         |

| IN3               | 23  | Input | Direct input 3; pulldown resistor         |

| IN4               | 22  | Input | Direct input 4; pulldown resistor         |

| Output switches   |     |       |                                           |

| OUT1              | 3   | Power | Output 1, connected to load (NMOS source) |

| OUT2              | 26  | Power | Output 2, connected to load (NMOS source) |

| OUT3              | 12  | Power | Output 3, connected to load (NMOS source) |

| OUT4              | 17  | Power | Output 4, connected to load (NMOS source) |

| Center pad        |     |       |                                           |

| _                 | GND | _     | Center pad [1]                            |

For enhanced thermal and electrical performance, the exposed center pad of the HTSSOP28 package should be soldered to board ground (and not to any other voltage level).

# 8 Functional description

### 8.1 Power supplies

The device is supplied by three sources: VPWR, VDD and VSPI.

- VPWR pins are the power supply for high side switch (HSS) and carry high current. They are connected to each drain of power NMOS.

- VDD pin is the power terminal to supply the internal circuits. If VDD voltage is lower than  $V_{DD\ UV}$  (3.95 V typ.), the device internal supply automatically switches to VPWR.

- VSPI supply line is used by the SPI port and has been designed for 3.3 V and 5.0 V logic level.

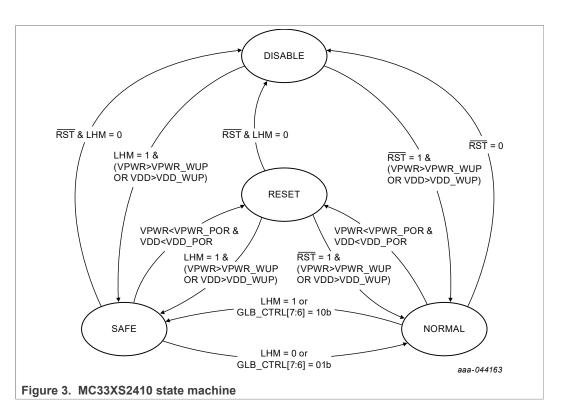

### 8.2 Operational mode

The MC33XS2410 has the following operation modes:

- Reset mode

- · Disable mode

- Normal mode

- · Safe mode

NXP Semiconductors MC33XS2410

Quad 100 m $\Omega$  / dual 50 m $\Omega$ , 3.0 V to 60 V high-side switch

#### 8.2.1 Reset mode

The reset mode is applied if VDD and VPWR are lower than their respective power-on reset values (VPWR\_POR and VDD\_POR). When the device is entering reset mode, all logic is reset, as well as SPI registers. Power NMOS is turned off and remains off state to protect the device. The device remains protected against overvoltage by active voltage clamp circuit (see <a href="Section 8.14.1" "Active voltage clamp")</a>.

#### 8.2.2 Disable mode

When entering disable mode, all outputs are turned off after  $\underline{T_{FAST\_TOFF\_D}}$  (see  $\underline{Table~56}$ ) and the current consumption is reduced to the very minimum (see parameter in  $\underline{Table~45}$ ). The device remains protected against overvoltage by active voltage clamp circuit. The disable mode is applied if  $\overline{RST}$  and LHM pins are pulled LOW, all registers configuration are reset to default values.

#### 8.2.3 Normal mode

The device wakes up and transits to normal mode if  $\overline{RST}$  pin goes from LOW to HIGH and VPWR > VPWR\_WUP. After a  $T_{WAKE\_UP}$  time, all functions are fully operational and the device is controlled by SPI port unless Safe mode is enabled. For details, see Figure 3.

#### 8.2.4 Safe mode

The device provides a safe mode via limp home mode LHM pin and INx input pin. In this mode all outputs OUTx are directly controlled by INx input logic signal. The ON\_OFFx bits in OUT1-4\_CTRL register programmed by SPI are therefore bypassed. During

MC33XS2410

safe mode all control register configurations are not reset and kept in memory. SPI communication is available for read access (diagnostics and ADC register are available).

The device switches to safe mode in the following case:

- If LHM pin is pulled to HIGH logic level

- If GLB\_CTRL[7:6] bits are set to b10 by SPI command

- If the watchdog timeout flag and transition in safe mode is enabled by bit WDT\_REG[6]

- If an overload protection (OLP) is detected and transition in safe mode is enabled by bit OLP\_CTRL[7]

- If a low-voltage condition (V<sub>SPI LV</sub>) is detected on VSPI supply pin

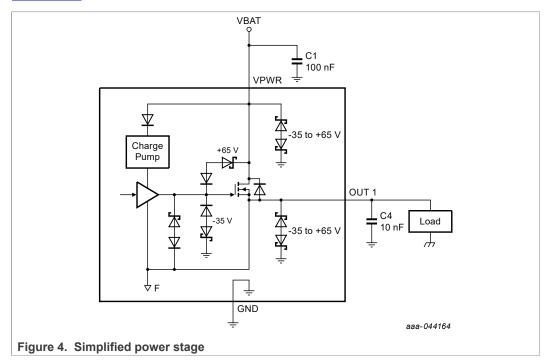

## 8.3 Power stages

Each HSS can be switched on via SPI or via direct input INx pin, when available. Output power stage is fully floating and can swing from Vpwr + 0.3 V to -35 V versus GND or Vpwr - 60 V (voltage is limited above that range). For details, see <a href="Section 8.14">Section 8.14</a> "Protection".

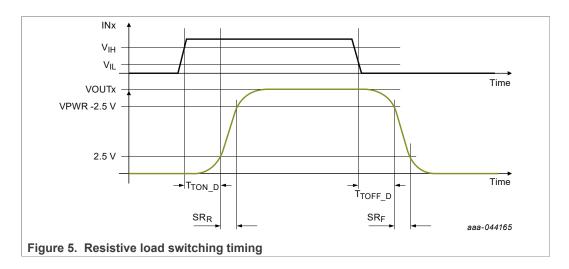

#### 8.3.1 Resistive load switch

A typical switching characteristic on resistive load is depicted in <u>Figure 5</u>. The risetime (SR<sub>R</sub>) and fall time (SR<sub>F</sub>) are adjustable in OUT1-4\_CTRL register in order to minimize EMI. Parameters are defined in <u>Table 46</u>.

#### 8.3.2 Minimum ON and OFF time

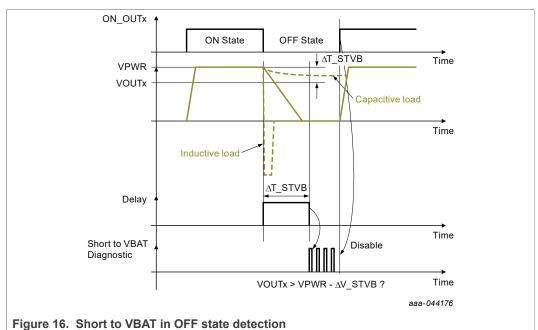

Open load in ON state and short to Vbat in OFF state features are respectively related to the ON and OFF state duration to provide their diagnostic.

Therefore, the minimum and maximum duty cycle can be limited depending on the PWM frequency used during operation.

To get these 2 diagnostics operational, the combination duty cycle ( $\delta$ ) / PWM frequency ( $F_{PWM}$ ) should respect the following conditions:

- Minimum duty cycle to get Open load in ON state operational:  $\delta_{MIN(\%)} = (T_{ON\_MIN} \times F_{PWM})$

- Maximum duty cycle to get short to Vbat in OFF state operational:  $\delta_{MAX(\%)} = 1 (T_{OFF\ MIN} \times F_{PWM})$

For more details about open load configuration in ON state, see <u>Section 8.13.3 "Open load in ON state"</u>. For more details about short to Vbat in OFF state, see <u>Section 8.13.1</u> "Short to VBAT in OFF state".

#### 8.3.3 Parallel mode

The outputs can be parallelized two by two (OUT1/2 and OUT3/4) to divide the output Rdson by 2 and drive higher currents. When one pair is set up in parallel mode, outputs must be connected together with a short and low impedance track (see <u>Section 9.1</u> "Circuit loops and tracks"). The current is split between the two power switches, the current limitation value is doubled and each current sense sees half of the total current.

If GLB\_CTRL[4] bit is set to 1, OUT1 and OUT2 are in parallel. All control bits are managed by OUT1 control bits while OUT2 control bits have no use. The IN2 direct input is OR logic with IN1 and directed to OUT1 ON/OFF Logic Control.

If GLB\_CTRL[3] bit is set to 1, OUT3 and OUT4 are in parallel. All control bits are managed by OUT3 control bits while OUT4 control bits have no use. The IN4 direct input is OR logic with IN3 and directed to OUT3 ON/OFF Logic Control.

#### 8.4 16-bit SPI interface

The SPI is used for communication with a controller and provides control and diagnostic functions. The device is configured as an SPI client.

MC33XS2410

All information provided in this document is subject to legal disclaimers.

© 2022 NXP B.V. All rights reserved.

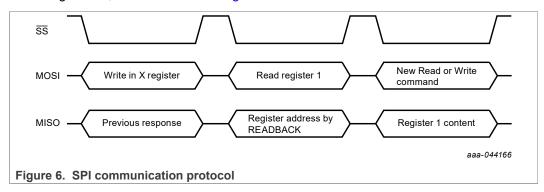

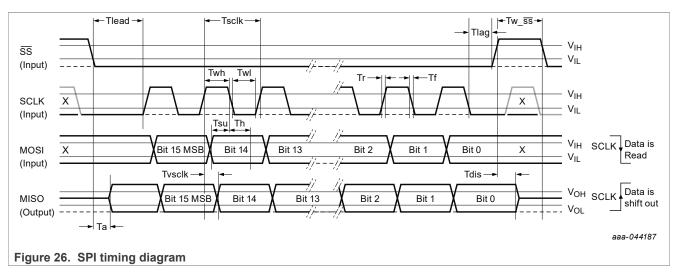

The serial peripheral interface (SPI) is a full duplex synchronous serial client interface, which uses four lines: MISO, MOSI, SCLK and  $\overline{SS}$ . Data is transferred by the lines MOSI and MISO at the rate given by SCLK. The falling edge of  $\overline{SS}$  indicates the beginning of an access.

Data is sampled on the MOSI line at the falling edge of SCLK and shifted out on the MISO line at the rising edge of SCLK. Each access must be terminated by a rising edge of  $\overline{SS}$ . In idle state, before and after the transfer, the base value of the clock SCLK is 0. A modulo 8 counter ensures that data is taken only when multiple of 8 bits have been transferred. The interface provides daisy chain capability.

#### 8.4.1 SPI communication protocol

Due to the SPI full duplex feature when a "Frame" is received by the device on MOSI line, simultaneously a "Frame" is transmitted on MISO line by the device. The MOSI line represents the frame sent from the MCU and MISO line is the answer provided by the device. The relationship between MOSI and MISO content during SPI communication is shown in <a href="Figure 6">Figure 6</a>. The "Previous Response" means that the "Frame" sent back depends on the command frame sent from the MCU before.

After a Write command the content of the next MISO frame reported by the device depends on the address selected by the READBACK register. After the reset by default, the register selected by READBACK is the global status register (GLB\_STA). The last written register can also be selected to be reported on the N+1 frame with Bit 6 = 1 on the READBACK register.

After a Read command the content of the next MISO frame reported by the device depends on the address selected in the Read command.

The device reads MOSI data on clock SCLK falling edge and shift out MISO data on the clock SCLK rising edge. So data is valid for reading by MCU on SCLK falling edge. For full timing details, see <u>Table 57</u> and <u>Figure 26</u>.

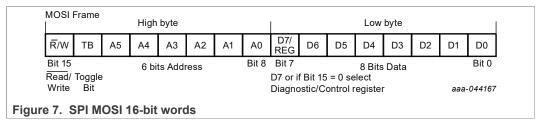

#### 8.4.2 SPI MOSI frame data IN

The SPI communication uses 2x8-bit words; see Figure 7 and Figure 8. In MISO frame, the most significant byte contents two control bits (Read/Write and Toggle) plus 6 bits of address. During a Write command (bit 15 = 1), the less significant byte contains 8 bits of data. During a Read command only bit 7 is used to select between Diagnostic or Control register.

Bit 15: R/W: Read/Write bit

0 = Read Diagnostic register or Control register (see bit 7)

1 = Write Control register

Bit 14: TB: Toggle bit

0 = Toggle bit to 0: TB = 0 1 = Toggle bit to 1: TB = 1

The 6 least significant bits in the high byte contains the address.

Bit 13-8: A5 to A0: Address to Read or Write

During a Write command (bit 15 = 1) the 8 bits of the low byte content the data.

Bit 7-0: D7 to D0: Data to Write

During a Read command (bit 15 = 0) the bit 7 selects the Diagnostic or Control register and bits 6-0 are not used.

Bit 7: D7/REG: Select Diagnostic or Control registers in read operation (bit 15 = 0)

0 = Select Diagnostic register

1 = Select Control register

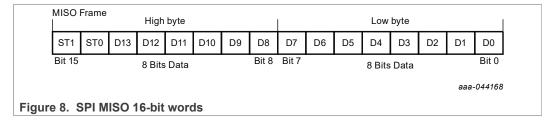

#### 8.4.3 SPI MISO frame data OUT

The 2 most significant bits (15-14) of the high byte are used to provide device status.

Bit 15-14: ST1-ST0: Status bits

00 = Nothing to report

01 = Warning event: WARN (maskable interrupt)

10 = Interrupt Request: IRQ (priority over WARN, maskable interrupt)

11 = Invalid SPI Communication: ISPI (high priority non-maskable interrupt)

The 6 least significant bits of the high byte content the highest significant bits data.

Bit 13-8: D13 to D8: Data read

The 8 bits of the low byte content the least significant bits data.

Bit 7-0: D7 to D0: Data read

MC33XS2410

## 8.4.4 SPI daisy chain configuration

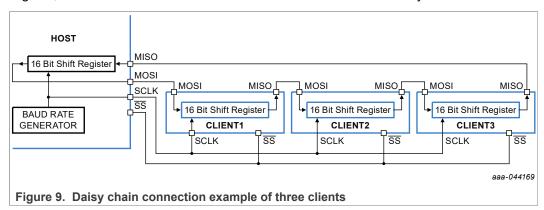

Devices can be daisy chained by connecting the MISO of the first client to the MOSI of the next client and so on; see <u>Figure 9</u>.

All devices have their  $\overline{SS}$  inputs connected to the same controller chip select so that they can be selected together. When n devices are daisy chained, then n SPI 16-bit word cycles must be executed to program all devices. This 16-bit shift register is a 2 byte shift register, therefore devices with modulo 8-bit can share the same daisy chain.

## 8.4.5 SPI communication error

In order to detect some SPI communication error the following functions are available:

- · SPI watchdog timer to detect a breakdown

- · Check a modulo 8-bit error in frame

- · Invalid address in MOSI frame

- Toggle bit error to improve the safety frame protocol

#### 8.4.5.1 SPI watchdog timer

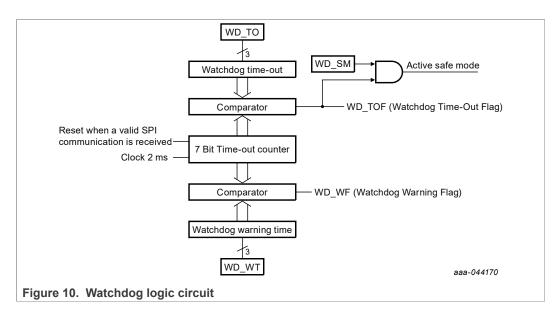

Watchdog purpose is to ensure that both device and MCU are active to continue operation. The SPI watchdog detects if there is a breakdown in the SPI communication with the controller. A timer is activated and is reset when a valid SPI communication is received. If no valid SPI communications are received within the specified period, the watchdog raises a flag to the logic. Two different timeout periods are available: the watchdog warning period and watchdog timeout period as depicted in <a href="Figure 10">Figure 10</a>. Both watchdog periods are configurable from 2.0 ms to 256 ms (see <a href="Figure 10">Table 5</a>).

When no valid SPI communication is received within the watchdog warning period, the bit ISR\_WARN[7] in interrupt service routine is set to 1 by WD\_WF flag.

When no valid SPI communication is received within the watchdog timeout period, the bit ISR\_IRQ[7] in interrupt service routine is set to 1 by WD\_TOF flag and if the bit WDT\_REG[6] = 1, the device transits in safe mode.

NXP Semiconductors MC33XS2410

## Quad 100 m $\Omega$ / dual 50 m $\Omega,$ 3.0 V to 60 V high-side switch

Table 4. Watchdog timer - control register (address 14h) bit description

| Address | Register | Bit      | Description                                                                                                                            |

|---------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| 14h     | WDT_REG  | 7 Unused |                                                                                                                                        |

|         |          | 6        | Transit in safe mode when watchdog timeout flag 0 = transit in safe mode is disabled 1 = transit in safe mode is enabled (reset value) |

|         |          | 5 to 3   | Watchdog timeout period (see <u>Table 5</u> )                                                                                          |

|         |          | 2 to 0   | Watchdog warning period (see <u>Table 5</u> )                                                                                          |

Table 5. Watchdog period

| Period |       |       |                       |

|--------|-------|-------|-----------------------|

| Value  | Time  | Value | Time                  |

| 000b   | 2 ms  | 100b  | 32 ms                 |

| 001b   | 4 ms  | 101b  | 64 ms                 |

| 010b   | 8 ms  | 110b  | 128 ms <sup>[1]</sup> |

| 011b   | 16 ms | 111b  | 256 ms <sup>[2]</sup> |

- [1] Reset value of watchdog warning period

- [2] Reset value of watchdog timeout period

#### 8.4.5.2 Wrong number of bits

This function monitors the number of bit that must be transmitted in a communication frame. If the number of clock pulses within  $\overline{SS}$  signal low state, not 0 or a multiple of 8, then the SPI frame is ignored and an invalid SPI communication ISPI code is generated. With this non-maskable ISPI code interrupt on the next SPI frame, MISO data reports an invalid SPI communication code.

#### 8.4.5.3 Invalid address

This function checks if each MOSI frame has a valid address. If the read or write address A0 to A5 in MOSI frame points to an unmapped address this wrong address is considered invalid and the SPI command is ignored. An invalid SPI communication ISPI code is generated. With this non-maskable ISPI code interrupt, MISO data reports an invalid SPI communication code in the next SPI frame.

#### 8.4.5.4 Toggle bit error

This feature improves safety of the system using SPI communication. When enabled, the TB bit (bit 14 in MOSI frame) must be toggled in each MOSI frame otherwise a SPI toggle bit error is detected and the SPI frame is ignored. So the SPI Toggle Bit Error (ISR\_IRQ[4]) is set to 1 in interrupt service routine. Depending on EN\_IRQ\_SPI[4] and EN\_IRQ\_PIN[4] bits an interrupt could be generated.

After the reset, by default the TB bit is 0. To avoid toggle bit error, once the feature is enabled, the first SPI command must be toggled with TB bit to 1.

## 8.5 Interrupt control logic

An interrupt can be generated to notify the controller that an event has occurred. This notification can be reported by the FAULT pin and or by SPI using ST1-ST0 bits status in each MISO frame. The FAULT open-drain output enables an immediate reporting and an interrupt sets pin FAULT = LOW. The SPI enables distinction between a warning event, an interrupt request or an invalid SPI communication error depending on ST1-ST0 bits status.

#### 8.5.1 Mask of interrupt register

Four registers configure which faults generate an interrupt as depicted in Table 6.

There are two sets of maskable interrupts: Warning even (WARN) and Interrupt Request (IRQ). Both the WARN and IRQ flags can be reported to SPI MISO bits status (see Section 8.4.3 "SPI MISO frame data OUT") and/or external /FAULT pin. In case both information are raised together, IRQ has priority over WARN.

Table 6. Mask of interrupt - control register (addresses 10h to 13h) bit description

| Address | Register   | Bit | Description                                               |

|---------|------------|-----|-----------------------------------------------------------|

| 10h     | EN_IRQ_SPI |     | SPI IRQ interrupt request; for each bit:                  |

|         |            |     | 0 = IRQ not active (reset value)                          |

|         |            |     | 1 = IRQ active                                            |

|         |            | 7   | Charge pump fault                                         |

|         |            | 6   | Unused                                                    |

|         |            | 5   | Watchdog timeout                                          |

|         |            | 4   | SPI toggle bit error                                      |

|         |            | 3   | The device transits to safe mode <sup>[1]</sup>           |

|         |            | 2   | overtemperature <sup>[2]</sup>                            |

|         |            | 1   | Current limit N retry reached or severe short-circuit [2] |

|         |            | 0   | Overload condition <sup>[2]</sup>                         |

MC33XS2410

**NXP Semiconductors** MC33XS2410

Quad 100 m $\Omega$  / dual 50 m $\Omega$ , 3.0 V to 60 V high-side switch

Table 6. Mask of interrupt - control register (addresses 10h to 13h) bit description continued

| Address | Register    | Bit | Description                                                                                         |

|---------|-------------|-----|-----------------------------------------------------------------------------------------------------|

| 11h     | EN_IRQ_PIN  |     | FAULT pin IRQ interrupt request; for each bit:  0 = IRQ not active (reset value)  1 = IRQ active    |

|         |             | 7   | Charge pump fault                                                                                   |

|         |             | 6   | Unused                                                                                              |

|         |             | 5   | Watchdog timeout                                                                                    |

|         |             | 4   | SPI toggle bit error                                                                                |

|         |             | 3   | The device transits to safe mode <sup>[1]</sup>                                                     |

|         |             | 2   | Overtemperature <sup>[2]</sup>                                                                      |

|         |             | 1   | Current limit N retry reached or severe short-circuit [2]                                           |

|         |             | 0   | Overload condition [2]                                                                              |

| 12h     | EN_WARN_SPI |     | SPI WARN interrupt request; for each bit: 0 = WARN not active (reset value) 1 = WARN active         |

|         |             | 7   | Watchdog warning                                                                                    |

|         |             | 6   | Overtemperature warning <sup>[2]</sup>                                                              |

|         |             | 5   | Overcurrent warning <sup>[2]</sup>                                                                  |

|         |             | 4   | undercurrent warning <sup>[2]</sup>                                                                 |

|         |             | 3   | Overvoltage warning <sup>[2]</sup>                                                                  |

|         |             | 2   | Undervoltage warning <sup>[2]</sup>                                                                 |

|         |             | 1   | VDD undervoltage <sup>[2]</sup>                                                                     |

|         |             | 0   | VPWR undervoltage <sup>[2]</sup>                                                                    |

| 13h     | EN_WARN_PIN |     | FAULT pin WARN interrupt request; for each bit:  0 = WARN not active (reset value)  1 = WARN active |

|         |             | 7   | Watchdog warning                                                                                    |

|         |             | 6   | Overtemperature warning <sup>[2]</sup>                                                              |

|         |             | 5   | Overcurrent warning <sup>[2]</sup>                                                                  |

|         |             | 4   | Undercurrent warning <sup>[2]</sup>                                                                 |

|         |             | 3   | Overvoltage warning <sup>[2]</sup>                                                                  |

|         |             | 2   | Undervoltage warning <sup>[2]</sup>                                                                 |

|         |             | 1   | VDD undervoltage warning <sup>[2]</sup>                                                             |

|         |             | 0   | VPWR undervoltage warning <sup>[2]</sup>                                                            |

Except when set by SPI command

At least one output reaches or exceeds the threshold

## 8.5.2 Interrupt service routines ISR

Two registers indicate when an interrupt occurs. The ISR\_IRQ register is dedicated for IRQ type interrupt event and ISR\_WARN register is dedicated for WARN type warning event; see <u>Table 7</u>.

Each bit in the ISR\_IRQ and ISR\_WARN registers is latched when a fault is generated. Each register ISR\_IRQ and ISR\_WARN is cleared by reading it.

Table 7. Interrupt service routine - diagnostics register (addresses 06h 07h) bit description

| Address | Register | Bit     | Description                                           |

|---------|----------|---------|-------------------------------------------------------|

| 06h     | ISR_IRQ  |         | ISR_IRQ interrupt status; for each bit:               |

|         |          |         | 0 = no interruption request (reset value)             |

|         |          |         | 1 = interruption is requested                         |

|         |          | 13 to 8 | Unused                                                |

|         |          | 7       | Charge pump fault                                     |

|         |          | 6       | Unused                                                |

|         |          | 5       | Watchdog timeout                                      |

|         |          | 4       | SPI toggle bit error                                  |

|         |          | 3       | The device transits to safe mode                      |

|         |          | 2       | Overtemperature                                       |

|         |          | 1       | Current limit N retry reached or severe short-circuit |

|         |          | 0       | Overload condition                                    |

| 07h     | ISR_WARN |         | ISR_WARN interrupt status; for each bit:              |

|         |          |         | 0 = no interruption request (reset value)             |

|         |          |         | 1 = interruption is requested                         |

|         |          | 13 to 8 | Unused                                                |

|         |          | 7       | Watchdog warning                                      |

|         |          | 6       | Overtemperature warning                               |

|         |          | 5       | Overcurrent warning                                   |

|         |          | 4       | Undercurrent warning                                  |

|         |          | 3       | Overvoltage warning                                   |

|         |          | 2       | Undervoltage warning                                  |

|         |          | 1       | VDD undervoltage                                      |

|         |          | 0       | VPWR undervoltage                                     |

## 8.6 Control register

The following table provides an overview of all user accessible control registers and available addressing space. All registers enable digital control of the device by SPI command. Control registers are 8-bits write and also read in order to check the content, if necessary. The default value is loaded during power-on reset.

Table 8. Control: 8-bits Read/Write registers

| Register [1] | Symbol      | Description                                                | Reset value                                       | Reference             |

|--------------|-------------|------------------------------------------------------------|---------------------------------------------------|-----------------------|

| 00h          | GLB_CTRL    | Global controls register                                   | 20h                                               | Section 8.6.1         |

| 01h          | READBACK    | Select which register is read back                         | 00h                                               | Section 8.6.2         |

| 02h          | OUT1-4_CTRL | Output control register, slew rate and turn ON/OFF control | 00h                                               | Section 8.6.3         |

| 03h          | IN_CTRL1    | Direct input control logic setup 1                         | 00h                                               | Section 8.6.4         |

| 04h          | IN_CTRL2    | Direct input control logic setup 2                         | 00h                                               | Section 8.6.4         |

| 05h          | PWM_CTRL1   | PWM module control register                                | 00h                                               | Section 8.7           |

| 06h          | PWM_CTRL2   | PWM module phase shift control                             | 00h                                               | Section 8.7           |

| 07h          | PWM_CTRL3   | PWM module control register                                | 00h                                               | Section 8.7           |

| 08h          | PWM_FREQ1   | PWM frequency setting output 1                             | 00h                                               | Section 8.7           |

| 09h          | PWM_FREQ2   | PWM frequency setting output 2                             | 00h                                               | Section 8.7           |

| 0Ah          | PWM_FREQ3   | PWM frequency setting output 3                             | 00h                                               | Section 8.7           |

| 0Bh          | PWM_FREQ4   | PWM frequency setting output 4                             | 00h                                               | Section 8.7           |

| 0Ch          | PWM_DC1     | PWM duty cycle control output 1                            | 00h                                               | Section 8.7           |

| 0Dh          | PWM_DC2     | PWM duty cycle control output 2                            | 00h                                               | Section 8.7           |

| 0Eh          | PWM_DC3     | PWM duty cycle control output 3                            | 00h                                               | Section 8.7           |

| 0Fh          | PWM_DC4     | PWM duty cycle control output 4                            | 00h                                               | Section 8.7           |

| 10h          | EN_IRQ_SPI  | IRQ type interrupt request by SPI                          | 00h                                               | Section 8.5.1         |

| 11h          | EN_IRQ_PIN  | IRQ type interrupt request by pin                          | 00h                                               | Section 8.5.1         |

| 12h          | EN_WARN_SPI | Warning type interrupt request by SPI                      | 00h                                               | Section 8.5.1         |

| 13h          | EN_WARN_PIN | Warning type interrupt request by FAULT pin                | 00h                                               | Section 8.5.1         |

| 14h          | WDT_REG     | Natchdog timer 7Eh                                         |                                                   | Section 8.4.5.1       |

| 15h          | M_SETUP     | leasurement setup: current range and timing 00h            |                                                   | <u>Section 8.12.1</u> |

| 16h          | C_CTRL      | Synchronous current mode and on-demand C and V             | ynchronous current mode and on-demand C and V 00h |                       |

| 17h          | WC_CTRL     | Warning current control                                    | 00h                                               | <u>Section 8.12.2</u> |

| 18h          | OCW_OUT1    | Overcurrent warning threshold output 1                     | FFh                                               | <u>Section 8.12.2</u> |

| 19h          | UCW_OUT1    | Undercurrent warning threshold output 1                    | 00h                                               | <u>Section 8.12.2</u> |

| 1Ah          | OCW_OUT2    | Overcurrent warning threshold output 2                     | FFh                                               | <u>Section 8.12.2</u> |

| 1Bh          | UCW_OUT2    | Undercurrent warning threshold output 2                    | 00h                                               | <u>Section 8.12.2</u> |

| 1Ch          | OCW_OUT3    | Overcurrent warning threshold output 3                     | FFh                                               | <u>Section 8.12.2</u> |

| 1Dh          | UCW_OUT3    | Undercurrent warning threshold output 3                    | 00h                                               | <u>Section 8.12.2</u> |

| 1Eh          | OCW_OUT4    | Overcurrent warning threshold output 4 FFh                 |                                                   | <u>Section 8.12.2</u> |

| 1Fh          | UCW_OUT4    | Undercurrent warning threshold output 4 00h                |                                                   | <u>Section 8.12.2</u> |

| 20h          | WV_CTRL     | Warning voltage control                                    | 00h                                               | <u>Section 8.12.4</u> |

| 21h          | OVW_OUT1    | Overvoltage warning threshold output 1                     | 00h                                               | Section 8.12.4        |

| 22h          | UVW_OUT1    | Undervoltage warning threshold output 1                    | 00h                                               | Section 8.12.4        |

| 23h          | OVW_OUT2    | Overvoltage warning threshold output 2                     | 00h                                               | Section 8.12.4        |

MC33XS2410

All information provided in this document is subject to legal disclaimers.

© 2022 NXP B.V. All rights reserved.

Table 8. Control: 8-bits Read/Write registers...continued

| Register [1] | Symbol    | Description                                                                               | Reset value                                 | Reference             |

|--------------|-----------|-------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------|

| 24h          | UVW_OUT2  | Undervoltage Warning threshold output 2                                                   | Undervoltage Warning threshold output 2 00h |                       |

| 25h          | OVW_OUT3  | Overvoltage warning threshold output 3                                                    | 00h                                         | Section 8.12.4        |

| 26h          | UVW_OUT3  | Undervoltage warning threshold output 3                                                   | 00h                                         | Section 8.12.4        |

| 27h          | OVW_OUT4  | Overvoltage warning threshold output 4                                                    | 00h                                         | <u>Section 8.12.4</u> |

| 28h          | UVW_OUT4  | Undervoltage warning threshold output 4                                                   | 00h                                         | <u>Section 8.12.4</u> |

| 29h          | TEMP_WT   | Common temperature warning threshold                                                      | A5h                                         | Section 8.12.6        |

| 2Ah          | ΔV_STVB   | Voltage offset short to VBAT in OFF state                                                 | 04h                                         | <u>Section 8.13.1</u> |

| 2Bh          | BT_STVB   | Blanking delay short to VBAT in OFF state                                                 | 70h                                         | <u>Section 8.13.1</u> |

| 2Ch          | OPD_CTRL1 | Open load detection control in ON state output 1 and 2 and clear OUT1_LF and OUT2_LF bits | 24h                                         | Section 8.13.3        |

| 2Dh          | OPD_CTRL2 | Open load detection control in ON state output 3 and 4 and clear OUT3_LF and OUT4_LF bits | 24h                                         | Section 8.13.3        |

| 2Eh          | I_OLD1    | Open load threshold in ON state output 1                                                  | 03h                                         | <u>Section 8.13.3</u> |

| 2Fh          | I_OLD2    | Open load threshold in ON state output 2                                                  | 03h                                         | <u>Section 8.13.3</u> |

| 30h          | I_OLD3    | Open load threshold in ON state output 3                                                  | 03h                                         | <u>Section 8.13.3</u> |

| 31h          | I_OLD4    | Open load threshold in ON state output 4                                                  | 03h                                         | <u>Section 8.13.3</u> |

| 32h          | ACL_CTRL1 | Active current limit control 1                                                            | 6Dh                                         | <u>Section 8.14.5</u> |

| 33h          | ACL_CTRL2 | Active current limit control 2                                                            | 2Dh                                         | Section 8.14.5        |

| 34h          | SSC_CTRL  | Severe short-circuit control                                                              | 00h                                         | Section 8.14.6        |

| 35h          | OLP_CTRL  | Overload protection control                                                               | 18h                                         | Section 8.14.7        |

| 36h          | OCL_OUT1  | Overload current level threshold output 1                                                 | CCh                                         | <u>Section 8.14.7</u> |

| 37h          | OCL_OUT2  | Overload current level threshold output 2                                                 | CCh                                         | <u>Section 8.14.7</u> |

| 38h          | OCL_OUT3  | Overload current level threshold output 3                                                 | CCh                                         | <u>Section 8.14.7</u> |

| 39h          | OCL_OUT4  | Overload current level threshold output 4                                                 | CCh                                         | <u>Section 8.14.7</u> |

| 3Ah          | PI_CTRL1  | Proportional-integral regulation compensation setup                                       | 00h                                         | Section 8.8           |

| 3Bh          | PI_CTRL2  | Dither PI setup                                                                           | 00h                                         | Section 8.8           |

| 3Ch          | I_SET1    | Current set-point output 1                                                                | 00h                                         | Section 8.8           |

| 3Dh          | I_SET2    | Current set-point output 2                                                                | 00h                                         | Section 8.8           |

| 3Eh          | I_SET3    | Current set-point output 3                                                                | 00h                                         | Section 8.8           |

| 3Fh          | I_SET4    | Current set-point output 4                                                                | 00h                                         | Section 8.8           |

<sup>[1]</sup> To address control register bit 7 (D7/REG) = 1 in 16-bits MOSI frame.

#### 8.6.1 Global control

The global control register GLB\_CTRL is used to:

- · Transit in normal or safe mode

- · Configure output in parallel

- Optimize EMI by selecting the MISO output buffer impedance

- · Change the oscillator spread spectrum

- Configure the direct inputs logic level.

**Transit mode:** Writing in bits GLB\_CTRL[7:6] enables transition from normal to safe mode or vice versa. The bit values are not retained and are cleared once transition is done.

Reset: Writing 11b in bits GLB\_CTRL[7:6] executes a complete reset of the device.

**Drive strength:** The bit GLB\_CTRL[5] configures the MISO output buffer impedance between MEDIUM and STRONG strength in order to optimize EMI.

**Parallel mode:** The bits GLB\_CTRL[4:3] configure independently the OUT1 + OUT2 and OUT3 + OUT4 in parallel; for details see <u>Section 8.3.3 "Parallel mode"</u>.

**Oscillator modulation frequency:** The bits GLB\_CTRL[2:1] help improve EMI by spreading the 42 MHz oscillator's frequency.

**Direct input logic level:** The bit GLB\_CTRL[0] help change the input logic level for LHM, IN1, IN2, IN3 and IN4 pins.

Table 9. Global control - control register (address 00h) bit description

| Address | Register | Bit                                                    | Description                               |

|---------|----------|--------------------------------------------------------|-------------------------------------------|

| 00h     | GLB_CTRL | 7 to 6                                                 | transit mode and reset                    |

|         |          |                                                        | 00 = no transition asked (reset value)    |

|         |          |                                                        | 01 = transit to normal mode               |

|         |          |                                                        | 10 = transit to safe mode                 |

|         |          |                                                        | 11 = reset                                |

|         |          | 5                                                      | drive strength (MISO)                     |

|         |          |                                                        | $0 = STRONG$ configuration (50 $\Omega$ ) |

|         |          | 1 = MEDIUM configuration (200 $\Omega$ ) (reset value) |                                           |

|         |          | 4                                                      | parallel mode for OUT1 and OUT2           |

|         |          |                                                        | 0 = OUT1-2 are independent (reset value)  |

|         |          | 1 = OUT1-2 are in parallel                             |                                           |

|         |          | 3                                                      | parallel mode for OUT3 and OUT4           |

|         |          |                                                        | 0 = OUT3-4 are independent (reset value)  |

|         |          |                                                        | 1 = OUT3-4 are in parallel                |

|         |          | 2                                                      | oscillator modulation frequency; F_MOD    |

|         |          |                                                        | 0 = disable (reset value)                 |

|         |          |                                                        | 1 = enable                                |

|         |          | 1                                                      | frequency modulation band; F_DEV          |

|         |          |                                                        | 0 = F1_DEV selected (reset value)         |

|         |          |                                                        | 1 = F2_DEV selected                       |

|         |          | 0                                                      | direct input logic level                  |

|         |          |                                                        | 0 = AUTOMOTIVE input level (reset value)  |

|         |          |                                                        | 1 = CMOS input logic level                |

MC33XS2410

#### 8.6.2 Readback

After a Write command, the content of the next MISO frame reported by the device depends on the address selected by the READBACK register. On first SPI communication after reset, the first register selected by READBACK and sent on the MISO line is the Global Status GLB\_STA (00h); for details see Section 8.4.1 "SPI communication protocol". This is also possible to read the last written register by enabling the automatic mode with bit READBACK[6] = 1. In that case, each MISO frame will report the content of the register configured in the previous SPI access.

Table 10. Readback - control register (address 01h) bit description

| Address | Register | Bit    | Description                                                                                         |

|---------|----------|--------|-----------------------------------------------------------------------------------------------------|

| 01h     | READBACK | 7      | Select Diagnostic or Control register  0 = Diagnostics bank register [1]  1 = Control bank register |

|         |          | 6      | Automatic 0 = No action (Default) 1 = Select automatically last written register (Control)          |

|         |          | 5 to 0 | Select register address <sup>[2]</sup>                                                              |

<sup>[1]</sup> By default, select diagnostics bank register

## 8.6.3 Output control

Outputs are controlled by OUT1-4\_CTRL (02h) register that enables turn-on, turn-off and selects the switching slew rate for each output.

**Slew rate:** The bits OUT1-4\_CTRL[7:4] configure the power NMOS switching slew rate. Defined slew rates minimize EMI during PWM operation but increase the switching losses and limit the frequency operation.

Table 11. Output control - control register (address 02h) bit description

| Address | Register    | Bit | Description                                                                                  |

|---------|-------------|-----|----------------------------------------------------------------------------------------------|

| 02h     | OUT1-4_CTRL |     | Output slew rate control for T_SRx bit  0 = slow slew rate (reset value)  1 = fast slew rate |

|         |             | 7   | T_SR4 output 4                                                                               |

|         |             | 6   | T_SR3 output 3                                                                               |

|         |             | 5   | T_SR2 output 2 <sup>[1]</sup>                                                                |

|         |             | 4   | T_SR1 output 1                                                                               |

|         |             |     | Output ON / OFF control for ON_OFFx bit  0 = OUTx is OFF (reset value)  1 = OUTx is ON [2]   |

|         |             | 3   | ON_OFF4 output 4 <sup>[1]</sup>                                                              |

|         |             | 2   | ON_OFF3 output 3                                                                             |

|         |             | 1   | ON_OFF2 output 2 <sup>[1]</sup>                                                              |

|         |             | 0   | ON_OFF1 output 1                                                                             |

<sup>[2]</sup> By default, the 5 bits = 0000b and select GLB\_STA register

- [1] This bit is non-active when this output is configured in parallel mode.

- [2] Unless latch-off by OUTx\_LF logic signal

#### 8.6.4 Direct input control

The device can be controlled by direct input in the following case:

- · In safe mode

- In normal mode if enabled by bits IN\_CTRL1[3:0]

Direct inputs are used to directly turn-on or turn-off the outputs. PWM signal can be applied within the limits of minimum on-time and off-time to guarantee diagnostic feature; for details see <u>Section 8.3.2 "Minimum ON and OFF time"</u>.

Two registers IN\_CTRL1 and IN\_CTRL2 configure the direct input:

**Deglitch time:** By default INx input is provided with a deglitch time of 200  $\mu$ s typ. ( $T_{IN\ DGL\ DI}$ ). This deglitch time can be disabled with IN\_CTRL[7:4] bits

**Input control:** Bits IN\_CTRL1[3:0] control the output by applying direct input logic signal to INx pins.

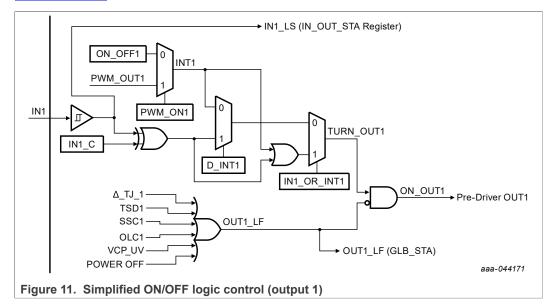

**OR logic with SPI control:** Bits IN\_CTRL2[7:4] enable an OR logic with internal INTx logic signal from ON / OFF SPI control or PWM module; see <u>Figure 11</u>.

Active logic level: Bits IN\_CTRL2[3:0] configure the input logic as active high or low.

Note that GLB\_CTRL[0] enables to change the input logic level: see <u>Section 8.6.1</u> "Global control".

NXP Semiconductors MC33XS2410

Quad 100 m $\Omega$  / dual 50 m $\Omega$ , 3.0 V to 60 V high-side switch

Table 12. Direct input control - control register (address 03h, 04h) bit description

| Address | Register | Bit | Description                                                                                               |

|---------|----------|-----|-----------------------------------------------------------------------------------------------------------|

| 03h     | IN_CTRL1 |     | Disable deglitch time                                                                                     |

|         |          |     | 0 = enable (reset value)<br>1 = disable                                                                   |

|         |          | 7   | DDT_IN4 output 4 <sup>[1]</sup>                                                                           |

|         |          | 6   | DDT_IN3 output 3                                                                                          |

|         |          | 5   | DDT_IN2 output 2 [1]                                                                                      |

|         |          | 4   | DDT_IN1 output 1                                                                                          |

|         |          |     | Output is controlled by                                                                                   |

|         |          |     | <ul><li>0 = OUTx is controlled by SPI (reset value)</li><li>1 = OUTx is controlled by INx input</li></ul> |

|         |          | 3   | D_IN4 output 4 [1]                                                                                        |

|         |          | 2   | D_IN3 output 3                                                                                            |

|         |          | 1   | D_IN2 output 2 <sup>[1]</sup>                                                                             |

|         |          | 0   | D_IN1 output 1                                                                                            |

| 04h     | IN_CTRL2 |     | OR Logic with internal INTx logic signal                                                                  |

|         |          |     | 0 = OR logic is disabled (reset value)                                                                    |

|         |          |     | 1 = INx input logic is OR logic with INTx                                                                 |

|         |          | 7   | IN4_OR_INT4 output 4 [1]                                                                                  |

|         |          | 6   | IN3_OR_INT3 output 3                                                                                      |

|         |          | 5   | IN2_OR_INT2 output 2 <sup>[1]</sup>                                                                       |

|         |          | 4   | IN1_OR_INT1 output 1                                                                                      |

|         |          |     | Active logic level: INx_C bit                                                                             |

|         |          |     | 0 = INx input logic is not invert (reset value)                                                           |

|         |          |     | 1 = INx input logic is complemented                                                                       |

|         |          | 3   | IN4_C output 4 <sup>[1]</sup>                                                                             |

|         |          | 2   | IN3_C output 3                                                                                            |

|         |          | 1   | IN2_C output 2 [1]                                                                                        |

|         |          | 0   | IN1_C output 1                                                                                            |

|         |          |     |                                                                                                           |

<sup>[1]</sup> This bit is non-active when the output is configured in parallel mode.

## 8.7 Pulse-width Modulation module (PWM)

The device integrates a PWM module with an 8-bit duty cycle capability per output. Reference frequency signal for PWM module can be either internal or external. When all outputs have same frequency they can be phase shifted by 0°, 90°, 180° or 270°. The internal clock drive loads at different frequencies typically from 0.5 Hz up to 2.048 kHz.

**PWM clock reference:** The internal reference clock has an accuracy of  $\pm$  5 % over temperature and voltage operating range. When the bit PWM\_CTRL1[7] is set high, the external clock source is selected and a clock signal (512 kHz typ.) should be applied to the PWM\_CLK input. A clock fail circuit is monitoring the PWM\_CLK clock and detects if the signal is toggled within  $T_{OUT}$  timeout (100  $\mu$ s typ.). If a clock fail is detected the

device clears the PWM\_CTRL1[7] bit and transits to internal PWM\_CLK clock signal. By reading the PWM\_CTRL1[7] bit the MCU can check if the external clock failed.

**PWM synchronization:** To start the PWM operation at a known point in time the bit PWM\_CTRL1[6] shall be set high. Once PWM\_CTRL1[6] is set high all PWM 8 bits counter reset when SS transits from 0 to 1 at the end of the 16-bit SPI frame. The PWM\_CTRL1[6] bit value is not retained and always reads 0.

**PWM output polarity:** For each PWM output the polarity can be selected by PWM\_POL\_x bits in PWM\_CTRL1 register.

**PWM frequency:** For the four outputs the PWM\_FREQx registers enable to configure the frequency typically from 0.5 Hz to 2.048 kHz. The 2 most significant bits (7-6) select the factor for division by 1, 4, 16, or 64. The 6 least significant bits (5-0) select the frequency step by step; see Table 13.

When one of the I\_SETx registers is enabled (≠ 00h) the PWMx module is rerouting to clock the PI loop module.

**PWM phase shift:** PWM\_CTRL2 register configures the phase shift by adding a delay of 0, 1/4, 1/2 or 3/4 of PWM period before turning ON PWM output signal. This contributes to improve EMI by shifting the output turn ON and spreading the inrush current.

**PWM duty cycle**: Duty cycle is defined by  $\delta$  = (n+1) / 256 where n is a decimal number from 0 to 255 configured by PWM\_DCx registers. Thus the duty cycle is adjustable from 0.39 % to 100 %. It is important to note that the on-time (T<sub>ON</sub>) is defined by: T<sub>ON</sub> = ( $\delta$  / F<sub>PWM</sub>) where  $\delta$  is the duty cycle and F<sub>PWM</sub> the PWM frequency. To guarantee diagnostic feature, T<sub>ON</sub> and also T<sub>OFF</sub> which is the off-time must be within the limits; for details see Section 8.3.2 "Minimum ON and OFF time".

**PWM control:** PWM\_CTRL3 register allows each PWM channel to be turned ON or OFF. Note that PWM operation gets the priority against ON\_OFFx bits from OUT1-4\_CTRL.

Table 13. PWM module control - control register (address 05h to 07h) bit description

| Address | Register  | Bit                         | Description                              |

|---------|-----------|-----------------------------|------------------------------------------|

| 05h     | PWM_CTRL1 | 7                           | Select PWM clock signal source           |

|         |           |                             | 0 = internal clock signal (reset value)  |

|         |           |                             | 1 = external clock input PWM_CLK pin     |

|         |           | 6                           | PWM synchronization                      |

|         |           | 0 = no action (reset value) |                                          |

|         |           |                             | 1 = reset PWM 8 bits counter             |

|         |           |                             | PWM output polarity                      |

|         |           |                             | 0 = Signal is non-inverted (reset value) |

|         |           |                             | 1 = Signal is inverted                   |

|         |           | 5                           | PWM_POL_4 output 4 <sup>[1]</sup>        |

|         |           | 4                           | PWM_POL_3 output 3                       |

|         |           | 3                           | PWM_POL_2 output 2 [1]                   |

|         |           | 2                           | PWM_POL_1 output 1                       |

|         |           | 1                           | unused                                   |

|         |           | 0                           | unused                                   |

NXP Semiconductors MC33XS2410

Quad 100 m $\Omega$  / dual 50 m $\Omega$ , 3.0 V to 60 V high-side switch

Table 13. PWM module control - control register (address 05h to 07h) bit description...continued

| Address    | Register  | Bit    | Description                                                              |

|------------|-----------|--------|--------------------------------------------------------------------------|

| 06h        | PWM_CTRL2 |        | PWM Phase shift control                                                  |

|            |           |        | 00 = 0° (reset value)                                                    |

|            |           |        | 01 = 90°                                                                 |

|            |           |        | 10 = 180°                                                                |

|            |           |        | 11 = 270°                                                                |

|            |           | 7 to 6 | PHA_4 output 4 [1]                                                       |

|            |           | 5 to 4 | PHA_3 output 3                                                           |

|            |           | 3 to 2 | PHA_2 output 2 [1]                                                       |

|            |           | 1 to 0 | PHA_1 output 1                                                           |

| 07h        | PWM_CTRL3 |        | enable PWM output                                                        |

|            |           |        | 0 = disable (reset value)                                                |

|            |           |        | 1 = enable                                                               |

|            |           | 7      | PWM_ON4 output 4 <sup>[1]</sup>                                          |

|            |           | 6      | PWM_ON3 output 3                                                         |

|            |           | 5      | PWM_ON2 output 2 [1]                                                     |

|            |           | 4      | PWM_ON1 output 1                                                         |

|            |           | 3 to 0 | unused                                                                   |

| 08h to 0Bh | PWM_FREQx | 7 to 6 | PWM Frequency range and step                                             |

|            |           |        | 00 = 0.5 Hz steps from 0.5 Hz to 32 Hz                                   |

|            |           |        | 01 = 2 Hz steps from 2 Hz to 128 Hz                                      |

|            |           |        | 10 = 8 Hz steps from 8 Hz to 512 Hz                                      |

|            |           |        | 11 = 32 Hz steps from 32 Hz to 2048 Hz                                   |

|            |           | 5 to 0 | Frequency = (code + 1) x steps                                           |

|            |           |        | Example to get 100 Hz in range 2 Hz to 128 Hz: code = ((100/2) - 1) = 49 |

| 0Ch to 0Fh | PWM_DCx   | 7 to 0 | Internal PWM duty cycle for specified x output:                          |

|            |           |        | 00h (reset value) = 0.39 % to FFh = 100 %                                |

|            |           |        | Example to get $\delta = 25 \%$ code = $(0.25 \times 256) - 1 = 63$      |

<sup>[1]</sup> This bit is non-active when the output is configured in parallel mode.

## 8.8 PI PWM closed loop current regulation

The device integrates a digital proportional-integral controller (PI controller) to regulate a constant current for Proportional Solenoid Valve (PSV) with 12-bits PWM resolution per output. For each output the desired set-point is programmable by 8-bits register up to 3.2 A. In parallel mode, the regulated current is multiplied by 2 compared to the current set point. Reference frequency signal for PWM module can be either internal or external signal. Each output can be phase shifted 0, 90, 180 or 270 ° from the internal PWM signal. To control the closed loop regulation the duty cycle and feedback current can be monitored; see Table 17.

**Regulated current:** For each output the current set point is programmable by I\_SETx register by step of 12.5 mA. The feedback current is sampling a Ton/2. When the I\_SETx is cleared the closed loop regulation is disabled.

MC33XS2410

All information provided in this document is subject to legal disclaimers.

© 2022 NXP B.V. All rights reserved.

**Loop stability:** PI\_CTRL1 register configures the loop regulation criteria and select the appropriate proportional gain KP factor and integral gain KI factor.

**Dither signal:** PI\_CTRL2 register allows the user to program a dither signal. The Amplitude D\_AMP of each step is 4 bits programmable where LSB  $\approx$  4.88 mA (= 5.0 A / 1023). The time N\_PI\_PWM of each step is 4 bits programmable PI\_PWM\_F clock count. So the dither period = (8 \* N\_PI\_PWM) / PI output frequency.

Table 14. PI module setting - control register (address 3Ah to 3Fh) bit description

| Address    | Register | Bit    | Description                                                                                                                                       |

|------------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 3Ah        | PI_CTRL1 | 7 to 4 | proportional gain KP factor; see Table 15                                                                                                         |

|            |          | 3 to 0 | integral gain KI factor, see <u>Table 16</u>                                                                                                      |

| 3Bh        | PI_CTRL2 | 7 to 4 | setup the dither amplitude: D_AMP  0000b = disable (reset value)  0001b = 1 x 4.88 mA  D_AMP = code x 4.88 mA                                     |

|            |          | 3 to 0 | setup the dither N_PI_PWM time  0000b = disable (reset value)  0001b = 1x PWM Div by 2 <sup>10</sup> N_PI_PWM = code x PWM Div by 2 <sup>10</sup> |

| 3Ch to 3Fh | n I_SETx | 7 to 0 | current set-point for output x (OUT1 to OUT4)  00h = disable  08h = 100 mA (reset value)  I_SET1 = code x 12.5 mA (LSB)                           |

Table 15. Proportional gain KP factor

| KP factor            | KP factor            |       |                      |       |                      |       |                      |

|----------------------|----------------------|-------|----------------------|-------|----------------------|-------|----------------------|

| Value                | Gain                 | Value | Gain                 | Value | Gain                 | Value | Gain                 |

| 0000b <sup>[1]</sup> | 0.13 A <sup>-1</sup> | 0100b | 1.07 A <sup>-1</sup> | 1000b | 2.27 A <sup>-1</sup> | 1100b | 4.28 A <sup>-1</sup> |

| 0001b                | 0.27 A <sup>-1</sup> | 0101b | 1.34 A <sup>-1</sup> | 1001b | 2.67 A <sup>-1</sup> | 1101b | 4.87 A <sup>-1</sup> |

| 0010b                | 0.53 A <sup>-1</sup> | 0110b | 1.51 A <sup>-1</sup> | 1010b | 3.21 A <sup>-1</sup> | 1110b | 5.34 A <sup>-1</sup> |

| 0011b                | 0.80 A <sup>-1</sup> | 0111b | 1.87 A <sup>-1</sup> | 1011b | 3.74 A <sup>-1</sup> | 1111b | 5.90 A <sup>-1</sup> |

<sup>[1]</sup> Reset value

Table 16. Integral gain KP factor

| KI factor            |                                      |       |                                      |       |                                      |       |                                      |

|----------------------|--------------------------------------|-------|--------------------------------------|-------|--------------------------------------|-------|--------------------------------------|

| Value                | Gain                                 | Value | Gain                                 | Value | Gain                                 | Value | Gain                                 |

| 0000b <sup>[1]</sup> | 0.03 A <sup>-1</sup> s <sup>-1</sup> | 0100b | 0.15 A <sup>-1</sup> s <sup>-1</sup> | 1000b | 0.33 A <sup>-1</sup> s <sup>-1</sup> | 1100b | 0.77 A <sup>-1</sup> s <sup>-1</sup> |

| 0001b                | 0.08 A <sup>-1</sup> s <sup>-1</sup> | 0101b | 0.17 A <sup>-1</sup> s <sup>-1</sup> | 1001b | 0.45 A <sup>-1</sup> s <sup>-1</sup> | 1101b | 0.88 A <sup>-1</sup> s <sup>-1</sup> |

| 0010b                | 0.11 A <sup>-1</sup> s <sup>-1</sup> | 0110b | 0.22 A <sup>-1</sup> s <sup>-1</sup> | 1010b | 0.56 A <sup>-1</sup> s <sup>-1</sup> | 1110b | 0.98 A <sup>-1</sup> s <sup>-1</sup> |

| 0011b                | 0.13 A <sup>-1</sup> s <sup>-1</sup> | 0111b | 0.27 A <sup>-1</sup> s <sup>-1</sup> | 1011b | 0.67 A <sup>-1</sup> s <sup>-1</sup> | 1111b | 1.09 A <sup>-1</sup> s <sup>-1</sup> |

<sup>[1]</sup> Reset value

MC33XS2410

All information provided in this document is subject to legal disclaimers.

© 2022 NXP B.V. All rights reserved.

Table 17. PI module measurement – diagnostic register (address 18h to 23h) bit description

| Address    | Register | Bit    | Description                                    |

|------------|----------|--------|------------------------------------------------|

| 27h to 2Ah | PI_DCx   |        | PI PWM duty cycle value OUT1 to OUT4           |

|            |          | 9 to 0 | 000h = 0 %<br>3FFh = 100 %                     |

| 2Bh to 2Eh | FB_IOUTx |        | Feedback current measure at Ton/2 OUT1 to OUT4 |

|            |          | 9 to 0 | 000h = 0 A<br>3FFh = 5.0 A                     |

## 8.9 Diagnostic register

The diagnostic registers enable to readout the device state and to provide detailed information on each output, supply and direct input. Diagnostic registers can be obtained by reading data from the relevant 14-bit read-only registers; see <u>Table 18</u>. Whatever the register read the 2 most significant bits (15-14) of the high byte are used to provide device status; see <u>Section 8.4.3 "SPI MISO frame data OUT"</u>.

Table 18. Diagnostic: 14-bits Read only register

| Register [1] | Symbol     | Description                                   | Reference             |

|--------------|------------|-----------------------------------------------|-----------------------|

| 00h          | GLB_STA    | Global status                                 | Section 8.10.1        |

| 01h          | IN_OUT_STA | Direct input and output logic state reporting | Section 8.10.2        |

| 02h          | OUT1_STA   | Bits status of OUT1                           | <u>Section 8.10.3</u> |

| 03h          | OUT2_STA   | Bits status of OUT2                           | <u>Section 8.10.3</u> |

| 04h          | OUT3_STA   | Bits status of OUT3                           | <u>Section 8.10.3</u> |

| 05h          | OUT4_STA   | Bits status of OUT4                           | <u>Section 8.10.3</u> |

| 06h          | ISR_IRQ    | ISR_IRQ interrupt status                      | Section 8.5.2         |

| 07h          | ISR_WARN   | ISR_WARN interrupt status                     | Section 8.5.2         |

| 08h          | OD_IOUT1   | On-demand output 1 current (ODCM)             | Section 8.12.1        |

| 09h          | OD_IOUT2   | On-demand output 2 current (ODCM)             | <u>Section 8.12.1</u> |

| 0Ah          | OD_IOUT3   | On-demand output 3 current (ODCM)             | <u>Section 8.12.1</u> |

| 0Bh          | OD_IOUT4   | On-demand output 4 current (ODCM)             | <u>Section 8.12.1</u> |

| 0Ch          | IOUT1      | Current monitoring output 1 (CMM)             | Section 8.12.1        |

| 0Dh          | IOUT2      | Current monitoring output 2 (CMM)             | Section 8.12.1        |

| 0Eh          | IOUT3      | Current monitoring output 3 (CMM)             | Section 8.12.1        |

| 0Fh          | IOUT4      | Current monitoring output 4 (CMM)             | Section 8.12.1        |

| 10h          | INI_IOUT1  | Initial output 1 current (SCM)                | Section 8.12.1        |

| 11h          | INI_IOUT2  | Initial output 2 current (SCM)                | Section 8.12.1        |

| 12h          | INI_IOUT3  | Initial output 3 current (SCM)                | <u>Section 8.12.1</u> |

| 13h          | INI_IOUT4  | Initial output 4 current (SCM)                | Section 8.12.1        |

| 14h          | FIN_IOUT1  | Final output 1 current (SCM)                  | Section 8.12.1        |

| 15h          | FIN_IOUT2  | Final output 2 current (SCM)                  | <u>Section 8.12.1</u> |

Table 18. Diagnostic: 14-bits Read only register...continued

| Register [1] | Symbol    | Description                                       | Reference      |

|--------------|-----------|---------------------------------------------------|----------------|

| 16h          | FIN_IOUT3 | Final output 3 current (SCM)                      | Section 8.12.1 |

| 17h          | FIN_IOUT4 | Final output 4 current (SCM)                      | Section 8.12.1 |

| 18h          | VOUT1_ON  | Continuous conversion mode voltage output 1 (CMM) | Section 8.12.3 |

| 19h          | VOUT2_ON  | Continuous conversion mode voltage output 2 (CMM) | Section 8.12.3 |

| 1Ah          | VOUT3_ON  | Continuous conversion mode voltage output 3 (CMM) | Section 8.12.3 |

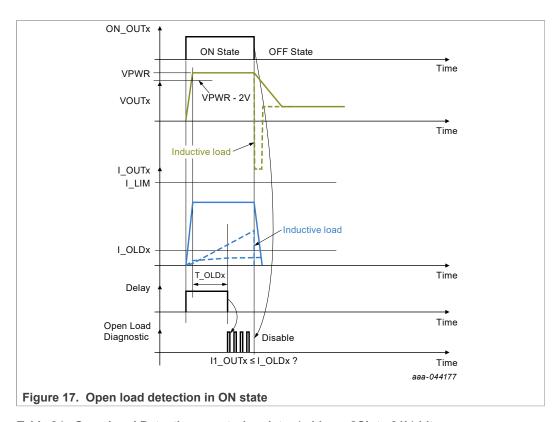

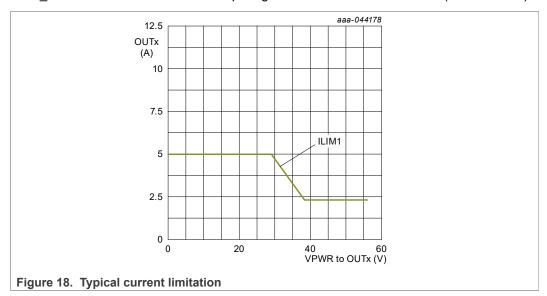

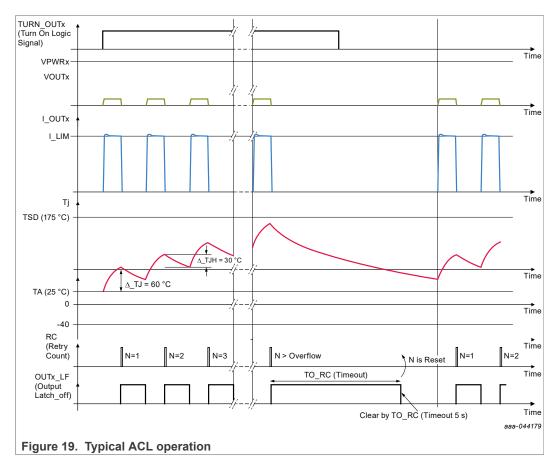

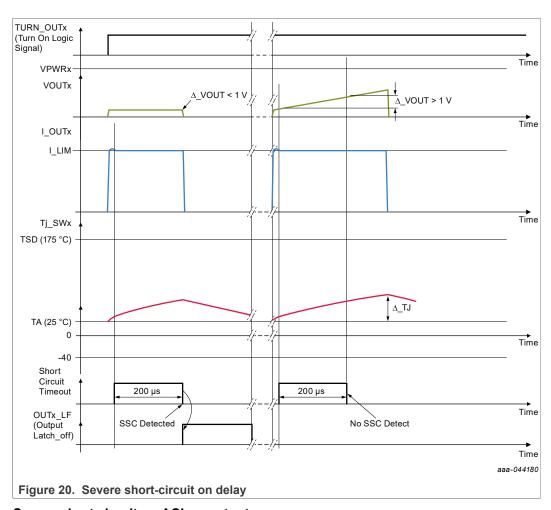

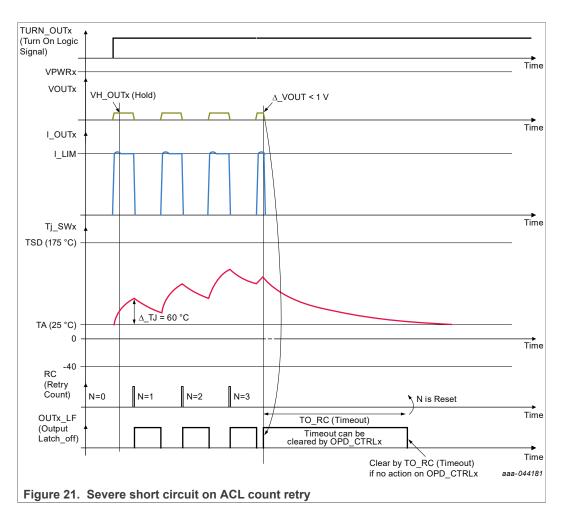

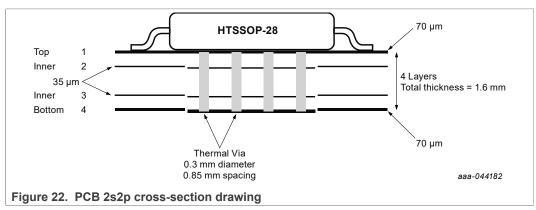

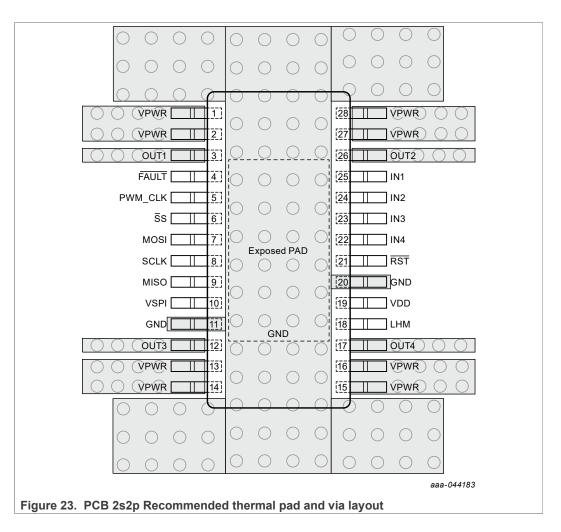

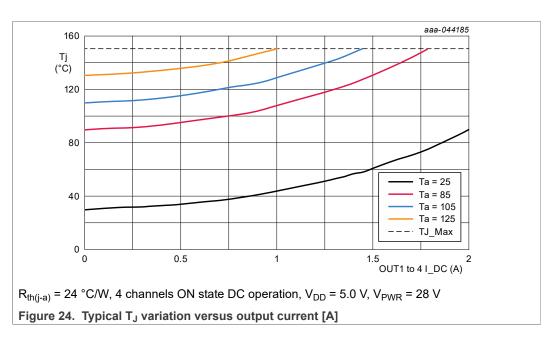

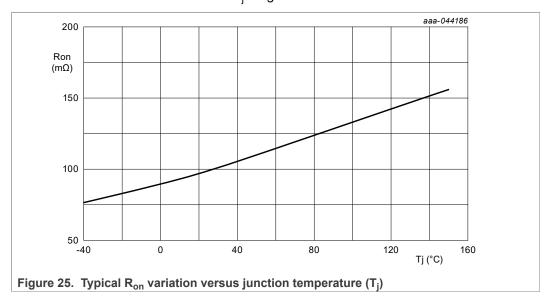

| 1Bh          | VOUT4_ON  | Continuous conversion mode voltage output 4 (CMM) | Section 8.12.3 |