# 8-Bit Serial or Parallel-Input/ Serial-Output Shift Register

High-Performance Silicon-Gate CMOS

# MC74HC165A

The MC74HC165A is identical in pinout to the LS165. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.

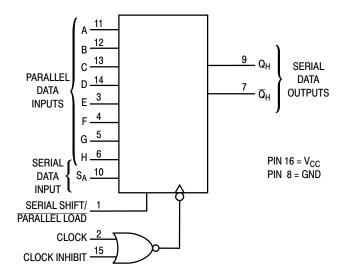

This device is an 8-bit shift register with complementary outputs from the last stage. Data may be loaded into the register either in parallel or in serial form. When the Serial Shift/Parallel Load input is low, the data is loaded asynchronously in parallel. When the Serial Shift/Parallel Load input is high, the data is loaded serially on the rising edge of either Clock or Clock Inhibit (see the Function Table).

The 2-input NOR clock may be used either by combining two independent clock sources or by designating one of the clock inputs to act as a clock inhibit.

# Features

- Output Drive Capability: 10 LSTTL Loads

- Outputs Directly Interface to CMOS, NMOS, and TTL

- Operating Voltage Range: 2.0 to 6.0 V

- Low Input Current: 1 µA

- High Noise Immunity Characteristic of CMOS Devices

- In Compliance with the Requirements Defined by JEDEC Standard No. 7 A

- Chip Complexity: 286 FETs or 71.5 Equivalent Gates

- NLV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb-Free, Halogen Free and are RoHS Compliant

# **ON Semiconductor®**

www.onsemi.com

|                                           |                                                                                             | MARKING<br>DIAGRAMS                                                             |

|-------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

|                                           | PDIP-16<br>N SUFFIX<br>CASE 648                                                             | 16<br><u> </u>                                                                  |

| 16 18 18 18 18 18 18 18 18 18 18 18 18 18 | SOIC-16<br>D SUFFIX<br>CASE 751B                                                            | 16<br><b>H H H H H H H H</b><br>HC165AG<br>AWLYWW<br>1<br>H H H H H H H H H H H |

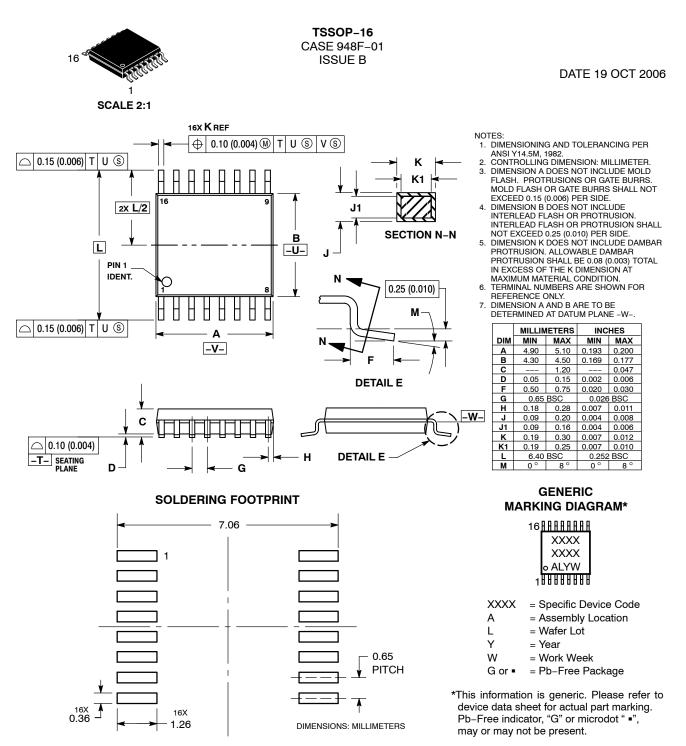

| 16* Trenter                               | TSSOP-16<br>DT SUFFIX<br>CASE 948F                                                          | 16<br>HHHHHHH<br>HC<br>165A<br>ALYW•<br>o •<br>HHHHHHHH                         |

|                                           | QFN16<br>MN SUFFIX<br>CASE 485AW                                                            | 165A<br>ALYW■<br>∘ ■                                                            |

| A<br>L, WL<br>Y, YY<br>W, WW<br>G or •    | = Assembly<br>= Wafer Lot<br>= Year<br>= Work Wee<br>= Pb-Free I                            | ek<br>Package                                                                   |

| A<br>L, WL<br>Y, YY<br>W, WW<br>G or •    | MN SUFFIX<br>CASE 485AW<br>= Assembly<br>= Wafer Lot<br>= Year<br>= Work Wee<br>= Pb-Free I | ALYW▪<br>_ ■<br>Location                                                        |

(Note: Microdot may be in either location)

## ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 6 of this data sheet.

| SERIAL SHIFT/    | 1• | 16 0 V <sub>CC</sub> | SERIAL SHI |                              |                   |

|------------------|----|----------------------|------------|------------------------------|-------------------|

|                  |    |                      |            | [1] [16]                     |                   |

| CLOCK [          | 2  |                      |            |                              |                   |

| ΕD               | 3  | 14 🛛 D               | E_3]       |                              | [14] D            |

| FO               | 4  | 13 🛛 C               | F 4]       | <br>  GND                    | [13] C            |

| G                | 5  | 12   B               | G 5        |                              | [12] B            |

| нЦ               |    | 11 🛛 A               | н_6]       |                              | []] A             |

| Q <sub>H</sub> [ |    | 10 🛛 S <sub>A</sub>  |            |                              | ⊡o S <sub>A</sub> |

|                  | 8  | 9 ] Q <sub>H</sub>   |            | 8   9 <br>GND Q <sub>H</sub> |                   |

Figure 1. Pin Assignments

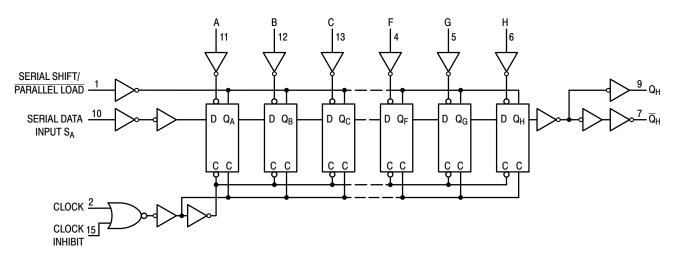

Figure 2. Logic Diagram

| Inputs                         |         |                  |        | Internal Stages Output |                | ernal Stages Output                |                                    |                                |

|--------------------------------|---------|------------------|--------|------------------------|----------------|------------------------------------|------------------------------------|--------------------------------|

| Serial Shift/<br>Parallel Load | Clock   | Clock<br>Inhibit | SA     | A – H                  | Q <sub>A</sub> | Q <sub>B</sub>                     | Q <sub>H</sub>                     | Operation                      |

| L                              | Х       | Х                | Х      | a h                    | a              | b                                  | h                                  | Asynchronous Parallel Load     |

| H<br>H                         | ے<br>بر | L                | L<br>H | X<br>X                 | L<br>H         | Q <sub>An</sub><br>Q <sub>An</sub> | Q <sub>Gn</sub><br>Q <sub>Gn</sub> | Serial Shift via Clock         |

| H<br>H                         | L       | ۔<br>بر          | L<br>H | X<br>X                 | L<br>H         | Q <sub>An</sub><br>Q <sub>An</sub> | Q <sub>Gn</sub><br>Q <sub>Gn</sub> | Serial Shift via Clock Inhibit |

| H<br>H                         | X<br>H  | H<br>X           | X<br>X | X<br>X                 | No Change      |                                    |                                    | Inhibited Clock                |

| Н                              | L       | L                | Х      | Х                      |                | No Change                          |                                    | No Clock                       |

#### FUNCTION TABLE

X = don't care  $Q_{An} - Q_{Gn}$  = Data shifted from the preceding stage

# MAXIMUM RATINGS

| Symbol           | Parameter                                                                               | Value                    | Unit |

|------------------|-----------------------------------------------------------------------------------------|--------------------------|------|

| V <sub>CC</sub>  | DC Supply Voltage (Referenced to GND)                                                   | – 0.5 to + 7.0           | V    |

| V <sub>in</sub>  | DC Input Voltage (Referenced to GND)                                                    | $-$ 0.5 to V_{CC} + 0.5  | V    |

| V <sub>out</sub> | DC Output Voltage (Referenced to GND)                                                   | $-0.5$ to $V_{CC}$ + 0.5 | V    |

| l <sub>in</sub>  | DC Input Current, per Pin                                                               | ± 20                     | mA   |

| I <sub>out</sub> | DC Output Current, per Pin                                                              | ± 25                     | mA   |

| I <sub>CC</sub>  | DC Supply Current, V <sub>CC</sub> and GND Pins                                         | ± 50                     | mA   |

| P <sub>D</sub>   | Power Dissipation in Still Air Plastic DIP†<br>SOIC Package†<br>TSSOP Package†          | 750<br>500<br>450        | mW   |

| T <sub>stg</sub> | Storage Temperature                                                                     | – 65 to + 150            | °C   |

| TL               | Lead Temperature, 1 mm from Case for 10 Seconds<br>(Plastic DIP, SOIC or TSSOP Package) | 260                      | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range GND  $\leq (V_{in} \text{ or } V_{out}) \leq V_{CC}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or  $V_{CC}$ ). Unused outputs must be left open.

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

†Derating – Plastic DIP: – 10 mW/°C from 65° to 125°C SOIC Package: – 7 mW/°C from 65° to 125°C

TSSOP Package: – 6.1 mW/°C from 65° to 125°C

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol                             | Parameter                                            |                                                                              |             | Max                       | Unit |

|------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------|-------------|---------------------------|------|

| V <sub>CC</sub>                    | DC Supply Voltage (Referenced to GND)                |                                                                              |             | 6.0                       | V    |

| V <sub>in</sub> , V <sub>out</sub> | DC Input Voltage, Output Voltage (Referenced to GND) |                                                                              |             | V <sub>CC</sub>           | V    |

| T <sub>A</sub>                     | Operating Temperature, All Package Type              | 6                                                                            | - 55        | + 125                     | °C   |

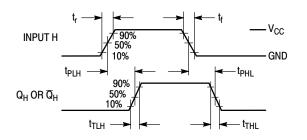

| t <sub>r</sub> , t <sub>f</sub>    | (Figure 1) V<br>V                                    | $C_{CC} = 2.0 V$<br>$C_{CC} = 3.0 V$<br>$C_{CC} = 4.5 V$<br>$C_{CC} = 6.0 V$ | 0<br>0<br>0 | 1000<br>600<br>500<br>400 | ns   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)

|                 |                                      |                                                                                                                                                                                                                  | v <sub>cc</sub>          | Gua                        | ranteed Limi               | t                          |      |

|-----------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------|----------------------------|----------------------------|------|

| Symbol          | Parameter                            | Test Conditions                                                                                                                                                                                                  | V                        | – 55 to 25°C               | ≤ 85°C                     | ≤ 125°C                    | Unit |

| V <sub>IH</sub> | Minimum High–Level Input<br>Voltage  | $V_{out} = 0.1 \text{ V or } V_{CC} - 0.1 \text{ V}$<br>$ I_{out}  \le 20 \ \mu\text{A}$                                                                                                                         | 2.0<br>3.0<br>4.5<br>6.0 | 1.5<br>2.1<br>3.15<br>4.2  | 1.5<br>2.1<br>3.15<br>4.2  | 1.5<br>2.1<br>3.15<br>4.2  | V    |

| V <sub>IL</sub> | Maximum Low-Level Input<br>Voltage   | $\begin{array}{l} V_{out} = 0.1 \text{ V or } V_{CC} - 0.1 \text{ V} \\  I_{out}  \leq 20 \ \mu\text{A} \end{array}$                                                                                             | 2.0<br>3.0<br>4.5<br>6.0 | 0.5<br>0.9<br>1.35<br>1.80 | 0.5<br>0.9<br>1.35<br>1.80 | 0.5<br>0.9<br>1.35<br>1.80 | V    |

| V <sub>OH</sub> | Minimum High-Level Output<br>Voltage |                                                                                                                                                                                                                  | 2.0<br>4.5<br>6.0        | 1.9<br>4.4<br>5.9          | 1.9<br>4.4<br>5.9          | 1.9<br>4.4<br>5.9          | V    |

|                 |                                      | $ \begin{aligned} V_{\text{in}} = V_{\text{IH}} \text{ or } V_{\text{IL}} &  I_{\text{out}}  \leq 2.4 \text{ mA} \\  I_{\text{out}}  \leq 4.0 \text{ mA} \\  I_{\text{out}}  \leq 5.2 \text{ mA} \end{aligned} $ | 3.0<br>4.5<br>6.0        | 2.48<br>3.98<br>5.48       | 2.34<br>3.84<br>5.34       | 2.20<br>3.70<br>5.20       | V    |

## DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)

|                 |                                                   |                                                                                                                                                                                                                   | v <sub>cc</sub>   |                      | Guaranteed Limit     |                      |      |

|-----------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------|----------------------|----------------------|------|

| Symbol          | Parameter                                         | Test Conditions                                                                                                                                                                                                   | v                 | – 55 to 25°C         | ≤ 85°C               | ≤ 125°C              | Unit |

| V <sub>OL</sub> | Maximum Low-Level Output<br>Voltage               | $ \begin{aligned} V_{in} &= V_{IH} \text{ or } V_{IL} \\ \left  I_{out} \right  &\leq 20 \ \mu \text{A} \end{aligned} $                                                                                           | 2.0<br>4.5<br>6.0 | 0.1<br>0.1<br>0.1    | 0.1<br>0.1<br>0.1    | 0.1<br>0.1<br>0.1    | V    |

|                 |                                                   | $\begin{array}{ll} V_{in} = V_{IH} \text{ or } V_{IL} & \left  I_{out} \right   \leq  2.4 \text{ mA} \\ \left  I_{out} \right   \leq  4.0 \text{ mA} \\ \left  I_{out} \right   \leq  5.2 \text{ mA} \end{array}$ | 3.0<br>4.5<br>6.0 | 0.26<br>0.26<br>0.26 | 0.33<br>0.33<br>0.33 | 0.40<br>0.40<br>0.40 |      |

| l <sub>in</sub> | Maximum Input Leakage<br>Current                  | V <sub>in</sub> = V <sub>CC</sub> or GND                                                                                                                                                                          | 6.0               | ± 0.1                | ± 1.0                | ± 1.0                | μΑ   |

| I <sub>CC</sub> | Maximum Quiescent Supply<br>Current (per Package) | $V_{in} = V_{CC} \text{ or } GND$<br>$I_{out} = 0 \ \mu A$                                                                                                                                                        | 6.0               | 4                    | 40                   | 160                  | μΑ   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

# AC ELECTRICAL CHARACTERISTICS (C\_L = 50 pF, Input $t_{r}$ = $t_{f}$ = 6 ns)

|                    |                                                                                    | v <sub>cc</sub> | Guaranteed Limit                        |        | it      |      |

|--------------------|------------------------------------------------------------------------------------|-----------------|-----------------------------------------|--------|---------|------|

| Symbol             | Parameter                                                                          | v               | – 55 to 25°C                            | ≤ 85°C | ≤ 125°C | Unit |

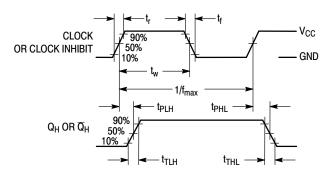

| f <sub>max</sub>   | Maximum Clock Frequency (50% Duty Cycle)                                           | 2.0             | 6                                       | 4.8    | 4       | MHz  |

|                    | (Figures 1 and 8)                                                                  | 3.0             | 18                                      | 17     | 15      |      |

|                    |                                                                                    | 4.5             | 30                                      | 24     | 20      |      |

|                    |                                                                                    | 6.0             | 35                                      | 28     | 24      |      |

| t <sub>PLH</sub> , | Maximum Propagation Delay, Clock (or Clock Inhibit) to $Q_H$ or $\overline{Q}_H$   | 2.0             | 150                                     | 190    | 225     | ns   |

| t <sub>PHL</sub>   | (Figures 1 and 8)                                                                  | 3.0             | 52                                      | 63     | 65      |      |

|                    |                                                                                    | 4.5             | 30                                      | 38     | 45      |      |

|                    |                                                                                    | 6.0             | 26                                      | 33     | 38      |      |

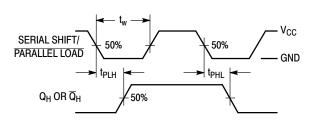

| t <sub>PLH</sub> , | Maximum Propagation Delay, Serial Shift/Parallel Load to $Q_H$ or $\overline{Q}_H$ | 2.0             | 175                                     | 220    | 265     | ns   |

| t <sub>PHL</sub>   | (Figures 2 and 8)                                                                  | 3.0             | 58                                      | 70     | 72      |      |

|                    |                                                                                    | 4.5             | 35                                      | 44     | 53      |      |

|                    |                                                                                    | 6.0             | 30                                      | 37     | 45      |      |

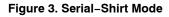

| t <sub>PLH</sub> , | Maximum Propagation Delay, Input H to $Q_H$ or $\overline{Q}_H$                    | 2.0             | 150                                     | 190    | 225     | ns   |

| t <sub>PHL</sub>   | (Figures 3 and 8)                                                                  | 3.0             | 52                                      | 63     | 65      |      |

|                    |                                                                                    | 4.5             | 30                                      | 38     | 45      |      |

|                    |                                                                                    | 6.0             | 26                                      | 33     | 38      |      |

| t <sub>TLH</sub> , | Maximum Output Transition Time, Any Output                                         | 2.0             | 75                                      | 95     | 110     | ns   |

| t <sub>THL</sub>   | (Figures 1 and 8)                                                                  | 3.0             | 27                                      | 32     | 36      |      |

|                    |                                                                                    | 4.5             | 15                                      | 19     | 22      |      |

|                    |                                                                                    | 6.0             | 13                                      | 16     | 19      |      |

| C <sub>in</sub>    | Maximum Input Capacitance                                                          | -               | 10                                      | 10     | 10      | pF   |

|                    |                                                                                    |                 | Typical @ 25°C, V <sub>CC</sub> = 5.0 V |        |         |      |

| C <sub>PD</sub>    | Power Dissipation Capacitance (Per Package)*                                       |                 |                                         | 40     |         | pF   |

\* Used to determine the no-load dynamic power consumption:  $P_D = C_{PD} V_{CC}^2 f + I_{CC} V_{CC}$ .

#### **TIMING REQUIREMENTS** (Input $t_r = t_f = 6 \text{ ns}$ )

|                                 |                                                                            |                      | Guar         | anteed Lim | it       |      |

|---------------------------------|----------------------------------------------------------------------------|----------------------|--------------|------------|----------|------|

| Symbol                          | Parameter                                                                  | V <sub>CC</sub><br>V | – 55 to 25°C | ≤ 85°C     | ≤ 125°C  | Unit |

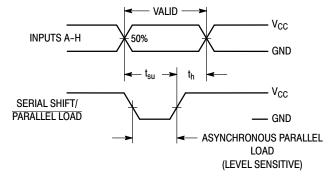

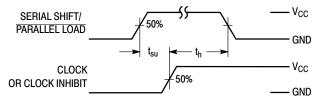

| t <sub>su</sub>                 | Minimum Setup Time, Parallel Data Inputs to Serial Shift/Parallel Load     | 2.0                  | 75           | 95         | 110      | ns   |

|                                 | (Figure 4)                                                                 | 3.0                  | 30           | 40         | 55       |      |

|                                 |                                                                            | 4.5                  | 15           | 19         | 22       |      |

|                                 |                                                                            | 6.0                  | 13           | 16         | 19       |      |

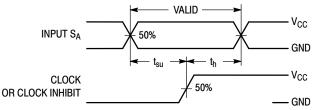

| t <sub>su</sub>                 | Minimum Setup Time, Input SA to Clock (or Clock Inhibit)                   | 2.0                  | 75           | 95         | 110      | ns   |

|                                 | (Figure 5)                                                                 | 3.0                  | 30           | 40         | 55       |      |

|                                 |                                                                            | 4.5                  | 15           | 19         | 22       |      |

|                                 |                                                                            | 6.0                  | 13           | 16         | 19       |      |

| t <sub>su</sub>                 | Minimum Setup Time, Serial Shift/Parallel Load to Clock (or Clock Inhibit) | 2.0                  | 75           | 95         | 110      | ns   |

|                                 | (Figure 6)                                                                 | 3.0                  | 30           | 40         | 55       |      |

|                                 |                                                                            | 4.5                  | 15           | 19         | 22       |      |

|                                 |                                                                            | 6.0                  | 13           | 16         | 19       |      |

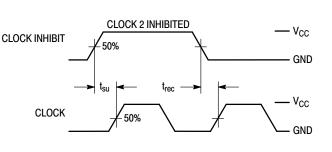

| t <sub>su</sub>                 | Minimum Setup Time, Clock to Clock Inhibit                                 | 2.0                  | 75           | 95         | 110      | ns   |

|                                 | (Figure 7)                                                                 | 3.0                  | 30           | 40         | 55       |      |

|                                 |                                                                            | 4.5                  | 15           | 19         | 22       |      |

|                                 |                                                                            | 6.0                  | 13           | 16         | 19       |      |

| t <sub>h</sub>                  | Minimum Hold Time, Serial Shift/Parallel Load to Parallel Data Inputs      | 2.0                  | 5            | 5          | 5        | ns   |

| 11                              | (Figure 4)                                                                 | 3.0                  | 5            | 5          | 5        |      |

|                                 | (Figure +)                                                                 | 4.5                  | 5            | 5          | 5        |      |

|                                 |                                                                            | 6.0                  | 5            | 5          | 5        |      |

| t <sub>h</sub>                  | Minimum Hold Time, Clock (or Clock Inhibit) to Input SA                    | 2.0                  | 5            | 5          | 5        | ns   |

| 41                              | (Figure 5)                                                                 | 3.0                  | 5            | 5          | 5        | 110  |

|                                 | (Figure 5)                                                                 | 4.5                  | 5            | 5          | 5        |      |

|                                 |                                                                            | 6.0                  | 5            | 5          | 5        |      |

| t <sub>h</sub>                  | Minimum Hold Time, Clock (or Clock Inhibit) to Serial Shift/Parallel Load  | 2.0                  | 5            | 5          | 5        | ns   |

| 41                              | (Figure 6)                                                                 | 3.0                  | 5            | 5          | 5        | 110  |

|                                 | (riguie o)                                                                 | 4.5                  | 5            | 5          | 5        |      |

|                                 |                                                                            | 6.0                  | 5            | 5          | 5        |      |

| t <sub>rec</sub>                | Minimum Recovery Time, Clock to Clock Inhibit                              | 2.0                  | 75           | 95         | 110      | ns   |

| rec                             | (Figure 7)                                                                 | 3.0                  | 30           | 40         | 55       | 115  |

|                                 |                                                                            | 4.5                  | 15           | 19         | 22       |      |

|                                 |                                                                            | 6.0                  | 13           | 19         | 19       |      |

| +                               | Minimum Pulse Width, Clock (or Clock Inhibit)                              | 2.0                  | 70           | 90         | 100      | ns   |

| tw                              | (Figure 1)                                                                 | 3.0                  | 27           | 32         | 36       | 115  |

|                                 |                                                                            | 4.5                  | 15           | 19         | 22       |      |

|                                 |                                                                            | 4.5<br>6.0           | 13           | 19         | 19       |      |

| +                               | Minimum Pulse width, Serial Shift/Parallel Load                            |                      |              |            |          | 200  |

| tw                              |                                                                            | 2.0                  | 70           | 90         | 100      | ns   |

|                                 | (Figure 2)                                                                 | 3.0                  | 27           | 32         | 36       |      |

|                                 |                                                                            | 4.5<br>6.0           | 15<br>13     | 19<br>16   | 22<br>19 |      |

| + +                             | Maximum Input Biog and Fall Times                                          |                      |              |            |          | 20   |

| t <sub>r</sub> , t <sub>f</sub> | Maximum Input Rise and Fall Times                                          | 2.0                  | 1000         | 1000       | 1000     | ns   |

|                                 | (Figure 1)                                                                 | 3.0                  | 800          | 800        | 800      |      |

|                                 |                                                                            | 4.5                  | 500          | 500        | 500      |      |

|                                 |                                                                            | 6.0                  | 400          | 400        | 400      |      |

# **PIN DESCRIPTIONS**

### INPUTS

# A, B, C, D, E, F, G, H (Pins 11, 12, 13, 14, 3, 4, 5, 6)

Parallel Data inputs. Data on these inputs are asynchronously entered in parallel into the internal flip-flops when the Serial Shift/Parallel Load input is low.

## SA (Pin 10)

Serial Data input. When the Serial Shift/Parallel Load input is high, data on this pin is serially entered into the first stage of the shift register with the rising edge of the Clock.

## **CONTROL INPUTS**

#### Serial Shift/Parallel Load (Pin 1)

Data-entry control input. When a high level is applied to this pin, data at the Serial Data input (SA) are shifted into the register with the rising edge of the Clock. When a low level is applied to this pin, data at the Parallel Data inputs are asynchronously loaded into each of the eight internal stages.

### Clock, Clock Inhibit (Pins 2, 15)

Clock inputs. These two clock inputs function identically. Either may be used as an active-high clock inhibit. However, to avoid double clocking, the inhibit input should go high only while the clock input is high.

The shift register is completely static, allowing Clock rates down to DC in a continuous or intermittent mode.

## OUTPUTS

# Q<sub>H</sub>, <u>Q</u><sub>H</sub> (Pins 9, 7)

Complementary Shift Register outputs. These pins are the noninverted and inverted outputs of the eighth stage of the shift register.

#### **ORDERING INFORMATION**

| Device            | Package              | Shipping <sup>†</sup> |

|-------------------|----------------------|-----------------------|

| MC74HC165ANG      | PDIP-16<br>(Pb-Free) | 500 Units / Rail      |

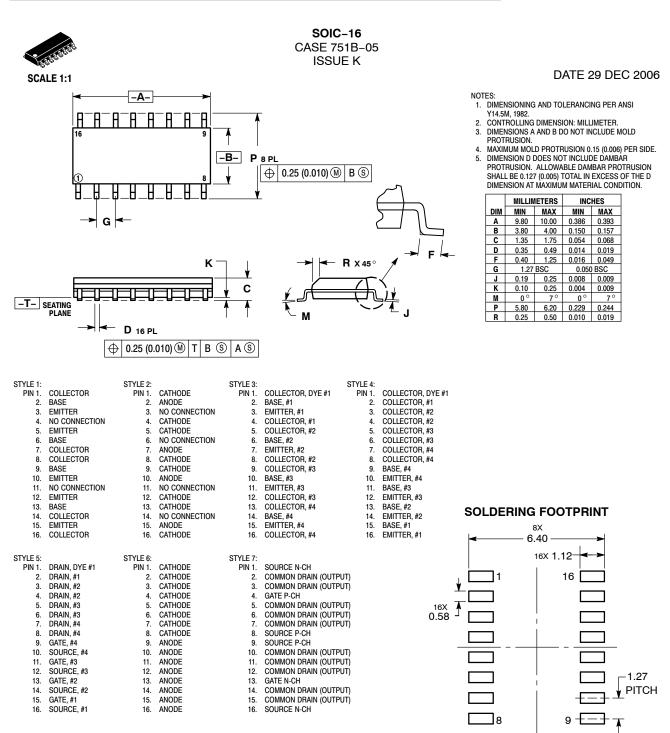

| MC74HC165ADG      |                      | 48 Units / Rail       |

| MC74HC165ADR2G    | SOIC-16<br>(Pb-Free) | 2500 Units / Reel     |

| NLV74HC165ADR2G*  | (1.5.1.00)           | 2500 Units / Reel     |

| MC74HC165ADTR2G   | TSSOP-16             | 2500 Units / Reel     |

| NLV74HC165ADTR2G* | (Pb-Free)            | 2500 Units / Reel     |

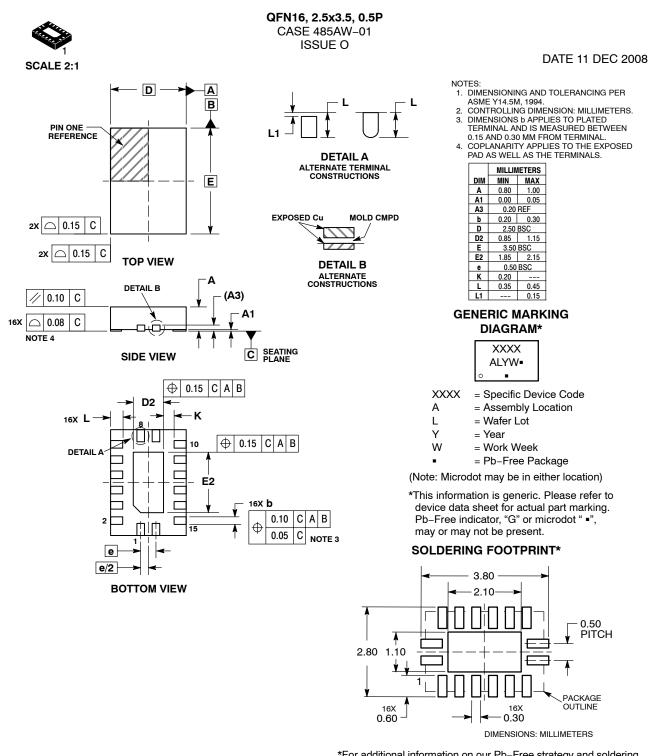

| MC74HC165AMNTWG   | QFN16                | 3000 Units / Reel     |

| MC74HC165AMN2TWG  | (Pb-Free)            | 3000 Units / Reel     |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*NLV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

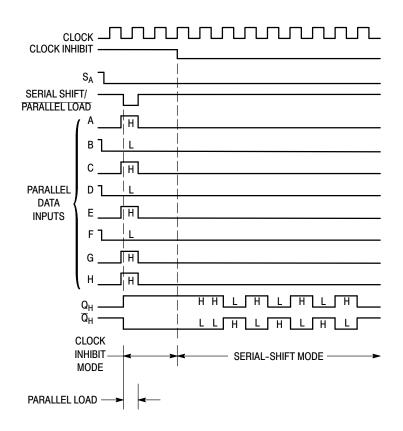

# SWITCHING WAVEFORMS

Figure 5. Parallel-Load Mode

Figure 6. Parallel-Load Mode

Figure 8. Serial-Shift Mode

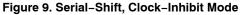

\*Includes all probe and jig capacitance

Figure 10. Test Circuit

## EXPANDED LOGIC DIAGRAM

TIMING DIAGRAM

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON36347E          | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | QFN16, 2.5X3.5, 0.5P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |

|                  |                      |                                                                                                                                                                                     |             |  |  |

ON Semiconductor and unarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

DIMENSIONS: MILLIMETERS

| DOCUMENT NUMBER:                                                         | 98ASB42566B                                                                                                                                                                                                                                                                                                                                             | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |  |  |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|

| DESCRIPTION:                                                             | SOIC-16                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |  |  |  |

| ON Semiconductor and ()) are trac<br>ON Semiconductor reserves the right | ON Semiconductor and 👊 are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding |                                                                                                                                                                                     |             |  |  |  |  |  |

ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

| DOCUMENT NUMBER:                                                                                                                                                        | 98ASH70247A | ASH70247A Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:                                                                                                                                                            | TSSOP-16    |                                                                                                                                                                                               | PAGE 1 OF 1 |

| ON Semiconductor and 🔟 are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. |             |                                                                                                                                                                                               |             |

ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.