# MIC3808/3809

### **Push-Pull PWM Controller**

### **General Description**

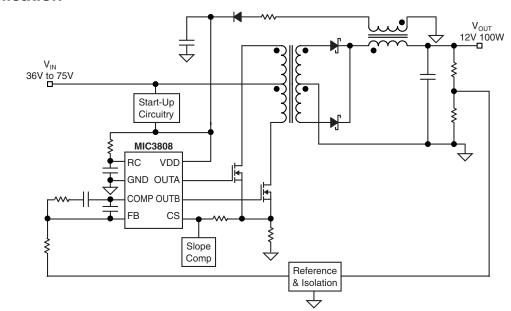

The MIC3808 and MIC3809 are a family of complementary output push-pull PWM control ICs that feature high speed and low power consumption. The MIC3808/9 are ideal for telecom level (36V to 75V) isolated step down dc/dc conversion applications where high output current, small size, and high efficiency are required.

The dual-ended push-pull architecture of the MIC3808/9 allows more efficient utilization of the transformer than singleended topologies, allowing smaller size dc/dc solutions. Additionally, the out-of-phase push-pull topology allows a higher effective duty cycle, reducing input and output ripple as well as stress on the external components. The dead-time between the two outputs is adjustable between 60ns to 200ns, limiting the duty cycle of each output stage to less than 50%.

The MIC3808/9 are built on a low-power, high-speed BiCMOS process. The  $130\mu$ A start-up current and 1mA run-current reduce the size of the start-up circuitry and allow high efficiency even at light loads. The high-speed internal 4MHz error amplifier allows MIC3808/9 operation up to 1MHz.

The MIC3808 has a turn-on threshold of 12.5V whereas the MIC3809 has a lower turn-on threshold of 4.3V. Both devices are available in SOP-8 and MSOP-8 package options with an operating range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Data sheets and support documentation can be found on Micrel's web site at: www.micrel.com.

### **Features**

- · Dual output drive stages in push-pull configuration

- Leading edge current-sense blanking

- 130µA typical start-up current

- 1mA typical run current

- Operation to 1MHz

- Internal soft start

- On-chip error amplifier with 4MHz gain bandwidth product

- On-chip V<sub>DD</sub> clamping

- Output drive stages capable of 500mA peak source current, 1A peak sink current

### **Applications**

- High efficiency "brick" power supply modules

- Half bridge converters

- Full bridge converters

- Push-pull converters

- Voltage-fed push-pull converters

- Telecom equipment and power supplies

- · Networking power supplies

- · Industrial power supplies

- · 42V automotive power supplies

- · Base stations

# Typical Application

### **Ordering Information**

| Part Number |            |                      |                       |                   |            |

|-------------|------------|----------------------|-----------------------|-------------------|------------|

| Standard    | Lead-Free  | Turn On<br>Threshold | Turn Off<br>Threshold | Temperature Range | Package    |

| MIC3808BM   | MIC3808YM  | 12.5V                | 8.3V                  | –40°C to +85°C    | 8-Pin SOIC |

| MIC3809BM   | MIC3809YM  | 4.3V                 | 4.1V                  | –40°C to +85°C    | 8-Pin SOIC |

| MIC3808BMM  | MIC3808YMM | 12.5V                | 8.3V                  | –40°C to +85°C    | 8-Pin MSOP |

| MIC3809BMM  | MIC3809YMM | 4.3V                 | 4.1V                  | –40°C to +85°C    | 8-Pin MSOP |

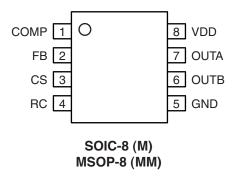

## **Pin Configuration**

### **Pin Description**

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | COMP     | COMP is the output of the error amplifier and the input of the PWM com-<br>parator. The error amplifier in the MIC3808 is a true low-output impedance,<br>4MHz operational amplifier. As such, the COMP pin can both source and<br>sink current. However, the error amplifier is internally current limited, so that<br>zero duty cycle can be externally forced by pulling COMP to GND. The<br>MIC3808 family features built-in full cycle soft start. Soft start is imple-<br>mented as a clamp on the maximum COMP voltage.                                                                |

| 2          | FB       | The inverting input to the error amplifier. For best stability, keep FB lead length as short as possible and FB stray capacitance as small as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3          | CS       | The input to the PWM, peak current, and overcurrent comparators. The overcurrent comparator is only intended for fault sensing. Exceeding the overcurrent threshold will cause a soft start cycle. An internal MOSFET discharges the current sense filter capacitor to improve dynamic performance of the power converter.                                                                                                                                                                                                                                                                    |

| 4          | RC       | The oscillator programming pin. The MIC3808's oscillator tracks $V_{DD}$ and GND internally, so that variations in power supply rails minimally affect frequency stability. Only two components are required to program the oscillator, a resistor (tied to the $V_{DD}$ and RC), and a capacitor (tied to the RC and GND). The approximate oscillator frequency is determined by the simple                                                                                                                                                                                                  |

|            |          | formula: $F_{OSCILLATOR} = \frac{1.41}{RC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            |          | where frequency is in Hertz, resistance in Ohms, and capacitance in Farads. The recommended range of timing resistors is between $7k\Omega$ and $200k\Omega$ and range of timing capacitors is between $100pF$ and $1000pF$ . Timing resistors less than $7k\Omega$ should be avoided. For best performance, keep the timing capacitor lead to GND as short as possible, the timing resistor lead from $V_{DD}$ as short as possible, and the leads between timing components and RC as short as possible. Separate ground and $V_{DD}$ traces to the external timing network are encouraged. |

## **Pin Description**

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5          | GND      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6          | OUTB     | Alternating high current output stages. Both stages are capable of driving the gate of a power MOSFET. Each stage is capable of 500mA peak source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7          | OUTA     | current, and 1A peak sink current. The output stages switch at half the oscillator frequency, in a push/pull configuration. When the voltage on the RC pin is rising, one of the two outputs is high, but during fall time, both outputs are off. This "dead time" between the two outputs, along with a slower output rise time than fall time, insures that the two outputs can not be on at the same time. This dead time is typically 60ns to 200ns and depends upon the values of the timing capacitor and resistor. The high-current output drivers consist of MOSFET output devices, which switch from $V_{DD}$ to GND. Each output stage also provides a very low impedance to overshoot and undershoot. This means that in many cases, external Schottky clamp diodes are not required. |

| 8          | VDD      | The power input connection for this device. Although quiescent V <sub>DD</sub> current is very low, total supply current will be higher, depending on OUTA and OUTB current, and the programmed oscillator frequency. Total V <sub>DD</sub> current is the sum of quiescent V <sub>DD</sub> current and the average OUT current. Knowing the operating frequency and the MOSFET gate charge (Qg), average OUT current can be calculated from I <sub>OUT</sub> = Qg × F, where F is frequency. To prevent noise problems, bypass V <sub>DD</sub> to GND with a ceramic capacitor as close to the chip as possible. A 1µF decoupling capacitor is recommended.                                                                                                                                     |

### Absolute Maximum Ratings (Note 1)

| Supply Voltage (I <sub>DD</sub> ≤ 10mA) | +15V                            |

|-----------------------------------------|---------------------------------|

| Supply Current                          | 20mA                            |

| OUTA/OUTB Source Current (peak)         | –0.5A                           |

| OUTA/OUTB Sink Current (peak)           | 1.0A                            |

| Comp Pin                                | V <sub>DD</sub>                 |

| Analog Inputs (FB, CS)                  | .–0.3V to V <sub>DD</sub> +0.3V |

| N                                       | OT TO EXCEED 6V                 |

| Junction Temperature                    | –55°C to +150°C                 |

| Storage Temperature                     | –65°C to +150°C                 |

| Lead Temperature (soldering, 10 sec.)   | +300°C                          |

| ESD Rating, Note 3                      | 2kV                             |

## Operating Ratings (Note 2)

| V <sub>DD</sub> Input Voltage (V <sub>DD</sub> ) | Note 11        |

|--------------------------------------------------|----------------|

| Oscillator Frequency (f <sub>OSC</sub> )         | 10kHz to 1MHz  |

| Ambient Temperature (T <sub>A</sub> )            | –40°C to +85°C |

| Package Thermal Resistance                       |                |

| SOIC-8 (θ <sub>JA</sub> )                        | 160°C/W        |

| MSOP-8 (θ <sub>JA</sub> )                        |                |

### **Electrical Characteristics**

$T_A = T_J = -40^{\circ}C$  to +85°C,  $V_{DD} = 10V$  (**Note 9**), 1µF capacitor from  $V_{DD}$  to GND, R = 22K $\Omega$ , C = 330pF.

| Parameter                | Condition                                              | Min   | Тур  | Max  | Units |

|--------------------------|--------------------------------------------------------|-------|------|------|-------|

| Oscillator Section       | ·                                                      | •     |      |      |       |

| Oscillator Frequency     |                                                        | 180   | 200  | 220  | kHz   |

| Oscillator Amplitude/VDD | Note 4                                                 | 0.44  | 0.5  | 0.56 | V/V   |

| Error Amp Section        | ·                                                      | •     |      |      |       |

| Input Voltage            | COMP = 2V                                              | 1.95  | 2    | 2.05 | V     |

| Input Bias Current       |                                                        | -1    |      | 1    | μΑ    |

| Open Loop Voltage Gain   | (Guaranteed by design)                                 | 60    | 80   |      | dB    |

| COMP Sink Current        | FB = 2.2V, COMP = 1V                                   | 0.3   | 2.5  |      | mA    |

| COMP Source Current      | FB = 1.3V, COMP = 3V, <b>Note 5</b>                    | -0.15 | -0.5 |      | mA    |

| COMP Clamp Voltage       | V <sub>FB</sub> = 0V                                   | 3.1   | 3.6  | 4.0  | V     |

| PWM Section              |                                                        | ·     |      |      |       |

| Maximum Duty Cycle       | Measured at OUTA or OUTB                               | 48    | 49   | 50   | %     |

| Minimum Duty Cycle       | COMP = 0V                                              |       |      | 0    | %     |

| Current Sense Section    | ·                                                      |       |      | •    |       |

| Gain                     | Note 6 (Guaranteed by design)                          | 1.9   | 2.2  | 2.5  | V/V   |

| Maximum Input Signal     | Note 7                                                 | 0.45  | 0.5  | 0.55 | V     |

| CS to Output Delay       | COMP = 3V, CS from 0 to 600mV                          |       | 70   | 200  | ns    |

| CS Source Current        |                                                        | -200  |      |      | nA    |

| CS Sink Current          | CS = 0.5V, RC = 5.5V, <b>Note 8</b>                    | 5     | 10   |      | mA    |

| Over Current Threshold   |                                                        | 0.7   | 0.75 | 0.8  | V     |

| COMP to CS Offset        | CS = 0V                                                | 0.35  | 0.8  | 1.2  | V     |

| Output Section           | ·                                                      | •     |      |      |       |

| OUT Low Level            | l = 100mA                                              |       | 0.5  | 1    | V     |

| OUT High Level           | $I = -50 \text{mA}, \text{V}_{\text{DD}} - \text{OUT}$ |       | 0.5  | 1    | V     |

| Rise Time                | C <sub>L</sub> = 1nF                                   |       | 25   | 60   | ns    |

| Fall Time                | C <sub>L</sub> = 1nF                                   |       | 25   | 60   | ns    |

4

| Parameter                                | Condition                              | Min         | Тур         | Max         | Units  |

|------------------------------------------|----------------------------------------|-------------|-------------|-------------|--------|

| Undervoltage Lockout Section             | n                                      | L           |             |             | 1      |

| Start Threshold                          | MIC3808, <b>Note 9</b><br>MIC3809      | 11.5<br>4.1 | 12.5<br>4.3 | 13.5<br>4.5 | V<br>V |

| Minimum Operating Voltage<br>After Start | MIC3808<br>MIC3809                     | 7.6<br>3.9  | 8.3<br>4.1  | 9<br>4.3    | V<br>V |

| Hysteresis                               | MIC3808<br>MIC3809                     | 3.5<br>0.1  | 4.2<br>0.2  | 5.1<br>0.3  | V<br>V |

| Soft Start Section                       | ·                                      |             |             |             |        |

| COMP Rise Time                           | FB = 1.8V, Rise from 0.5V to 3V        |             | 2.5         | 20          | ms     |

| Overall Section                          |                                        | ŀ           |             |             | •      |

| Startup Current                          | V <sub>DD</sub> < Start Threshold      |             | 130         | 260         | μΑ     |

| Operating Supply Current                 | FB = 0V, CS = 0V, Notes 9 and 10       |             | 1           | 2           | mA     |

| VDD Zener Shunt Voltage                  | I <sub>DD</sub> = 10mA, <b>Note 12</b> | 13          | 14          | 15          | V      |

Note 2. The device is not guaranteed to function outside its operating rating.

Note 3. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5k in series with 100pF.

Note 4. Measured at RC. Signal amplitude tracks V<sub>DD</sub>.

Note 5. The COMP pin is internally clamped to 3.65V(typ). The COMP pin source current is tested at  $V_{COMP} = 3.0V$  to avoid interfering with this clamp voltage. The minimum source current increases as  $V_{COMP}$  approaches  $V_{CLAMP}$ .

**Note 6.** Gain is defined by

$$A = \frac{\Delta V_{COMP}}{\Delta V_{CS}}$$

,  $0 \le V_{CS} \le 0.4V$ .

Note 7. Parameter measured at trip point of latch with FB at 0V.

Note 8. The internal current sink on the CS pin is designed to discharge an external filter capacitor. It is not intended to be a DC sink path.

Note 9. For MIC3808, set  $V_{DD}$  above the start threshold before setting at 10V.

Note 10. Does not include current in the external oscillator network.

- Note 11. Maximum operating voltage is equal to the V<sub>DD</sub> [zener] shunt voltage. When operating at or near the shunt voltage, care must be taken to limit the V<sub>DD</sub> pin current to less than the 20mA V<sub>DD</sub> maximum supply current rating.

- Note 12. Start threshold and Zener Shunt threshold track one another.

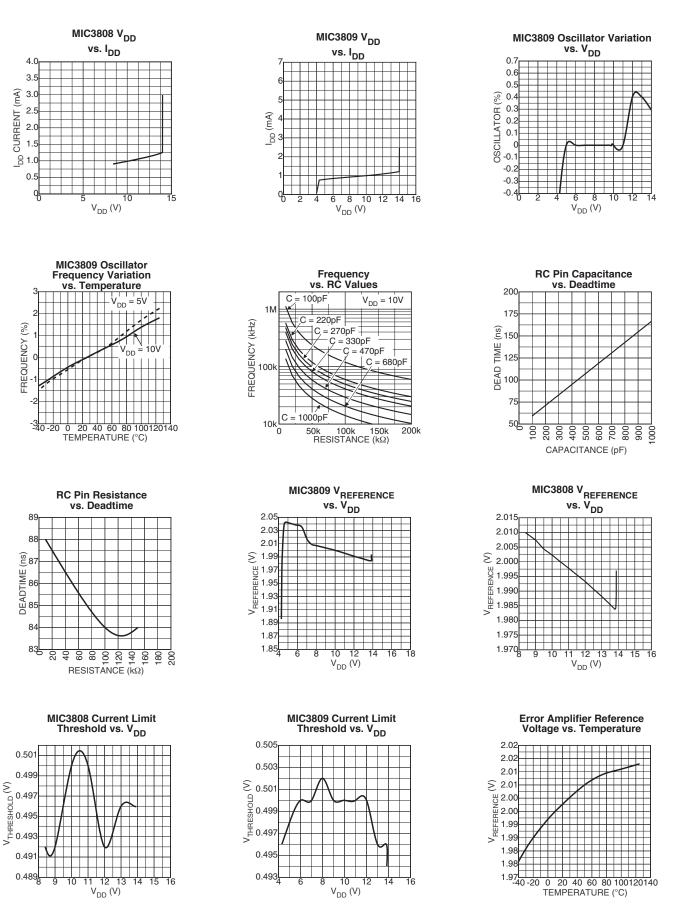

## **Typical Characteristics**

VTHRESHOLD (V)

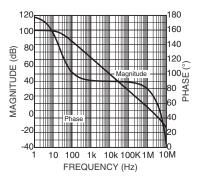

Error Ampifier

## **Functional Diagram**

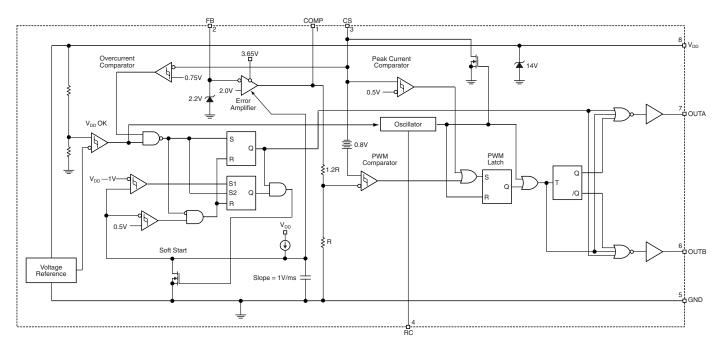

Figure 1. MIC3808 Block Diagram

### **Functional Description**

The MIC3808/9 is a high-speed power supply controller with push-pull output drive capability. MIC3808 has a higher  $V_{DD}$  turn-on threshold and more hysteresis between  $V_{DD}$  turn-on and turn-off than the MIC3809. The outputs of the controller operate in a push-pull fashion with a guaranteed dead time between them. A block diagram of the MIC3808/9 controller is shown in Figure 1.

#### V<sub>DD</sub> and Turn-on Sequence

The oscillator and output gate drive signals are disabled when  $V_{DD}$  is lower than the turn on threshold. Circuitry in the output drivers eliminates glitching or random pulsing during the start-up sequence. The oscillator is enabled when  $V_{DD}$  is applied and reaches the turn-on threshold. The  $V_{DD}$  comparator also turns off the internal soft-start discharge FET, slowly bringing up the COMP pin voltage.

The V<sub>DD</sub> pin is internally clamped. As V<sub>DD</sub> approaches this clamp voltage, the V<sub>DD</sub> current will increase over the normal current draw of the IC. Exceeding the V<sub>DD</sub> zener shunt voltage may cause excessive power dissipation in the MIC3808/9.

#### Soft-Start

The soft start feature helps reduce surge currents at the power supply input source. An internal current source and capacitor ramp up from 0V to near Vdd at a typical rate of 1V/ms. The softstart feature limits the output voltage of the

error amplifier at the COMP pin. As the softstart voltage rises, it allows the COMP pin voltage to rise, which in turn allows the duty cycle of the output drivers to increase. The internal softstart voltage is discharged and remains discharged during the following conditions:

- 1. The  $\rm V_{\rm DD}$  voltage drops below the turn-off threshold

- 2. The voltage on the CS pin exceeds the overcurrent comparator threshold

Once the internal softstart discharge FET is turned on, it cannot be turned off until the internal softstart voltage drops down below 0.5V. This insures a clean restart.

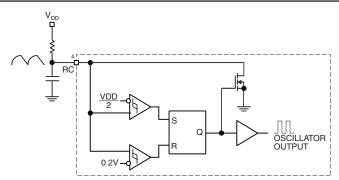

#### Oscillator

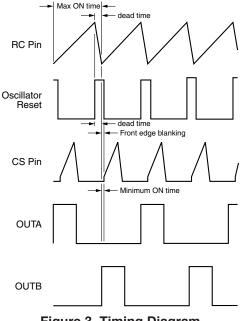

The oscillator operates at twice the switching frequency of either OUTA or OUTB. The oscillator generates a sawtooth waveform on the RC pin. The rising edge of the waveform is controlled by the external resistor/capacitor combination. The fall time is set by the on-resistance of the discharge FET (see Figure 2). The fall time sets the delay (dead time) between the turn-off of one output driver and the turn-on of the other driver. A toggle flip-flop insures that drive signals to OUTA and OUTB are alternated and therefore insures a maximum duty cycle of less than 50% for each output driver. Graphs of component values vs. oscillator frequency and dead time are shown in the typical characteristic section of this specification.

Figure 2. Oscillator

The voltage source to the resistor/capacitor timing components is V<sub>DD</sub>. The internal turn-off comparator threshold in the oscillator circuit is V<sub>DD</sub>/2. This allows the oscillator to track changes in V<sub>DD</sub> and minimize frequency variations in the oscillator. The oscillator frequency can be roughly approximated using the following formula:

F\_oscillator = 1.41/R\*C

Where: frequency is in Hz

Resistance is in Ohms

Capacitance is in Farads.

Graphs of oscillator frequency and dead time vs component values are shown in the Typical Characteristic section of this specification. The recommended range of timing resistors and capacitors is  $10k\Omega$  to  $200k\Omega$  and 100pF to 1000pF. To minimize oscillator noise and insure a stable waveform the following layout rules should be followed:

- 1. The higher impedance of capacitor values less than 100pF may causes the oscillator circuit to become more susceptible to noise. Parasitic pin and etch trace capacitances become a larger part of the total RC capacitance and may influence the desired switching frequency.

- 2. The circuit board etch between the timing resistor, capacitor, RC pin and ground must be kept as short as possible to minimize noise pickup and insure a stable oscillator waveform.

- 3. The ground lead of the capacitor must be routed close to the ground lead of the MIC3808/9.

#### **Current Sensing and Overcurrent Protection**

The CS pin features are:

- 1. Peak current limit

- 2. Overcurrent limit

- 3. Internal current sense discharge

- 4. Front edge blanking

In current mode control, a PWM comparator uses the inductor current signal and the error amplifier signal to determine the operating duty cycle. In the MIC3808/9 the signal at the CS pin is level shifted up before it reaches the PWM comparator as shown in Figure 1. This allows operation of the error amplifier and PWM comparator in a linear region.

There are two current limit thresholds in the MIC3808/9; peak current limit and overcurrent limit. The normal operating voltage at the CS pin is designed less than these thresholds.

A pulse-by-pulse current limit occurs when the inductor current signal at the CS pin exceeds the peak current limit threshold. The on-time is terminated for the remainder of the switching cycle, regardless of whether OUTA or OUTB is active.

If the signal at the CS pin goes past the peak threshold and exceeds the overcurrent limit threshold, the overcurrent limit comparator forces the soft start node to discharge and initiates a soft start reset.

An internal FET discharges the CS pin at the end of the oscillator charge time. The FET turns on when the voltage on the RC pin reaches the upper threshold ( $V_{DD}/2$ ) and remains on for the duration of the RC pin discharge time and for typically 100ns after the start of the next on-time period. The 100ns period at the beginning of the on-time implements a front edge blanking feature that prevents false triggering of the PWM comparator due to noise spikes on the leading edge of the current turn-on signal. The front edge blanking also sets the minimum on-time for OUTA and OUTB. The timing diagram for the CS pin is shown in Figure 3.

Figure 3. Timing Diagram

#### **Error Amplifier**

The error amplifier is part of the voltage control loop of the power supply. The FB pin is the inverting input to the error amplifier. The non-inverting input is internally connected to a reference voltage. The output of the error amplifier, COMP, is connected to the PWM comparator. A voltage divider between the error amplifier output (COMP pin) and the PWM comparator allows the error amplifier to operate in a linear region for better transient response. The output of the error amplifier (COMP pin) is limited to typically 3.65V to prevent the COMP pin from rising up too high during startup or during a transient condition. This feature improves the transient response of the power supply.

#### **Output Drivers**

OUTA and OUTB are alternating output stages, which switch at half the oscillator frequency. A toggle flip-flop in the MIC3808/9 guarantee both outputs will not be on at the same time. The RC discharge time is the dead time, where both outputs are off. This provides an adjustable non-overlap time to prevent shoot through currents and transformer saturation in the power supply.

The output drivers are inhibited when  $V_{\text{DD}}$  is below the undervoltage threshold. Internal circuitry prevents the output drivers from glitching high when  $V_{\text{DD}}$  is first applied to the MIC3808/9 controller.

#### **Decoupling and PCB Layout**

PCB layout is critical to achieve reliable, stable and efficient operation. A ground plane is required to control EMI and minimize the inductance in power, signal and return paths. The following guidelines should be followed to insure proper operation of the circuit:

Low level signal and power grounds should be kept separate and connected at only one location, preferably the ground pin of the control IC. The ground signals for the current sense, voltage feedback and oscillator should be grouped together. The return signals for the gate drives should be grouped together and a common connection made at the ground pin of the controller. The low level signals and their returns must be kept separate from the high current and high voltage power section of the power supply.

- Avoid running sensitive traces, such as the current sense and voltage feedback signals next to or under power components, such as the switching FETs and transformer.

- If a current sense resistor is used, it's ground end must be located very close to the ground pin of the MIC3808/ 9 controller. Careful PCB layout is necessary to keep the high current levels in the current sense resistor from running over the low level signals in the controller.

- A minimum 1µf bypass capacitor must be connected directly between the  $V_{DD}$  and GND pins of the MIC3808/ 9. An additional 0.1µf capacitor between the  $V_{DD}$  end oscillator frequency setting resistor and the ground end of the oscillator capacitor may be necessary if the resistor is a distance away from the main 1µF bypass capacitor