# Product Document

# **Datasheet**

DS000496

# **AS7225**

**Calibrated XYZ Chromatic Smart Lighting Director**

v2-00 • 2019-Jun-28

# **Content Guide**

| 1                                      | General Description                                                               | 3                    |

|----------------------------------------|-----------------------------------------------------------------------------------|----------------------|

| 1.1<br>1.2<br>1.3                      | Key Benefits & Features<br>Applications<br>Block Diagram                          | 4                    |

| 2                                      | Ordering Information                                                              | 6                    |

| 3                                      | Pin Assignment                                                                    | 7                    |

| 3.1<br>3.2                             | Pin Diagram Pin Description                                                       |                      |

| 4                                      | Absolute Maximum Ratings                                                          | 9                    |

| 5                                      | Electrical Characteristics                                                        | 10                   |

| 6                                      | Optical Characteristics                                                           | 11                   |

| 7                                      | Functional Description                                                            | 14                   |

| 7.1<br>7.2<br>7.3                      | Calibrated XYZ Chromatic Smart Lighti<br>Director – Overview<br>Inputs<br>Outputs | 14<br>16             |

| 8                                      | I <sup>2</sup> C Slave Interface                                                  |                      |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6 | I <sup>2</sup> C Feature List                                                     | 19<br>20<br>22<br>24 |

| 9                                      | I <sup>2</sup> C Master Interface (Local Ser                                      |                      |

|                                        | Interface)                                                                        |                      |

| 9.1<br>9.2                             | I <sup>2</sup> C Feature List                                                     |                      |

| 9.2                                    | I <sup>2</sup> C Write Access                                                     |                      |

| 9.4                                    | I <sup>2</sup> C Read Access                                                      | 27                   |

| 9.5                                    | I <sup>2</sup> C Master Timing Characteristics                                    | 28                   |

| 10                   | Register Description                                                           | 30 |

|----------------------|--------------------------------------------------------------------------------|----|

| 10.1<br>10.2         | Register Overview  Detailed Register Description                               |    |

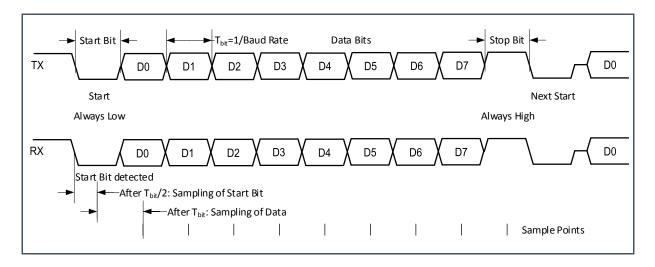

| 11                   | UART Command Interface                                                         | 51 |

| 11.2<br>11.3<br>11.4 | UART Protocol                                                                  | 52 |

| 12                   | Smart Lighting Command Interface                                               | 55 |

| 12.1                 | AT Commands                                                                    | 56 |

| 13                   | Application Information                                                        | 62 |

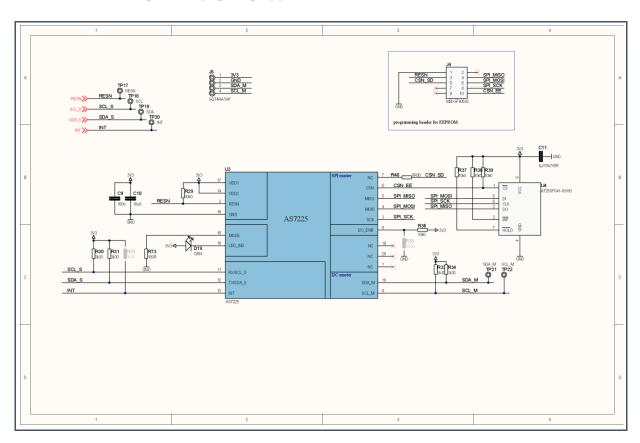

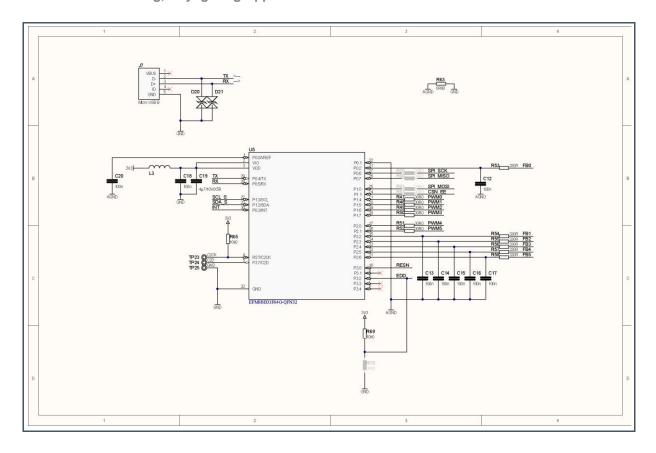

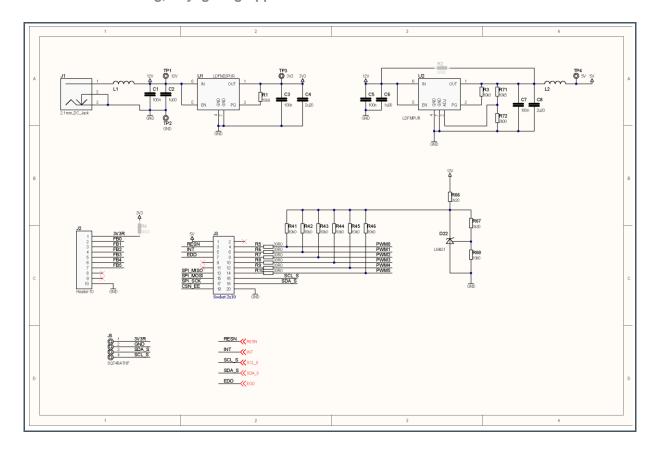

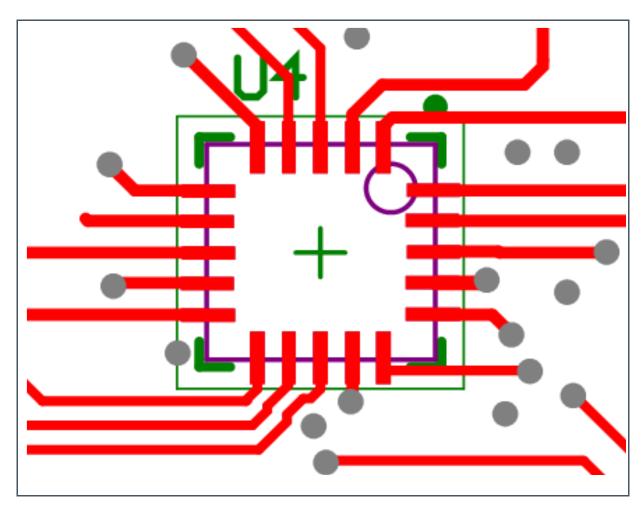

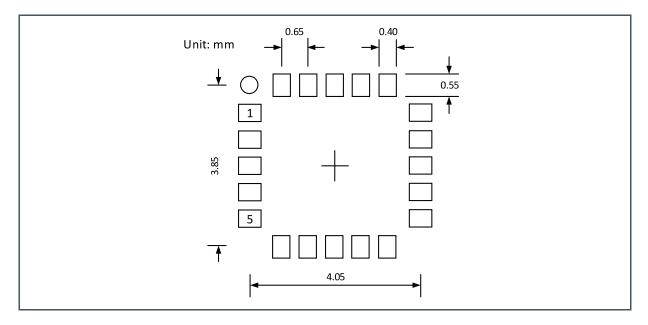

| 13.1<br>13.2<br>13.3 | SchematicPCB LayoutPCB Pad Layout                                              | 65 |

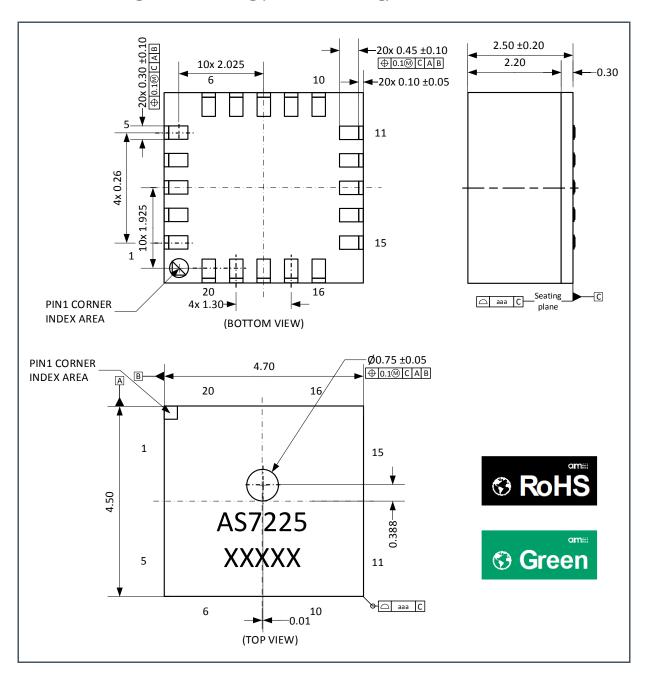

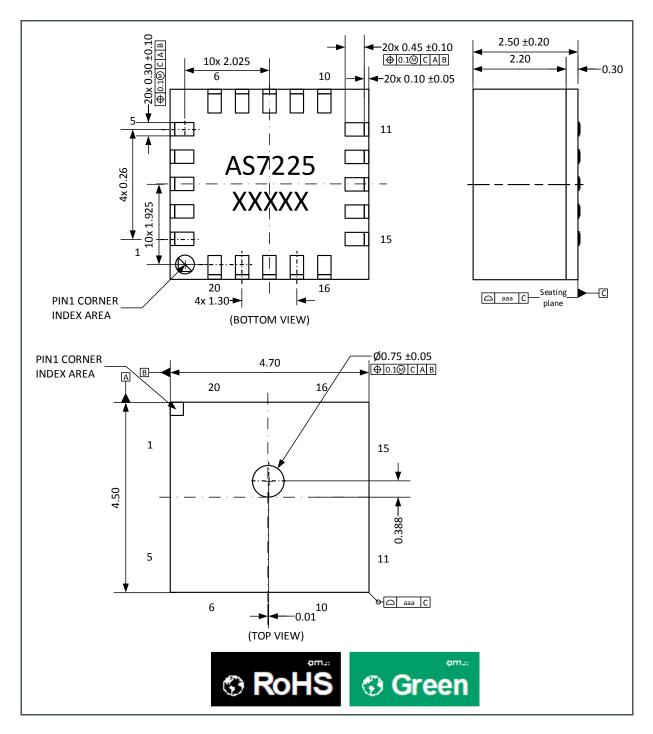

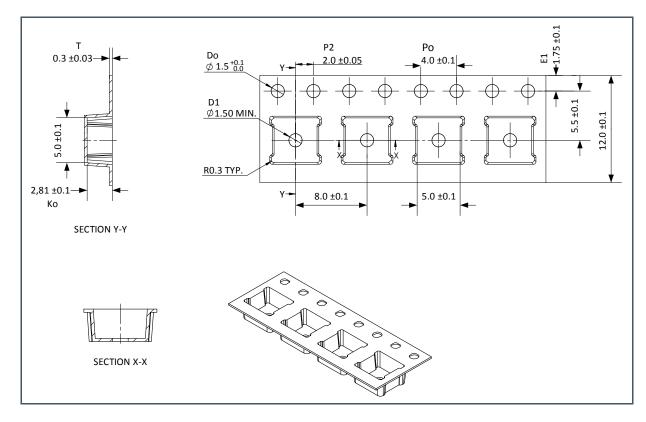

| 14                   | Package Drawings & Markings                                                    | 67 |

| 15                   | Tape & Reel Information                                                        | 69 |

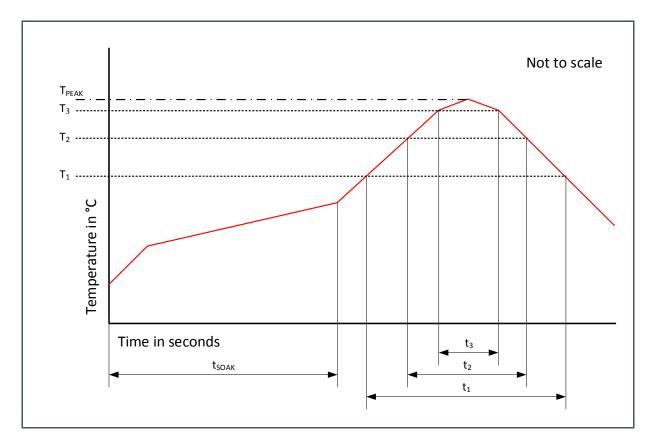

| 16                   | Soldering & Storage Information                                                | 70 |

| 16.1<br>16.2<br>16.3 | Manufacturing Process Considerations Storage Information Rebaking Instructions | 71 |

| 17                   | Revision Information                                                           | 73 |

| 18                   | Legal Information                                                              | 75 |

# 1 General Description

The AS7225 is designed for use directly in tunable white luminaires, replacement lamps (bulbs) and light-engines/modules. The AS7225 Smart Lighting Director incorporates an embedded digital tristimulus chromatic calibrated for life nano-optic sensor providing direct CIE1931 XYZ and CIE 1976 u'v' coordinate mapping. Adaptive algorithmic support enables a companion microprocess or to implement closed-loop, autonomous adjustment of variable CCT and daylight responsive LED lamps and luminaires. The AS7225 arrives pre-calibrated, and is designed for rapid integration into white-tunable and daylight responsive luminaire designs, delivering directives to the local microprocessor via an industry-standard I<sup>2</sup>C bus or UART interface.

An additional on-chip I²C master provides native support for select **ams** sensors, such as the TSL25721 or TSL45315 for combining in-looking CCT tunable director functions with outward-looking ambient light sensing and daylighting control. The AS7225's silicon via nano-optic deposited interference filters deliver high-stability over both time and temperature. The Director's integrated intelligence enables **ams** factory CCT calibration, which mitigates chip to chip variation. By combining this factory calibration with a supported luminaire design-level "application matrix", an end luminaire design can often eliminate the need for light-by-light calibration while delivering lifetime color control. With such a system calibration, accuracies within 2-4 Macadam steps are possible. The LGA package includes a built in aperture to control light entering the sensor array. No additional optics are required.

## 1.1 Key Benefits & Features

The benefits and features of AS7225, Calibrated XYZ Chromatic Smart Lighting Director, are listed below:

Figure 1: Added Value of Using AS7225

| Benefits                                                                                                                            | Features                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Provides accurate external host MCU supervision of variable CCT and spectrally tunable lighting                                     | Integrated intelligence with XYZ tri-stimulus color sensing for direct translation to CIE 1931 standard observer color map                                              |

| Uses accurate XYZ sensed data to provide a host MCU, with its own PWMs, simple to use directives for closed loop tuned LED lighting | Automatically directs external warm and cool white PWM controlled LED strings for chromatic LED luminaire tuning. Also directs dimming (combined with PWM color tuning) |

| Automatic spectral and lumen maintenance over temperature and time                                                                  | Supports autonomous color point and lumen output adjustment resulting in automatic spectral and lumen maintenance                                                       |

| Provides direct register or AT command based access to closed loop tuning directives                                                | I <sup>2</sup> C slave digital or UART Interface                                                                                                                        |

| Benefits                                                                                                                     | Features                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Used to interface other <b>ams</b> sensors with native support by the AS7225 (e.g. TSL2572 for adding Daylighting operation) | I <sup>2</sup> C master digital or UART interface                                                                             |

| Rapid luminaire integration                                                                                                  | Simple register-based or AT commands to control and configure key light-tuning supervisory and IoT sensor expansion functions |

| Complete data on lighting environment                                                                                        | Readable registers or AT commands for CIE 1931 and 1975 color-point coordinates, CCT, duv and lux                             |

| Calibrated sensing with minimal drift over time and temperature                                                              | Chromatic white color realized by silicon interference filters                                                                |

| Small package, with build in aperture                                                                                        | 20-pin LGA package 4.5 mm x 4.7 mm x 2.5 mm, with integrated aperture, -40 °C to 85 °C                                        |

# 1.2 Applications

- Commercial, retail, and residential CCT tunable LED lighting systems

- Higher precision replacement lamps/bulbs

- Intelligent, networked solid state lighting director for variable CCT chromatic tuning luminaires systems

- Integrated smart lighting control of variable CCT white lighting solutions

- Luminaires intended to meet California Title 24 daylighting requirements

- Networked lighting systems with IoT sensor expandability

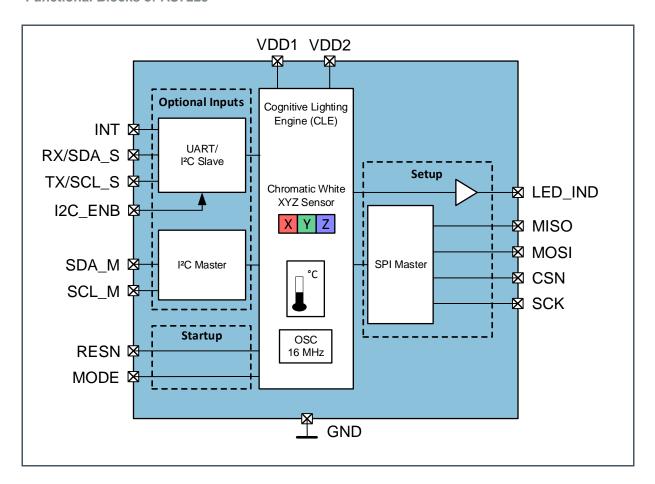

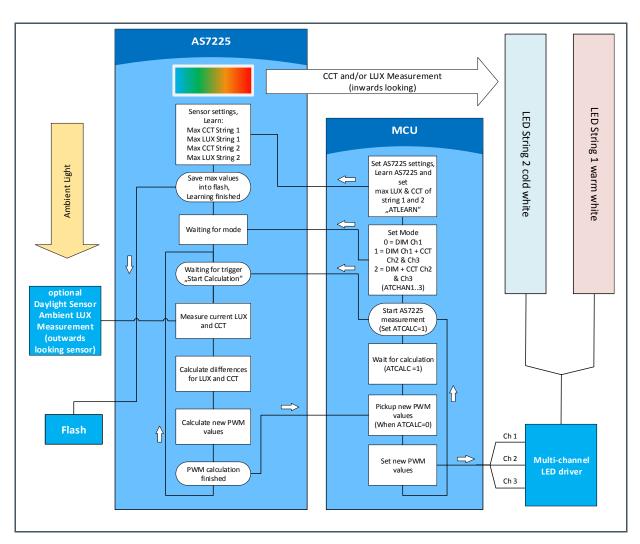

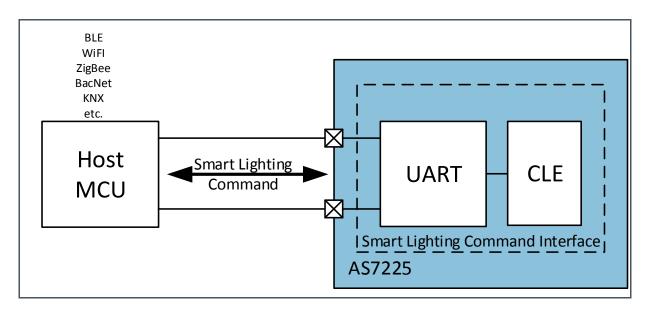

# 1.3 Block Diagram

The functional blocks of this device are shown below:

Figure 2: Functional Blocks of AS7225

# 2 Ordering Information

| Ordering<br>Code | Description                                                               | Package    | Marking | Delivery<br>Form           | Delivery<br>Quantity |

|------------------|---------------------------------------------------------------------------|------------|---------|----------------------------|----------------------|

| AS7225 –<br>BLGT | Calibrated XYZ<br>Chromatic Smart<br>Lighting Director –<br>Standard Reel | 20-Pin LGA | AS7225  | 13-inch Tape<br>& Reel     | 2000 pcs/reel        |

| AS7225 –<br>BLGM | Calibrated XYZ<br>Chromatic Smart<br>Lighting Director –<br>Mini Reel     | 20-Pin LGA | AS7225  | 7-inch Mini<br>Tape & Reel | 500 pcs/reel         |

# 3 Pin Assignment

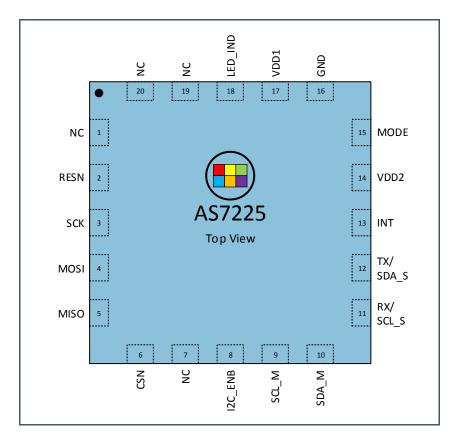

# 3.1 Pin Diagram

Figure 3: Pin Diagram for AS7225 (Top View)

# 3.2 Pin Description

Figure 4: Pin Description of AS7225

| Pin Number | Pin Name | Pin Type <sup>(1)</sup> | Description           |

|------------|----------|-------------------------|-----------------------|

| 1          | NC       | -                       | Not connected         |

| 2          | RESN     | DI                      | Reset pin, active low |

| 3          | SCK      | DI                      | SPI serial clock      |

| 4          | MOSI     | DO                      | SPI MOSI              |

| Pin Number | Pin Name | Pin Type <sup>(1)</sup> | Description                                                                      |

|------------|----------|-------------------------|----------------------------------------------------------------------------------|

| 5          | MISO     | DI                      | SPI MISO                                                                         |

| 6          | CSN      | DO                      | Chip select for the required external flash memory, active low                   |

| 7          | NC       | -                       | Not connected                                                                    |

| 8          | I2C_ENB  | DI                      | Select UART (Low) or I <sup>2</sup> C (High) Operation                           |

| 9          | SCL_M    | DI/O                    | I <sup>2</sup> C master clock pin                                                |

| 10         | SDA_M    | DI/O                    | I <sup>2</sup> C master data pin                                                 |

| 11         | RX/SCL_S | DI/O                    | RX (UART) or SCL_S (I <sup>2</sup> C Slave) Depending on I2C_ENB                 |

| 12         | TX/SDA_S | DI/O                    | TX (UART) or SDA_S (I <sup>2</sup> C Slave) Depending on I2C_ENB                 |

| 13         | INT      | DO                      | Interrupt, active low                                                            |

| 14         | VDD2     | Р                       | Voltage supply                                                                   |

| 15         | MODE     | DI                      | Mode selection pin. Set to Mode=0 via 1000hm resistor. Other Modes are reserved. |

| 16         | GND      | Р                       | Ground                                                                           |

| 17         | VDD1     | Р                       | Voltage supply                                                                   |

| 18         | LED_IND  | AO                      | LED Driver output for Indicator LED, current sink.                               |

| 19         | NC       | -                       | Not connected                                                                    |

| 20         | NC       | -                       | Not connected                                                                    |

(1) Explanation of abbreviations:

DI Digital Input

DO Digital Output

DI/O Digital In Out

AO Analog out

AI Analog In

P Power pin

# **Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. The device is not designed for high-energy UV (ultraviolet) environments, including upward looking outdoor applications, which could affect long-term optical performance. All voltages with respect to GND. Device parameters are guaranteed at VDD = 3.3 V and TAMB = 25 °C unless otherwise noted.

**Absolute Maximum Ratings of AS7225**

| Symbol                           | Parameter                              | Min  | Тур    | Max          | Unit | Comments                                          |

|----------------------------------|----------------------------------------|------|--------|--------------|------|---------------------------------------------------|

| Electrical Param                 | neters                                 |      |        |              |      |                                                   |

| V <sub>DD1_MAX</sub>             | Supply Voltage VDD1                    | -0.3 |        | 5            | V    | Pin VDD1 to GND                                   |

| V <sub>DD2_MAX</sub>             | Supply Voltage VDD2                    | -0.3 |        | 5            | V    | Pin VDD2 to GND                                   |

| $V_{DD\_IO}$                     | Input/Output Pin<br>Voltage            | -0.3 |        | VDD +<br>0.3 | V    | Low Voltage pins to GND                           |

| I <sub>SCR</sub>                 | Input Current (latch-up immunity)      |      | ± 100  |              | mA   | JESD78D                                           |

| Electrostatic Dis                | scharge                                |      |        |              |      |                                                   |

| ESD <sub>HBM</sub>               | Electrostatic Discharge<br>HBM         |      | ± 1000 |              | V    | JS-001-2014                                       |

| ESD <sub>CDM</sub>               | Electrostatic Discharge<br>CDM         |      | ± 500  |              | V    | JEDEC JESD22-<br>C101F Oct 2013                   |

| Temperature Ra                   | nges and Storage Conditions            |      |        |              |      |                                                   |

| T <sub>STRG</sub>                | Storage Temperature<br>Range           | -40  |        | 85           | °C   |                                                   |

| T <sub>BODY</sub>                | Package Body<br>Temperature            |      |        | 260          | °C   | IPC/JEDEC J-STD-<br>020 (1)                       |

| RH <sub>NC</sub>                 | Relative Humidity (non-<br>condensing) | 5    |        | 85           | %    |                                                   |

| MSL                              | Moisture Sensitivity<br>Level          |      | 3      |              |      | Represents a 168-<br>hour max. floor<br>lifetime. |

| Bump Temperat                    | ure (soldering)                        |      |        |              |      |                                                   |

| T <sub>PEAK</sub> <sup>(1)</sup> | Peak Temperature                       | 235  |        | 245          | °C   | Solder Profile                                    |

<sup>(1)</sup> The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices." The lead finish for Pb-free leaded packages is "Matte Tin" (100 % Sn)

# **5** Electrical Characteristics

All limits are guaranteed with VDD = VDD1 = VDD2 = 3.3 V,  $T_{\text{AMB}} = 25 \,^{\circ}\text{C}$ . The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods. If VDD1 and VDD2 must be sourced by the same  $2.97 \,^{\circ}\text{V}$  to  $3.6 \,^{\circ}\text{V}$  supply. All voltages with respect to GND.

Figure 6: Electrical Characteristics of AS7225

| Symbol                            | Parameter                                                          | Conditions                      | Min     | Тур | Max              | Unit |

|-----------------------------------|--------------------------------------------------------------------|---------------------------------|---------|-----|------------------|------|

| General Operati                   | ng Conditions                                                      |                                 |         |     |                  |      |

| VDD1 / VDD2                       | Voltage Operating<br>Supply                                        |                                 | 2.97    | 3.3 | 3.6              | V    |

| Т <sub>АМВ</sub>                  | Operating Temperature                                              |                                 | -40     | 25  | 85               | °C   |

| I <sub>VDD</sub>                  | Operating Current                                                  |                                 |         |     | 5                | mA   |

| Internal RC Osc                   | illator                                                            |                                 |         |     |                  |      |

| F <sub>osc</sub>                  | Internal RC Oscillator<br>Frequency                                |                                 | 15.7    | 16  | 16.3             | MHz  |

| t <sub>JITTER</sub> (1)           | Jitter                                                             | @25 °C                          |         |     | 1.2              | ns   |

| Temperature Se                    | ensor                                                              |                                 |         |     |                  |      |

| $D_Temp$                          | Absolute Accuracy of<br>the Internal<br>Temperature<br>Measurement |                                 | -8.5    |     | 8.5              | °C   |

| Indicator LED                     |                                                                    |                                 |         |     |                  |      |

| I <sub>IND</sub>                  | LED Current                                                        |                                 | 1       |     | 8                | mA   |

| I <sub>ACC</sub>                  | Accuracy of Current                                                |                                 | -30     |     | 30               | %    |

| $V_{LED}$                         | Voltage Range of Connected LED                                     | V <sub>DS</sub> of current sink | 0.3     |     | VDD              | V    |

| Digital Inputs a                  | nd Outputs                                                         |                                 |         |     |                  |      |

| I <sub>IH</sub> , I <sub>IL</sub> | Logic Input Current                                                | V <sub>in</sub> =0 V or VDD     | -1      |     | 1                | μΑ   |

| V <sub>IH</sub>                   | CMOS Logic High<br>Input                                           |                                 | 0.7*VDD |     | VDD              | V    |

| V <sub>IL</sub>                   | CMOS Logic Low Input                                               |                                 | 0       |     | 0.3*VDD          | V    |

| V <sub>OH</sub>                   | CMOS Logic High<br>Output                                          | I=1 mA                          |         |     | VDD-0.4          | V    |

| V <sub>OL</sub>                   | CMOS Logic Low<br>Output                                           | I=1 mA                          |         |     | 0.4              | V    |

| t <sub>RISE</sub>                 | Current Rise Time                                                  | C(Pad)=30 pF                    |         |     | 5                | ns   |

| t <sub>FALL</sub>                 | Current Fall Time                                                  | C(Pad)=30 pF                    |         |     | 5 <sup>(1)</sup> | ns   |

|                                   |                                                                    |                                 |         |     |                  |      |

<sup>(1)</sup> Guaranteed, not production tested.

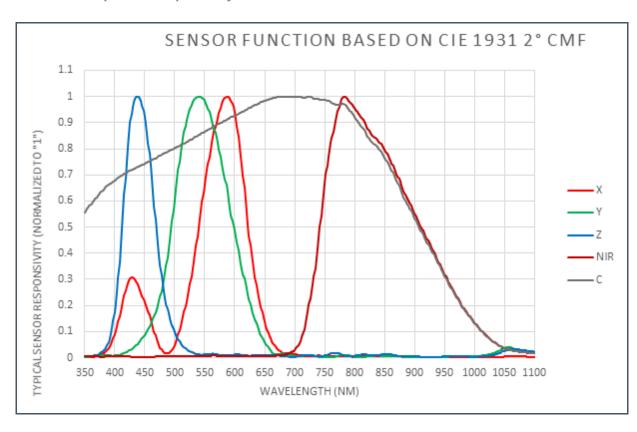

# **6** Optical Characteristics

The AS7225 contains an integrated tristimulus sensing element designed to meet the XYZ standard observer response compliant with the CIE 1931 standard. The device contains a 16-bit integrating analog-to-digital converter, which integrates current from the photodiodes. To ensure the integrity of the data, upon completion of an integration cycle, results are transferred to double-buffered registers.

Standard observer tristimulus (XYZ) interference filters are applied to the Calibrated XYZ Chromatic Smart Lighting Director optical channels as part of the CMOS process. This unique process enables filter responses that mimic the human eye and is extremely stable over both operating temperature and time. This in turn allows lifetime correlated color temperature (CCT) calibration to be performed as part of the manufacturing process. Calibration is accomplished using standard white LEDs at a variety of CCTs to deliver high accuracy and typically eliminate the need for light-by-light calibration in most designs. Note, that any change of the pre-calibrated measurement conditions have an impact on the accuracy of the measurement results. In such cases a design-level diffuser or color brightness calibration is recommended to achieve highest accuracies. The AS7225 provides 2 calibration matrices, a factory calibration and a second application specific matrix to optimize the measurement performance. The additional calibration values will be set using the Smart Lighting Command Set directives ATNORMGAIN and ATNORMINTT. These settings will be saved in the external flash and reloaded automatically by the sensor firmware. See Section 12 for description of the complete Smart Lighting Command Set.

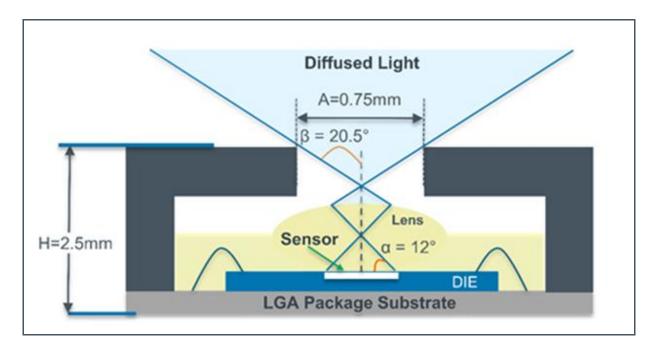

The AS7225 LGA package contains an internal aperture that provides a package field of view (PFOV) of ± 20.5°. External optics can be used as needed to expand or reduce this built in PFOV.

Sensor data readout to the maximum count value range is limited by the ADC. The maximum count range value of 65535 is only reached with an integration time  $t_{\rm INT}$  of approximately 177.92ms. Below that value, the FSR will be less than the maximum 16-bit /65536 count maximum as described in the chart below.

Figure 7:

Overview Signal Resolution

| Bit Resolution | t <sub>INT</sub> in ms | Maximum Counts |

|----------------|------------------------|----------------|

| 10             | 2.78                   | 1024           |

| 11             | 5.56                   | 2048           |

| 12             | 11.12                  | 4096           |

| 13             | 22.24                  | 8192           |

| 14             | 44.48                  | 16384          |

| 15             | 88.96                  | 32768          |

| 16             | 177.92                 | 65536          |

Figure 8: AS7225 Optical Characteristics

| Symbol                 | Parameter                        | Conditions                                                 | Min   | Typ <sup>(1)</sup> | Max   | Unit                |

|------------------------|----------------------------------|------------------------------------------------------------|-------|--------------------|-------|---------------------|

| Color_m <sup>(2)</sup> | Color<br>Measurement<br>Accuracy | White light<br>CCT=2700 K,<br>3500 K, 4500 K<br>and 5700 K |       | 0.002              |       | du'v'               |

| Z_count                | Z Channel<br>Count Accuracy      | White light CCT = 5700 K                                   | 3.375 | 4.5                | 5.625 | counts/<br>(µW/cm²) |

- (1) Typical values at Lux  $\geq$ 50, integration time = 400.4 ms. Gain = 1x,  $T_{AMB}$  = 25 °C

- (2) Calibration and measurements are made using diffused light

Figure 9: Normalized Spectral Responsivity

Figure 10: AS7225 LGA Average Field of View

# 7 Functional Description

### 7.1 Calibrated XYZ Chromatic Smart Lighting Director – Overview

By sensing a sample of the mixed warm and cool CCTs as either a reflection from the diffuser or other light-guide/optical light gathering technique, the AS7225 serves as a calibrated chromatic smart lighting director for a companion host MCU. Please note, that non-diffused applications require some form of reflective or other light gathering that delivers an adequate sample of mixed light to the sensor. Care should be taken to fulfill the angle of incidence requirements of the nano-optic filter set. Director operation also provides selectable dimming information for either PWM-based or current-based luminaire dimming designs.

Figure 11: AS7225 Workflow Abstract

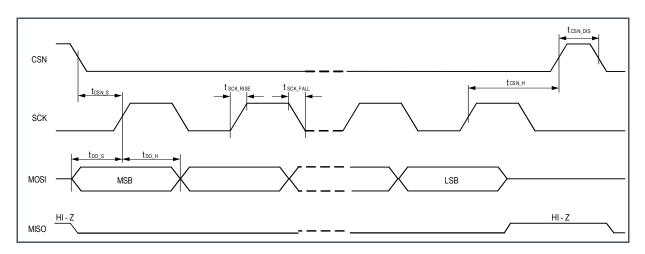

The AS7225 initial setup and ongoing parameter storage is automatically done by software within the required external serial Flash memory, via SPI bus. Only **ams**-verified models of Flash devices can be supported. A subset of supported devices is noted in the UART Command Interface section of this document, which also provides a reference to the current list of supported Flash memory devices. For the Flash memory, overview please refer to Figure 83. A SPI Flash device is a required operating companion to the AS7225. Using other devices can cause communication issues and may not be compatible. Flash timing is provided in Figure 81 and Figure 82.

A binary image software configuration tool is available from **ams** to allow the luminaire, lamp or driver manufacturer to create their own "factory default" conditions that will be integrated with the **ams**—supplied initial binary image to create a ready-to-program default Flash image. The configuration tool is available from <a href="https://download.ams.com">https://download.ams.com</a> (see Smart Lighting Command Interface section).

XYZ white color point measurement is accomplished via nano-optic interference filters, which deliver a CIE standard-observer type spectral response. As an extension of the CMOS processing of the device, the filters are extremely stable over time and temperature. To minimize off-angle light exposure and ensure accuracy, the AS7225 LGA package contains an internal aperture that limits the sensor field of view (PFOV) of ± 20.5°, as shown in the Figure 1 above. External optics can be used as needed to expand or reduce this built in PFOV.

For daylight operation, the AS7225 can be used two ways. As a standalone device pointing out of the luminaire, or if pointing inward for white color, it can support daylighting operation by using an I<sup>2</sup>C master connected (ams TSL25721 or TSL45315) for ambient light sensing. In either case, the AS7225 is the daylighting engine and directs the external MCU.

TSL25721 device combines a channel 0 (CH0) which is responsive to both visible and infrared light, and channel 1 (CH1) which is responsive primarily to infrared light. Therefore, to get the LUX, a calibration is necessary. In this calibration, both channels has to be considered. First counts per lux (CPL) needs to be calculated in this calibration method.

Counts per LUX (CPL):

$$CPL = \frac{CH0 - (1.87 * CH1)}{LUX}$$

Calibration scalar:

$$LUX = K0 * ADC0 - K1 * ADC1$$

Default setting K0 is 0.2178 (normal sunlight conditions in Europe in May, 1m distance to a window). If K0=0, the result for K1 will be inverted to prevent negative LUX values. At different light conditions, this value has to adjust.

Example:

Spectrometer value = 9764 Lux, CH0 = 22870, CH1 = 2734 $\rightarrow$  CPL = 1.8186

K0 = 1/CPL = 0.549855,

K1 = 1.87/CPL = 1.028228

To save the values, write in the console tab, ATLXSL0=0.549855 and ATLXSL1= 1.028228

Overall AS7225 timing generation uses an on chip 16MHz temperature compensated oscillator for master clock timing.

#### 7.2 Inputs

#### 7.2.1 Mode Pin

The AS7225 MODE pin must be connected to ground (GND) via a 100  $\Omega$  resistor (1%) to set the AS7225 mode of operation. All other MODEs (using other resistor values) are reserved.

#### **7.2.2** Reset

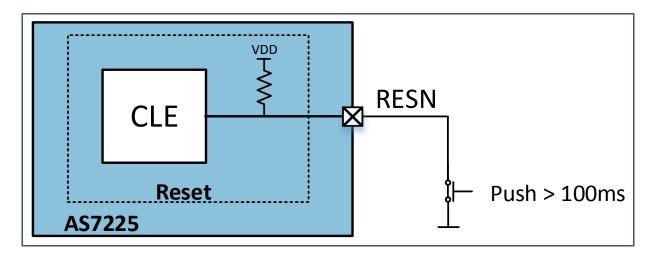

Pulling down the RESN pin for longer than 100 ms resets the AS7225.

Figure 12: Reset Circuit

## 7.3 Outputs

#### 7.3.1 Indicator LED

An LED, when connected to pin LED\_IND, is used to indicate on state and programming progress of the device. During companion SPI Flash programming the AS7225 indicator LED is off. When

programming is finished and the programming tool is disconnected the indicator LED turns on. In case of an error while programming the LED starts a blinking operation.

The LED\_IND pin is set for 1 mA LED operation by the AS7225 factory firmware, and is not under user control. The indicator LED can be enabled or disabled by using the ATLED0 command or the LED\_CONFIG register (0x07). Consideration should be taken with respect to any final product design to avoid light intrusion from the indicator LED into the direct or reflected field of view of the sensor.

Refer to the separate **ams** document for a complete description of AS7225 Firmware Update Methodology.

#### 7.3.2 Interrupt Operation

The INT-pin informs the external MCU that the calculation of new PWM values is finished and the data are ready to read. To activate the INT-pin, bit1 of the DIR\_CONF command has to be enabled (INT=1). By using UART the ATINTRP command has to be enabled. When the DATA\_RDY register bit finished the integration and the new PWM value calculation is finished the INT-pin of the DIR\_CONF register pulled down to 0. After reading of the PWM values due to the external MCU the INT-pin will be reset to 1 automatically.

# 8 I<sup>2</sup>C Slave Interface

Interface and control can be accomplished through an I<sup>2</sup>C compatible slave interface to a set of registers that access device control functions and output data. These control and output registers on the AS7225 are, in reality, implemented as virtual registers in software. The actual I<sup>2</sup>C slave hardware registers number only three and are described in the table below. The steps necessary to access the virtual registers defined in the pages that follow are explained in pseudocode for external I<sup>2</sup>C master writes and reads below. A compatible companion Flash device must be incorporated and preprogrammed for I<sup>2</sup>C virtual-registers to function.

#### 8.1 I<sup>2</sup>C Feature List

- Fast mode (400 kHz) and standard mode (100 kHz) support

- 7+1-bit addressing mode

- Write format: ByteRead format: Byte

Figure 13:

I<sup>2</sup>C Slave Device Address and Physical Registers

| Entity                  | Description                                                      | Note                                                                                                                                                                                                                                                    |

|-------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Slave<br>Address | 8-bit slave address                                              | Byte = 1001001x (device address = 49 h)<br>x= 1 for Master Read (byte = 93 h)<br>x= 0 for Master Write (byte = 92 h)                                                                                                                                    |

| STATUS Register         | I <sup>2</sup> C slave interface<br>STATUS register<br>Read-only | Register Address = 0x00h  Bit 1: TX_VALID  0 -> New data may be written to WRITE register  1 -> WRITE register occupied. Do NOT write.  Bit 0: RX_VALID  0 -> No data is ready to be read in READ register.  1 -> Data byte available in READ register. |

| WRITE Register          | I <sup>2</sup> C slave interface<br>WRITE register<br>Write-only | Register Address = 0x01<br>8 bits of data written by the I <sup>2</sup> C Master intended for<br>receipt by the I <sup>2</sup> C slave. Used for both virtual register<br>addresses and write data.                                                     |

| READ Register           | I <sup>2</sup> C slave interface<br>READ register<br>Read-only   | Register Address = 0x02<br>8 bits of data to be read by the I <sup>2</sup> C Master.                                                                                                                                                                    |

### 8.2 I<sup>2</sup>C Virtual Register Write Access

I<sup>2</sup>C Virtual Resister Byte Write, detailed below, shows the pseudocode necessary to write virtual registers on the AS7225. Note that, because the actual registers of interest are realized as virtual registers, a means of indicating whether there is a pending read or write operation of a given virtual register is needed. To convey this information, the most significant bit of the virtual register address is used as a marker. If it is 1, then a write is pending, otherwise the slave is expecting a virtual read operation. The pseudocode illustrates the proper technique for polling of the I<sup>2</sup>C slave status register to ensure the slave is ready for each transaction.

#### 8.2.1 I<sup>2</sup>C Virtual Register Byte Write

#### **Pseudocode**

- Poll I<sup>2</sup>C slave STATUS register;

If TX\_VALID bit is 0, a write can be performed on the interface;

- 3 Send a virtual register address and set the MSB of the register address to 1 to indicate the pending write;

- 4 Poll I<sup>2</sup>C slave STATUS register;

- If TX\_VALID bit is 0, the virtual register address for the write has been received and the data may now be written;

- 6 Write the data.

#### Sample Code

```

// Read slave I2C status to see if the write buffer is ready.

status = i2cm_read(I2C_AS72XX_SLAVE_STATUS_REG) ;

if ((status & I2C AS72XX SLAVE TX VALID) == 0)

// No inbound TX pending at slave. Okay to write now.

break;

}

// Send the virtual register address (setting bit 7 to indicate a pending

write).

i2cm_write(I2C_AS72XX_SLAVE_WRITE_REG, (virtualReg | 0x80));

while (1)

{

// Read the slave I2C status to see if the write buffer is ready.

Status = i2cm_read(I2C_AS72XX_SLAVE_STATUS_REG) ;

if ((status & I2C_AS72XX_SLAVE_TX_VALID) == 0)

// No inbound TX pending at slave. Okay to write data now.

break;

}

// Send the data to complete the operation.

i2cm_write(I2C_AS72XX_SLAVE_WRITE_REG, d);

}

```

### 8.3 I<sup>2</sup>C Virtual Register Read Access

I<sup>2</sup>C Virtual Register Byte Read, detailed below, shows the pseudocode necessary to read virtual registers on the AS7225. Note that in this case, reading a virtual register, the register address is not modified.

#### 8.3.1 I<sup>2</sup>C Virtual Register Byte Read

```

Pseudocode

Poll I<sup>2</sup>C slave STATUS register;

If TX_VALID bit is 0, the virtual register address for the read may be

2

written;

3

Send a virtual register address;

4

Poll I<sup>2</sup>C slave STATUS register;

5

If RX_VALID bit is 1 the read data is ready;

Read the data.

Sample Code

uint8_t i2cm_AS72xx_read(uint8_t virtualReg)

{

volatile uint8_t status, d;

while (1)

{

// Read slave I2C status to see if the read buffer is ready.

Status = i2cm_read(I2C_AS72XX_SLAVE_STATUS_REG) ;

if ((status & I2C_AS72XX_SLAVE_TX_VALID) == 0)

// No inbound TX pending at slave. Okay to write now.

```

// Send the virtual register address (setting bit 7 to indicate a pending

i2cm\_write(I2C\_AS72XX\_SLAVE\_WRITE\_REG, virtualReg);

// Read the slave I2C status to see if our read data is available.

status = i2cm\_read(I2C\_AS72XX\_SLAVE\_STATUS\_REG);

break ;

```

Datasheet • PUBLIC

DS000496 • v2-00 • 2019-Jun-28

```

}

{

write).

while (1)

The details of the i2cm\_read() and i2cm\_write() functions in previous Figures are dependent upon the nature and implementation of the external I2C master device.

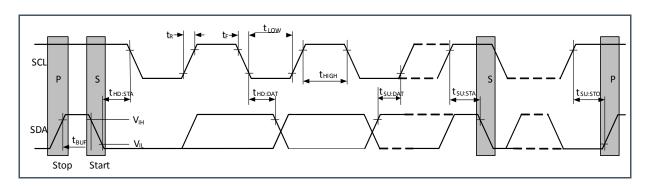

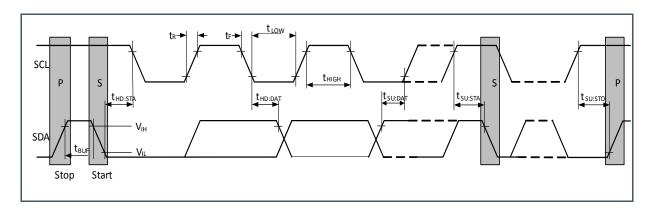

# 8.4 I<sup>2</sup>C Slave Timing Characteristics

Figure 14: Electrical Characteristics of AS7225

| Symbol                     | Parameter                                    | Conditions | Min | Тур | Max | Unit |

|----------------------------|----------------------------------------------|------------|-----|-----|-----|------|

| I <sup>2</sup> C Interface |                                              |            |     |     |     |      |

| f <sub>SCLK</sub>          | SCL Clock Frequency                          |            | 0   | 100 | 400 | kHz  |

| t <sub>BUF</sub>           | Bus Free Time<br>Between a STOP and<br>START |            | 1.3 |     |     | μs   |

| thd:sta                    | Hold Time<br>(Repeated) Start                |            | 0.6 |     |     | μs   |

| tLOW                       | LOW Period of SCL<br>Clock                   |            | 1.3 |     |     | μs   |

| tніgн                      | HIGH Period of SCL<br>Clock                  |            | 0.6 |     |     | μs   |

| tsu:sta                    | Setup Time for a<br>Repeated START           |            | 0.6 |     |     | μs   |

| t <sub>HD:DAT</sub>        | Data Hold Time                               |            | 0   |     | 0.9 | μs   |

| t <sub>SU:DAT</sub>        | Data Setup Time                              |            | 100 |     |     | ns   |

| t <sub>R</sub>             | Rise Time of Both<br>SDA and SCL             |            | 20  |     | 300 | ns   |

| t <sub>F</sub>             | Fall Time of Both<br>SDA and SCL             |            | 20  |     | 300 | ns   |

| Symbol           | Parameter                            | Conditions                                   | Min | Тур | Max | Unit |

|------------------|--------------------------------------|----------------------------------------------|-----|-----|-----|------|

| tsu:sto          | Setup Time for STOP Condition        |                                              | 0.6 |     |     | μs   |

| Св               | Capacitive Load for<br>Each Bus Line | CB — total capacitance of one bus line in pF |     |     | 400 | pF   |

| C <sub>I/O</sub> | I/O Capacitance (SDA, SCL)           |                                              |     |     | 10  | pF   |

Figure 15: I<sup>2</sup>C Slave Timing Diagram

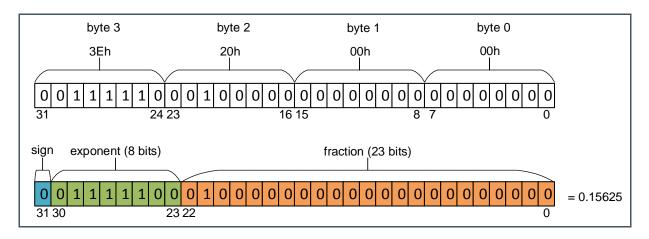

# 8.5 4-Byte Floating-Point (FP) Registers

In addition to single and two byte, several 4-byte registers (hex) are shown in the tables starting below. Here is an example of how the registers are used to represent floating point data (based on the IEEE 754 standard):

Figure 16: Example of the IEEE 754 Standard

The floating-point (FP) value assumed by 32-bit binary data with a biased exponent e (the 8-bit unsigned integer) and a 23-bit fraction is (for the above example):

#### **Equation 1:**

FPvalue =

$$(-1)^{sign} \left( 1 + \sum_{i=1}^{23} b_{23-i} 2^{-i} \right) \times 2^{(e-127)}$$

#### **Equation 2:**

FP value =

$$(-1)^0 \left(1 + \sum_{i=1}^{23} b_{23-i} 2^{-i}\right) \times 2^{(124-127)}$$

#### **Equation 3:**

$$FPvalue = 1 \times (1 + 2^{-2}) \times 2^{(-3)} = 0.15625$$

# 8.6 I<sup>2</sup>C Virtual Register Set

A register overview and a detailed description of the AS7225 I<sup>2</sup>C register set you find in chapter 10. All register data are hex, and all multi-byte entities are Big Endian (most significant byte is situated at the lowest register address).

Multiple byte registers (2-byte integer or 4-byte floating point) must be read in the order of ascending register addresses (low to high). In addition, if capable of being written to, have to be written in the order of ascending register addresses as well.

# 9 I<sup>2</sup>C Master Interface (Local Sensor Interface)

The I<sup>2</sup>C Master interface can be used to connect external sensors such as the current TSL25721 or legacy TSL45315 ambient light sensor (or other external sensors with AS7225 native support). Once the AS7225 has detected the supported ambient light sensor, daylight-responsive dimming directives can be activated by using the ATCHANMOD command or DIR\_CONF register.

#### 9.1 I<sup>2</sup>C Feature List

- Clock is set to 400 kHz

- 7+1-bit addressing mode.

- Write formats: Single-Byte-Write, Page-Write

- Read formats: Random-Read, Sequential-Read

#### 9.2 I<sup>2</sup>C Protocol

Figure 17:

I<sup>2</sup>C Symbol Definition

| Symbol  | Definition                   | RW | Note               |

|---------|------------------------------|----|--------------------|

| S       | Start condition after stop   | R  | 1-bit              |

| Sr      | Repeated start               | R  | 1-bit              |

| SW      | Slave address for write      | R  | Slave address      |

| SR      | Slave address for read       | R  | Slave address      |

| WA      | Word address                 | R  | 8-bit              |

| А       | Acknowledge                  | W  | 1-bit              |

| N       | No Acknowledge               | R  | 1-bit              |

| Data    | Data/write                   | R  | 8-bit              |

| Data(n) | Data/read                    | W  | 8-bit              |

| Р       | Stop condition               | R  | 1-bit              |

| WA++    | Slave increment word address | R  | During acknowledge |

The above I<sup>2</sup>C symbol definition table describes the symbols used in the following Read and Write descriptions.

#### 9.3 I<sup>2</sup>C Write Access

Byte Write and Page Write formats are used to write data to the slave.

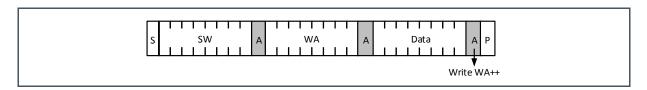

Figure 18: I<sup>2</sup>C Byte Write

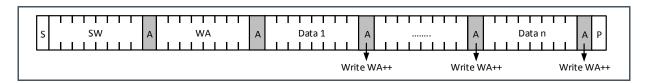

Figure 19: I<sup>2</sup>C Page Write

The transmission begins with the START condition, which is generated by the master when the bus is in IDLE state (the bus is free). The device-write address is followed by the word address. After the word address, any number of data bytes can be sent to the slave. The word address is incremented internally, in order to write subsequent data bytes on subsequent address locations.

For reading data from the slave device, the master has to change the transfer direction. This can be done either with a repeated START condition followed by the device-read address, or simply with a new transmission START followed by the device-read address, when the bus is in IDLE state. The device-read address is always followed by the first register byte transmitted from the slave. In Read Mode, any number of subsequent register bytes can be read from the slave. The word address is incremented internally.

### 9.4 I<sup>2</sup>C Read Access

Random, Sequential and Current Address Read are used to read data from the slave.

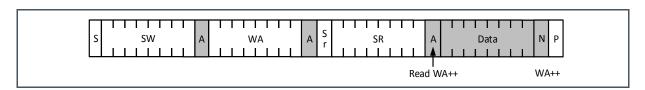

Figure 20: I<sup>2</sup>C Random Read

Random Read and Sequential Read are combined formats. The repeated START condition is used to change the direction after the data transfer from the master.

The word address transfer is initiated with a START condition issued by the master while the bus is idle. The START condition is followed by the device-write address and the word address.

In order to change the data direction a repeated START condition is issued on the first SCL pulse after the acknowledge bit of the word address transfer. After the reception of the device-read address, the slave becomes the transmitter. In this state, the slave transmits register data located by the previous received word address vector. The master responds to the data byte with a not-acknowledge, and issues a STOP condition on the bus.

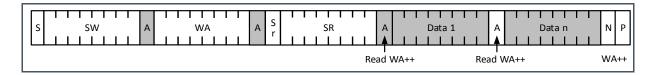

Figure 21: I<sup>2</sup>C Sequential Read

Figure 21 shows the format of an I<sup>2</sup>C sequential read access. Sequential Read is the extended form of Random Read, as more than one register-data bytes are transferred subsequently. In difference to the Random Read, for a sequential read the transferred register-data bytes are responded by an acknowledgement from the master. The number of data bytes transferred in one sequence is unlimited (consider the behavior of the word-address counter). To terminate the transmission the master has to send a not-acknowledge following the last data byte and generate the STOP condition subsequently.

The AS7225 is compatible to the NXP two wire specifications. http://www.nxp.com/documents/user\_manual/UM10204.pdf Version 4.0 Feb 2012 for standard mode and fast mode.

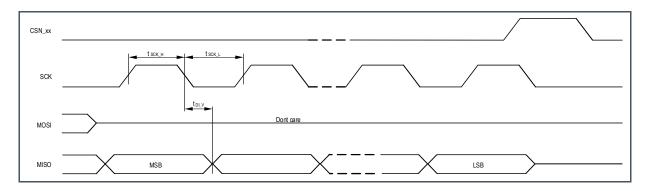

# 9.5 I<sup>2</sup>C Master Timing Characteristics

Figure 22: I<sup>2</sup>C Master Timing Characteristics

| Symbol                   | Parameter                              | Conditions | Min | Тур | Max | Unit |

|--------------------------|----------------------------------------|------------|-----|-----|-----|------|

| I <sup>2</sup> C Interfa | ce                                     |            |     |     |     |      |

| f <sub>SCLK</sub>        | SCL Clock Frequency                    |            |     | 400 | 400 | kHz  |

| tBUF                     | Bus Free Time Between a STOP and START |            | 1.3 |     |     | μs   |

| thd:sta                  | Hold Time (Repeated)<br>START          |            | 0.6 |     |     | μs   |

| t <sub>LOW</sub>         | LOW Period of SCL Clock                |            | 1.3 |     |     | μs   |

| Symbol           | Parameter                            | Conditions                                         | Min | Тур | Max | Unit |

|------------------|--------------------------------------|----------------------------------------------------|-----|-----|-----|------|

| tнідн            | HIGH Period of SCL Clock             |                                                    | 0.6 |     |     | μs   |

| tsu:sta          | Setup Time for a Repeated START      |                                                    | 0.6 |     |     | μs   |

| thd:dat          | Data Hold Time                       |                                                    | 0   |     | 0.9 | μs   |

| tsu:dat          | Data Setup Time                      |                                                    | 100 |     |     | ns   |

| t <sub>R</sub>   | Rise Time of Both SDA and SCL        |                                                    | 20  |     | 300 | ns   |

| t <sub>F</sub>   | Fall Time of Both SDA and SCL        |                                                    | 20  |     | 300 | ns   |

| tsu:sto          | Setup Time for STOP<br>Condition     |                                                    | 0.6 |     |     | μs   |

| Св               | Capacitive Load for Each<br>Bus Line | CB – total<br>capacitance of<br>one bus line in pF |     |     | 400 | pF   |

| C <sub>I/O</sub> | I/O Capacitance (SDA, SCL)           |                                                    |     |     | 10  | pF   |

Figure 23: I<sup>2</sup>C Master Timing Diagram

# 10 Register Description

# 10.1 Register Overview

Figure 24: I<sup>2</sup>C Virtual Register Overview

| Adress   | Name                 | <d7></d7> | <d6></d6> | <d5></d5> | <d4></d4> | <d3></d3> | <d2></d2> | <d1></d1>    | <d0></d0>   |

|----------|----------------------|-----------|-----------|-----------|-----------|-----------|-----------|--------------|-------------|

| Device V | ersion Registers     |           |           |           |           |           |           |              |             |

| 0x00     | HW_V_H               |           |           |           |           |           |           |              |             |

| 0x01     | HW_V_L               |           |           |           |           |           |           |              |             |

| 0x02     | FW_V_H               |           |           |           |           |           |           |              |             |

| 0x03     | FW_V_L               |           |           |           |           |           |           |              |             |

| General  | Setup and Control R  | egisters  | ;         |           |           |           |           |              |             |

| 0x04     | CONFIGURATIO<br>N    | SRST      | RSVD      | G/        | AIN       | RS        | SVD       | DATA<br>_RDY | FRST        |

| 0x05     | INTEGRATION_T<br>IME |           |           |           |           |           |           |              |             |

| 0x06     | TEMPERATURE          |           |           |           |           |           |           |              |             |

| 0x07     | LED_CONFIG           |           |           |           |           |           |           |              | LED_I<br>ND |

| 0x4F     | ESP                  |           |           |           |           |           |           |              |             |

| Director | Operations Register  | r         |           |           |           |           |           |              |             |

| 0x60     | DIR_CONF             |           | CHAN_     | _MODE     |           |           |           | INT          | LEAR<br>N   |

| 0x61     | DIR_CTRL             |           |           |           |           |           |           |              | STAR<br>T   |

| 0x62     | DIR_CH_1_H           |           |           |           |           |           |           |              |             |

| 0x63     | DIR_CH_1_L           |           |           |           |           |           |           |              |             |

| 0x64     | DIR_CH_2_H           |           |           |           |           |           |           |              |             |

| 0x65     | DIR_CH_2_L           |           |           |           |           |           |           |              |             |

| 0x66     | DIR_CH_3_H           |           |           |           |           |           |           |              |             |

| 0x67     | DIR_CH_3_L           |           |           |           |           |           |           |              |             |

| 0x70     | DIR_LUXT_H           |           |           |           |           |           |           |              |             |

| 0x71     | DIR_LUXT_L           |           |           |           |           |           |           |              |             |

| 0x72     | DIR_CCTT_H           |           |           |           |           |           |           |              |             |

|          |                      |           |           |           |           |           |           |              |             |

| Adress        | Name                 | <d7></d7> | <d6></d6> | <d5></d5> | <d4></d4> | <d3></d3> | <d2></d2> | <d1></d1> | <d0></d0> |

|---------------|----------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Raw Valu      | ue Registers         |           |           |           |           |           |           |           |           |

| 0x08          | RAW_VALUE_0_<br>H    |           |           |           |           |           |           |           |           |

| 0x09          | RAW_VALUE_0_<br>L    |           |           |           |           |           |           |           |           |

| 0x0A          | RAW_VALUE_1_<br>H    |           |           |           |           |           |           |           |           |

| 0x0B          | RAW_VALUE_1_<br>L    |           |           |           |           |           |           |           |           |

| 0x0C          | RAW_VALUE_2_<br>H    |           |           |           |           |           |           |           |           |

| 0x0D          | RAW_VALUE_2_<br>L    |           |           |           |           |           |           |           |           |

| 0x0E          | RAW_VALUE_3_<br>H    |           |           |           |           |           |           |           |           |

| 0x0F          | RAW_VALUE_3_<br>L    |           |           |           |           |           |           |           |           |

| 0x10          | RAW_VALUE_4_<br>H    |           |           |           |           |           |           |           |           |

| 0x11          | RAW_VALUE_4_<br>L    |           |           |           |           |           |           |           |           |

| 0x12          | RAW_VALUE_5_<br>H    |           |           |           |           |           |           |           |           |

| 0x13          | RAW_VALUE_5_<br>L    |           |           |           |           |           |           |           |           |

| Calibration   | on Coefficient Regis | sters     |           |           |           |           |           |           |           |

| 0x50          | COEF_DATA_0          |           |           |           |           |           |           |           |           |

| 0x51          | COEF_DATA_1          |           |           |           |           |           |           |           |           |

| 0x52          | COEF_DATA_2          |           |           |           |           |           |           |           |           |

| 0x53          | COEF_DATA_3          |           |           |           |           |           |           |           |           |

| 0x54          | COEF_READ            |           |           |           |           |           |           |           |           |

| 0x55          | COEF_WRITE           |           |           |           |           |           |           |           |           |

| Calibrate     | ed Sensor Result Re  | gister    |           |           |           |           |           |           |           |

| 0x14:<br>0x17 | Cal_X                |           |           |           |           |           |           |           |           |

| 0x18:<br>0x1B | Cal_Y                |           |           |           |           |           |           |           |           |

| 0x1C:<br>0x1F | Cal_Z                |           |           |           |           |           |           |           |           |

| 0x20:<br>0x23 | Cal_x_1931           |           |           |           |           |           |           |           |           |

| Adress        | Name                | <d7></d7> | <d6></d6> | <d5></d5>                    | <d4></d4> | <d3></d3>  | <d2></d2> | <d1></d1> | <d0></d0>  |

|---------------|---------------------|-----------|-----------|------------------------------|-----------|------------|-----------|-----------|------------|

| 0x24:<br>0x27 | Cal_y_1931          |           |           |                              |           |            |           |           |            |

| 0x28:<br>0x2B | Cal_u_pri           |           |           |                              |           |            |           |           |            |

| 0x2C:<br>0x2F | Cal_v_pri           |           |           |                              |           |            |           |           |            |

| 0x30:<br>0x33 | Cal_u               |           |           |                              |           |            |           |           |            |

| 0x34:<br>0x37 | Cal_v               |           |           |                              |           |            |           |           |            |

| 0x38:<br>0x3B | DUV                 |           |           |                              |           |            |           |           |            |

| 0x3C          | LUX_H               |           |           |                              |           |            |           |           |            |

| 0x3D          | LUX_L               |           |           |                              |           |            |           |           |            |

| 0x3E          | CCT_H               |           |           |                              |           |            |           |           |            |

| 0x3F          | CCT_L               |           |           |                              |           |            |           |           |            |

| Firmware      | Update Registers    |           |           |                              |           |            |           |           |            |

| 0x48          | FW_CNTRL            | STAR<br>T | STOP      | BYTE<br>S_TR<br>ANSF<br>ERED | LOCK      | SWIT<br>CH | BANK<br>1 | ERR<br>OR | CHKS<br>UM |

| 0x49          | FW_BYTE_COU<br>NT_H |           |           |                              |           |            |           |           |            |

| 0x4A          | FW_BYTE_COU<br>NT_L |           |           |                              |           |            |           |           |            |

| 0x4B          | FW_PAYLOAD          |           |           |                              |           |            |           |           |            |

# 10.2 Detailed Register Description

#### 10.2.1 Hardware Version Registers (Address 0x00/0x01)

These byte registers are used together as HW\_V\_H: HW\_V\_L

Figure 25:

**Hardware Version Register High**

| Addr: 0x00 |             | HW_VERSION_ | Н      |                    |

|------------|-------------|-------------|--------|--------------------|

| Bit        | Bit Name    | Default     | Access | Bit Description    |

| 7:0        | Device Type | 0x40        | R      | Device type number |

Figure 26:

**Hardware Version Register Low**

| Addr: 0x01 |            | HW_VERSION_ | L      |                         |

|------------|------------|-------------|--------|-------------------------|

| Bit        | Bit Name   | Default     | Access | Bit Description         |

| 7:0        | HW Version | 0x19        | R      | Hardware version number |

#### 10.2.2 Firmware Version Registers (Address 0x02/0x03)

These byte registers are used together as  $FW_V_H$ :  $FW_V_L$ . Set register 0x02 or 0x03 to 1-3 to get each firmware positions. Other write values set registers 0x02/0x03 to zero.

Figure 27:

Firmware Version Register High

| Addr: 0x02 (R/W) |                   | FW_VERSIC | FW_VERSION_H |                                                                                                   |  |  |

|------------------|-------------------|-----------|--------------|---------------------------------------------------------------------------------------------------|--|--|

| Bit              | Bit Name          | Default   | Access       | Bit Description                                                                                   |  |  |

| 15:8             | MAJOR Version     | 0         | R            | Major version high byte                                                                           |  |  |

| 15:8             | PATCH Version     | 0         | R            | Patch version high byte                                                                           |  |  |

| 15:8             | BUILD Version     | 0         | R            | Build version high byte                                                                           |  |  |

| 7:0              | Firmware Position | 0         | W            | FW position setting 1= Read out Major version 2= Read out Patch version 3= Read out Build version |  |  |

Figure 28: Firmware Version Register Low

| Addr: 0x03 (R/W) |                   | FW_VERSIC | FW_VERSION_L |                                                                                                   |  |  |

|------------------|-------------------|-----------|--------------|---------------------------------------------------------------------------------------------------|--|--|

| Bit              | Bit Name          | Default   | Access       | Bit Description                                                                                   |  |  |

| 7:0              | MAJOR Version     | 0         | R            | Major version low byte                                                                            |  |  |

| 7:0              | PATCH Version     | 0         | R            | Patch version low byte                                                                            |  |  |

| 7:0              | BUILD Version     | 0         | R            | Build version low byte                                                                            |  |  |

| 7:0              | Firmware Position | 0         | W            | FW position setting 1= Read out Major version 2= Read out Patch version 3= Read out Build version |  |  |

### 10.2.3 Configuration Register (Address 0x04)

Figure 29: Configuration Register

| Addr: 0x04 (R/W) |          | CONFIGURATION |        |                                                                                                             |

|------------------|----------|---------------|--------|-------------------------------------------------------------------------------------------------------------|

| Bit              | Bit Name | Default       | Access | Bit Description                                                                                             |

| 7                | SRST     | 0             | R/W    | R = Gain error<br>W= Software reset                                                                         |

| 6                | RSVD     | 0             | -      | Reserved, do not use                                                                                        |

| 5:4              | GAIN     | 00            | R/W    | Gain Setting<br>00= 1x Gain; 01= 3.7x;<br>10= 16x; 11= 64x                                                  |

| 3:2              | RSVD     | 00            | -      | Reserved, do not use                                                                                        |

| 1                | DATA_RDY | 0             | R      | 1= Conversion Data Ready<br>to read<br>Cleared (=0) after read if set<br>Cleared (=0) after device<br>reset |

| 0                | FRST     | 0             | W      | Soft reset set to 1 for soft reset. Goes to 0 when complete                                                 |

#### 10.2.4 Integration Time Register (Address 0x05)

Figure 30:

**INTEGRATION\_TIME** Register

| Addr: 0x05 (R/W) |                  | INTEGRATION_TIME |        |                                                                               |

|------------------|------------------|------------------|--------|-------------------------------------------------------------------------------|

| Bit              | Bit Name         | Default          | Access | Bit Description                                                               |

| 7:0              | INTEGRATION_TIME | 20               | R/W    | Sensor integration time =<br><value>*2.8 ms (valid value range 1-255)</value> |

#### 10.2.5 Device Temperature Register (Address 0x06)

Figure 31:

**Temperature Register**

| Addr: 0x06 |             | TEMPERATURE |        |                                                                          |

|------------|-------------|-------------|--------|--------------------------------------------------------------------------|

| Bit        | Bit Name    | Default     | Access | Bit Description                                                          |

| 7:0        | TEMPERATURE | -           | R      | Device internal temperature (1byte). Byte is a hex integer value, in °C. |

#### 10.2.6 LED Configuration Register (Address 0x07)

Figure 32:

**LED\_CONFIG Register**

| Addr: 0x07 (R/W) |            | LED_CONFIG | LED_CONFIG |                        |  |

|------------------|------------|------------|------------|------------------------|--|

| Bit              | Bit Name   | Default    | Access     | Bit Description        |  |

| 7:1              | RSVD       | -          | -          | Reserved               |  |

| 0                | LED_CONFIG | 0x01       | R/W        | Enable/disable LED_IND |  |

#### 10.2.7 External Device Status Register (Address 0x4F)

Figure 33: ESP Register

| Addr: | 0x4F     | ESP     |        |                                                              |

|-------|----------|---------|--------|--------------------------------------------------------------|

| Bit   | Bit Name | Default | Access | Bit Description                                              |

| 7     | RSVD     | -       | -      | Reserved                                                     |

| 6     | ESP      | -       | R      | 1= An external ALS is<br>available (TSL25721 or<br>TSL45315) |

| 5:0   | RSVD     | -       | -      | Reserved                                                     |

### 10.2.8 Director Configuration Register (Address 0x60)

Figure 34: DIR\_CONF Register

| Addr: | 0x60 (R/W) | DIR_CONF |        |                                                                                                                                                           |

|-------|------------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Bit Name   | Default  | Access | Bit Description                                                                                                                                           |

| 7:4   | CHAN_MODE  | -        | R/W    | Select channel mode  0= Daylighting (CH1)  1= Daylighting (CH1) + Color Tuning (CH2/3)  2= Daylighting + Color Tuning (CH2/3)  3-15= Reserved, do not use |

| 1     | INT        | -        | R/W    | 1= Enable interrupt pin<br>0= Disable                                                                                                                     |

| 0     | LEARN      | -        | R/W    | 1= Activate learn mode Cleared by AS7225 automatically after being set and device reset.                                                                  |

#### 10.2.9 Director Control Register (Address 0x61)

Figure 35: DIR\_CTRL Register

| Addr: 0 | x61      | DIR_CTRL |        |                                                                                                                   |

|---------|----------|----------|--------|-------------------------------------------------------------------------------------------------------------------|

| Bit     | Bit Name | Default  | Access | Bit Description                                                                                                   |

|         |          |          |        | 1 = Host MCU has<br>completed last directive and<br>is ready for new AS7225<br>conversion start.                  |

| 0       | START    | 0        | R/W    | Cleared by AS7225<br>automatically when PWM<br>target values are ready for<br>the MCU or after a device<br>reset. |

#### 10.2.10 Director Channel\_1 Result Registers (Addresses 0x62, 0x63)

These byte registers are used together as DIR\_CH\_1\_H: DIR\_CH\_1\_L.

In Color Tuning operation, the registers create a 16-bit integer value from 0 to 65535 representing a PWM (Color + Dimming) tuning percentage between 0.00 and 100.00%.

Example: 0001101001001111 = 1A4F = 6735 = 10.28%

In Daylighting operation, the registers create a 16-bit integer value from 0 to 65535 representing a PWM Lux tuning percentage between 0.00 and 100.00%.

Figure 36:

Director Channel\_1 Result Register High

| Addr: 0x62 D |            | DIR_CH_1_H | DIR_CH_1_H |                                                                                                                             |  |

|--------------|------------|------------|------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Bit          | Bit Name   | Default    | Access     | Bit Description                                                                                                             |  |

| 15:8         | DIR_CH_1_H | 00000000   | R          | Channel 1 high byte  CHAN_MODE 0 = Dimming  CHAN_MODE 1 = Dimming  CHAN_MODE 2 = Overall  brightness (only for information) |  |

Figure 37:

Director Channel\_1 Result Register Low

| Addr: 0 | )x63       | DIR_CH_1_L |        |                    |

|---------|------------|------------|--------|--------------------|

| Bit     | Bit Name   | Default    | Access | Bit Description    |

| 7:0     | DIR_CH_1_L | 00000000   | R      | Channel 1 low byte |

#### 10.2.11 Director Channel\_2 Result Registers (Addresses 0x64, 0x65)

These byte registers are used together as DIR\_CH\_2\_H: DIR\_CH\_2\_L

The registers create a 16-bit integer value from 0 to 65535 representing a PWM (Color + Dimming) tuning percentage between 0.00 and 100.00%.

Example: 0001101001001111 = 1A4F = 6735 = 10.28%

Figure 38:

Director Channel\_2 Result Register High

| Addr: 0x64 |            | DIR_CH_2_H |        |                                                                                                                                           |

|------------|------------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Bit        | Bit Name   | Default    | Access | Bit Description                                                                                                                           |

| 15:8       | DIR_CH_2_H | 00000000   | R      | Channel 2 high byte  CHAN_MODE 0 = Disabled (0)  CHAN_MODE 1 = String1  COLOR_TUNING  CHAN_MODE 2 = String 2  COLOR_TUNING incl.  dimming |

Figure 39:

Director Channel\_2 Result Register Low

| Addr: | 0x65       | DIR_CH_2_L |        |                    |

|-------|------------|------------|--------|--------------------|

| Bit   | Bit Name   | Default    | Access | Bit Description    |

| 7:0   | DIR_CH_2_L | 00000000   | R      | Channel 2 low byte |

#### 10.2.12 Director Channel\_3 Result Registers (Addresses 0x66, 0x67)

These byte registers are used together as DIR\_CH\_3\_H: DIR\_CH\_3\_L

The registers create a 16-bit integer value from 0 to 65535 representing a PWM (Color + Dimming) tuning percentage between 0.00 and 100.00%.

Example: 0001101001001111 = 1A4F = 6735 = 10.28%

Figure 40:

**Director Channel\_3 Result Register High**

| Addr: 0x66 |            | DIR_CH_3_H | DIR_CH_3_H |                                                                                                                                                   |  |

|------------|------------|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name   | Default    | Access     | Bit Description                                                                                                                                   |  |

| 15:8       | DIR_CH_3_H | 00000000   | R          | Channel 3 high byte  CHAN_MODE 0 = Disabled (0)  CHAN_MODE 1 = String1 complement COLOR_TUNING  CHAN_MODE 2 = String 2 COLOR_TUNING incl. dimming |  |

Figure 41:

Director Channel\_3 Result Register Low

| Addr: 0 | )x67       | DIR_CH_3_L |        |                    |

|---------|------------|------------|--------|--------------------|

| Bit     | Bit Name   | Default    | Access | Bit Description    |

| 7:0     | DIR_CH_3_L | 00000000   | R      | Channel 3 low byte |

#### 10.2.13 Director Target for LUX Registers (Addresses 0x70, 0x71)

These byte registers are used together as DIR\_LUXT\_H: DIR\_LUXT\_L.

They create a 16-bit integer value for LUX target.

Example: 0000001111101000 = 1000 LUX

Figure 42:

**Director Target for LUX Register High**

| Addr: ( | 0x70 (R/W) | DIR_LUXT_H |        |                                   |

|---------|------------|------------|--------|-----------------------------------|

| Bit     | Bit Name   | Default    | Access | Bit Description                   |

| 15:8    | DIR_LUXT_H | 00000000   | R/W    | Director target for LUX high byte |

Figure 43:

**Director Target for LUX Register Low**

| Addr: ( | 0x71 (R/W) | DIR_LUXT_L |        |                                  |

|---------|------------|------------|--------|----------------------------------|

| Bit     | Bit Name   | Default    | Access | Bit Description                  |

| 7:0     | DIR_LUXT_L | 00000000   | R/W    | Director target for LUX low byte |

#### 10.2.14 Director Target for CCT Registers (Addresses 0x72, 0x73)

These byte registers are used together as DIR\_CCTT\_H: DIR\_CCTT\_L.

They create a 16-bit integer value for CCT target (Kelvin).

Example: 0000101110111000 = 3000 K

Figure 44:

**Director Target for CCT Register High**

| Addr: ( | 0x72 (R/W) | DIR_CCTT_H |        |                                   |

|---------|------------|------------|--------|-----------------------------------|

| Bit     | Bit Name   | Default    | Access | Bit Description                   |

| 15:8    | DIR_CCTT_H | 00000000   | R/W    | Director target for CCT high byte |

Figure 45:

**Director Target for CCT Register Low**

| Addr: | 0x73 (R/W) | DIR_CCTT_L |        |                                  |

|-------|------------|------------|--------|----------------------------------|