# MP3309C

2.7V-5.5V Input, 38V Output, F<sub>sw</sub> Programmable, White LED Driver with I<sup>2</sup>C Interface

# DESCRIPTION

The MP3309C is a WLED step-up converter for 2.7V to 5.5V input that uses peak current mode to regulate the LED current sensed through an external low-side resistor. The 200mV feedback voltage and synchronous rectification reduces power loss and reduces PCB space requirements. For non-synchronous mode, setting an internal register can disable the rectifier MOSFET to save driver losses.

The MP3309C features a programmable switching frequency to optimize efficiency. It supports both analog and PWM dimming.

In addition, the MP3309C has LED open protection, cycle-by-cycle current limit protection, thermal shutdown protection, and  $V_{OUT}$  to GND short-circuit protection. The I<sup>2</sup>C interface can set the protection indication bits and over-voltage protection point.

# FEATURES

- 2.7V to 5.5V Input Voltage

- Analog and PWM Dimming

- Selectable Synchronous or Nonsynchronous Mode

- 400kHz I<sup>2</sup>C-Compatible Interface

- Digitally Set LED Current

- Programmable Switching Frequency

- Programmable Open Load Protection Point

- Low 200mV Feedback Voltage with ±1% Accuracy at Room Temperature

- Software Enable Function

- UVLO, Thermal Shutdown

- Available in a 1.4mmx1.8mm QFN10 Package

# APPLICATIONS

- Feature Phones and Smart Phones

- Tablets

- <10in Video Displays</li>

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

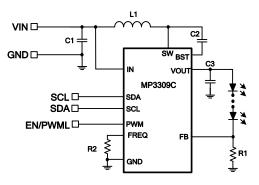

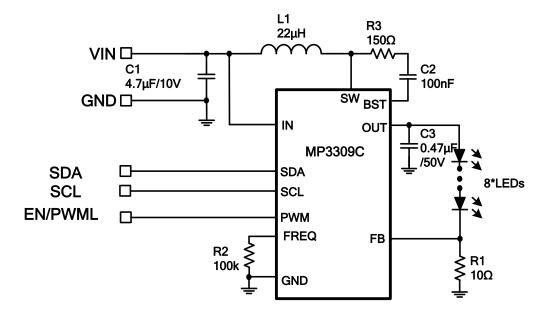

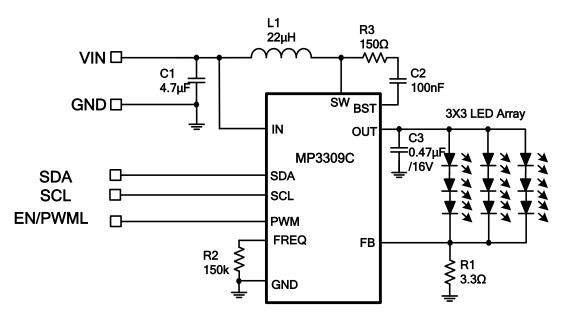

# TYPICAL APPLICATION

**Typical Application Circuit**

### **ORDERING INFORMATION**

| Part Number | Package              | Top Marking |

|-------------|----------------------|-------------|

| MP3309CGQG  | QFN-10 (1.4mmx1.8mm) | See Below   |

For Tape & Reel, add suffix -Z (e.g. MP3309CGQG-Z);

# **TOP MARKING**

CJ LL

CJ: Product code of MP3309CGQG LL: Lot number

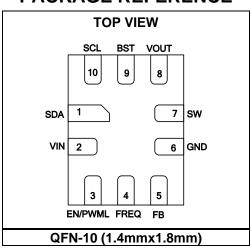

#### PACKAGE REFERENCE

# **PIN FUNCTIONS**

| Pin # | Name    | Description                                                                                                                                                                                                                                                                                                                            |

|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SDA     | I <sup>2</sup> C clock data input.                                                                                                                                                                                                                                                                                                     |

| 2     | VIN     | <b>Input supply.</b> Provides power for the internal power and logic circuits. Must be locally bypassed.                                                                                                                                                                                                                               |

| 3     | EN/PWML | <b>PWM brightness control/enable.</b> Apply a PWM signal for PWM dimming. The PWM frequency is proportional to the LED current dimming ratio—a lower dimming frequency results in a smaller dimming current. For most applications, use a frequency range of 200Hz to 2kHz. A low-level signal longer than 20ms will shut down the IC. |

| 4     | FREQ    | <b>Switching frequency set.</b> Connect a resistor between FREQ and GND to program the converter switching frequency. Do not leave this pin floating.                                                                                                                                                                                  |

| 5     | FB      | <b>LED current feedback.</b> Regulates the voltage across the current sense resistor between FB and GND to 200mV.                                                                                                                                                                                                                      |

| 6     | GND     | Ground.                                                                                                                                                                                                                                                                                                                                |

| 7     | SW      | <b>Power switch node.</b> Drain of the internal low-side MOSFET. Connect the power inductor between SW and VIN. For non-synchronous mode, connect a Schottky diode between SW and VOUT.                                                                                                                                                |

| 8     | VOUT    | <b>Output voltage.</b> Internally connected to the source of the synchronous MOSFET. For non-synchronous mode, connect a Schottky diode between SW and VOUT.                                                                                                                                                                           |

| 9     | BST     | <b>Booststrap.</b> Connect a capacitor between SW and BST to provide the synchronous MOSFET gate driver.                                                                                                                                                                                                                               |

| 10    | SCL     | I <sup>2</sup> C interface clock signal.                                                                                                                                                                                                                                                                                               |

# ABSOLUTE MAXIMUM RATINGS (1)

| V <sub>IN</sub>                     | 0.3V to +6V                  |

|-------------------------------------|------------------------------|

| V <sub>SW</sub> , V <sub>OUT</sub>  | 1V to +40V                   |

| V <sub>BST</sub>                    | -0.3V to V <sub>SW</sub> +6V |

| All Other Pins                      | –0.3V to +6V                 |

| Junction Temperature                | 150°C                        |

| Lead Temperature                    | 260°C                        |

| <b>Continuous Power Dissipation</b> | $(T_A = 25^{\circ}C)^{(2)}$  |

| QFN-10 (1.4mmx1.8mm)                | 0.892W                       |

#### **Recommended Operating Conditions** <sup>(3)</sup> Supply Voltage ( $V_{IN}$ ).....2.7V to 5.5V Operating Junction Temp. ( $T_J$ ). -40°C to +125°C

# *Thermal Resistance* <sup>(4)</sup> *θ*<sub>JA</sub> *θ*<sub>JC</sub> QFN-10 (1.4mmx1.8mm)...... 140...... 30 °C/W

Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  =3.6V,  $V_{EN}$  =  $V_{IN}$ ,  $T_A$  = 25°C, unless otherwise noted.

| Parameters                  | Symbol              | Condition                                                                     | Min      | Тур      | Max  | Units    |

|-----------------------------|---------------------|-------------------------------------------------------------------------------|----------|----------|------|----------|

| STEP-UP CONVERTER           |                     |                                                                               |          |          |      |          |

| Operating input voltage     | VIN                 |                                                                               | 2.7      |          | 5.5  | V        |

| Supply current (quiescent)  | lα                  | $V_{IN}$ =3.6V, $V_{EN}$ = $V_{IN}$ , no load with switching                  |          | 420      |      | μA       |

| Supply current (shutdown)   | I <sub>ST</sub>     | V <sub>EN</sub> =0V, V <sub>IN</sub> =3.6V<br>EN Bit=0, V <sub>IN</sub> =3.6V |          | 68       | 1    | μΑ<br>μΑ |

| Input UVLO threshold        | Vin_uvlo            | Rising Edge                                                                   |          | 2.5      |      | V        |

| Input UVLO hysteresis       |                     |                                                                               |          | 200      |      | mV       |

| EN high voltage             | Ven_high            | VEN Rising                                                                    | 1.2      |          |      | V        |

| EN low voltage              | V <sub>EN_LOW</sub> | V <sub>EN</sub> Falling                                                       |          |          | 0.4  | V        |

| Switching frequency         | f <sub>SW</sub>     | R <sub>osc</sub> = 200kΩ                                                      | 540      | 640      | 740  | kHz      |

| Maximum duty cycle          | Dмах                | Sync Mode, 600kHz<br>Non-sync Mode, 600kHz                                    | 89<br>90 | 93<br>95 |      | %        |

| Feedback regulation voltage | V <sub>REF</sub>    |                                                                               | 198      | 200      | 202  | mV       |

| VREF ramp-up time           | t <sub>STEP</sub>   |                                                                               |          | 320      |      | μs       |

| POWER SWITCH                | ·                   |                                                                               |          | •        |      | •        |

| Main switch on resistance   | Rdson_m             | VIN=3.6V                                                                      |          | 0.3      | 0.5  | Ω        |

| Sync switch on resistance   | Rdson_s             | VIN=3.6V                                                                      |          | 0.5      | 0.8  | Ω        |

| CURRENT DIMMING             |                     |                                                                               |          | •        | •    |          |

| PWML input low threshold    | Vpwm_lo             | V <sub>PWM</sub> Falling                                                      |          |          | 0.4  | V        |

| PWML input high threshold   | V <sub>PWM_HI</sub> | V <sub>PWM</sub> Rising                                                       | 1.2      |          |      | V        |

| PWML shutdown time          | tsp                 | EN/PWML High to Low                                                           |          | 20       |      | ms       |

| PROTECTION                  |                     |                                                                               |          |          |      |          |

|                             |                     | OVP0=0, OVP1=1<br>(Default)                                                   | 33.5     | 35.5     | 37.5 | V        |

| OVP voltage                 | Vovp                | Hysteresis                                                                    |          | 2.5      |      |          |

| CVI voltage                 | V OVP               | OVP0=1,OVP1=0                                                                 | 22.5     | 24       | 25.5 | V        |

|                             |                     |                                                                               | 40.5     | 2        | 445  |          |

|                             |                     | OVP0=0,OVP1=0                                                                 | 12.5     | 13.5     | 14.5 | V        |

| Cycle-cycle current limit   | ILIM                | Hysteresis<br>OVP0=1,OVP1=0                                                   |          | 1.5      |      | A        |

# ELECTRICAL CHARACTERISTICS (continued)

### $V_{IN} = 3.6V$ , $V_{EN} = V_{IN}$ , $T_A = 25^{\circ}$ C, unless otherwise noted.

| Parameters                                         | Symbol              | Condition | Min                       | Тур  | Max | Units |

|----------------------------------------------------|---------------------|-----------|---------------------------|------|-----|-------|

| OVP UVLO threshold                                 | Vovp_uv             |           |                           | 1.24 |     | V     |

| Thermal shutdown threshold                         | t <sub>S⊺</sub>     |           |                           | 150  |     | °C    |

| Thermal shutdown hysteresis                        |                     |           |                           | 25   |     | °C    |

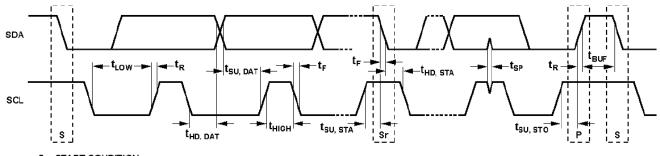

| I <sup>2</sup> C Interface Specifications          |                     |           | -                         |      |     |       |

| Input logic low                                    | VIL                 |           | 0                         |      | 0.4 | V     |

| Input logic high                                   | VIH                 |           | 1.3V                      |      |     | V     |

| Output logic low                                   | Vol                 | ILOAD=3mA |                           |      | 0.4 | V     |

| SCL clock frequency                                | fscl                |           |                           |      | 400 | kHz   |

| SCL high time                                      | tнigн               |           | 0.6                       |      |     | μs    |

| SCL low time                                       | t <sub>LOW</sub>    |           | 1.3                       |      |     | μs    |

| Data setup time                                    | <b>t</b> su,dat     |           | 100                       |      |     | ns    |

| Data hold time                                     | <b>t</b> hd,dat     |           | 0                         |      | 0.9 | μs    |

| Setup time for repeated start                      | t <sub>su,sta</sub> |           | 0.6                       |      |     | μs    |

| Hold time for start                                | <b>t</b> hd,sta     |           | 0.6                       |      |     | μs    |

| Bus free time between a start and a stop condition | t <sub>BUF</sub>    |           | 1.3                       |      |     | μs    |

| Setup time for stop condition                      | tsu,sto             |           | 0.6                       |      |     | μs    |

| Rise time of SCL and SDA                           | t <sub>R</sub>      |           | 20+0.1<br>×С <sub>в</sub> |      | 120 | ns    |

| Fall time of SCL and SDA                           | t⊧                  |           | 20+0.1<br>×Св             |      | 120 | ns    |

| Pulse width of suppressed spike                    | tsp                 |           | 0                         |      | 50  | ns    |

| Capacitance bus for each bus line                  | Св                  |           |                           |      | 400 | рF    |

S = START CONDITION Sr = REPEATED START CONDITION P = STOP CONDITION

I<sup>2</sup>C Compatible Interface Timing Diagram

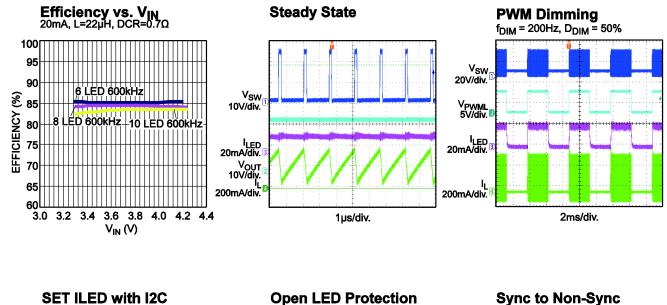

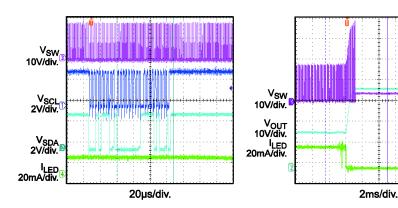

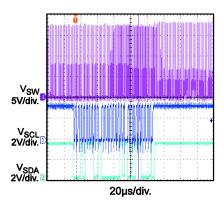

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{IN}$  = 3.6V, 8 LEDs, L = 10µH, T<sub>A</sub> = 25°C, unless otherwise noted.

### Sync to Non-Sync

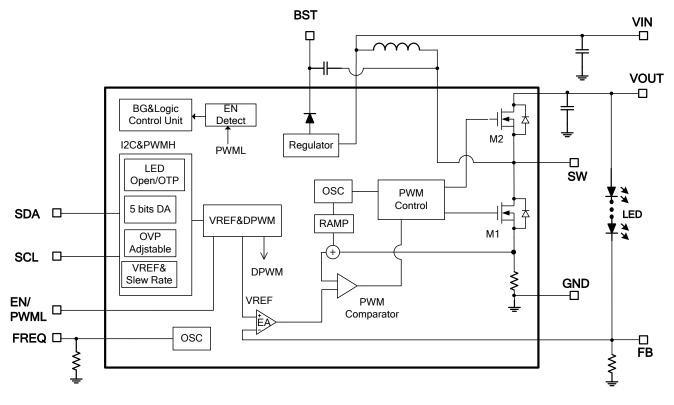

# **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

# OPERATION

The MP3309C uses peak-current-mode control to regulate the current through the WLED string. At the start of each oscillator cycle, the control circuit turns on the low-side MOSFET (LS-FET, M1). A stabilizing ramp is added to the output of the current sense amplifier, which then feeds into the positive input of the PWM comparator and prevents sub-harmonic oscillations at duty cycles greater than 50%. When the input to the PWM comparator equals the output voltage of the error amplifier. M1 turns off. Then the inductor current flows through the synchronous power MOSFET, or the external Schottky diode, which forces the inductor current to decrease.

The voltage at the output of the error amplifier is the amplified difference between the 200mV reference voltage and the feedback voltage. If the feedback voltage starts to drop, the output of the error amplifier increases, increasing the current flowing through M1, thus increasing the power to the inductor and the output power. This method accurately regulates the LED current.

#### System Start-Up

When the EN bit is set to 1 thru the I<sup>2</sup>C interface, the MP3309C initially checks the topology connection. The chip monitors the over-voltage protection (OVP) block for shorts between the boost output and GND. A low OVP voltage will disable the chip. The MP3309C also checks other safety limits, including UVLO, over-temperature protection (OTP), and overcurrent protection (after passing the OVP test). If all the protection tests pass, the chip then starts boosting the step-up converter with an internal soft start. During the soft start, the reference voltage gradually ramps up with a time step of 320µs for a total of 32 steps. In addition, the current limit drops to 0.7A during start-up to prevent a large inrush current. This low current limit time period lasts for 5ms after the IC is enabled.

# Synchronous or Non-synchronous Mode Selection

In default mode (internal register bit SYNC=1), the converter works in synchronous mode. Synchronous mode can reduce diode power consumption caused by a large voltage drop. This synchronous mode increases the converter efficiency for low LED string voltage. This mode does not need an external Schottky diode, which reduces PCB space requirements and BOM costs.

In some applications (see below), select nonsynchronous mode by setting the internal register bit to SYNC=0. Be sure to connect an external Schottky diode between SW and VOUT.

- 1. When the LED string voltage is high, the duty cycle is large, which means the synchronous power MOSFET turn-on time is very short

- 2. When the switching frequency is set too high, the synchronous power MOSFET driver loss is large.

#### Dimming Control

The MP3309C provides two dimming methods: PWM and analog dimming mode.

For PWM dimming, apply a PWM signal to the EN/PWML pin. The LED current is then segmented as per the PWM signal and the average LED current equals:

$$\mathbf{I}_{\text{set}}\!\times\!\mathbf{D}_{\text{dim}}$$

Where  $D_{dim}$  is the PWM duty cycle, and  $I_{set}$  is the LED current amplitude. When the PWM signal is high, the converter operates in normal mode. Conversely, when the PWM amplitude is low, the converter stops switching. Make sure that the PWM signal low-level time is less than 20ms or the IC will shut down. Use a 100Hz to 2kHz PWM dimming frequency for most dimming ratio requests.

For analog dimming, set the LED current amplitude through the I<sup>2</sup>C interface. The internal reference register bits (D0-D4) control the LED current regulation voltage by setting the DIMS bit to 0.

|     | FB<br>Voltage(mV) | D4    | D3 | D2 | D1     | D0    |

|-----|-------------------|-------|----|----|--------|-------|

| 0   | 0                 | 0     | 0  | 0  | 0      | 0     |

| 1   | 5                 | 0     | 0  | 0  | 0      | 1     |

| 2   | 8                 | 0     | 0  | 0  | 1      | 0     |

| 3   | 11                | 0     | 0  | 0  | 1      | 1     |

| 4   | 14                | 0     | 0  | 1  | 0      | 0     |

| 5   | 17                | 0     | 0  | 1  | 0      | 1     |

| 6   | 20                | 0     | 0  | 1  | 1      | 0     |

| 7   | 23                | 0     | 0  | 1  | 1      | 1     |

| 8   | 26                | 0     | 1  | 0  | 0      | 0     |

| 9   | 29                | 0     | 1  | 0  | 0      | 1     |

| 10  | 32                | 0     | 1  | 0  | 1      | 0     |

| 11  | 35                | 0     | 1  | 0  | 1      | 1     |

| 12  | 38                | 0     | 1  | 1  | 0      | 0     |

| 13  | 44                | 0     | 1  | 1  | 0      | 1     |

| 14  | 50                | 0     | 1  | 1  | 1      | 0     |

| 15  | 56                | 0     | 1  | 1  | 1      | 1     |

| 16  | 62                | 1     | 0  | 0  | 0      | 0     |

| 17  | 68                | 1     | 0  | 0  | 0      | 1     |

| 18  | 74                | 1     | 0  | 0  | 1      | 0     |

| 19  | 80                | 1     | 0  | 0  | 1      | 1     |

| 20  | 86                | 1     | 0  | 1  | 0      | 0     |

| 21  | 92                | 1     | 0  | 1  | 0      | 1     |

| 22  | 98                | 1     | 0  | 1  | 1      | 0     |

| 23  | 104               | 1     | 0  | 1  | 1      | 1     |

| 24  | 116               | 1     | 1  | 0  | 0      | 0     |

| 25  | 128               | 1     | 1  | 0  | 0      | 1     |

| 26  | 140               | 1     | 1  | 0  | 1      | 0     |

| 27  | 152               | 1     | 1  | 0  | 1      | 1     |

| 28  | 164               | 1     | 1  | 1  | 0      | 0     |

| 29  | 176               | 1     | 1  | 1  | 0      | 1     |

| 30  | 188               | 1     | 1  | 1  | 1      | 0     |

| 31  | 200               | 1     | 1  | 1  | 1      | 1     |

| Lo. | D\//M dimming     | اممما |    |    | anal t | h tho |

Table 1: I<sup>2</sup>C Reference Voltage Table

For PWM dimming, apply a PWM signal to the EN/PWML pin directly. When the PWM signal is low, the MP3309C stops switching and resumes normal operation when the PWM signal is high.

#### IC Enable and Shutdown

The MP3309C enables the internal bandgap and normal switching if both:

- 1. The EN/PWML pin is high

- 2. The internal register EN bit is set to 1.

The MP3309C shuts down the chip if either:

1. The EN/PWML pin is low for longer than 20ms

2. The internal register EN bit is set to 0. Note: if only the EN bit set to 1, the bandgap of the IC is still active.

#### **Open-String Protection**

The MP3309C monitors the VOUT pin for openstring protection. If the LED string is open, the feedback voltage is lower than the reference voltage. The COMP then rises and charges the output capacitor until the VOUT voltage reaches the protection point ( $V_{OVP}$ ). Select  $V_{OVP}$ by setting the internal register bits : OVP0 and OVP1. Please refer to the OVP Protection section in the EC table to select the OVP point.

Selecting a lower OVP protection point permits the use of a lower voltage output capacitor to reduce costs.

The IC stops switching when  $V_{OUT}$  reaches the OVP threshold; the IC resumes operation when  $V_{OUT}$  drops below the threshold.

#### Input Under-Voltage Protection

When VIN exceeds 2.5V, the converter starts to charge the internal reference and provides power to the internal control circuitry. There is a UVLO hysteresis, approximately 200mV, as VIN falls. The IC shuts down when the input voltage drops below 2.3V.

#### **Thermal Shutdown Protection**

Thermal shutdown prevents the IC from operating at exceedingly high temperatures. When the die temperature exceeds the upper threshold ( $T_{ST}$ ), the IC shuts down and resumes normal operation when the die temperature drops below the lower threshold. Typically, the hysteresis is 25°C.

#### Fault Indicator

The MP3309C provides several fault register bits to indicate when different protection conditions occur. The host controller can read these fault indication bits. See the list of protection faults and their descriptions below:

**LEDO:** LED open protection fault bit, read only.

**OTP:** Over-temperature protection fault bit, read only.

**VOS:** VOUT short to GND bit, read only

MP3309C Rev. 1.1 7/25/2022

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2022 MPS. All Rights Reserved.

# **APPLICATION INFORMATIO**

# Selecting the Switching Frequency

The switching frequency of the step-up converter can be programmed from 300kHz to 1.2MHz. A resistor on OSC sets the internal oscillator frequency for the step-up converter. See equation (1):

$$f_{SW}(kHz) = \frac{120000}{R_{FREQ}(k\Omega)}$$

(1)

For instance, if  $R_{FREQ}=200k\Omega$ , the switching frequency is to 600kHz.

# Setting the LED Current

Set the LED current through the current-setting resistor on FB with equation (2):

$$I_{LED}(mA) = \frac{V_{REF}(V)}{R_{FB}(\Omega)} \times 1000$$

(2)

For instance, if  $V_{REF}=200mV$ , and  $R_{FB}=10\Omega$ , the LED current is 20mA. Do not leave FB floating.

## Selecting the Input Capacitor

The input capacitor reduces the surge current drawn from the input supply and the switching noise from the device. The input capacitor impedance at the switching frequency should be less than the input source impedance to prevent the high-frequency switching current from passing through to the input. Use ceramic capacitors with X5R or X7R dielectrics for their low ESR and small temperature coefficients. For most applications, use a 2.2µF to 10µF ceramic capacitor.

## Selecting the Inductor

The MP3309C requires an inductor to boost its output voltage. A larger value inductor results in less ripple current, lowering both the peak inductor current and the stress on the internal N-channel MOSFET. However, the larger inductor is larger physically, has a higher series resistance, and a lower saturation current.

Choose an inductor that does not saturate under the worst-case load conditions. Select the minimum inductor value to ensure that the boost converter works in continuous conduction mode with high efficiency and good EMI performance.

Calculate the required inductance value using

equation (3):

$$L \ge \frac{\eta \times V_{OUT} \times D \times (1-D)^2}{2 \times f_{SW} \times I_{LOAD}}$$

(3)

$$D = 1 - \frac{V_{IN}}{V_{OUT}}$$

Where  $V_{IN}$  and  $V_{OUT}$  are the input and output voltages,  $f_{SW}$  is the switching frequency,  $I_{LOAD}$  is the LED load current, and n is the efficiency.

To avoid hitting the current limit, the worst-case inductor peak current should be less than 80% of the current limit  $(I_{\text{LIM}})$ .

# **Selecting the Output Capacitor**

The output capacitor keeps the output voltage ripple small and ensures feedback loop stability. The output capacitor impedance must be low at the switching frequency. Ceramic capacitors with X7R dielectrics are recommended for their low ESR characteristics. Selection must also account for the capacitance's dependence on the voltage rating; with a DC bias voltage, the capacitor can lose as much as 50% of its capacitance at its rated voltage rating. Leave a sufficient voltage rating margin when selecting the component.

Capacitance that is too high or too low will cause loop instability. For most applications, select a capacitor in the range of  $0.1\mu$ F to  $1\mu$ F.

# Setting the Over-Voltage Protection Point

V<sub>OUT</sub> determines the OVP point for open-string protection. In some cases, an LED string failure results in a 0V feedback voltage. The part then continuously boosts the output voltage higher and higher until the output voltage reaches the programmed OVP threshold to trigger openstring protection.

Select an OVP protection point through the I<sup>2</sup>C interface—about 1.1 to 1.2 times higher than the output voltage for normal operation. An appropriate OVP voltage can also allow for lowvoltage output capacitors.

| Mode                   | OVP Point |

|------------------------|-----------|

| OVP0=0,OVP1=1(Default) | 35.5V     |

| OVP0=1,OVP1=0          | 24V       |

| OVP0=0,OVP1=0          | 13.5V     |

### Dimming Mode

The MP3309C has a smart dimming function for both analog and PWM dimming.

1. PWM Dimming

For PWM dimming, apply a PWM signal to the EN/PWML pin. The LED current is then segmented as per the PWM signal and the average LED current equals:

$$I_{set} \times D_{dim}$$

Where  $D_{dim}$  is the PWM duty cycle, and  $I_{set}$  is the LED current amplitude. When the PWM signal is high, the converter operates normally. Conversely, when the PWM amplitude is low, the converter stops switching. Make sure that the PWM signal low-level time is less than 20ms, or the IC will shut down. Use a 100Hz to 2kHz PWM dimming frequency for most dimming ratio requests.

2. Analog Dimming

For analog dimming, set the LED current amplitude through the I<sup>2</sup>C. The internal reference register bits (D0-D4) control the LED current regulation voltage by setting the DIMS bit to 0.

## Selecting the External Schottky Diode

Non-synchronous mode (internal register bit SYNC=0) requires an external free-wheeling diode between SW and VOUT. To optimize efficiency, use a high-speed and low reverse recovery current Schottky diode. Make sure the diode's average and peak current rating exceeds the output average LED current and the peak inductor current. In addition, the diode's breakdown voltage rating should exceed the maximum voltage across the diode. Usually, unexpected high-frequency voltage spikes on the diode occur when the diode turns off. Therefore, leave a voltage rating margin to guarantee normal long-term operation.

# LED Current Ramp Slew Rate

To prevent a large inrush current and provide a smooth start-up, the MP3309C has a reference rising/falling slew rate. The time is 320µs per step for a total of 32 steps from 0 to 200mV.

# I<sup>2</sup>C Register

I<sup>2</sup>C Chip Address:

The device address for the MP3309C is 0x17. After the START condition, the I<sup>2</sup>C compatible master sends a seven-bit address followed by an eighth read (Read: 1) or write (Write: 0) bit. The following byte indicates the register address to/from which the data will be written/read.

| 0 0 1 | 0 | 1 | 1 | 1 | R/W |

|-------|---|---|---|---|-----|

|-------|---|---|---|---|-----|

## The I<sup>2</sup>C Compatible Device Address

Register Descriptions:

| Part Number | Register<br>Address | Default/Reset<br>Value |

|-------------|---------------------|------------------------|

| MD00000     | 0X00                | 011111XX               |

| MP3309C     | 0X01                | X0101000               |

0x00 Register Descriptions:

| EN D0 D1 D2 | D3 | D4 X | X |

|-------------|----|------|---|

|-------------|----|------|---|

**EN:** IC enable bit. Default=0 for MP3309C.

**D0:D4:** Reference set bits. Default=11111.

## X: Reserved Bits.

0x01 Register Descriptions:

X DIMSSYNCOVPOOVP1 VOS LEDO OTP

## X: Reserved Bits.

**DIMS:** Dimming Mode Select. Use the I<sup>2</sup>C to write to D0 through D4 directly if setting this pin to 0. Default=0 for MP3309C.

**SYNC:** Synchronous Mode Select. 1: Synchronous, 0: Non-synchronous.

**OVP0:OVP1:** OVP Protection Point Set. Default=01.

**VOS:** VOUT short to GND Fault. Read only. Default=0.

**LEDO:** LED Open-Protection Fault. Read only. Default=0.

**OTP:** Over-Temperature Protection Fault. Read only. Default=0

#### Layout Considerations

Efficient PCB board layout is critical for stable operation.

Proper layout of the high frequency switching path is critical to prevent noise and limit electromagnetic interference. The loop consisting of the MP3309C's internal low-side MOSFET, synchronous MOSFET or diode, and output capacitor contains a high-frequency ripple current—minimize this loop. Place the input and output capacitor as close to the IC as possible.

# TYPICAL APPLICATION CIRCUITS

Figure 2: Typical Application for Single String 8LEDs

Figure 3: Typical Application for 3X3 LED Array

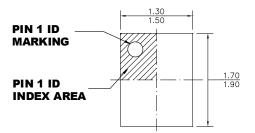

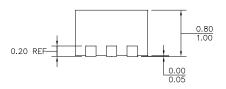

# PACKAGE INFORMATION

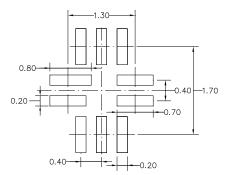

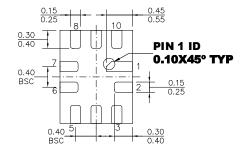

QFN-10 (1.4mmx1.8mm)

TOP VIEW

SIDE VIEW

**RECOMMENDED LAND PATTERN**

**BOTTOM VIEW**

#### NOTE:

ALL DIMENSIONS ARE IN MILLIMETERS.

LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX.

JEDEC REFERENCE IS MO-220.

DRAWING IS NOT TO SCALE.