# High-Brightness, High-Current Accuracy WLED Controller

#### DESCRIPTION

The MP4013B is a current mode controller designed for driving the high brightness Light Emitting Diodes (LEDs) with wide supply voltage 8V-26V. It can be used in both Boost and SEPIC topologies.

The MP4013B drives external MOSFET with fixed frequency architecture to regulate the LED current, which is measured through an external current feedback resistor. The switching frequency can be programmed to meet kinds of applications. The cycle-by-cycle current limit can be programmed by the sense resistor on CS pin.

The MP4013B integrates a 600mV reference voltage for LED current feedback with ±1.2% accuracy; a 5V reference voltage with ±1% accuracy for the reference voltage for external circuit.

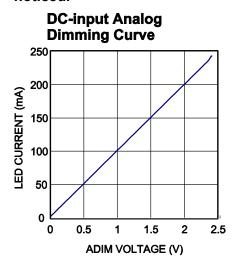

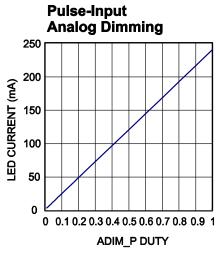

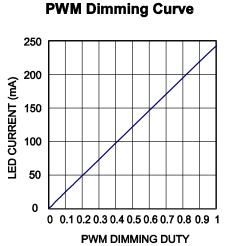

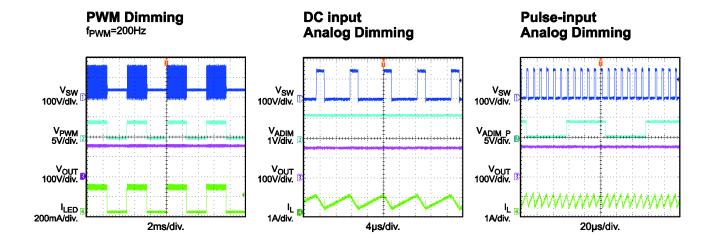

The MP4013B implements both DC input analog dimming and pulse signal input analog dimming function. The amplitude of the LED current could be controlled either by the level of a DC input signal or by the duty cycle of a pulse signal. The MP4013B also employs fast and deep PWM dimming to the LED current with high dimming ratio.

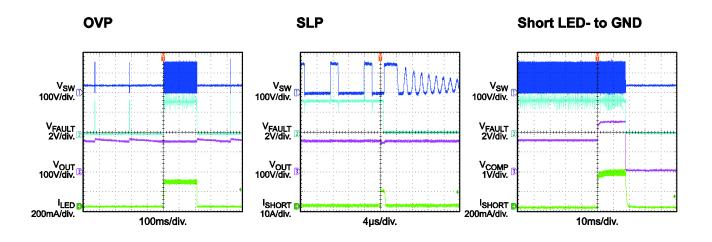

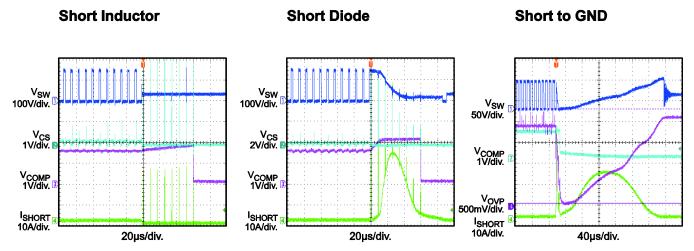

MP4013B integrates Under-Voltage Lockout, Over Voltage Protection, Over Current Protection, Short LED Protection, Short Output Protection, Short Inductor/diode Protection and OTP. The fault indicator is pulled low in fault condition.

The MP4013B is available in SOIC-16 package.

#### **FEATURES**

- Constant-current WLED Driver

- 600mV Feedback Voltage with ±1.2% Accuracy

- 8V-26V Input Voltage

- Programmable Switching Frequency

- Leading Edge Blanking for Current Sense

- High Dimming Ratio Fast PWM Dimming

- DC Input or Pulse Signal Input Analog Dimming

- 5V Reference Voltage with ±1% Accuracy

- External PWM Dimming MOS Driver

- Programmable Input Bus Voltage UVLO

- Soft Start @ Any Startup Condition

- Over Voltage Protection

- Short LED Protection

- Short Output Protection

- Over Current Protection

- Short Inductor/Diode Protection

- Fault Indicator

- VIN UVLO

- Thermal Shutdown

- Available in SOIC-16 package

#### **APPLICATIONS**

- LCD Backlighting applications

- DC/DC LED Driver applications

- General Illumination

- Industrial Lighting

- Automotive/ Decorative LED Lighting

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

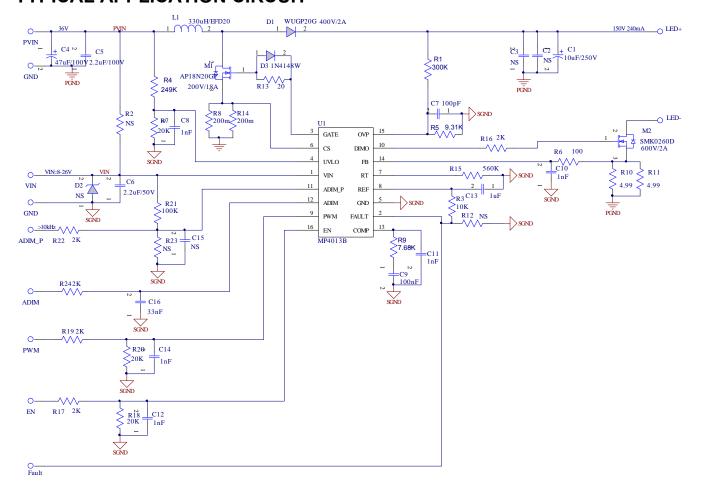

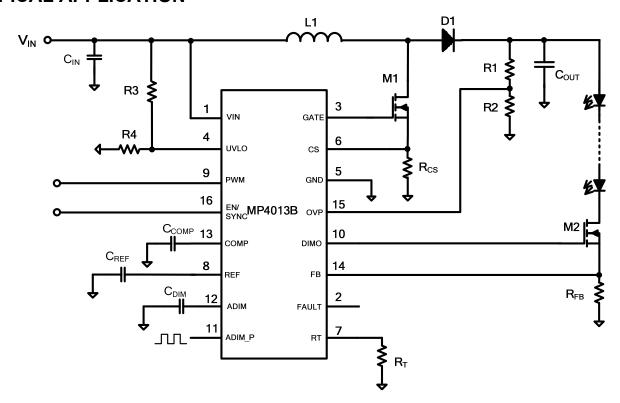

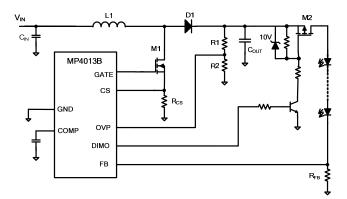

# **TYPICAL APPLICATION**

#### ORDERING INFORMATION

| Part Number* | Package | Top Marking |

|--------------|---------|-------------|

| MP4013BGS    | SOIC-16 | See Below   |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP4013BGS-Z);

#### **TOP MARKING**

MPSYYWW MP4013B LLLLLLLL

MPS: MPS prefix: YY: year code; WW: week code:

MP4013B: product code of MP4013BGS;

LLLLLLL: lot number;

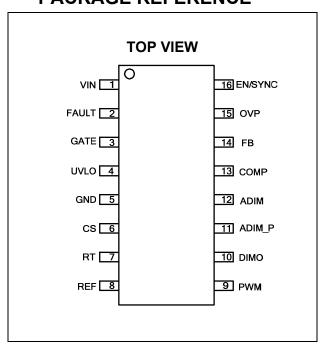

# **PACKAGE REFERENCE**

#

Operating Junction Temp. T<sub>1</sub>.....-40°C to +125°C

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|------------------------|-------------------------|-------------------------|------|

| SOIC-16                | 80                      | . 35                    | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

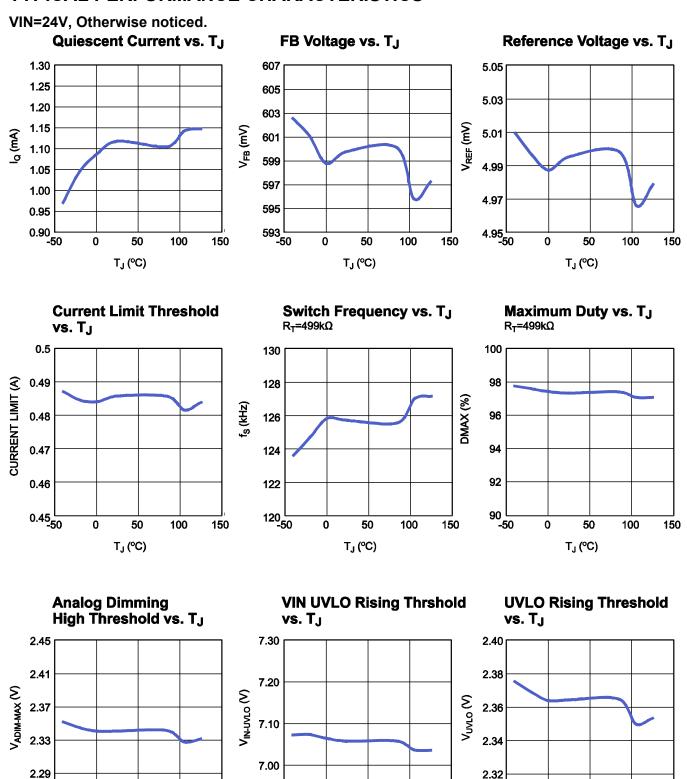

$V_{IN}$  =24V,  $T_A$  = +25°C, unless otherwise noted.

| Parameters                           | Symbol                     | Condition                                         | Min  | Тур  | Max  | Units |  |

|--------------------------------------|----------------------------|---------------------------------------------------|------|------|------|-------|--|

| Operating Input Voltage              | V <sub>IN</sub>            |                                                   | 7.6  |      | 26   | V     |  |

| Supply Current (Quiescent)           | IQ                         | V <sub>FB</sub> =1V                               |      | 1.1  | 1.3  | mA    |  |

| VIN Under Voltage Lockout            | $V_{\text{IN-UVLO}}$       | V <sub>IN</sub> Rising                            | 6.7  | 7.1  | 7.5  | V     |  |

| VIN Under Voltage Lockout Hysteresis | V <sub>IN-HYS</sub>        |                                                   | 320  | 395  | 470  | mV    |  |

| Feedback                             |                            |                                                   |      |      |      |       |  |

| FB Feedback Voltage                  | $V_{FB}$                   |                                                   | 593  | 600  | 607  | mV    |  |

| FB Input Current                     | I <sub>FB</sub>            | V <sub>FB</sub> =600mV                            | -0.1 |      | 0.1  | μΑ    |  |

| Reference                            |                            |                                                   |      |      |      |       |  |

| Reference Voltage                    | $V_{REF}$                  |                                                   | 4.95 | 5    | 5.05 | V     |  |

| Reference Line Regulation            | 0 1uE hypass canacitor I=0 |                                                   | 0    |      | 25   | mV    |  |

| Reference Load Regulation            | V <sub>REFLOAD</sub>       | 0.1µF bypass capacitor, I <sub>REF</sub> =0-500uA | 0    |      | 50   | mV    |  |

| UVLO                                 |                            |                                                   |      |      |      |       |  |

| UVLO Threshold                       | $V_{\text{UVLO}}$          | UVLO Rising                                       | 2.25 | 2.37 | 2.49 | V     |  |

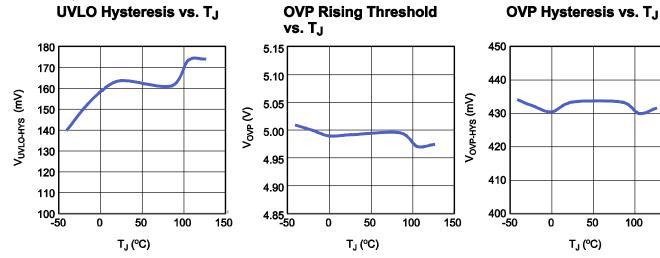

| UVLO Hysteresis                      | V <sub>UVLO-HYS</sub>      |                                                   | 110  | 160  | 210  | mV    |  |

| UVLO pin Leakage Current             | I <sub>UVLO</sub>          |                                                   | -1   |      | 1    | uA    |  |

| Oscillator                           |                            |                                                   |      |      |      |       |  |

| Oscillator Frequency                 | f <sub>OSC1</sub>          | $R_T$ =100k $\Omega$                              | 510  | 590  | 670  | kHz   |  |

| Oscillator Frequency                 | f <sub>OSC2</sub>          | $R_T$ =499k $\Omega$                              | 112  | 130  | 148  | kHz   |  |

| Maximum Duty Cycle                   | D <sub>MAX</sub>           | $R_T$ =499k $\Omega$                              | 95   | 97.5 |      | %     |  |

| GATE                                 |                            |                                                   |      |      |      |       |  |

| GATE High Threshold                  | $V_{GATE}$                 |                                                   | 12   | 13   | 13.8 | V     |  |

| GATE Output Rise Time                | T <sub>RISE</sub>          | C <sub>GATE</sub> =1nF                            |      | 40   |      | ns    |  |

| GATE Output Fall Time                | T <sub>FALL</sub>          | C <sub>GATE</sub> =1nF                            |      | 40   |      | ns    |  |

| GATE Source Current <sup>(5)</sup>   | I <sub>GATE-SO</sub>       | V <sub>GATE</sub> =0V                             |      | 1.5  |      | Α     |  |

| GATE Sink Current <sup>(5)</sup>     | I <sub>GATE-SI</sub>       | V <sub>GATE</sub> =13V                            |      | 0.7  |      | Α     |  |

| Enable                               |                            |                                                   |      |      |      |       |  |

| EN High Threshold                    | $V_{\text{EN-HI}}$         | V <sub>EN</sub> Rising                            | 1.5  |      |      | V     |  |

| EN Low Threshold                     | $V_{EN\text{-}LO}$         | V <sub>EN</sub> Falling                           |      |      | 8.0  | V     |  |

| EN Input Current                     | I <sub>EN</sub>            | V <sub>EN</sub> =3.3V                             |      | 3    | 4    | μA    |  |

| PWM Dimming                          | PWM Dimming                |                                                   |      |      |      |       |  |

| PWM High Threshold                   | $V_{\text{PWMI-HI}}$       | V <sub>PMW</sub> Rising                           | 1.5  |      |      | V     |  |

| PWM Low Threshold                    | $V_{\text{PWMI-LO}}$       | V <sub>PMW</sub> Falling                          |      |      | 8.0  | V     |  |

| PWM Pull-down Resistance             | $R_{PWM}$                  |                                                   |      | 1    |      | МΩ    |  |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  =24V,  $T_A$  = +25°C, unless otherwise noted.

| Parameters                                                                                     | Symbol               | Condition                            | Min  | Тур   | Max  | Units |

|------------------------------------------------------------------------------------------------|----------------------|--------------------------------------|------|-------|------|-------|

| DIMO                                                                                           |                      |                                      |      |       |      |       |

| DIMO High Threshold                                                                            | $V_{DIMO}$           | V <sub>IN</sub> =24V                 | 12.8 | 13.3  | 13.8 | V     |

| DIMO Source Current <sup>(5)</sup>                                                             | I <sub>DIMO-SO</sub> | V <sub>DIMO</sub> =0V                |      | 0.1   |      | Α     |

| DIMO Sink Current <sup>(5)</sup>                                                               | I <sub>DIMO-SI</sub> | V <sub>DIMO</sub> =13V               |      | 0.2   |      | Α     |

| Analog Dimming                                                                                 |                      |                                      |      |       |      |       |

| Maximum Analog Dimming Threshold                                                               | $V_{ADMAX}$          |                                      | 2.25 | 2.34  | 2.43 | V     |

|                                                                                                | $V_{FB\_ADIM}$       | V <sub>ADIM</sub> =24mV              |      | 9.8   |      | mV    |

|                                                                                                |                      | V <sub>ADIM</sub> =100mV             |      | 28.4  |      | mV    |

| Dimming Linearity                                                                              |                      | V <sub>ADIM</sub> =240mV             |      | 63.3  |      | mV    |

|                                                                                                |                      | V <sub>ADIM</sub> =480mV             |      | 123.3 |      | mV    |

|                                                                                                |                      | V <sub>ADIM</sub> =720mV             |      | 183.3 |      | mV    |

| ADIM_P High Threshold                                                                          | $V_{ADIM\ PHI}$      |                                      | 1.5  |       |      | V     |

| ADIM_P Low Threshold                                                                           | $V_{ADIM\ PLO}$      |                                      |      |       | 8.0  | V     |

| ADIM_P Pull Down Resistor                                                                      | R <sub>ADIM P</sub>  |                                      |      | 1     |      | МΩ    |

| ADIM_P Floating (when the voltage high than this level, IC take it as no pulse signal applied) | $V_{ADIM\_PF}$       |                                      | 6    | 6.45  | 6.9  | V     |

| Current Sense                                                                                  |                      |                                      |      | •     |      |       |

| Current Limit Value                                                                            | $V_{CL}$             | Duty=0                               | 435  | 485   | 535  | mV    |

| OCP Detect Voltage                                                                             | $V_{OCP}$            | Over Current Protection              |      | 490   |      | mV    |

| Leading Edge Blanking Time                                                                     | $T_{BLANK}$          |                                      | 100  | 180   | 250  | ns    |

| Compensation                                                                                   |                      |                                      |      |       |      |       |

| Transconductance of Error Amplifier                                                            | $G_{EA}$             |                                      | 280  | 370   | 460  | μA/V  |

| Maximum Sourcing/Sinking Current                                                               | I <sub>EA</sub>      |                                      | 80   |       |      | μA    |

| Soft Start Current                                                                             | $I_{SS}$             | V <sub>FB</sub> <0.8*IREF            | 15   | 22    | 30   | μΑ    |

| Time for COMP Saturated Protection Detection                                                   | $T_{COMP}$           |                                      |      | 2048  |      | cycle |

| Over Voltage Protection                                                                        |                      |                                      |      |       |      |       |

| OVP Threshold                                                                                  | $V_{\text{OVP-TH}}$  |                                      | 4.9  | 5     | 5.1  | V     |

| OVP Threshold Hysteresis                                                                       | V <sub>OVP-HYS</sub> |                                      |      | 440   |      | mV    |

| SCP Protection Threshold                                                                       | V <sub>OVP-SCP</sub> |                                      | 250  | 300   | 350  | mV    |

| Output Short Protection                                                                        |                      |                                      |      |       |      |       |

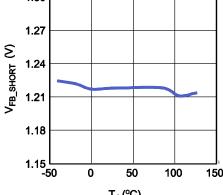

| FB Short Protection Threshold                                                                  |                      |                                      | 1.15 | 1.22  | 1.29 | V     |

| Propagation time for short circuit detection                                                   | T <sub>OFF</sub>     | FB=1.3V, FAULT goes form high to low |      | 1.4   | 2    | μs    |

| Thermal Shutdown (5)                                                                           |                      |                                      |      | 160   |      | °C    |

#### Notes:

5) Guaranteed by design

2.25 L -50

0

50

T<sub>J</sub> (°C)

100

150

50

T<sub>J</sub> (°C)

100

150

0

6.90 L -50

2.30 L -50

0

50

T<sub>J</sub> (°C)

100

150

SCP Threshold vs. TJ

150

1.30 0.32 1.27 0.31 VovP-scP (V) 1.24 0.30 1.21 0.29 1.18 0.28 L -50 1.15 L -50 0 50 100 150 0 50 100 T<sub>J</sub> (°C) T<sub>J</sub> (°C)

100

150

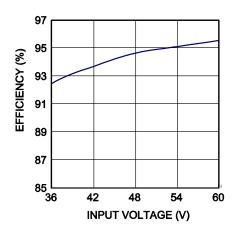

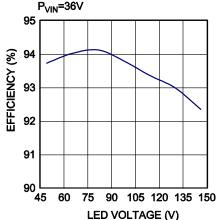

PVIN<sub>(bus voltage)</sub>=36V, VIN<sub>(IC supply)</sub>=12V,  $V_{LED}$ =150V,  $I_{LED}$ =240mA,  $f_{S}$ =100kHz, L=330 $\mu$ H. Otherwise noticed.

#### Effciency vs. Input Voltage

#### Efficiency vs. LED Voltage P<sub>VIN</sub>=36V

$PVIN_{(bus\ voltage)} = 36V,\ VIN_{(IC\ supply)} = 12V,\ V_{LED} = 150V,\ I_{LED} = 240mA,\ f_S = 118kHz,\ L = 330\mu H.\ Otherwise$ noticed.

$PVIN_{(bus\ voltage)} = 36V,\ VIN_{(IC\ supply)} = 12V,\ V_{LED} = 150V,\ I_{LED} = 240mA,\ f_S = 100kHz,\ L = 330\mu H.\ Otherwise$ noticed.

# **PIN FUNCTIONS**

| Pin# | Name    | Pin Function                                                                                                                                                                                                                                                                                                                                 |

|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VIN     | Input Supply Pin, 8-26V. It is the input of internal linear regulator. Must be locally bypassed.                                                                                                                                                                                                                                             |

| 2    | FAULT   | Fault Indication Output Pin, open drain. FAULT is high-Z during normal operation, and pulled to GND when fault is triggered.                                                                                                                                                                                                                 |

| 3    | GATE    | External MOSFET Gate Driver Pin.                                                                                                                                                                                                                                                                                                             |

| 4    | UVLO    | Input Voltage Bus UVLO Pin. A voltage higher than UVLO threshold (2.37V) to enable IC.                                                                                                                                                                                                                                                       |

| 5    | GND     | Ground.                                                                                                                                                                                                                                                                                                                                      |

| 6    | CS      | Switch Current Sense Input Pin. It is used to sense the current of the external power FET. It integrates a built-in blanking time to avoid switching noise interruption.                                                                                                                                                                     |

| 7    | RT      | Switching frequency set Pin. A resistor connected between this pin and GND sets the frequency.                                                                                                                                                                                                                                               |

| 8    | REF     | Reference Output Pin. 5V reference voltage with ±1% accuracy. Must be locally bypassed.                                                                                                                                                                                                                                                      |

| 9    | PWM     | PWM Dimming Input Pin. Apply a PWM signal on this pin for brightness control. The GATE and DIMO are disabled when PWM signal is low. The GATE and DIMO are enabled when PWM signal is high.                                                                                                                                                  |

| 10   | DIMO    | External Dimming MOS Driving Signal Pin. This pin is pulled down to GND when the PWM signal is Low, or the protection is triggered.                                                                                                                                                                                                          |

| 11   | ADIM_P  | Pulse signal Input Analog Dimming Input Pin. Apply a high-frequency pulse signal on this pin while doing pulse signal input analog dimming. Pull this pin high (>6.9V) to disable the pulse-signal-input analog dimming function.                                                                                                            |

| 12   | ADIM    | Analog Dimming Input Pin. Apply a DC voltage from 0 to 2.34V to adjust the amplitude of LED current from minimum to full scale to implement the DC analog dimming function. Place a capacitor on this pin while doing pulse signal input analog dimming. Keep the voltage of this pin higher than 2.43V when analog dimming is not required. |

| 13   | СОМР    | Compensation Pin. This pin is used to compensate the regulation control loop. Connect a capacitor or a series RC network from COMP to GND. COMP pin is also used for soft start. At IC start up, the internal error sourcing/sinking current is limited until the output current reaches 80% of setting current.                             |

| 14   | FB      | Feedback Input Pin. 600mV internal feedback voltage. Connect a current sense resistor from FB to GND. The FB voltage is higher than 1.22V for 1us, the short load protection is triggered, and IC latch off.                                                                                                                                 |

| 15   | OVP     | Over Voltage Protection Input Pin. Connect a resistor divider from output to this pin to program the OVP threshold. When the voltage of this pin reaches 5V, the MP4013B triggers over voltage protection.                                                                                                                                   |

| 16   | EN/SYNC | Enable/Switching frequency Synchronization Pin. A high level to enable the IC. Apply a high frequency (>40kHz) pulse signal on this pin, the switching frequency can be synchronized.                                                                                                                                                        |

#### **OPERATION**

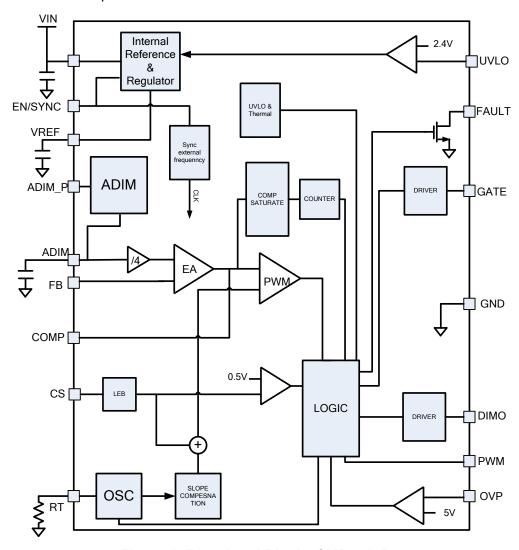

MP4013B drives external MOSFET with current mode architecture to regulate the LED current. which is measured through an external current sense resistor.

MP4013B employs a special circuit for regulating the internal power supply, which covers a wide input voltage from 8V to 26V. MP4013B has a 5V reference with ±1% accuracy, which is used as the reference of external circuit.

The switching frequency of MP4013B can be programmed through the resistor between RT pin and GND to meet variable specifications.

The slope compensation is integrated to avoid sub harmonic resonant when duty cycle is greater than 0.5. The cycle-by-cycle current limit can be programmed by the sense resistor on CS pin.

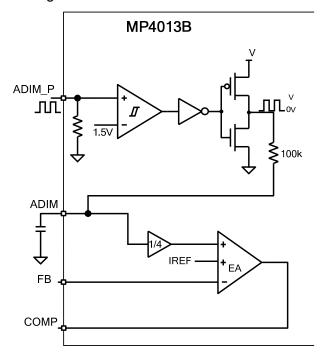

MP4013B implements both DC input analog dimming and pulse signal input analog dimming.

MP4013B integrates Under-Voltage Lockout, Over Voltage Protection, Over Current Protection, Short LED protection, Short Circuit Protection, Short Inductor/diode Protection and OTP.

Figure 1: Functional Block of MP4013B

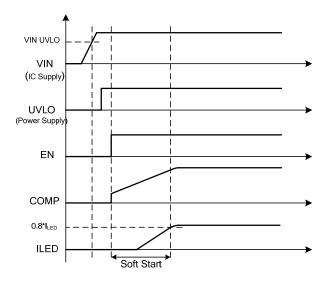

#### **Soft Start**

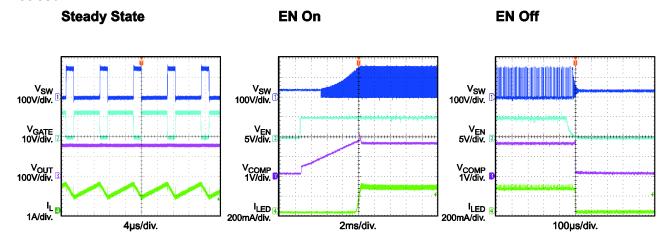

MP4013B implements soft start by limiting the current of the internal error amplifier when startup. The COMP is firstly jump to its clamp voltage (~0.3V), and then the sourcing/ sinking current of the internal error amplifier is limited to charge up external COMP capacitor. IC is always in soft start mode until the output current reaches 0.8 of the setting value to achieve the soft start.

The soft start process is showing the figure 2, note that the VIN UVLO, UVLO and EN get the same priority to ensure the soft start at any startup condition.

Figure 2: Soft Start Process

#### **Analog Dimming**

MP4013B implements DC input analog dimming and pulse signal input analog dimming.

For DC input analog dimming, apply a DC voltage from 0-2.34V on ADIM pin to linearly adjust internal LED current reference voltage from minimum to the maximum value.

For pulse-signal-input analog dimming, place a capacitor on the ADIM pin and apply a pulse signal (>10 kHz recommended) on ADIM\_P pin. This external pulse signal is adjusted internally and forms an internal pulse signal with the same duty and internal reference amplitude. Through an R-C filter, the average voltage of this internal pulse signal is gotten on ADIM pin. Adjust the duty cycle of the pulse signal on ADIM\_P to

adjust the voltage on ADIM pin and realize the pulse signal input analog dimming.

Pull ADIM\_P high (>6.9V) to disable the pulse-signal-input analog dimming.

Connect ADIM pin to 2.43V or higher, if neither analog dimming or pulse-signal-input analog dimming is not used.

Figure 3: Analog Dimming Functional Block PWM Dimming

PWM dimming can be achieved by applying a PWM signal on PWM pin. When the PWM signal is high, the GATE and DIMO outputs are enabled, and the output of the internal error amplifier is connected to the external compensation network. So the LED current is regulated accurately. When the PWM signal goes low, the GATE signal is disabled, and the DIMO pin is pulled down to GND to turn off the external dimmina MOSFET. Meanwhile, the output of the internal EA is disconnected from the compensation network. Thus, the COMP voltage will be held by the external capacitor. And the dimming MOSFET can prevent the output voltage from being discharged, which helps to achieve the high-speed and deep-ratio PWM dimming with better linear dimming performance.

To avoid the LED flicker in small ratio PWM dimming such as 0.1% PWM dimming duty, the

oscillator is synchronized by the PWM dimming signal.

#### **Protection**

MP4013B includes Under-Voltage Lockout, Over Voltage Protection, Short Load Protection, Short Circuit Protection, Over Current Protection and Short Inductor/diode Protection. If the fault conditions are detected, the Gate, DIMO, COMP and Fault pins are pulled down.

#### A Under Voltage Lockout

MP4013B integrates VIN UVLO. The internal circuit does not work until the VIN voltage reaches 7.1V. The hysteresis of VIN UVLO is 395mV.

#### **B. Over Voltage Protection**

The Over Voltage Protection is detected by the voltage of OVP pin. When the OVP voltage rise to its high threshold, the over voltage protection is triggered. The GATE, DIMO, COMP and Fault pin are pulled down. After the OVP voltage decreases to its low threshold, the IC tries to recover.

#### C. Short Load Protection

In short load condition, a large short current will be detected by FB sense resistor. If the FB sensed voltage is higher than 1.22V for 1.4us, the Short Load Protection is triggered, IC latch off, and FAULT pin pulls to low.

#### **D. Short Circuit Protection**

When short circuit at normal operation, the output voltage is pulled low and no current is sensed on FB pin. If the conditions OVP<300mV, FB<0.3×IREF, COMP>1V are satisfied, the protection is triggered and IC latch off.

Fig 5 shows another circuit for the short circuit protection. It uses a PMOS for PWM dimming and also for short circuit protection. When LED+ is shorted to GND, the MP4013B disables the output of DIMO, and the PMOS is disconnected.

**Figure 4: Short Circuit Protection Scheme**

# E. Over Current Protection (Short Inductor/ Diode Protection)

MP4013B implements cycle-by-cycle current limit function for protection. In normal operation caused by over load and lower input voltage, the over current protection can be recoverable.

In some unexpected cases, like inductor or diode short cases, when the voltage of CS pin which is detected by external CS sense resistor hits latch off current limit value within mini-on time (around 300ns) for 7 consecutive cycles, the Over Current Protection is triggered, IC latch off.

#### F. LED- to GND Short Protection

In LED- to GND short condition, FB pin sense no current that makes the COMP charge to its saturated value. When COMP keeps saturated for 2048 switching cycles and FB is below 30% of internal IREF, protection is triggered, IC latches off.

#### APPLICATION INFORMATION

#### **LED Current Setting**

The LED current is set by LED current sense resistor (R<sub>FB</sub>).

$$R_{\text{FB}} = \frac{600 mV}{I_{\text{LFD}}}$$

#### **Switching Frequency Setting**

The switching frequency is set by an external frequency resistor on RT pin.

$$R_T(k\Omega) = \frac{6.8 \times 10^4}{f_S(kHz)} - 15.6$$

Set switching frequency to 100 kHz, a 664kOhm resistor is needed.

#### Selecting Inductor

Select the inductor to make the circuit work in CCM (Continuous Conduction Mode).

$$L = \frac{V_{IN} \times (V_O - V_{IN})}{V_O \times \Delta I_L \times f_S}$$

Where, △ I<sub>L</sub> is the peak-to-peak current of inductor current. Design the A IL 30% to 60% of inductor average current.

$$I_{L\_AVG} = \frac{V_O \times I_{LED}}{V_{IN}}$$

Make sure the inductor saturated current is greater than the inductor peak current.

$$I_{L\_PK} = I_{L\_AVG} + \frac{1}{2} \Delta I_L$$

#### **Current Sense Resistor Setting**

The cycle-by cycle current limit and slope compensation are both integrated. The current limit value can be programmed by the external CS resistor which connects from CS pin to GND. The maximum value of CS sense resistor can be set as follow:

$$Rcs_1(\Omega) = \frac{0.435 \text{-} 0.27 \times D}{I_{L pk}}$$

The D is duty cycle of GATE signal, in CCM,

$$D = 1 - \frac{V_{IN}}{V_{O}}$$

The I<sub>L\_PK</sub> is the peak current of inductor. The slope compensation is integrated to avoid subharmonic resonant when duty is larger than 0.5 in CCM. The following must be satisfied.

$$Rcs_2(\Omega) = 5.4 \times \frac{L(\mu H) \times fs(kHz)}{V_L(V)} \times 10^{-4}$$

Where, V<sub>L</sub> is the voltage across the inductor at GATE off.

$$V_L(V) = V_{O max} - V_{IN min}$$

The CS resistance must be smaller than R<sub>CS1</sub> and R<sub>CS2</sub>

#### **Over Voltage Protection Setting**

Choose a voltage divider (R1, R2 in typical application) to set the over voltage protection threshold:

$$V_{OVP} = 5V \times \frac{R1 + R2}{R2}$$

Normally set the OVP point 10%-20% higher than normal operation output voltage.

#### **Bus Voltage UVLO Setting**

Choose a voltage divider (R3, R4 in typical application) to set the Input Bus Voltage UVLO point

$$V_{\text{UVLO}} = 2.37V \times \frac{R3 + R4}{R3}$$

Normally, set the Bus voltage UVLO point about 10%-20% lower than minimum input bus voltage.

#### **Selecting MOSFET and Diode**

There are 2 MOSFET for MP4013B applications. One is for boost converter, the power MOSFET; and the other is for PWM dimming, the dimming MOSFET.

Choose the power MOS with voltage rating at least 20% higher than OVP voltage to ensure the safety in all condition. The RMS current of the MOSFET can be calculated as follow.

$$I_{RMS} = \sqrt{D \times (I_{L_AVG}^2 + \frac{1}{12} \Delta I_L^2)}$$

Choose the dimming MOS with the voltage rating 20% higher than OVP voltage, and the current rating is about 3-5 of LED current.

Choose the diode with voltage rating greater than OVP point, at least 20% higher than OVP point, and the current rating greater than LED current.

#### **Selecting Input Capacitor**

The input capacitor reduces the surge current drawn from the input supply and switching noise from the device. Use ceramic capacitor with X7R dielectrics with low ESR and small temperature coefficients.

Select a capacitor to limit the input voltage ripple  $\triangle$  V<sub>IN</sub> to less than 5% to 10% of its DC value.

$$C_{\text{IN}} \ge \frac{\Delta I_{\text{L}}}{8 \times \Delta V_{\text{IN}} \times f_{\text{s}}}$$

#### **Selecting Output Capacitor**

The output capacitor limits the output voltage ripple  $\triangle V_O$  (normally less than 1% to 5% of its DC value), and ensure feedback loop stability.

$$C_{\text{OUT}} \ge \frac{I_{\text{LED}} \times (V_{\text{O}} - V_{\text{IN}})}{\Lambda V_{\text{O}} \times f_{s} \times V_{\text{O}}}$$

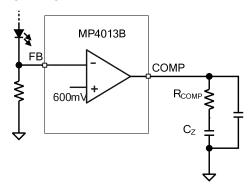

#### **Compensation Network Setting**

The MP4013B implements peak-current-mode control to regulate the LED current through a compensation network on COMP pin. Usually a RCC network is adopted for most applications, as showing in Figure 5.

Figure 5: Compensation Network

The transfer function of the compensation network is (assume  $C_7 >> C_P$ ):

$$EA(s) \approx \frac{G_{\text{EA}} \times R_{\text{FB}}}{R_{\text{FB}} + R_{\text{LED\_AC}}} \times \frac{1}{s \times C_z} \times \frac{1 + s \times C_z \times R_{\text{COMP}}}{1 + s \times C_P \times R_{\text{COMP}}}$$

Where, GEA is the transconductance of internal error amplifier.  $G_{EA}$ =370uA/V.  $R_{LED\ AC}$  is the dynamic resistor of LED load, which can be gotten from

$$R_{LED\_AC} = \frac{\Delta V_{LED}}{\Delta I_{LED}}$$

The zero of compensation network is

$$f_{Z\_EA} = \frac{1}{2\pi \times C_Z \times R_{COMP}}$$

The pole of this compensation network is

$$f_{P\_EA} = \frac{1}{2\pi \times C_P \times R_{COMP}}$$

The power stage of boost converter is

$$f_{P\_PS} = \frac{1}{2\pi \times (\frac{V_O}{I_{LED}} // (R_{LED\_AC} + R_{FB})) \times C_{OUT}}$$

Where, Vo is output voltage, ILED is LED current, C<sub>OUT</sub> is output capacitance. The right-half-plane (RHP) zero of boost converter stage is:

$$f_{RHP_z} = \frac{(1-D)^2 \times \frac{V_o}{I_{LED}}}{2\pi \times L}$$

Choose the cross frequency fc below 1/3 of f<sub>RHP Z</sub> to get the R<sub>COMP</sub> value as follow.

$$R_{\text{COMP}} = \frac{R_{\text{LED\_AC}} + R_{\text{FB}}}{R_{\text{FB}}} \frac{fc \times C_{\text{OUT}} \times 2\pi}{G_{\text{EA}} \times (1 - D) \times G_{\text{CS}}}$$

Where, G<sub>CS</sub> is conductance of CS circuit.

The zero of the compensation network is to compensate the power-stage pole.

$$C_z = \frac{1}{2\pi \times f_{PS}} \times R_{COMP}$$

The pole of the compensation network is to compensate the RHP zero.

$$C_P = \frac{1}{2\pi \times f_{RHP}} \times R_{COMP}$$

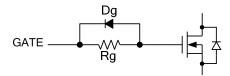

#### Gate Drive Design

A 10-20  $\Omega$  gate resistor is recommended as following figure.

Figure 6: Gate Drive w/ Resistor

#### TYPICAL APPLICATION CIRCUIT