# MP62160/MP62161

3.3V/5V, Single-Channel 2A Current-Limited Power Distribution Switch with Output Discharge

# **DESCRIPTION**

The MP62160/MP62161 Power Distribution Switch features internal current limiting to prevent damage to host devices due to faulty load conditions. The MP62160/MP62161 operates from a 3.3V or 5V input voltage and includes an  $85m\Omega$  Power MOSFET to handle up to 2A continuous load with a 2.8A typical current limit. The MP62160/MP62161 has built-in protection for both over current and increased thermal stress. For over-current protection (OCP), the device will limit the current by going into a constant current mode.

When continuous output overload condition exceeds power dissipation of the package, the thermal protection will shut the part off. The device will recover once the device temperature reduces to approx 120°C.

The MP62160/MP62161 involves a discharge function that provides a resistive discharge path for the external output capacitor when the part is disabled.

The MP62160/MP62161 is available in QFN8E MSOP8E and SOIC8 packages.

# **FEATURES**

- 2A Continuous Current

- 2.8A accurate Current Limit

- Output Discharge Function

- 2.7V to 5.5V Supply Range

- 90uA Quiescent Current

- 85mΩ MOSFET

- Thermal-Shutdown Protection

- Under-Voltage Lockout

- 8ms FLAG Deglitch Time

- No FLAG Glitch During Power Up

- Reverse Current Blocking

- Active High & Active Low Options

- UL Recognized: E322138

# APPLICATIONS

- Smartphone and PDA

- Portable GPS Device

- Notebook PC

- Set-top-box

- Telecom and Network Systems

- PC Card Hot Swap

- USB Power Distribution

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance.

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

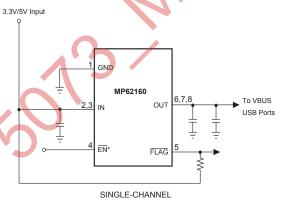

# TYPICAL APPLICATION

\*: EN is active high for MP62161

**UL Recognized Component**

### ORDERING INFORMATION

| Part Number | Enable         | Switch | Maximum<br>Continuous<br>Load Current | Typical Short-<br>Circuit Current<br>@ T <sub>A</sub> =25C | Package              | Top<br>Marking | Free Air<br>Temperature<br>(T <sub>A</sub> ) |

|-------------|----------------|--------|---------------------------------------|------------------------------------------------------------|----------------------|----------------|----------------------------------------------|

| MP62160DS   |                |        |                                       |                                                            | SOIC8                | 62160DS        |                                              |

| MP62160DD   | Active<br>Low  |        |                                       |                                                            | QFN8E<br>(2mm x 3mm) | 62160DD        |                                              |

| MP62160DH*  |                | Single | 2A                                    | 2.8A                                                       | MSOP8E               | 62160DH        | -40°C to +85°C                               |

| MP62161DD   | Active<br>High |        |                                       |                                                            | QFN8E<br>(2mm x 3mm) | 62161DD        |                                              |

| MP62161DH   | 9.1            |        |                                       |                                                            | MSOP8E               | 62161DH        |                                              |

\* For Tape & Reel, add suffix –Z (e.g. MP62160DH–Z). For RoHS Compliant Packaging, add suffix –LF (e.g. MP62160DH–L)

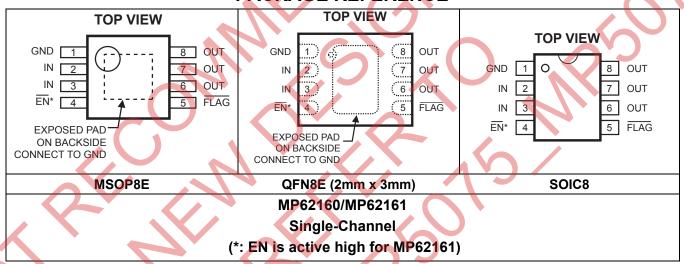

# PACKAGE REFERENCE

| Δ | BSOL | UTF             | MAXIMUM | RATINGS | (1) |

|---|------|-----------------|---------|---------|-----|

|   | DOCE | $\cup$ $\sqcup$ |         |         |     |

| IN                                                   |               |

|------------------------------------------------------|---------------|

| EN, FLAG, OUT to GND Continuous Power Dissipation (T |               |

| MSOP8E                                               |               |

| QFN8E (2mm x 3mm)                                    |               |

| SOIC8                                                |               |

| Junction Temperature                                 |               |

| Lead Temperature                                     |               |

| Storage Temperature68                                |               |

| Operating Temperature                                | 40°C to +85°C |

| Thermal Resistance (3) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |   |

|------------------------|-------------------------|-------------------------|---|

| MSOP8E                 | 55                      | 12 °C/W                 | / |

| QFN8E (2mm x 3mm)      | 55                      | 12 °C/W                 | / |

| SOIC8                  | 90                      | 42 °C/W                 | / |

#### Notes

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS** (4)

T<sub>A</sub>=+25°C, 2.7V≤V<sub>IN</sub>≤5.5V, R<sub>FLAG</sub>=100kΩ, unless otherwise noted.

| Parameter                            | Symbol                | Condition                                                                                    | Min  | Тур | Max      | Units    |

|--------------------------------------|-----------------------|----------------------------------------------------------------------------------------------|------|-----|----------|----------|

| IN Voltage Range                     | $V_{IN}$              |                                                                                              | 2.7  |     | 5.5      | V        |

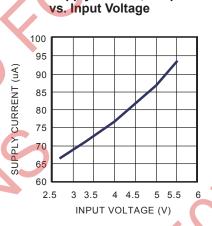

| Supply Current                       | I <sub>IN_ON</sub>    | Device Active, V <sub>OUT</sub> =float, V <sub>IN</sub> =5.5V, I <sub>OUT</sub> =0           |      | 90  | 120      | μΑ       |

| Shutdown Current                     | I <sub>IN_OFF</sub>   | Device Disable, V <sub>OUT</sub> =float, V <sub>IN</sub> =5.5V                               |      | 1   |          | μA       |

| Off Switch Leakage                   |                       | Device Disable, V <sub>OUT</sub> =GND, V <sub>IN</sub> =5.5V                                 |      | 1   |          | μΑ       |

| Current Limit                        | I <sub>OS</sub>       |                                                                                              | 2.1  | 2.8 | 3.5      | Α        |

| Trip Current                         | I <sub>trip</sub>     | Current Ramp (slew rate≤100A/s) on Output                                                    |      | 3.1 | 4        | Α        |

| Under-voltage Lockout                | $INUV_{VTH}$          | V <sub>IN</sub> Rising Edge                                                                  | 1.95 |     | 2.65     | V        |

| Under-voltage<br>Hysteresis          | INUV <sub>HYS</sub>   | 12                                                                                           |      | 250 |          | mV       |

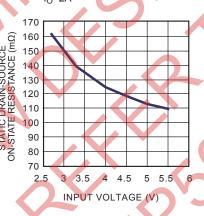

|                                      |                       | MSOP8E                                                                                       |      | 75  | 120      | mΩ       |

| FET On Resistance                    | R <sub>DS(on)</sub>   | $V_{IN}=5V$ , $I_{OUT}=100$ mA (- QFN8E<br>40°C≤ $T_A \le 85$ °C) (2mm x 3mm)                |      | 75  | 120      | mΩ       |

|                                      |                       | SOIC8                                                                                        |      | 85  | 120      | mΩ       |

| EN Input Logic High<br>Voltage       | VIH <sub>EN</sub>     |                                                                                              | 2    |     | 7.       | V        |

| EN Input Logic Low<br>Voltage        | VIL <sub>EN</sub>     |                                                                                              |      |     | 0.8      | V        |

| FLAG Output Logic<br>Low Voltage     | V <sub>OL</sub>       | I <sub>FLAG</sub> =5mA                                                                       |      |     | 0.4      | V        |

| FLAG Output High<br>Leakage Current  | I <sub>FLAG_OFF</sub> | V <sub>FLAG</sub> =5.5V                                                                      |      |     | 1        | μΑ       |

| Thermal Shutdown<br>Threshold        | T                     |                                                                                              |      | 140 |          | °C       |

| Thermal Shutdown<br>Hysteresis       | $T_{J\_HYS}$          | 76, 70                                                                                       |      | 20  |          | °C       |

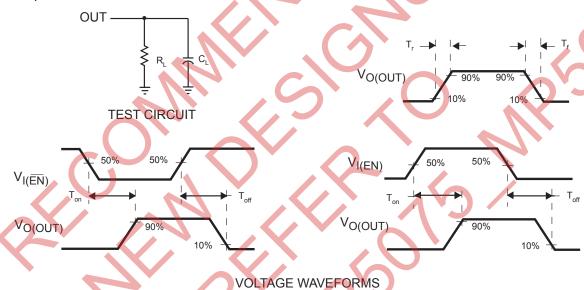

| <b>V</b> <sub>OUT</sub> Rising Time  | Tr <sup>(5)</sup>     | $V_{IN}=5.5V$ , $C_L=1\mu F$ , $R_L=5\Omega$                                                 |      | 0.9 |          | ms       |

| 3                                    |                       | $V_{IN}=2.7V$ , $C_L=1\mu F$ , $R_L=5\Omega$                                                 |      | 1.7 | 0.5      | ms       |

| <b>V</b> <sub>OUT</sub> Falling Time | Tf <sup>(6)</sup>     | $V_{IN}=5.5V$ , $C_{L}=1\mu F$ , $R_{L}=5\Omega$                                             |      |     | 0.5      | ms       |

| Turn On Time                         | Ton (7)               | $V_{IN}$ =2.7V, $C_L$ =1 $\mu$ F, $R_L$ =5 $\Omega$<br>$C_L$ =100 $\mu$ F, $R_L$ =5 $\Omega$ |      |     | 0.5<br>3 | ms<br>ms |

| Turn Off Time                        | Toff <sup>(8)</sup>   | C <sub>L</sub> =100μF, R <sub>L</sub> =5Ω                                                    |      |     | 10       | ms       |

| Discharge Resistance                 | R <sub>DIS</sub>      | - 100μ1, 11, -022                                                                            |      | 250 | 10       | Ω        |

| FLAG Deglitch Time                   | T <sub>FLAG_Deg</sub> | Delay time for assertion or deassertion due to over-current condition                        | 4    | 8   | 15       | ms       |

| EN Input Leakage                     | I <sub>EN</sub>       | V <sub>EN</sub> =0~5.5V                                                                      | -1   |     |          | μA       |

| Reverse Leakage<br>Current           | I <sub>REV</sub>      | V <sub>OUT</sub> =5.5V, V <sub>IN</sub> =GND                                                 | -    | 0.2 |          | μА       |

### NOTE:

- 4) Production test at +25°C. Specifications over the temperature range are guaranteed by design and characterization.

- 5) Measured from 10% to 90%.

- 6) Measured from 90% to 10%.

- 7) Measured from (50%) EN signal to (90%) output signal.

- 8) Measured from (50%) EN signal to (10%) output signal.

# **PIN FUNCTIONS**

| Pin #<br>SOIC8 | Pin #<br>MSOP8E | Pin #<br>QFN8E | Name | I/O | Description                                                 |

|----------------|-----------------|----------------|------|-----|-------------------------------------------------------------|

| 1              | 1               | 1              | GND  |     | Ground.                                                     |

| 2, 3           | 2, 3            | 2, 3           | IN   | I   | Input Voltage. Accepts 2.7V to 5.5V input.                  |

| 4              | 4               | 4              | EN   | I   | Active Low: (MP62160), Active High: (MP62161)               |

| 5              | 5               | 5              | FLAG | 0   | IN-to-OUT Over-current, active-low output flag. Open-Drain. |

| 6, 7, 8        | 6, 7, 8         | 6, 7, 8        | OUT  | 0   | IN-to-OUT Power-Distribution Output (for all 3 output pins) |

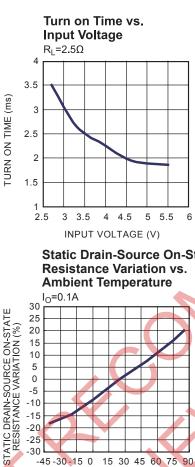

# TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = +25$ °C, unless otherwise noted.

Figure 1—Test Circuit and Voltage Waveforms

© 2018 MPS. All Rights Reserved.

### TYPICAL PERFORMANCE CHARACTERISTICS

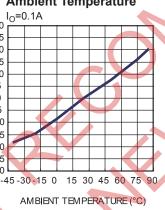

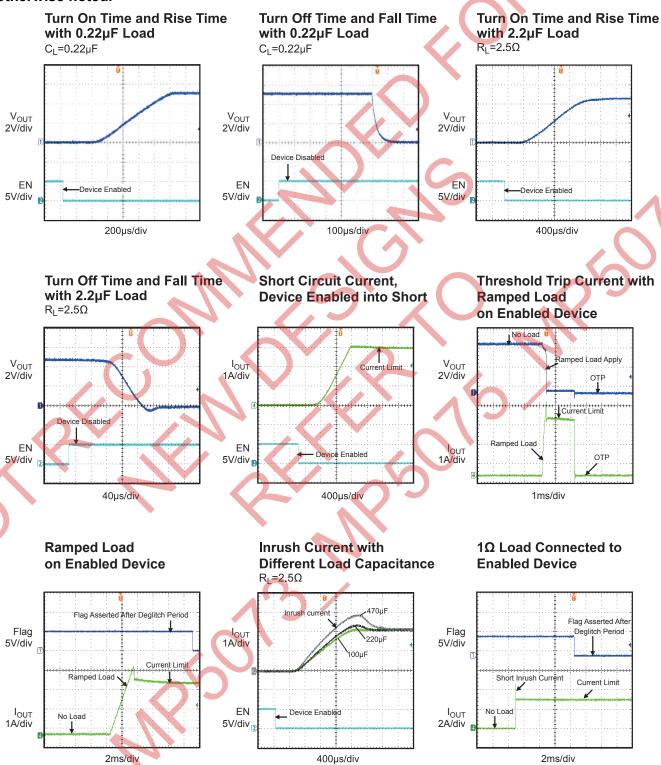

$V_{IN} = 5V$ ,  $V_{EN} = 0V$  for MP62160 or 5V for MP62161,  $C_L = 2.2 \mu F$ ,  $R_{FLAG} = 100 k \Omega$ ,  $T_A = +25 ^{\circ} C$ , unless otherwise noted.

Turn off Time vs. Input Voltage  $R_L=2.5\Omega$ 0.25 (ms) 0.2 TURN OFF TIME 0.15 0.1 0.05 3 3.5 4 4.5 5 5.5 INPUT VOLTAGE (V)

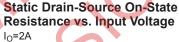

Static Drain-Source On-State

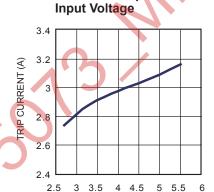

Threshold Trip Current vs.

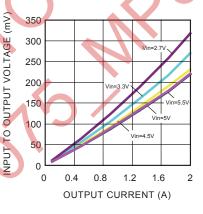

Input to Output Voltage vs **Load Current**

Supply Current, Output Enabled

**Current Limit Response Time**

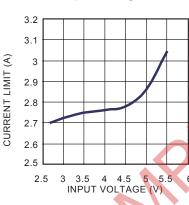

**Current Limit** vs. Input Voltage

20

15

10

5

0

-5

-10

-15

-20

-25

vs. Peak Current 30 **CURRENT LIMIT RESPONSE TIME** 25 20 15 10 5 0 PEAK CURRENT (A)

INPUT VOLTAGE (V)

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  =5V,  $V_{EN}$ =0V for MP62160 or 5V for MP62161,  $C_L$ =2.2 $\mu$ F,  $R_{FLAG}$ =100k $\Omega$ ,  $T_A$  = +25°C, unless otherwise noted.

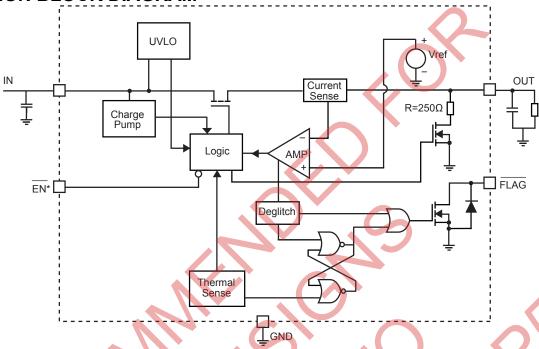

# **FUNCTION BLOCK DIAGRAM**

\*: EN is active high for MP62161

Figure2—Functional Block Diagram

# DETAILED DESCRIPTION

#### **Over Current**

When the load exceeds trip current (minimum threshold current triggering constant-current mode) or a short is present, MP62160/MP62161 switches into to a constant-current mode (current limit value). MP62160/MP62161 will be shutdown only if the over current condition stays long enough to trigger thermal protection.

Trigger over current protection for different overload conditions occurring in applications:

- The output has been shorted or overloaded before the device is enabled or input applied. MP62160/MP62161 detects the short or overload and immediately switches into a constant-current mode.

- 2) A short or an overload occurs after the device is enabled. After the current-limit circuit has been tripped (reached the trip current threshold), the device switches into constantcurrent mode. However, high current may flow for a short period of time before the current-limit circuit can react.

3) Output current has been gradually increased beyond the recommended operating current. The load current rises until the trip current threshold is reached or until the thermal limit of the device is exceeded. The MP62160/MP62161 is capable of delivering current up to the trip current threshold without damaging the device. Once the trip threshold has been reached, the device switches into its constant-current mode.

### Flag Response

The FLAG pin is an open drain configuration. This FLAG will report a fail mode after an 8ms deglitch timeout. This is used to ensure that no false fault signals are reported. This internal deglitch circuit eliminates the need for extend components. The FLAG pin is not deglitched during an over temp. or a voltage lockout.

#### **Thermal Protection**

The purpose of thermal protection is to prevent damage in the IC by allowing exceptive current to flow and heating the junction. The temperature is internally monitored until the thermal limit is reached. Once this temperature is reached, the switch will turn off and allow the chip to cool. The switch has a built-in hysteresis.

### **Under-voltage Lockout (UVLO)**

This circuit is used to monitor the input voltage to ensure that the MP62160/MP62161 is operating correctly.

This UVLO circuit also ensures that is no operation until the input voltage reaches the minimum spec.

#### **Enable**

The logic pin disables the switch to reduce overall supply current .Once the EN pin reaches logic enable threshold, the MP62160/MP62161 is enabled.

### **Output Discharge**

The part involves a discharge function that provides a resistive discharge path for the external output capacitor. The function will be active when the part is disabled (Input voltage is under UVLO or enable is deasserted) and it will be done in a very limited time.

# APPLICATION INFORMATION

# **Power-Supply Considerations**

Over 10µF capacitor between IN and GND is recommended. This precaution reduces power-supply transients that may cause ringing on the input and improves the immunity of the device to short-circuit transients.

In order to achieve smaller output load transient ripple, placing a high-value electrolytic capacitor on the output pin(s) is recommended when the load is heavy.

© 2018 MPS. All Rights Reserved.

# PACKAGE INFORMATION

#### **MSOP8E (EXPOSED PAD)** 0.087(2.20) 0.114(2.90) 0.122(3.10) 0.099(2.50) 0.114(2.90) 0.187(4.75) 0.062(1.58) 0.199(5.05) 0.074(1.88) 0.122(3.10) PIN 1 ID (NOTE 5) **Exposed Pad** 0.010(0.25) 0.0256(0.65)BSC 0.014(0.35) **BOTTOM VIEW TOP VIEW GAUGE PLANE** 0.010(0.25) 0.030(0.75) 0.043(1.10)MAX 0.037(0.95) 0.004(0.10) SEATING PLANE 0.008(0.20) 0.002(0.05) 0.016(0.40) 0.006(0.15) 0.026(0.65) SIDE VIEW **FRONT VIEW** NOTE 0.100(2.54)1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS. 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, 0.075(1.90) 0.181(4.60) PROTRUSION OR GATE BURR. 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

# RECOMMENDED LAND PATTERN

-0.0256(0.65)BSC

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

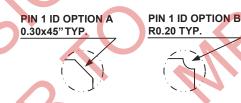

- 5) PIN 1 IDENTIFICATION HAS HALF OR FULL CIRCLE OPTION.

- 6) DRAWING MEETS JEDEC MO-187, VARIATION AA-T.

- 7) DRAWING IS NOT TO SCALE.

0.040(1.00)

0.016(0.40)

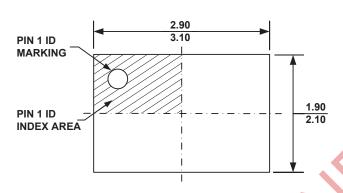

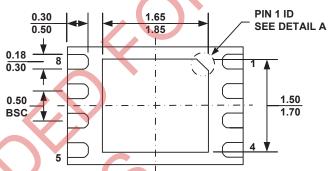

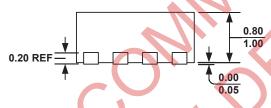

# **PACKAGE INFORMATION** (continued)

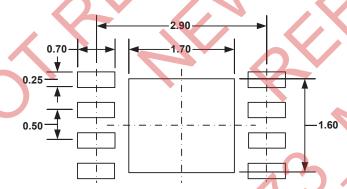

# QFN8E (2mm x 3mm)

**TOP VIEW**

**BOTTOM VIEW**

SIDE VIEW

**DETAIL A**

RECOMMENDED LAND PATTERN

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

- 4) DRAWING CONFORMS TO JEDEC MO-229, VARIATION VCED-2.

- 5) DRAWING IS NOT TO SCALE.