# MP6924, MP6924A

Fast Turn-off, CCM/DCM Compatible Dual LLC Synchronous Rectifier with low Sleep Mode Current

# DESCRIPTION

The MP6924, MP6924A is a dual, fast turn-off, intelligent rectifier for synchronous rectification in LLC resonant converters.

The IC drives two N-channel MOSFETs, regulates their forward voltage drop to  $V_{\text{fwd}}(\text{MP6924:45mV},\text{MP6924A:29mV})$ , and turns the MOSFETs off before the switching current goes negative.

The MP6924, MP6924A has a light-load function to latch off the gate driver under light-load conditions, limiting the current to 175µA.

The MP6924, MP6924A's fast turn-off enables both continuous conduction mode (CCM) and discontinuous conduction mode (DCM).

The MP6924, MP6924A requires a minimal number of readily available, standard, external components and is available in a SOIC-8 package.

Table 1: MP6924A vs. MP6924

| Turn-off Blanking  | 1.75µs vs. 210ns        |  |

|--------------------|-------------------------|--|

| Time               | Improve noise immunity  |  |

| Driving Capability | Be half                 |  |

| Driving Capability | Improve EMI performance |  |

| Famusand Maltages  | 29mV vs. 45mV           |  |

| Forward Voltage    | Improve efficiency      |  |

# **FEATURES**

- Works with Standard and Logic Level MOSFETs

- Compatible with Energy Star

- Fast Turn-Off Total Delay of 35ns

- Wide 4.2V ~ 35V V<sub>DD</sub> Operating Range

- 175µA Low Quiescent Current in Light-Load Mode

- Supports CCM, CrCM, and DCM Operation

- Supports High-Side and Low-Side Rectification

- Power Savings of Up to 1.5W in a Typical Notebook Adapter

- Available in a SOIC-8 Package

# **APPLICATIONS**

- AC/DC Adapters

- PC Power Supplies

- LCD and LED TVs

- Isolated DC/DC Power Converters

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

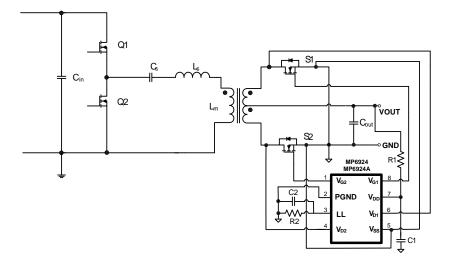

### TYPICAL APPLICATION

# ORDERING INFORMATION

| Part Number* | Package | Top Marketing |  |

|--------------|---------|---------------|--|

| MP6924GS     | SOIC 9  | Saa Balaw     |  |

| MP6924AGS    | SOIC-8  | See Below     |  |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. MP6924GS–Z)

# **TOP MARKING (MP6924GS)**

MP6924 LLLLLLLL MPSYWW

MP6924: Part number LLLLLLL: Lot number MPS: MPS prefix Y: Year code WW: Week code

# **TOP MARKING (MP6924AGS)**

MP6924A LLLLLLL MPSYWW

MP6924A: Part number LLLLLLL: Lot number MPS: MPS prefix Y: Year code WW: Week code

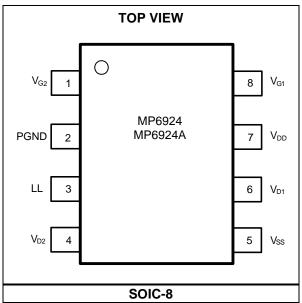

# PACKAGE REFERENCE

# **ABSOLUTE MAXIMUM RATINGS (1)**

| $V_{DD}$ to $V_{SS}$              | 0.3V to +38V                 |

|-----------------------------------|------------------------------|

| PGND to Vss                       | 0.3V to +0.3V                |

| V <sub>G</sub> to V <sub>SS</sub> | 0.3V to +20V                 |

| V <sub>D</sub> to V <sub>SS</sub> | 1V to +180V                  |

| LL to V <sub>SS</sub>             | 0.3V to +6.5V                |

| Continuous power dissipation      | $(T_A = +25^{\circ}C)^{(2)}$ |

| SOIC-8                            | 1.4W                         |

| Junction temperature              | 150°C                        |

| Lead temperature (solder)         | 260°C                        |

| Storage temperature               | 55°C to +150°C               |

| Recommended Operation             | Conditions (3)               |

V<sub>DD</sub> to V<sub>SS</sub> ...... 4.2V to 35V Operating junction temp. (T<sub>J</sub>)...-40°C to +125°C

#### Thermal Resistance (4) $\theta_{JA}$ **Ө**ЈС SOIC-8 ......90 ..... 45 ... °C/W

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)- $T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{DD} = 12V$ ,  $-40^{\circ}C \le T_{J} \le +125^{\circ}C$ , unless otherwise noted.

| Parameter                                                     |                       | Symbol              | Conditions                                                                 | Min      | Тур                     | Max        | Units |

|---------------------------------------------------------------|-----------------------|---------------------|----------------------------------------------------------------------------|----------|-------------------------|------------|-------|

| V <sub>DD</sub> voltage range                                 |                       |                     |                                                                            | 4.2      |                         | 35         | V     |

| V <sub>DD</sub> UVLO rising                                   |                       |                     |                                                                            | 3.7      | 3.95                    | 4.2        | V     |

| V <sub>DD</sub> UVLO hysteresis                               |                       |                     |                                                                            | 0.13     | 0.185                   | 0.24       | V     |

| Operating current                                             |                       | Icc                 | $C_{LOAD} = 4.7 nF,$<br>$F_{SW} = 100 kHz$                                 |          | 16                      | 20         | mA    |

| Quiescent current                                             |                       | ΙQ                  | $V_{SS} - V_{D} = 0.5V$                                                    |          | 4.6                     | 6          | mA    |

| Shutdown current                                              |                       |                     | $V_{DD} = 4V$ , $LL = 0V$<br>$V_{DD} = 20V$ , $LL = 0V$                    |          | 135<br>155              | 190<br>210 | μA    |

| Light-load mode current                                       |                       |                     | 155 201, 22 01                                                             |          | 175                     | 225        | μA    |

| Thermal shutdown (5)                                          | MP6924<br>MP6924A     |                     |                                                                            |          | 150<br>175              |            | °C    |

| Thermal shutdown hyste                                        | eresis <sup>(5)</sup> |                     |                                                                            |          | 10                      |            | °C    |

| Control Circuitry Section                                     |                       |                     |                                                                            |          | 1                       | l          | ı     |

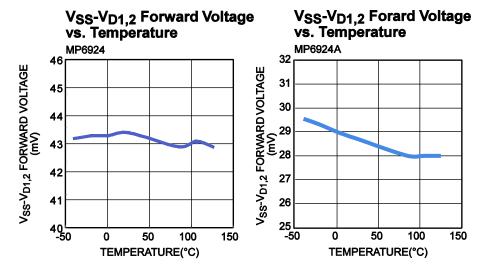

| Vss - V <sub>D</sub> forward voltage                          | MP6924<br>MP6924A     | $V_{\text{fwd}}$    |                                                                            | 28<br>17 | 45<br>29                | 58<br>41   | mV    |

| Turn off threshold (V <sub>SS</sub> -                         | V <sub>D</sub> )      |                     |                                                                            | -56      | -40                     | -20        | mV    |

| Time on delay                                                 | MP6924<br>MP6924A     | t <sub>Don</sub>    | $C_{LOAD} = 4.7 nF$ , $V_{GS} = 2V$                                        |          | 80<br>190               | 140<br>300 | ns    |

| Turn-on delay                                                 | MP6924<br>MP6924A     | t <sub>Don</sub>    | $C_{LOAD} = 10nF, V_{GS} = 2V$                                             |          | 90<br>270               | 180<br>410 | ns    |

| Input bias current on V <sub>D</sub>                          |                       |                     | V <sub>D</sub> = 180V                                                      |          |                         | 1          | μΑ    |

| Turn-on blanking time                                         |                       | t <sub>B_ON</sub>   | $C_{LOAD} = 4.7 nF$                                                        | 0.75     | 1.1                     | 1.65       | μs    |

| Turn-off blanking time MP6924 MP6924A                         |                       | t <sub>B_OFF</sub>  | C <sub>LOAD</sub> = 4.7nF                                                  |          | 210<br>1750             |            | ns    |

| Turn-off blanking V <sub>DS</sub> threshold(MP6924A disabled) |                       | $V_{B\_OFF}$        |                                                                            | 1        | 1.7                     | 2.5        | V     |

| Light-load enter pulse width                                  |                       | TLL                 | $R_{LL} = 100k\Omega$                                                      | 1.7      | 2.3                     | 3          | μs    |

| Light-load turn-on pulse width hysteresis                     |                       | T <sub>LL-H</sub>   | R <sub>LL</sub> = 100kΩ                                                    |          | 0.45                    |            | μs    |

| Palitical action data                                         | MP6924                | <b>-</b>            |                                                                            | 0.5      | 1                       | 1.52       | ms    |

| Light-load enter delay                                        | MP6924A               | $T_{LL	ext{-}D}$    |                                                                            | 45       | 78                      | 121        | μs    |

| Gate disable threshold on LL                                  |                       | V <sub>LL_DIS</sub> |                                                                            | 0.1      | 0.2                     | 0.3        | V     |

| Turn-on threshold (V <sub>DS</sub> )                          |                       | V <sub>LL_DS</sub>  | V <sub>DD</sub> = 12V                                                      | -330     | -230                    | -130       | mV    |

| Gate Driver Section                                           |                       |                     | •                                                                          | <u>.</u> |                         |            | •     |

| V <sub>G</sub> (low)                                          |                       | $V_{G\_L}$          | I <sub>LOAD</sub> = 1mA                                                    |          |                         | 0.1        | V     |

| V <sub>G</sub> (high)                                         |                       | $V_{G\_H}$          | $\frac{V_{DD} > 10V}{V_{DD} \le 10V}$                                      |          | 11.5<br>V <sub>DD</sub> | 13         | V     |

| Turn-off propagation delay                                    |                       |                     | $V_D = V_{SS}$                                                             |          | 15                      |            | ns    |

| Turn-off total delay                                          |                       | <b>t</b> Doff       | $V_D = V_{SS}$ , $C_{LOAD} = 4.7nF$ , $R_{GATE} = 0\Omega$ , $V_{GS} = 2V$ |          | 35                      | 80         | ns    |

|                                                               |                       | t <sub>Doff</sub>   | $V_D = V_{SS}, C_{LOAD} = 10 nF,$<br>$R_{GATE} = 0\Omega, V_{GS} = 2V$     |          | 45                      | 100        | ns    |

| Maximum source current (6)                                    | MP6924<br>MP6924A     |                     |                                                                            |          | 0.5<br>0.13             |            | А     |

| Pull-down impedance                                           |                       |                     |                                                                            |          | 0.6                     | 1.5        | Ω     |

<sup>5)</sup> Guaranteed by characterization. 6) Guaranteed by design.

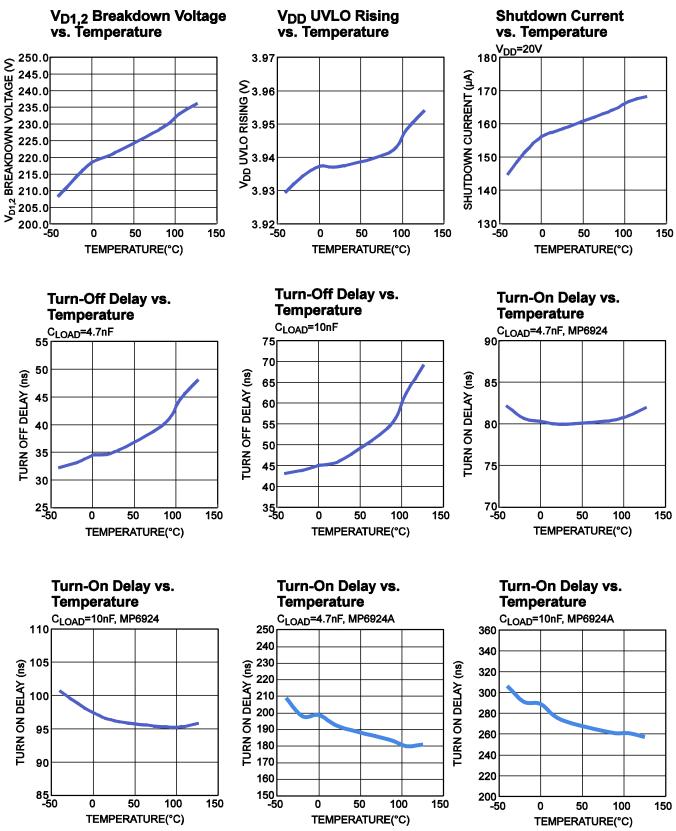

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{DD}$  = 12V, MP6924/MP6924A, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{DD}$  = 12V, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{DD}$  = 12V, unless otherwise noted.

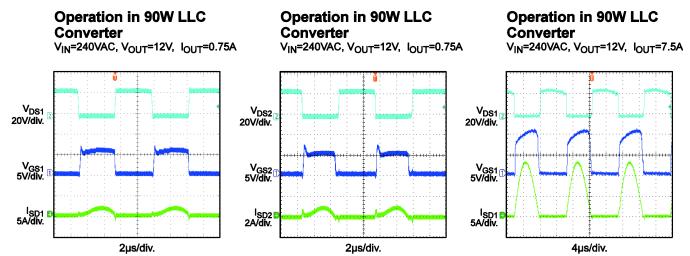

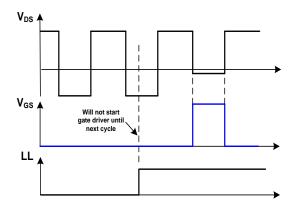

# Operation in 90W LLC Converter

$V_{IN}$ =240VAC,  $V_{OUT}$ =12V,  $I_{OUT}$ =7.5A

# **PIN FUNCTIONS**

| Pin #<br>(SOIC-8) | Name            | Description                                                                                                                                                                                     |

|-------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | $V_{G2}$        | MOSFET 2 gate driver output.                                                                                                                                                                    |

| 2                 | PGND            | Power ground. PGND is the power switch return.                                                                                                                                                  |

| 3                 | LL              | <b>Light-load timing setting.</b> Connect a resistor to LL to set the light-load timing. Leave LL open to prevent the IC from entering light-load mode. Pull LL low to disable the gate driver. |

| 4                 | $V_{D2}$        | MOSFET 2 drain voltage sense.                                                                                                                                                                   |

| 5                 | Vss             | Source pin used as reference for V <sub>D1</sub> and V <sub>D2</sub> .                                                                                                                          |

| 6                 | V <sub>D1</sub> | MOSFET 1 drain voltage sense.                                                                                                                                                                   |

| 7                 | $V_{DD}$        | Supply voltage.                                                                                                                                                                                 |

| 8                 | V <sub>G1</sub> | MOSFET 1 gate driver output.                                                                                                                                                                    |

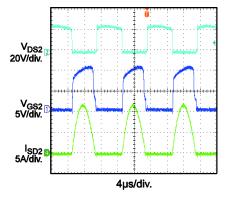

# **BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

# **OPERATION**

MP6924. MP6924A The operates in discontinuous conduction mode continuous conduction mode (CCM), and critical conduction mode (CrCM). When the MP6924, MP6924A operates in either DCM or CrCM, the control circuitry controls the gate in forward mode, and the gate turns off when the MOSFET current is low. In CCM, the control circuitry turns off the gate during very fast transients.

#### **VD Clamp**

Because  $V_{D1,2}$  can go as high as 180V, a high-voltage JFET is used at the input. To prevent excessive currents when  $V_{DS1,2}$  goes below -0.7V, a 1k $\Omega$  resistor is recommended between  $V_{D1,2}$  and the drain of the external MOSFET.

# **Under-Voltage Lockout (UVLO)**

When  $V_{DD}$  is below the  $V_{DD}$  UVLO threshold, the MP6924, MP6924A falls into sleep mode and  $V_{G1,2}$  remains at a low level.

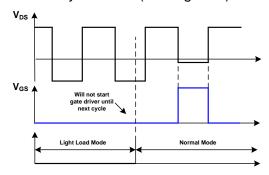

#### **Enable**

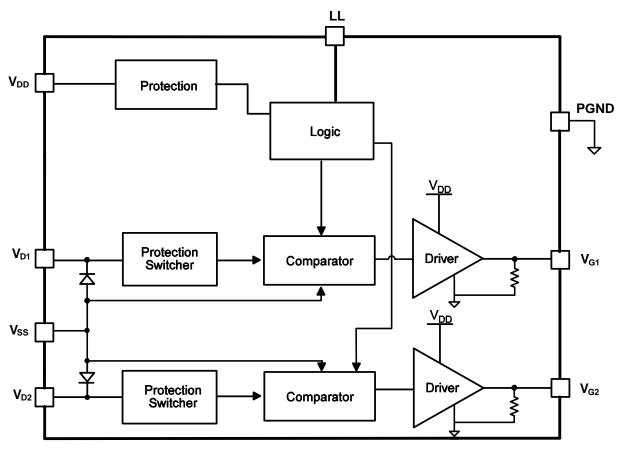

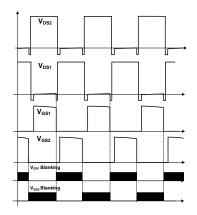

If LL is pulled low, the MP6924, MP6924A is in shutdown mode, which consumes  $175\mu A$  of shutdown current. If LL is pulled high during the rectification cycle, the gate driver will not appear until the next rectification cycle begins (see Figure 2).

Figure 2: LL Control Scheme

### **Thermal Shutdown**

If the junction temperature of the chip exceeds thermal shutdown threshold,  $V_{G1,2}$  is pulled low, and the MP6924, MP6924A stops switching. The IC resumes normal function after the junction temperature drops 10°C.

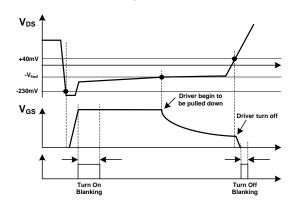

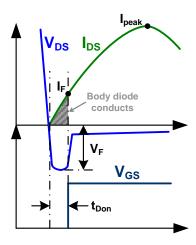

#### **Turn-On Phase**

When the switch current flows through the body diode of the MOSFET, there is a negative voltage drop ( $V_D$  -  $V_{SS}$ ) across the body diode.  $V_{DS}$  is much lower than the turn-on threshold of the control circuitry ( $V_{LL-DS}$ ), which triggers a maximum 500mA of charge current to turn on the MOSFET (see Figure 3).

# **Turn-On Blanking**

The control circuitry contains a blanking function that ensures that when the MOSFET turns on or off, it remains in that state for  $t_{B\_ON}$  (~1.1 $\mu$ s), which determines the minimum on time. During the turn-on blanking period, the turn-off threshold is not blanked completely, but changes to about +100mV (instead of +40mV). This ensures that the part can always turn off, even during the turn-on blanking period, although it does so slower. Avoid setting the synchronous period below  $t_{B\_ON}$  in CCM condition in the LLC converter to eliminate shoot-through.

#### **Conduction Phase**

When  $V_{DS}$  rises above the forward voltage drop (- $V_{fwd}$ ) according to the decrease of the switching current, the MP6924, MP6924A pulls down the gate voltage level to make the on resistance of the synchronous MOSFET larger to ease the rise of  $V_{DS}$ .

Figure 3: Turn-On/-Off Timing Diagram

The control scheme in Figure 3 shows  $V_{DS}$  adjusted to be around  $-V_{fwd}$ , even when the current through the MOSFET is fairly low. This function puts the driver voltage at a very low level when the synchronous MOSFET is turning off, which boosts the turn-off speed.

#### **Turn-Off Phase**

When V<sub>DS</sub> rises to trigger the turn-off threshold (+40mV), the gate voltage is pulled to zero after a very short turn-off delay (see Figure 3).

# **Turn-Off Blanking**

After the gate driver is pulled to zero by  $V_{DS}$  reaching the turn-off threshold (+40mV), turn-off blanking is triggered to ensure that the gate driver is off for at least  $t_{B\_ON}$  to prevent an error trigger on  $V_{DS}$ .

# **Light-Load Latch-Off Function**

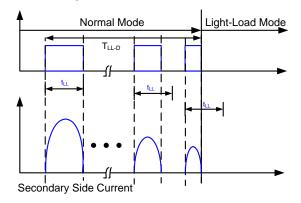

The gate driver of the MP6924, MP6924A is latched off to save driver loss in light-load condition and improve efficiency.

When the MOSFET's switching cycle conducting period falls below  $T_{LL}$ , the MP6924, MP6924A enters light-load mode and latches off the MOSFET after a light-load enter delay,  $T_{LL-D}$  (see Figure 4).

Figure 4: MP6924, MP6924A Entering Light-Load Mode

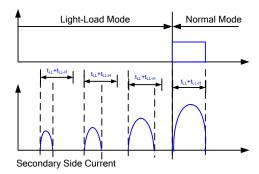

During light-load mode, the MP6924, MP6924A monitors the body diode conduction time. If this time exceeds  $T_{LL}$  +  $T_{LL-H}$ , the IC exits light-load mode and initiates the gate driver in the next new switching cycle (see Figure 5 and Figure 6).

Light-load enter timing ( $T_{LL}$ ) is programmable by connecting a resistor ( $R_{LL}$ ) to LL. By monitoring the LL current (the LL voltage is kept at ~2V internally),  $T_{LL}$  can be calculated with Equation (1):

$$T_{LL} = R_{LL}(k\Omega) \cdot \frac{2.3us}{100k\Omega}$$

(1)

Figure 5: MP6924, MP6924A Exiting Light-Load Mode

If the light-load mode of the MP6924, MP6924A ends during the rectification cycle, the gate driver signal does not appear until the next rectification cycle starts (see Figure 6).

Figure 6: Gate Driver Starts After Exiting Light-Load Mode

### **Anti-Bounce Logic (MP6924)**

The MP6924 has anti-bounce logic, which helps protect the two-channel driver against cross conduction. MP6924A disables this feature.

Figure 7 shows the anti-bounce logic for the two-channel driver. When channel 1 or 2 are turned off, the corresponding channel gate driver is blanked until another channel is switched off.

Figure 7: Anti-Bounce Logic of the Gate Driver

# **APPLICATION INFORMATION**

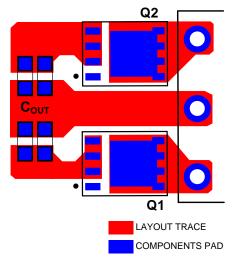

# **Layout Considerations**

Listed below are the main recommendations that should be taken into consideration when designing the PCB.

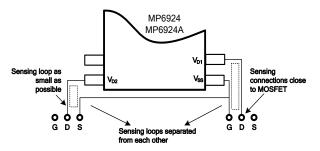

### Sensing for V<sub>D</sub>/V<sub>S</sub>

- 1. Keep the sensing connections  $(V_{D1}/V_{SS}, V_{D2}/V_{SS})$  as close to each of the MOSFETs (drain/source) as possible.

- 2. Keep the two channels' sensing loops separated from each other.

- 3. Make the sensing loop as small as possible (see Figure 8).

Figure 8: Sensing for V<sub>D</sub>/V<sub>S</sub>

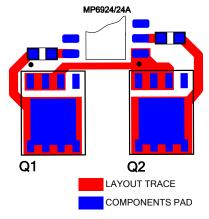

Figure 9 shows a layout example of the MP6924, MP6924A driving PowerPAK SO8 package MOSFETs with two, separate, small sensing loops.

Figure 9: Layout Example for Sensing Loop and V<sub>DD</sub> Decoupling

### **V<sub>DD</sub>** Decoupling Capacitor

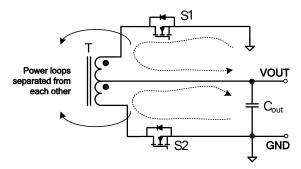

Place a decoupling capacitor no smaller than 1μF from V<sub>DD</sub> to PGND close to the IC for adequate filtering (see Figure 10).

### System Power Loop

- 1. Keep the two channels' power loops separated from each other (see Figure 10).

This minimizes the interaction between the two channels' power loops, which may affect the voltage sensing of the IC.

- 2. Make the power loop as small as possible to reduce parasitic inductance.

Figure 10: System Power Loop

Figure 11 shows a layout example of the power loop trace, which has a minimized loop length. The two channel power traces do not cross each other.

It is highly recommended to place the driver's sensing loop trace away from the power loop trace (see Figure 11). The sensing loop trace and power loop trace can be placed on different layers to keep them separate from each other.

Do not place the driver IC inside the power loop; this may affect MOSFET voltage sensing.

Figure 11: Layout Example for System Power Loop

### **SR MOSFET Selection and Driver Ability**

Power MOSFET selection is a trade-off between  $R_{DS(ON)}$  and  $Q_g$ . To achieve high efficiency, a MOSFET with a smaller  $R_{DS(ON)}$  is recommended. A larger  $Q_g$  with a smaller  $R_{DS(ON)}$  makes the turn-on/-off speed lower and the power loss larger. For the MP6924, MP6924A,  $V_{DS}$  is adjusted at  $V_{fwd}$  during the driving period. A MOSFET with a small  $R_{DS(ON)}$  is not recommended because the gate driver may be kept at a fairly low level with a small  $R_{DS(ON)}$ , even when the system load is high, which makes the advantage of the low  $R_{DS(ON)}$  inconspicuous.

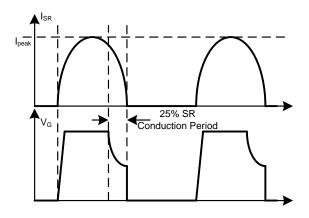

Figure 12 shows the typical waveform of the LLC on the secondary side. To achieve a fairly high usage of the MOSFET's  $R_{DS(ON)}$ , it is expected that the MOSFET driver voltage is kept at the maximum level until the last 25% of the SR conduction period. Calculate  $V_{DS}$  with Equation (2):

$$V_{DS} = -R_{ds(ON)} \cdot \frac{\sqrt{2}}{2} \cdot I_{peak} = -R_{ds(ON)} \cdot I_{OUT} = -V_{fwd} (2)$$

Where  $V_{DS}$  is drain-source voltage of the MOSFET.

The MOSFET's  $R_{DS(ON)}$  is recommended to be no lower than  $\sim V_{fwd}/I_{OUT}$  (m $\Omega$ ). For example, in a 10A application with  $V_{fwd}$  at 45mV, the  $R_{DS(ON)}$  of the MOSFET is recommended to be no lower than  $4.5 m\Omega$ .

Figure 12: Synchronous Rectification Typical Waveform in LLC

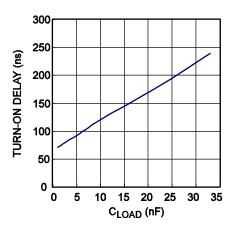

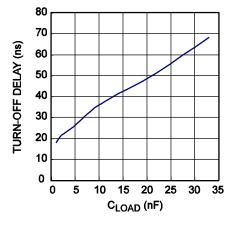

$Q_g$  of the MOSFET affects the turn-on and turn-off delay. Figure 3 indicates the turn-on delay ( $t_{Don}$ ) and the turn-off delay ( $t_{Doff}$ ).  $t_{Don}$  indicates how long the body diode conducts before the MOSFET is turned on, while  $t_{Doff}$  indicates how long the driver takes to turn off the MOSFET. With a higher turn-on delay, the body diode conduction duration of the MOSFET is longer, which brings down the total efficiency. However, with a higher turn-off delay, the shoot-through risk is higher in CCM operation.

Figure 13 and Figure 14 show the  $t_{\text{Don}}$  and  $t_{\text{Doff}}$  of the MP6924, MP6924A according to different  $C_{\text{load}}$  values.

### Turn-On Delay vs. CLOAD

Figure 13: Turn-On Delay vs. C<sub>load</sub> **Turn-Off Delay vs. C<sub>LOAD</sub>**

Figure 14: Turn-Off Delay vs. Cload

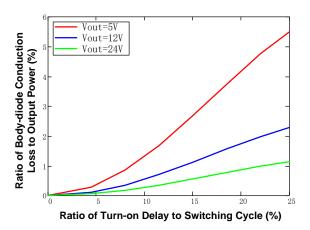

Figure 15: Turn-On Delay Effect on Efficiency

Figure 15 shows how  $t_{Don}$  affects system efficiency. During  $t_{Don}$ , the body diode of the SR MOSFET conducts, which leads to a power loss that can be calculated with Equation (3):

$$P_{on} \approx \frac{V_{F} \cdot I_{F}}{2} \cdot 2f_{s} \cdot t_{Don} = V_{F} \cdot I_{F} \cdot f_{s} \cdot t_{Don}$$

(3)

Where  $V_F$  is the body diode forward voltage drop,  $I_F$  is the switching current when the turnon delay ( $t_{Don}$ ) has ended, and  $f_s$  is the switching frequency.

When considering the switching current as a complete sine wave,  $I_F$  can be estimated with Equation (4) and Equation (5):

$$I_{F} = I_{\text{peak}} \cdot \sin(2 \cdot f_{s} \cdot t_{\text{Don}} \cdot \pi) \tag{4}$$

$$I_{\text{peak}} \approx \frac{\pi}{2} \cdot I_{\text{out}}$$

(5)

Where  $I_{\text{peak}}$  is the peak switching current through the MOSFET, and  $I_{\text{out}}$  is the system output current.

When plugging the values from Equation (4) and Equation (5) into Equation (3), the turn-on delay power loss through the SR MOSFET's body diode can be derived with Equation (6):

$$P_{on} = \frac{\pi}{2} \cdot I_{out} \cdot V_F \cdot f_s \cdot t_{Don} \cdot \sin(2 \cdot f_s \cdot t_{Don} \cdot \pi)$$

(6)

Figure 16 shows how different turn-on delay values affect efficiency according to different output voltages. To keep the body diode conduction loss at a fairly low level (below 0.5% of the output power), the turn-on delay is recommended to be less than 5% of the switching cycle. For example, in a  $f_{sw} = 200 \text{kHz}$  LLC system, the switching cycle is ~5 $\mu$ s, and it is recommended to select the MOSFET to make  $t_{Don} < 250 \text{ns}$ .

Figure 16: Turn-On Delay vs. Power Loss

The turn-off delay ( $t_{Doff}$ ) is critical in some fast transient CCM applications. Choose the MOSFET to make  $t_{Doff}$  below the CCM current transient duration. Otherwise, the MOSFET may need to be selected with a lower  $Q_g$ , or an external totem pole driver circuit may be added to prevent shoot-through.