Intelli-Phase Solution (Integrated HS/LS FETs and Driver) in 4x6mm TQFN

# The Future of Analog IC Technology

NOT RECOMMENDED FOR NEW DESIGNS. REFER TO MP86905

### DESCRIPTION

The MP86885 is a monolithic half-bridge with built-in internal power MOSFETs and gate drivers. It achieves 40A of continuous output current over a wide input supply range.

Integration of the driver and MOSFETS results in high efficiency due to optimal dead time control and parasitic inductance reduction.

The MP86885 is a Monolithic IC approach to drive up to 40A per phase. This very small 4mm x 6mm FC-TQFN device can operate from 100kHz to 1MHz.

This device works with tri-state output controllers. It also comes with a general-purpose current sense and temperature sense.

The MP86885 is ideal for server applications where efficiency and small size are a premium.

### **FEATURES**

®

- Wide 4.5V to 14V Operating Input Range

- Simple Logic Interface

- 40A Output Current

- Accepts Tri-State PWM Signal

- Built-In Switch for bootstrap

- Current Sense

- Temperature Sense (10mV/°C)

- Current Limit Protection

- Used for Multi-Phase Operation

- Fault Reporting

- Available in 4mm x 6mm FC-TQFN

Package

- RoHS 6 Compliant

### APPLICATIONS

- Server/Workstation/Desktop Core Voltage

- Graphic Card Core Regulators

- Power Modules

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

Intelli-Phase is Trademark of Monolithic Power Systems, Inc.

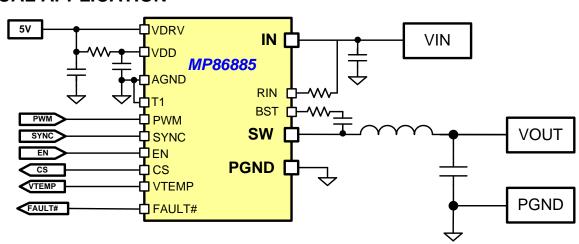

### TYPICAL APPLICATION

### ORDERING INFORMATION

| ſ | Part Number* | Package            | Top Marking |  |

|---|--------------|--------------------|-------------|--|

|   | MP86885GQWT  | FC-TQFN-29 4x6(mm) | M86885      |  |

\* For Tape & Reel, add suffix -Z (e.g. MP86885GQWT-Z).

## PACKAGE REFERENCE

### ABSOLUTE MAXIMUM RATINGS (1)

| Supply Voltage V <sub>IN</sub> | 16V                                    |

|--------------------------------|----------------------------------------|

| V <sub>SW (DC)</sub>           | 1 V to 16V                             |

| V <sub>SW (25ns)</sub>         | 3V to 23V                              |

| V <sub>BST</sub>               | V <sub>SW</sub> + 6V                   |

| All Other Pins                 | 0.3V to +6V                            |

| Instantaneous Current          | 65A                                    |

| Continuous Power Dissipation   | (T <sub>A</sub> =+25°C) <sup>(2)</sup> |

|                                | 3.5 W                                  |

| Junction Temperature           | 150°C                                  |

| Lead Temperature               | 260°C                                  |

| Storage Temperature            | 65°C to +150°C                         |

Recommended Operating Conditions <sup>(3)</sup> Supply Voltage V<sub>IN</sub>...... 4.5V to 14V Driver Voltage V<sub>DRV</sub>...... 4.5V to 5.5V Logic Voltage V<sub>DD</sub> ...... 4.5V to 5.5V Operating Junction Temp. (T<sub>J</sub>). -40°C to +125°C

#### Thermal Resistance <sup>(4)</sup> θ.ιΔ θια

#### Notes:

- Exceeding these ratings may damage the device. 1)

- The maximum allowable power dissipation is a function of the 2) maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its 3) operating conditions.

- Measured on JESD51-7, 4-layer PCB. 4)

### **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 12V$ ,  $V_{DRV}=V_{DD}=5V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

| Parameters                                                 | Symbol           | Condition                                            | Min  | Тур  | Max  | Units |

|------------------------------------------------------------|------------------|------------------------------------------------------|------|------|------|-------|

| I <sub>IN</sub> Shutdown                                   |                  | Vdrv=Vdd=0V                                          | 25   | 65   | 100  | μA    |

| I <sub>IN</sub> Standby                                    | IN Standby       | V <sub>DRV</sub> =V <sub>DD</sub> =5V,<br>PWM=EN=Low | 30   | 55   | 60   | μA    |

| V <sub>IN</sub> Under Voltage Lockout Threshold Rising     |                  |                                                      | 3.4  | 4    | 4.5  | V     |

| V <sub>IN</sub> Under Voltage Lockout Threshold Hysteresis |                  |                                                      |      | 340  |      | mV    |

| IDRV Quiescent Current                                     | DRV Quiescent    | PWM=Low                                              |      | 1    |      | mA    |

| IDRV Shutdown Current                                      | DRV Shutdown     |                                                      | 200  | 230  | 260  | μA    |

| IDD Quiescent Current                                      | DD Quiescent     | PWM=Low                                              | 1.5  | 2.3  | 3    | mA    |

| IDD Shutdown Current                                       | DD Shutdown      |                                                      | 30   | 46   | 60   | μA    |

| VDD Voltage UVLO Rising                                    |                  |                                                      | 3.3  | 3.9  | 4.4  | V     |

| VDD Voltage UVLO Hysteresis                                |                  |                                                      |      | 300  |      | mV    |

| High Side Current Limit <sup>(5)</sup>                     | I <sub>LIM</sub> |                                                      |      | 60   |      | А     |

| Low Side Current Limit <sup>(5)</sup>                      |                  |                                                      |      | -25  |      | A     |

| EN Input Low Voltage                                       |                  |                                                      |      |      | 0.4  | V     |

| EN Input High Voltage                                      |                  |                                                      | 2    |      |      | V     |

| Dead-Time Rising <sup>(5)</sup>                            |                  |                                                      |      | 3    |      | ns    |

| Dead-Time Falling <sup>(5)</sup>                           |                  |                                                      |      | 8    |      | ns    |

| SYNC Current                                               | ISYNC            | V <sub>SYNC</sub> =0V                                | -50  |      | -43  | μA    |

| SYNC Logic High Voltage                                    |                  |                                                      | 2    |      |      | V     |

| SYNC Logic Low Voltage                                     |                  |                                                      |      |      | 0.4  | V     |

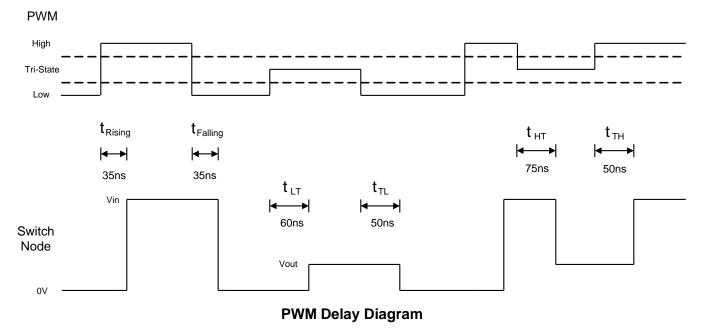

| PWM High to SW Rising Delay <sup>(5)</sup>                 |                  |                                                      |      | 35   |      | ns    |

| PWM Low to SW Falling Delay <sup>(5)</sup>                 |                  |                                                      |      | 35   |      | ns    |

|                                                            | t∟⊤              |                                                      |      | 60   |      | ns    |

| PWM Tristate to SW Hi-Z Delay <sup>(5)</sup>               | t⊤∟              |                                                      |      | 50   |      |       |

|                                                            | t <sub>HT</sub>  |                                                      |      | 75   |      |       |

|                                                            | t <sub>тн</sub>  |                                                      |      | 50   |      |       |

| Minimum PWM Pulse Width <sup>(5)</sup>                     |                  |                                                      |      | 30   |      | ns    |

| PWM Input Current                                          | IPWM             | $V_{PWM}=3.3V, V_{EN}=5V$                            | 80   |      | 100  | μA    |

| •                                                          |                  | $V_{PWM}=0V, V_{EN}=5V$                              | -100 | -90  | -80  | μA    |

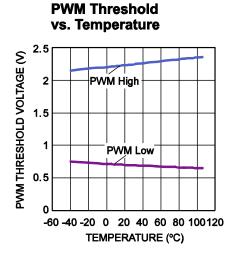

| PWM Logic High Voltage                                     |                  |                                                      | 2.45 |      |      | V     |

| PWM Tristate Region                                        |                  |                                                      | 1.1  |      | 2.0  | V     |

| PWM Logic Low Voltage                                      |                  |                                                      |      |      | 0.50 | V     |

| Current Sense Accuracy <sup>(5)</sup>                      |                  | I <sub>ОUT</sub> =15А                                | -4   |      | +4   | %     |

| Current Sense Gain                                         |                  |                                                      |      | 10   |      | μΑ/Α  |

| Current Sense Common-Mode Voltage Range                    |                  |                                                      | 1    |      | 3.5  | V     |

| Temperature Sense Gain <sup>(5), (6)</sup>                 |                  |                                                      |      | 10   |      | mV/°C |

| Temperature Sense Offset <sup>(5), (6)</sup>               |                  |                                                      |      | -100 |      | mV    |

| Temperature Sense Accuracy <sup>(5)</sup>                  |                  |                                                      |      | ±5   |      | °C    |

| VTEMP Pull-Down Current                                    |                  | VTEMP=VDD                                            |      | 160  |      | μA    |

| Over Temperature Protection <sup>(5)</sup>                 |                  |                                                      |      | 170  |      | °C    |

Notes:

5) Guaranteed by design, not tested in production. The parameter is tested during parameter characterization.

6) See "Junction Temperature Sense" section for details.

MP86885 – INTELLI-PHASE SOLUTION IN 4x6mm TQFN

NOT RECOMMENDED FOR NEW DESIGNS. REFER TO MP86905

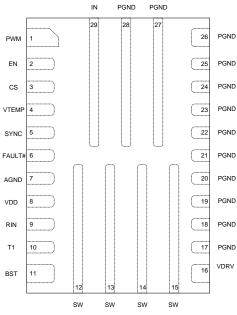

### **PIN FUNCTIONS**

| Pin # | Name   | Description                                                                                                                                                                                                         |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | PWM    | Pulse Width Modulation. Leave PWM floating or drive to mid-state to put SW in high impedance state.                                                                                                                 |

| 2     | EN     | On/Off Control. Pull low to place SW in a high impedance state.                                                                                                                                                     |

| 3     | CS     | Current Sense Output. Requires an external resistor.                                                                                                                                                                |

| 4     | VTEMP  | Single pin temperature sense output.                                                                                                                                                                                |

| 5     | SYNC   | Synchronous Low Switch. Leave open or pull high to enable. Pull low to enter diode emulation mode.                                                                                                                  |

| 6     | FAULT# | Fault reporting on HS current limit, Over Temperature and VDD UVLO. It is an open-<br>drain output during normal operation and pull-low when fault occurred. Low side<br>current limit will not pull low fault pin. |

| 7     | AGND   | Analog Ground.                                                                                                                                                                                                      |

| 8     | VDD    | Internal Circuitry Voltage. Connect to VDRV thru $2.2\Omega$ resistor and decouple with 1µF capacitor to AGND. Connect AGND and PGND at this point.                                                                 |

| 9     | RIN    | Current Sense Compensation. Connect a resistor from this pin to Vin to fine tune current sense gain.                                                                                                                |

| 10    | T1     | Test pin. Connect to ground.                                                                                                                                                                                        |

| 11    | BST    | Bootstrap. Requires a $0.22\mu$ F to $1\mu$ F capacitor to drive the power switch's gate above the supply voltage. Connects between SW and BST pins to form a floating supply across the power switch driver.       |

| 12-15 | SW     | Switch Output.                                                                                                                                                                                                      |

| 16    | VDRV   | Driver Voltage. Connect to 5V supply and decouple with $1\mu F$ to $4.7\mu F$ ceramic capacitor.                                                                                                                    |

| 17-28 | PGND   | Power Ground.                                                                                                                                                                                                       |

| 29    | IN     | Supply Voltage. Place $C_{IN}$ close to the device to prevent large voltage spikes at the input.                                                                                                                    |

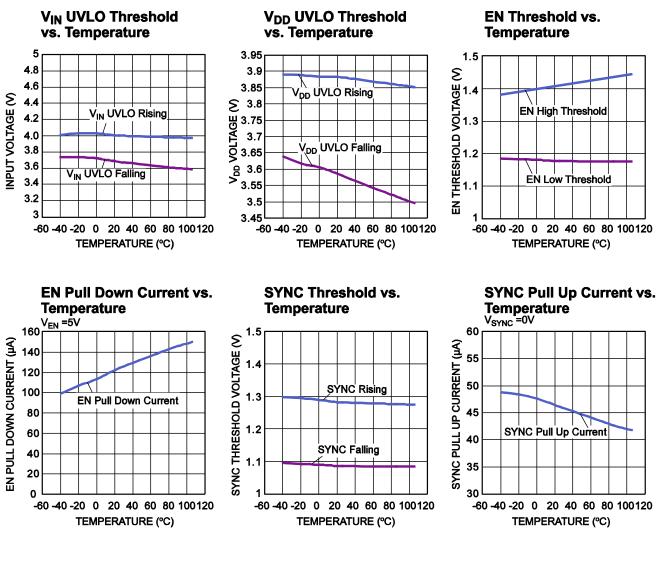

### **TYPICAL CHARACTERISTICS**

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

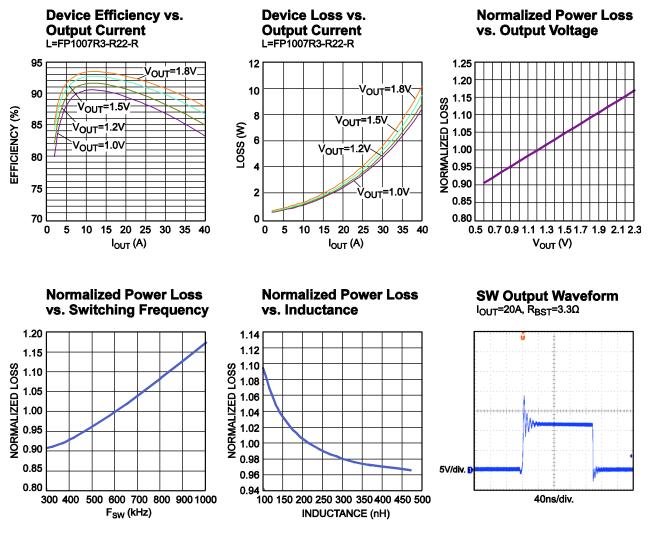

### **TYPICAL PERFORMANCE CHARACTERISTICS**

V<sub>IN</sub>=12V, V<sub>DRV</sub>=V<sub>DD</sub>=5V, V<sub>OUT</sub>=1.2V, L=215nH, F<sub>SW</sub>=600kHz, T<sub>A</sub>=25°C, no droop, unless otherwise noted.

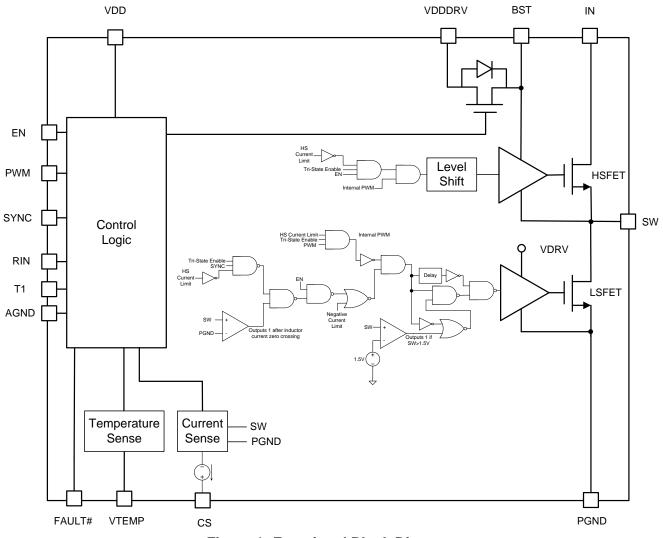

### **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

### **OPERATION**

The MP86885 is a 40A monolithic half-bridge driver with MOSFETs ideally suited for multiphase buck regulators.

When the EN transitions from low to high and both  $V_{DD}$  and  $V_{BST}$  signals are sufficiently high, operation begins. It is recommended to use EN pin to startup and shutdown the Intelli-Phase.

To put SW node in a high impedance state, let PWM pin float or drive PWM pin to mid-state. Drive the SYNC pin low to enter diode emulation mode. In diode emulation mode, the LSFET is off after inductor current crossed zero current.

When HSFET over current is detected, the part will latch off. Recycling VIN/VDD or toggling EN will release the latch and restart the device. When the LSFET detects -25A current, the part will turn off the LSFET for that cycle.

#### **Current Sense**

The CS pin is a bi-directional current source proportional to the inductor current. Use the following equations to select the RIN resistance to connect between RIN pin and IN pin:

$$\begin{split} R_{\text{IN}} &= -7.55 \times I_{\text{L}_{\text{RIPPLE}}} + 170 (k\Omega) \\ I_{\text{L}_{\text{RIPPLE}}} &= \frac{t_{\text{ON}} \times (V_{\text{IN}} - V_{\text{OUT}})}{L} = \frac{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{IN}} \times F_{\text{SW}} \times L} \end{split}$$

Where  $I_{L\_RIPPLE}$  is the peak to peak inductor ripple current. For example, if the ripple current is 10A, then the calculated  $R_{IN}$  is 94.5k $\Omega$  and 95.3k $\Omega$  (the closest 1% resistor value) should be selected for  $R_{IN}$ .

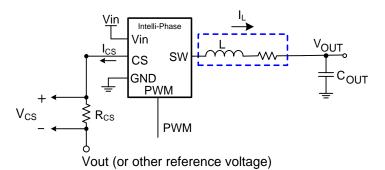

The current sense gain is  $10\mu$ A/A. In general, there is a resistor, R<sub>CS</sub>, connected from CS pin and V<sub>OUT</sub> or an external voltage which is capable to sink small current to provide enough voltage shift to meet the operating voltage on CS pin.

The CS voltage range of 1V to 3.5V is required to keep CS's output current linearly proportional to inductor current. Use the following equations to determine a proper reference voltage and/or  $R_{CS}$  value:

$$1V < I_{CS} \times R_{CS} + V_{REF} < 3.5V$$

$$I_{CS} = I_{L} \times 10 \times 10^{-6}$$

Intelli-Phase's current sense output can be used by controller to accurately monitor the output current. The cycle-by-cycle current information from CS pin can be used for phase current balancing, over current protection and active voltage positioning (output voltage droop).

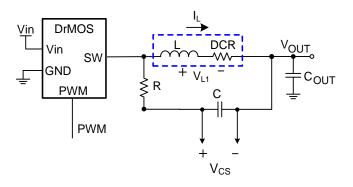

Intelli-Phase's accurate current sense can replace traditional inductor DCR current sensing scheme. In traditional inductor DCR current sense:

$$V_{\text{CS}} = I_{\text{L}} \times R_{\text{DCR}}$$

With Intelli-Phase's CS output, V<sub>CS</sub> becomes:

$$V_{CS} = I_{CS} \times R_{CS} = I_{L} \times R_{CS} \times 10 \times 10^{-6}$$

Where the  $R_{DCR}$  term is replaced with  $R_{CS} \times 10 \times 10^{-6}$ . Figure 2 shows a circuit replacing inductor DCR sensing with Intelli-Phase's CS output. There are several advantages with this current sensing method:

- Since current sensing is done by Intelli-Phase, user can select low DCR inductors and still have large current sense signal by selecting larger R<sub>CS</sub>.

- 2. Tight DCR variation is not required.

- 3. CS signal is independent of impedance matching and inductor temperature.

Inductor DCR Current Sense

#### Intelli-Phase Current Sense

#### Figure 2: Replacing DCR Current Sense with Intelli-Phase's CS Output

#### **Junction Temperature Sense**

The VTEMP pin is a voltage output proportional to the junction temperature. The junction temperature can be calculated from the following equation:

$$T_{JUNCTION} = \frac{\left(V_{TEMP} + 100mV\right)}{\frac{10mV}{^{\circ}C}},$$

for T\_{JUNCTION>10°C

For example, if the VTEMP voltage is 700mV, then the junction temperature of Intelli-Phase is 80°C. VTEMP can not go below 0V, so it will read 0V for junction temperature lower than 10°C.

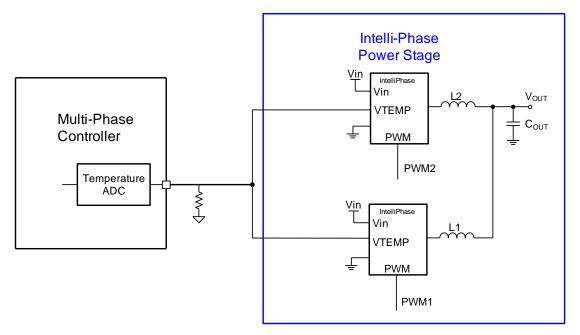

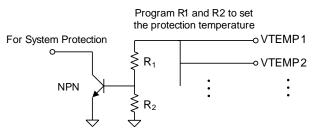

Be sure to measure this voltage between VTEMP and AGND pins for the most accurate reading. In multi-phase operation, the VTEMP pins of every Intelli-Phase can be connected to the temperature monitor pin of the controller. A sample circuitry is shown in Figure 3. VTEMP signals can also be used for system thermal protection as shown in Figure 4.

**Figure 4: System Thermal Protection**

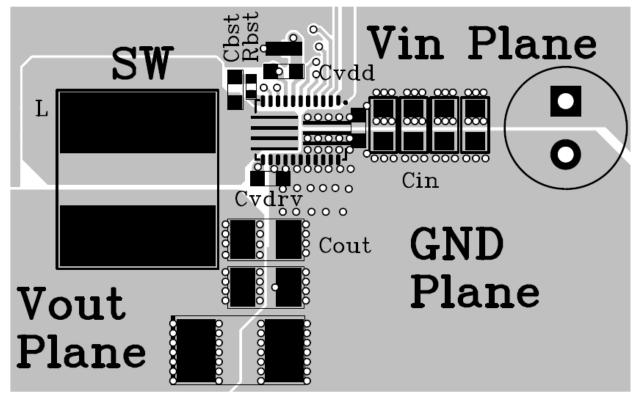

#### **PCB Layout Guide Line**

PCB layout plays an important role to achieve stable operation. For optimal performance, follow these guidelines. The sample layout at the end of these guidelines can be used as a layout reference.

- Always place some input bypass ceramic capacitors next to the device and on the same layer as the device. Do not put all of the input bypass capacitors on the back side of the device. Use as many via and input voltage planes as possible to reduce switching spikes. Place the BST capacitor and the VDRV capacitor as close to the device as possible.

- 2. Place the VDD decoupling capacitor close to the device. Connect AGND and PGND at the point of VDD capacitor's ground connection.

- 3. It is recommended to use  $0.22\mu$ F to  $1\mu$ F bootstrap capacitor and  $3.3\Omega$  bootstrap resistance. Do not use capacitance values below 100nF for the BST capacitor.

- 4. Connect IN, SW and PGND to large copper areas and use via to cool the chip to improve thermal performance and long-term reliability.

- 5. Keep the path of switching current short and minimize the loop area formed by the input capacitor. Keep the connection between the SW pin and the input power ground as short and wide as possible.

Figure 5: Sample PCB Layout

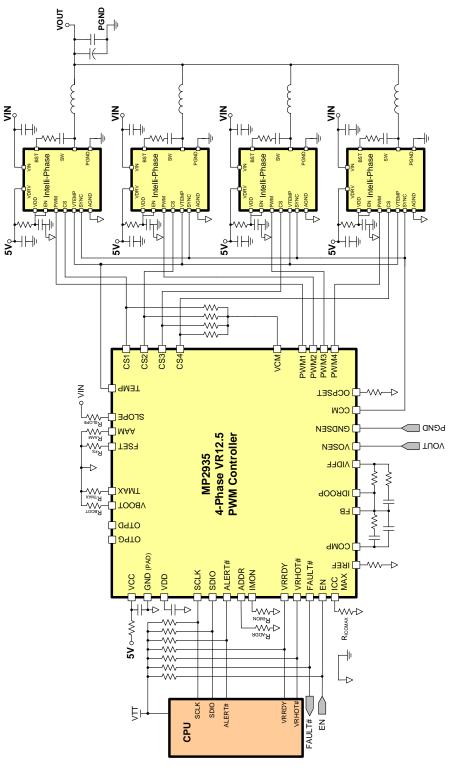

### **TYPICAL APPLICATION CIRCUITS**

Figure 6: MP2935+Intelli-Phase Application Circuit