# 4V-60V Input, Current Mode, Synchronous Step-Down Controller

#### **DESCRIPTION**

The MP9928 is a high-voltage, synchronous step-down switching regulator controller that can directly step down voltages from up to 60V. The MP9928 uses PWM current control architecture with accurate cycle-by-cycle current limiting. It is capable of driving dual N-channel MOSFET switches.

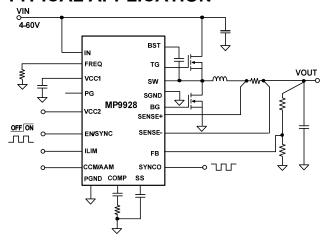

AAM Mode (Advanced asynchronous mode) enables non-synchronous operation and PFM mode to optimize light load efficiency.

The operating frequency of MP9928 can be programmed by an external resistor or synchronized to an external clock for noise-sensitive applications. Fault protections are available including a precision output over voltage protection (OVP), output over current protection (OCP), and thermal shutdown.

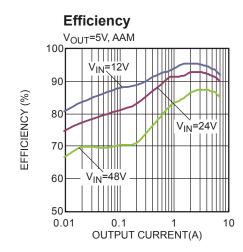

The MP9928 is available in TSSOP20-EP package and QFN-20 (3mmx4mm) package.

#### **FEATURES**

- Wide 4V to 60V Operating Input Range

- Dual N-Channel MOSFET Driver

- Low Dropout Operation: Maximum Duty Cycle at 99.5%

- Programmable Frequency Range: 100kHz 1000kHz

- 180° Out-of-Phase SYNCO

- External Soft-Start and PG Pin

- Selectable Cycle-by-Cycle Current Limit

- Output Over Voltage Protection

- Internal LDO with Externally Power Supply Option

- Programmable CCM and AAM Pulse-Skipping Mode

- Accuracy Over Temperature Protection

- TSSOP20-EP package and QFN-20 (3mmx4mm) Package

# **APPLICATIONS**

- PD Power Supply in PoE System

- USB Dedicated Charging Port (DCP)

- Industrial Control Systems

- Power Supply for Linear Chargers

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under quality assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

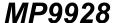

#### TYPICAL APPLICATION

### ORDERING INFORMATION

| Part Number | Package          | Top Marking |

|-------------|------------------|-------------|

| MP9928GF*   | TSSOP-20 EP      | See Below   |

| MP9928GL**  | QFN-20 (3mmx4mm) | See Below   |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. MP9928GF–Z)

# **TOP MARKING (MP9928GF)**

MPSYYWW MP9928 LLLLLLLLL

MP9928: product code of MP9928GF;

MPS: MPS prefix; YY: year code; WW: week code: LLLLLLLL: lot number;

# **TOP MARKING (MP9928GL)**

MPYW 9928 LLL

9928: product code of MP9928GL;

MP: MPS prefix; Y: year code; W: week code: LLL: lot number;

<sup>\*\*</sup> For Tape & Reel, add suffix -Z (e.g. MP9928GL-Z)

### **PACKAGE REFERENCE**

# **ABSOLUTE MAXIMUM RATINGS (1)**

# Recommended Operating Conditions (3)

| Supply voltage (V <sub>IN</sub> )          | 4V to 60V <sup>(4)</sup> |

|--------------------------------------------|--------------------------|

| Output voltage (V <sub>OUT</sub> )         | ≤24V                     |

| Supply voltage for (VCC2)                  | 5V to 12V                |

| Operating junction temp. (T <sub>J</sub> ) | 40°C to +125°C           |

| Thermal Resistance (5) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |       |

|------------------------|-------------------------|-------------------------|-------|

| TSSOP-20 EP            | 40                      | 8                       | .°C/W |

| QFN-20 (3mmx4mm)       | 48                      | 10                      | .°C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

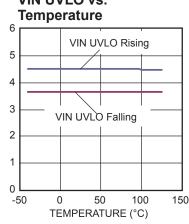

- UVLO\_rising is 5V but UVLO\_falling is lower than 4V, so input must be >5V for startup, and after start up MP9928 can work down to 4V input voltage.

- 5) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 24V,  $T_J$  = -40°C to 125°C, EN = 2V,  $V_{ILIMIT}$  = 75mV, unless otherwise noted.

| Parameters                                          | Symbol                   | Condition                                                                           | Min   | Тур   | Max   | Units |

|-----------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Input Supply                                        |                          |                                                                                     |       |       |       |       |

| V <sub>IN</sub> UVLO threshold (rising)             | INuv_rising              |                                                                                     |       | 4.5   | 5     | V     |

| V <sub>IN</sub> UVLO threshold (falling)            | IN <sub>UV_FALLING</sub> |                                                                                     |       | 3.7   | 3.95  | V     |

| V <sub>IN</sub> UVLO hysteresis                     | IN <sub>UV_HYS</sub>     |                                                                                     |       | 800   |       | mV    |

| V <sub>IN</sub> supply current with VCC2 bias       | IQ_VCC2                  | VCC2 = 12V, external bias                                                           |       | 25    | 40    | μΑ    |

| $V_{\text{IN}}$ supply current without VCC2 bias    | lα                       | VCC2 = 0, V <sub>FB</sub> = 0.84V, V <sub>AAM</sub> = 5V,<br>SENSE+ = SENSE- = 0.3V |       | 750   | 1000  | μA    |

| V <sub>IN</sub> AAM current                         | IQ_AAM                   | V <sub>AAM</sub> =0.6V, V <sub>FB</sub> =0.84V,<br>SENSE+ = SENSE- = 0.3V           |       | 250   | 350   | μA    |

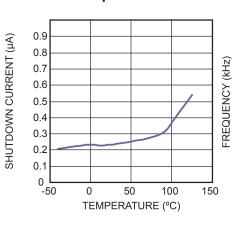

| V <sub>IN</sub> shutdown current                    | Ishdn                    | V <sub>EN</sub> = 0V                                                                |       | 0.5   | 3     | μΑ    |

| Vcc Regulator                                       |                          |                                                                                     |       |       |       |       |

| VCC1 regulator output voltage from V <sub>IN</sub>  | VCC1_vin                 | VIN > 6V                                                                            |       | 5     |       | ٧     |

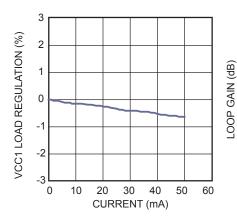

| VCC1 regulator load regulation from $V_{\text{IN}}$ |                          | Load = 0 to 50mA,<br>VCC2 floating or connects to GND                               |       | 1     | 3     | %     |

| VCC1 regulator output voltage from VCC2             | VCC1_ <sub>VCC2</sub>    | VCC2 > 6V                                                                           |       | 5     |       | V     |

| VCC1 regulator load regulation from VCC2            |                          | Load = 0 to 50mA, VCC2 = 12V                                                        |       | 1     | 3     | %     |

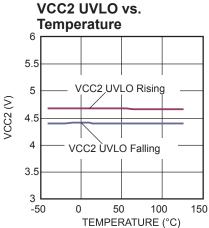

| VCC2 UVLO threshold (rising)                        | VCC2_RISING              |                                                                                     |       | 4.7   | 4.92  | V     |

| VCC2 UVLO threshold (falling)                       | VCC2_FALLING             |                                                                                     |       | 4.45  |       | V     |

| VCC2 threshold hysteresis                           | VCC2_ <sub>HYS</sub>     |                                                                                     |       | 250   |       | mV    |

| VCC2 supply current                                 | I <sub>VCC2</sub>        | V <sub>AAM</sub> = 5V, V <sub>FB</sub> = 0.84V,<br>VCC2 = 12V                       |       | 800   | 1200  | μΑ    |

| VOOZ Supply Suffern                                 | 10002                    | V <sub>AAM</sub> = 0.6V,<br>V <sub>FB</sub> = 0.84V, VCC2 = 12V                     |       | 200   | 300   | μA    |

| Feedback (FB)                                       |                          |                                                                                     |       |       |       |       |

| Feedback voltage                                    | $V_{FB}$                 | $4V \leq V_{IN} \leq 60V,  T_J \text{=} 25^{\circ}C$                                | 0.792 | 0.800 | 0.808 | V     |

|                                                     |                          | $4V \le V_{IN} \le 60V$ , $T_J$ =- $40^{\circ}C$ to $125^{\circ}C$                  | 0.788 | 0.800 | 0.812 | V     |

| Feedback current                                    | I <sub>FB</sub>          | V <sub>FB</sub> = 0.84V                                                             |       | 10    |       | nA    |

| Enable (EN)                                         |                          |                                                                                     |       |       |       |       |

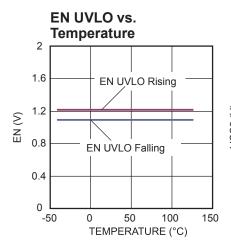

| Enable threshold (rising)                           | VEN_RISING               |                                                                                     | 1.16  | 1.22  | 1.28  | V     |

| Enable threshold (falling)                          | Ven_falling              |                                                                                     | 1.03  | 1.09  | 1.15  | V     |

| Enable threshold hysteresis                         | V <sub>EN_TH</sub>       |                                                                                     |       | 130   |       | mV    |

| EN input current                                    | I <sub>EN</sub>          | V <sub>EN</sub> = 2V                                                                |       | 2     |       | μA    |

| Enable turn-off delay                               | T <sub>OFF</sub>         |                                                                                     | 10    | 15    |       | μs    |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{\text{IN}}$  = 24V,  $T_{\text{J}}$  = -40°C to 125°C, EN = 2V,  $V_{\text{ILIMIT}}$  = 75mV, unless otherwise noted.

| Parameters                                 | Symbol                  | Condition                                            | Min  | Тур        | Max  | Units           |

|--------------------------------------------|-------------------------|------------------------------------------------------|------|------------|------|-----------------|

| Oscillator and Sync                        |                         |                                                      |      |            |      |                 |

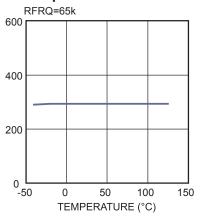

| Operating frequency                        | Fsw                     | $R_{Freq} = 65k\Omega$                               | 240  | 300        | 360  | kHz             |

| Foldback operating frequency               | Fsw_foldback            | V <sub>FB</sub> = 0.1V                               |      | 50%        |      | Fsw             |

| Maximum programmable frequency             | Fswн                    |                                                      | 1000 |            |      | kHz             |

| Minimum programmable frequency             | FswL                    |                                                      |      |            | 100  | kHz             |

| Sync/EN frequency range                    | Fsync                   |                                                      | 100  |            | 1000 | kHz             |

| Sync/EN voltage rising threshold           | VSYNC_RISING            |                                                      | 2    |            |      | V               |

| Sync/EN voltage falling threshold          | VSYNC_FALLING           |                                                      |      |            | 0.35 | V               |

| Current Sense                              |                         |                                                      |      |            |      |                 |

| Current sense common mode voltage range    | Vsense+/-               |                                                      | 0    |            | 24   | V               |

|                                            |                         | I <sub>LIM</sub> = GND, V <sub>SENSE+</sub> = 3.3V   | 15   | 25         | 35   | mV              |

| Current limit sense voltage                | VILIMIT                 | I <sub>LIM</sub> = VCC1, V <sub>SENSE+</sub> = 3.3V  | 40   | 50         | 60   | mV              |

|                                            |                         | I <sub>LIM</sub> = FLOAT, V <sub>SENSE+</sub> = 3.3V | 65   | 75         | 85   | mV              |

| Reverse current limit sense                |                         | I <sub>LIM</sub> = GND, V <sub>SENSE+</sub> = 3.3V   |      | 8          |      | mV              |

| voltage                                    | V <sub>REV_ILIMIT</sub> | I <sub>LIM</sub> = VCC1, V <sub>SENSE+</sub> = 3.3V  |      | 17         |      |                 |

|                                            |                         | I <sub>LIM</sub> = FLOAT, V <sub>SENSE+</sub> = 3.3V |      | 24         |      |                 |

|                                            | Vval_ilimit             | I <sub>LIM</sub> = GND, V <sub>SENSE+</sub> = 3.3V   |      | 22.5       |      | mV              |

| Valley current limit                       |                         | I <sub>LIM</sub> = VCC1, V <sub>SENSE+</sub> = 3.3V  |      | 47.5       |      |                 |

|                                            |                         | I <sub>LIM</sub> = FLOAT, V <sub>SENSE+</sub> = 3.3V |      | 72.5       |      |                 |

| Input current of concer                    | 1                       | $V_{SENSE+/-(CM)} = 0V$                              |      | -45<br>115 |      | μΑ              |

| Input current of sensor                    | I <sub>SENSE</sub>      | $V_{SENSE+/-(CM)} = 3.3V$ $V_{SENSE+/-(CM)} > 5V$    |      | 150        |      | μA<br>μA        |

| Soft Start (SS)                            |                         | V SENSET/-(CIVI)                                     |      | 100        |      | μπ              |

| Soft-start source current                  | Iss                     | SS = 0.5V                                            | 2    | 4          | 6    | μA              |

| Error Amplifier                            |                         |                                                      |      |            |      |                 |

| Error amp transconductance                 | G <sub>m</sub>          | ∆ V = 5mV                                            |      | 500        |      | μA/V            |

| Error amp open loop DC gain <sup>(6)</sup> | Ao                      |                                                      |      | 70         |      | dB              |

| Error amp sink/source current              | I <sub>EA</sub>         | FB = 0.7/0.9V                                        |      | ±30        |      | μA              |

| Protection                                 |                         |                                                      |      |            |      |                 |

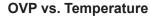

| Over-voltage threshold                     | Vov                     |                                                      | 110% | 115%       | 120% | V <sub>FB</sub> |

| Over-voltage hysteresis                    | Vov_HYS                 |                                                      |      | 10%        |      | V <sub>FB</sub> |

| Thermal shutdown <sup>(7)</sup>            |                         |                                                      |      | 170        |      | °C              |

| Thermal shutdown hysteresis <sup>(7)</sup> |                         |                                                      |      | 20         |      | °C              |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 24V,  $T_J$  = -40°C to 125°C, EN = 2V,  $V_{ILIMIT}$  = 75mV, unless otherwise noted.

| Parameters                         | Symbol                    | Condition                  | Min         | Тур         | Max             | Units           |

|------------------------------------|---------------------------|----------------------------|-------------|-------------|-----------------|-----------------|

| Gate Driver                        |                           |                            |             |             |                 |                 |

| TG pull-up resistor                | RTG_PULLUP                | Source 20mA                |             | 2           |                 | Ω               |

| TG pull-down resistor              | RTG_PULLDN                | Sink 20mA                  |             | 1           |                 | Ω               |

| BG pull-up resistor                | R <sub>BG</sub> _PULLUP   | Source 20mA                |             | 3           |                 | Ω               |

| BG pull-down resistor              | R <sub>BG</sub> _PULLDN   | Sink 20mA                  |             | 1           |                 | Ω               |

| Dead time                          | T <sub>Dead</sub>         | C <sub>Load</sub> = 3.3nF  |             | 60          |                 | ns              |

| TG maximum duty cycle              | D <sub>max</sub>          | V <sub>FB</sub> = 0.7V     | 98          | 99.5        |                 | %               |

| TG minimum on time <sup>(7)</sup>  | Ton_min_tg                |                            |             | 92          |                 | ns              |

| BG minimum on time                 | Ton_min_bg                |                            |             | 175         | 250             | ns              |

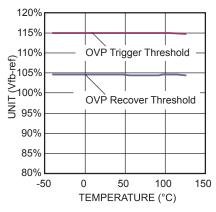

| Power Good                         |                           |                            |             |             |                 |                 |

| Power good low                     | V <sub>PG_Low</sub>       | I <sub>SINK</sub> = 4mA    |             | 0.1         | 0.3             | V               |

| PG rising threshold                | PGvth_RSING               | Vout rising Vout falling   | 85%<br>101% | 90%<br>107% | 96.5%<br>112.5% | V <sub>FB</sub> |

| PG falling threshold               | PG <sub>Vth_FALLING</sub> | Vout falling Vout rising   | 81%<br>105% | 87%<br>110% | 92.5%<br>116.5% | V <sub>FB</sub> |

| PG threshold hysteresis            | PGvth_HYS                 |                            |             | 3%          |                 | V <sub>FB</sub> |

| Power good leakage                 | I <sub>PG_LK</sub>        | PG = 5V                    |             |             | 2               | μΑ              |

| Power good delay                   | T <sub>PG_delay</sub>     | PG rising and falling      |             | 25          |                 | μs              |

| AAM/CCM                            |                           |                            | •           |             | 1               | •               |

| AAM output current                 | Іаам                      | $R_{Freq}$ = 65 k $\Omega$ |             | 9.2         |                 | μA              |

| CCM required AAM threshold voltage | V <sub>ССМ_ТН</sub>       |                            | 2.3         |             |                 | V               |

#### NOTES:

<sup>6)</sup> Guaranteed by design, not tested.7) Guaranteed by characterization, not production tested.

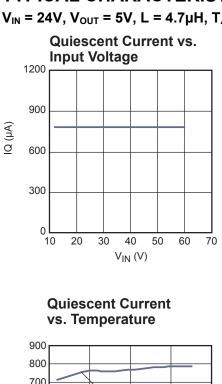

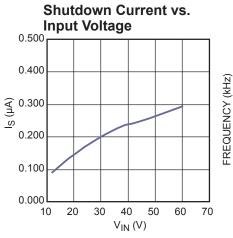

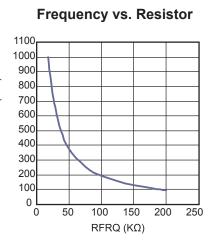

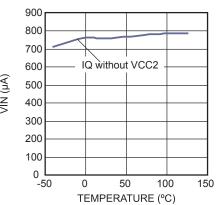

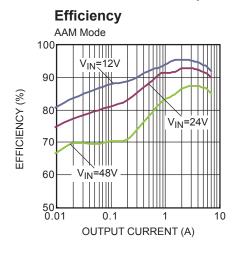

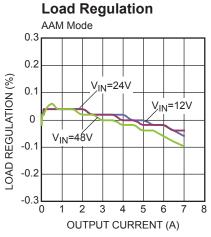

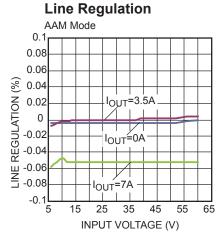

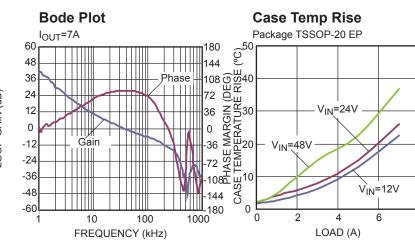

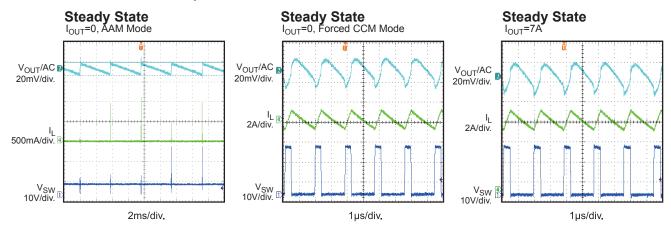

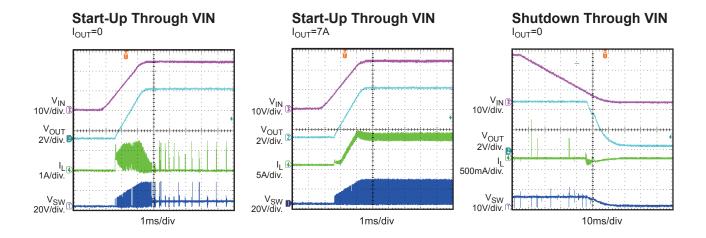

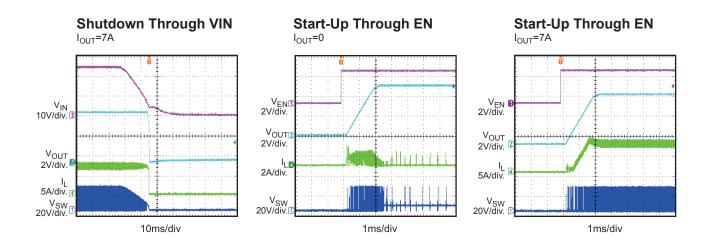

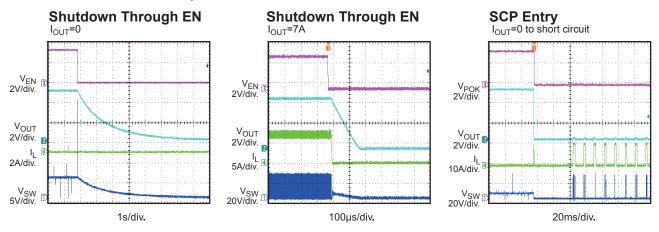

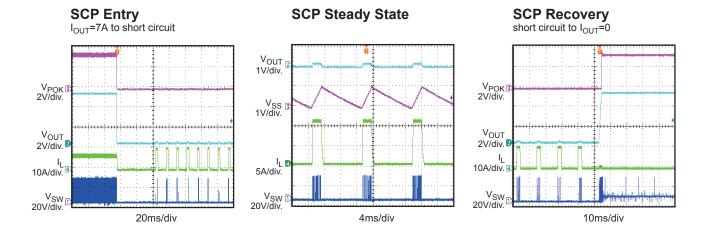

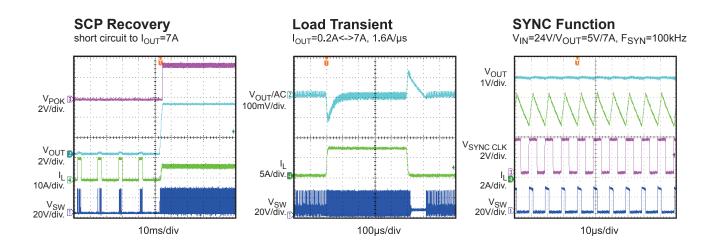

# TYPICAL CHARACTERISTICS

$V_{IN}$  = 24V,  $V_{OUT}$  = 5V, L = 4.7 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

**Shutdown Current** vs. Temperature

Frequency vs. **Temperature**

VIN UVLO vs.

# TYPICAL CHARACTERISTICS (continued)

$V_{IN}$  = 24V,  $V_{OUT}$  = 5V, L = 4.7 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

PG Threshold vs.

Temperature

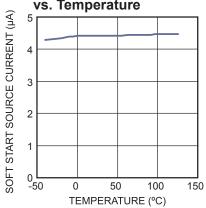

Soft Start Source Current vs. Temperature

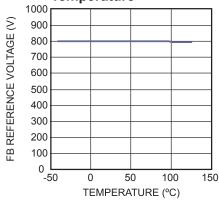

FB Reference Voltage vs. Temperature

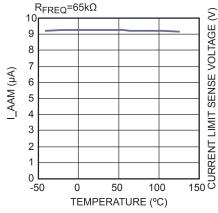

I\_AAM vs. Temperature

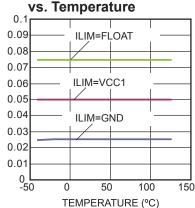

Internal Current Limit

$V_{IN}$  = 24V,  $V_{OUT}$  = 5V, L = 4.7 $\mu$ H,  $T_A$  = +25°C, unless otherwise noted.

$V_{IN}$  = 24V,  $V_{OUT}$  = 5V, L = 4.7 $\mu$ H, AAM Mode,  $T_A$  = +25°C, unless otherwise noted.

$V_{IN}$  = 24V,  $V_{OUT}$  = 5V, L = 4.7 $\mu$ H, AAM mode,  $T_A$  = +25°C, unless otherwise noted.

$V_{IN}$  = 24V,  $V_{OUT}$  = 5V, L = 4.7 $\mu$ H, AAM Mode,  $T_A$  = +25°C, unless otherwise noted.

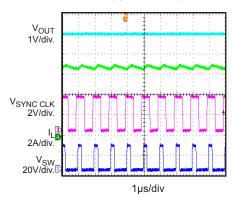

#### **SYNC Function**

V<sub>IN</sub>=24V/V<sub>OUT</sub>=5V/7A, F<sub>SYN</sub>=1MHz

# **PIN FUNCTIONS**

| TSSOP<br>Pin # | QFN<br>Pin# | Name    | Description                                                                                                                                                                                                                                                                                                            |

|----------------|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 19          | IN      | Input supply. The MP9928 operates from a 4V to 60V input. Ceramic capacitor is needed to prevent large voltage spikes from appearing at the input.                                                                                                                                                                     |

| 2              | 20          | EN/SYNC | Enable input. The threshold is 1.22V with 130mV of hysteresis, and it is used to implement an input under voltage lockout (UVLO) function externally. If an external sync clock is applied to this pin, internal clock will follow the sync frequency.                                                                 |

| 3              | 1           | VCC2    | External power supply for the internal VCC1 regulator. It will disable the power from $V_{\text{IN}}$ as long as VCC2 is higher than 4.7V. Do not connect >12V power supply to this pin. Connecting VCC2 pin to external power supply will reduce power dissipation and thus increases efficiency.                     |

| 4              | 2           | VCC1    | Internal bias supply. Decouple with a 1 $\mu$ F ceramic capacitor or greater ceramic capacitor. But the capacitance should be no more than 4.7 $\mu$ F.                                                                                                                                                                |

| 5              | 3           | SGND    | Low noise signal ground reference.                                                                                                                                                                                                                                                                                     |

| 6              | 4           | SS      | Soft-start control input. This pin is used to program the soft-start period with an external capacitor between SS to SGND.                                                                                                                                                                                             |

| 7              | 5           | COMP    | COMP is used to compensate the regulation control loop. Connect an RC network from COMP to GND to compensate for the regulation control loop.                                                                                                                                                                          |

| 8              | 6           | FB      | Feedback. This is the input to the error amplifier. An external resistive divider connected between the output and GND is compared to the internal +0.8V reference to set the regulation voltage.                                                                                                                      |

| 9              | 7           | CCM/AAM | Continuous conduction mode/advanced asynchronous mode set pin. Connect this pin to VCC1 pin or float can set the part operates in CCM mode. Connecting an appropriate external resistor from this pin to GND to make AAM at low level, can set the part operates in AAM. The AAM voltage should be no less than 480mV. |

| 10             | 8           | FREQ    | Connect a resistor between FREQ and GND to set the switching frequency.                                                                                                                                                                                                                                                |

| 11             | 9           | PG      | Power good output. The output of this pin is open drain.                                                                                                                                                                                                                                                               |

| 12             | 10          | ILIM    | Current sense voltage limit set. The voltage at this pin sets the nominal sense voltage at maximum output current. There are three fixed options (float, connect to VCC1 or connect to GND.)                                                                                                                           |

| 13             | 11          | SYNCO   | outputs a clock which are 180° out-of-phase with internal Oscillator Clock or external Synchronize Clock when part works in CCM or DCM(but not Sleep mode) for dual channel co-pack. SYNCO outputs DC voltage in other cases(Sleep mode, Low Dropout mode, Fault protections, etc.).                                   |

| 14             | 12          | SENSE-  | Negative input for the current sense. The sensed inductor current limit threshold is determined by status of ILIM pin.                                                                                                                                                                                                 |

| 15             | 13          | SENSE+  | Positive input for the current sense. The sensed inductor current limit threshold is determined by status of ILIM pin.                                                                                                                                                                                                 |

| 16             | 14          | PGND    | Power ground reference for the internal low side switch driver and the VCC1 regulator circuit. Connect this pin directly to the negative terminal of the VCC1 decoupling capacitor.                                                                                                                                    |

# PIN FUNCTIONS (continued)

| TSSOP<br>Pin# | QFN<br>Pin# | Name | Description                                                                                                                                                                                                                                           |

|---------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17            | 15          | BG   | Bottom gate driver output. Connect this pin to the gate of the synchronous N-channel MOSFET.                                                                                                                                                          |

| 18            | 16          | SW   | Switch node. Reference for the $V_{\mbox{\footnotesize{BST}}}$ supply and high current returns for bootstrapped switch.                                                                                                                               |

| 19            | 17          | TG   | Top gate drive. The TG pin drives the gate of the top N-channel MOSFET. The TG driver draws power from the BST capacitor and returns to SW pin, providing a true floating drive to the top N-channel MOSFET.                                          |

| 20            | 18          | BST  | Bootstrap. This pin is the positive power supply for the internal floating high side MOSFET driver. Connect a bypass capacitor between this pin and SW pin.  A diode from VCC1 to this pin charges the BST capacitor when the low side switch is off. |

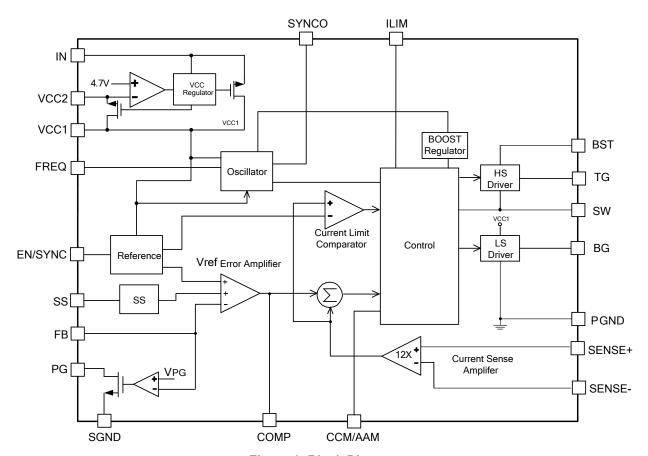

### **BLOCK DIAGRAM**

Figure 1: Block Diagram

#### **OPERATION**

#### Overview

The MP9928 is a high-performance, step down, synchronous DC/DC converter controller IC with a wide input range. It implements current mode, switching frequency programmable control architecture to regulate the output voltage with external N-channel MOSFET switches.

The MP9928 senses the voltage at FB pin. The difference between the voltage on this pin and an internal 0.8V reference is amplified to generate an error voltage on COMP pin which is used as a threshold for the current sense comparator with a slope compensation ramp.

Under normal load condition, the controller operates in full PWM mode. At the beginning of each oscillator cycle, the top gate driver is enabled. Top gate turns on for a period determined by the duty cycle. When the top gate turns off, the bottom gate turns on after a dead time and stays on until the beginning of the next clock cycle.

There is an optional power save mode for light load or no load conditions, and see details in the following section.

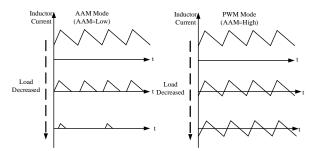

#### **AAM Mode**

MP9928 employs AAM mode functionality to optimize the efficiency during light-load or noload conditions. This AAM mode can be optional enabled when CCM/AAM pin is at a low level by connecting an appropriate resistor to GND to make sure that V<sub>AAM</sub> is no less than 480mV.

$$V_{AAM}$$

(mV) =  $I_{AAM}$  ( $\mu$ A) x  $R_{AAM}$  ( $k\Omega$ )

Where, I<sub>AAM</sub> is AAM pin output current, it can be shown below.

$$I_{AAM}(\mu A) = 600 \text{ (mV)} / R_{FREQ}(k\Omega)$$

R<sub>FREQ</sub> is the resistor from FREQ to SGND, for given operating frequency, and its value is shown in 'Programmable Switching Frequency' section.

AAM is disabled when CCM/AAM pin is floating or connected to VCC1.

If AAM is enabled, the MP9928 will firstly enter non-synchronous operation as long as the inductor current approaches zero at light-load. If the load is further decreased or even no load that make COMP voltage below the voltage of AAM threshold at about  $V_{AAM}+V_{OFFSET}$ , MP9928 enters AAM mode, where  $V_{AAM}$  is the voltage of CCM/AAM pin and  $V_{OFFSET}$  is about 720mV. In AAM mode, the internal clock is reset every time when  $V_{COMP}$  crosses over AAM threshold, and the crossover time is taken as benchmark of the next clock. When the load increases and the DC value of  $V_{COMP}$  is higher than AAM threshold, the operation mode is DCM or CCM which has a constant switching frequency.

Figure 2: AAM and PWM

#### Floating Driver and Bootstrap Charging

The floating top gate driver is powered by an external bootstrap capacitor ( $C_{BST}$ ), which is normally refreshed when the high-side MOSFET (HS-FET) turns off. This floating driver has its own UVLO protection. This UVLO's rising threshold is 3.05V with a hysteresis of 170mV.

#### VCC1 Regulator and VCC2 Power Supply

Both high-side and low-side MOSFET drivers and most of the internal circuitries are powered from the VCC1 regulator. An internal low dropout linear regulator supplies VCC1 power from VIN, usually a 1µF to 4.7µF ceramic capacitor is recommended from VCC1 to GND.

If VCC2 pin is left open or connected to a voltage <4.45V, an internal 5V regulator supplies VCC1 power from VIN. If VCC2 is >4.7V, the 5V regulator is disabled and another 5V regulator is triggered that supplies VCC1 power from VCC2. If 4.5V<VCC2<5V, the 5V regulator is in dropout and VCC1 is

approximately equal to VCC2. When VCC2 is greater than 5V (max. is 12V), VCC1 is regulated to 5V. Using the VCC2 power supply allows the VCC1 power to be derived from a high-efficiency external source, such as one of the MP9928's switching regulator outputs.

#### **Error Amplifier**

The error amplifier compares the FB pin voltage with the internal 0.8V reference (REF) and outputs a current proportional to the difference between the two input voltages. This output current is then used to charge or discharge the external compensation network to form the COMP voltage, which is used to control the power MOSFET current. Adjusting the compensation network from COMP pin to GND could optimize the control loop for good stability or fast transient response.

#### **Current Limit Function**

There are three fixed options for current limit setting: When ILIM connects to GND, the current limit sense voltage is set to 25mV; when ILIM connects to VCC1, the current limit sense voltage is set to 50mV; when ILIM pin floats, the current limit sense voltage is set to 75mV.

When the peak value of the inductor current exceeds the set current limit threshold, meanwhile, output voltage starts to drop until FB is 62.5% of the reference. MP9928 enters hiccup mode to periodically restart the part. Meanwhile, the frequency would be lowered when FB<0.5V. This protection mode is especially useful when the output is dead-shorted to ground. The average short-circuit current is greatly reduced to alleviate the thermal issues. The MP9928 exits the hiccup mode once the over-current condition is removed.

### **Low Dropout Operation**

At low dropout mode, the MP9928 is designed to operate at HS max duty on mode as long as the voltage across BST - SW is greater than 3.05V, this improves dropout. When the voltage from BST to SW drops below 3.05V, an under-voltage lockout (UVLO) circuit turns off the high-side MOSFET (HS-FET), and at the same time, the low-side MOSFET (LS-FET) turns on to refresh the BST capacitor. After the BST capacitor voltage is re-charged, the HS-FET turns on again to regulate the output. Since the BST capacitor

voltage is greater than 3.05V, the HS-FET can remain on for more switching cycles than are required to refresh the BST capacitor, thus increasing the effective duty cycle of the switching regulator. The low dropout operation makes the MP9928 suitable for application such as automotive cold-crank.

#### **Power Good Function**

The MP9928 includes an open-drain power good output that indicates whether the regulator's output is within about  $\pm\,10\%$  of its nominal value. When the output voltage falls outside this range, the PG output is pulled to low. It should be connected to a voltage source of no more than 5V through a resistor (e.g.,  $100k\Omega$ ). The PG delay time is  $25\mu$ s.

PG pin has self-driving capability, if MP9928 is off and PG pin is pulled up to another DC power source through a resistor, the PG pin can also be pulled low by self-driving circuit.

#### **Soft Start**

The soft start (SS) is implemented to prevent the converter output voltage from overshooting during startup. When the chip starts, the internal circuitry generates a soft-start voltage ramping up from 0V to 0.8V. When it is lower than the internal reference (REF), SS voltage overrides REF, so the error amplifier uses SS voltage as the reference. When SS voltage is higher than REF, REF regains control.

An external capacitor connected from SS to SGND is charged from an internal  $4\mu A$  current source, producing a ramped voltage. The soft-start time ( $t_{SS}$ ) is set by the external SS capacitor and can be calculated by below formula:

$$t_{SS}(ms) = \frac{C_{SS}(nF) \times V_{REF}(V)}{I_{SS}(\mu A)}$$

Where  $C_{SS}$  is the external SS capacitor,  $V_{REF}$  is the internal reference voltage (0.8V), and  $I_{SS}$  is the 4 $\mu$ A SS charge current. There is no internal SS capacitor.

SS will be reset when a fault protection happened except for output over voltage protection.

#### **Output Over-Voltage Protection**

MP9928 output voltage is monitored by FB voltage. If FB voltage is typically 10% higher than

the reference, it'll trigger OVP. Once it triggers OVP, MP9928 will go into discharge mode, the HS-FET is turned off, and the LS-FET is turned on and keeps on until the reverse current limit is triggered, after LS-FET is turned off, inductor current will increase to 0. The LS-FET will be turned on again next clock cycle. MP9928 works at discharge mode until the over-voltage condition is cleared.

#### **Enable**

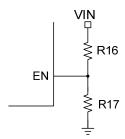

The MP9928 has a dedicated enable control pin. It uses a bandgap generated precision threshold of 1.22V. By pulling it high or low, the IC can be enabled or disabled. To disable the part, EN/SYNC must be pulled low for at least 15µs.

Tie EN to VIN through a resistor divider R16 and R17 to program the VIN start up threshold (see Figure 3). The EN threshold is 1.08V (falling edge), so the VIN falling UVLO threshold is 1.08V x (1+ R16/R17).

In high input design, EN pin voltage should not be greater than 50V.

Figure 3: EN Resistor Divider

#### **Synchronize**

The MP9928 can be synchronized to an external clock range from 100kHz up to 1000kHz through EN/SYNC pin. The internal clock rising edge is synchronized to the external clock rising edge. The pulse width (both on and off) of external clock signal should be no less than 100ns.

#### **Under-Voltage Lockout**

Under-voltage lockout (UVLO) is implemented to protect the chip from operating at insufficient input supply voltages. The MP9928 UVLO rising threshold is about 4.5V while its falling threshold is about 3.7V.

#### **Thermal Protection**

The purpose of thermal protection is to prevent damage in the IC by allowing exceptive current to flow and heating the junction. The die temperature is internally monitored until the thermal limit is reached. When the silicon die temperature is higher than 170°C, it shuts down the whole chip. When the temperature is lower than its lower threshold, typically 150°C, the chip is enabled again.

#### Start-Up and Shutdown

If both VIN and EN are higher than their respective thresholds, the chip starts up. The reference block starts first, generating stable reference voltages and currents. And then the internal regulator is enabled. The regulator provides stable supply for the remaining circuitry.

Three events can shut down the chip: EN low, VIN low and thermal shutdown. In the shutdown procedure, the signal path is firstly blocked to avoid any fault triggering. The COMP voltage and the internal supply rail are then pulled down. The floating driver is not subjected to this shutdown command.

#### **Pre-Bias Start-Up**

For MP9928, at startup, If SS<FB, which means output has pre-bias voltage, neither TG nor BG would be turned on until SS is greater than FB.

#### APPLICATION INFORMATION

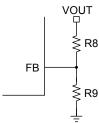

#### **Setting the Output Voltage**

The external resistor divider is used to set the output voltage.

Figure 4: Vout Setting Resistor

If R8 is determined, then R9 can be calculated with below formula:

$$R_9 = \frac{R_8}{\frac{V_{OUT}}{0.8V} - 1}$$

Table 1—Resistor Selection for Common Output Voltages

| <b>V</b> оит <b>(V)</b> | R8 (kΩ)   | R9 (kΩ) |

|-------------------------|-----------|---------|

| 3.3                     | 37.4 (1%) | 12 (1%) |

| 5                       | 63.4 (1%) | 12 (1%) |

| 12                      | 169 (1%)  | 12 (1%) |

#### **Setting Current Sensing**

The MP9928 has three fixed options for current limit setting: when ILIM pin is connected to GND, the current sense voltage is set to 25mV; when ILIM pin is connected to VCC1, the current sense voltage is set to 50mV and when ILIM pin is floating, the current limit sense voltage is set to 75mV.

The current sense resistor,  $R_{\text{SENSE}}$ , monitors the inductor current. Its value is chosen based on the current limit threshold. The relationship between the peak inductor current  $I_{pk}$  and  $R_{\text{SENSE}}$  is:

$$R_{SENSE} = \frac{V_{ILIMIT}}{Ipk}$$

(5)

The typical values for  $R_{\text{SENSE}}$  are in the range of  $5m\Omega$  to  $50m\Omega$ .

#### **Programmable Switching Frequency**

There are a number of variables to consider when choosing the switching frequency. A high frequency will increase switching losses and gate charge losses, while a lower frequency requires more inductance and capacitance, which results in larger real estate and also higher cost. It is a trade off between power loss and passive component size. Additionally, in noise-sensitive applications, the switching frequency should be out of a sensitive frequency band.

The MP9928's frequency can be programmed from 100kHz to 1000kHz with a resistor from FREQ to SGND. The value of  $R_{\text{FREQ}}$  for a given operating frequency can be calculated by:

$$R_{FREQ}(k\Omega) = \frac{20000}{f_s(kHz)} - 1$$

To get  $f_S = 500kHz$ , set  $R_{FREQ}$  to  $39k\Omega$ .

Table 2: Frequency vs. Resistor

| Resistor (kΩ) | Frequency (kHz) |

|---------------|-----------------|

| 65            | 300             |

| 39            | 500             |

| 19            | 1000            |

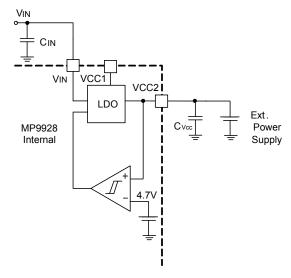

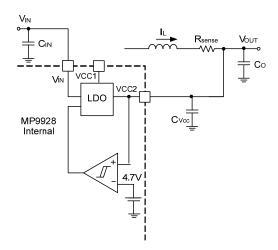

#### **V<sub>CC</sub>** Regulator Connection

VCC1 can be powered from both VIN and VCC2. If connecting VCC2 to an external power supply to improve the overall efficiency, this VCC2 should be larger than 4.7V but smaller than 12V.

Figure 5: V<sub>CC</sub> Power from External Supply

If  $V_{OUT}$  is higher than 4.7V but  $\leq$ 12V, VCC2 can be connected to  $V_{OUT}$  directly.

Figure 6: Vcc Power from Vout

#### Selecting the Inductor

An inductor with a DC current rating at least 25% higher than the maximum load current is recommended for most applications. A larger value inductor results in less ripple current and a lower output ripple voltage. However, the larger value inductor has a larger physical size, higher series resistance, and lower saturation current. Generally, choose the inductor ripple current approximately 30% of the maximum load current. Then the inductance value can be then be calculated by:

$$L = \frac{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{IN}} \times \Delta I_{\text{L}} \times f_{\text{S}}}$$

Where  $V_{OUT}$  is the output voltage,  $V_{IN}$  is the input voltage,  $f_S$  is the switching frequency, and  $\Delta I_L$  is the peak-to-peak inductor ripple current.

The maximum inductor peak current is:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_{L}}{2}$$

Where, ILOAD is the load current.

#### **Input Capacitor Selection**

Since the input capacitor absorbs the input switching current, it requires an adequate ripple current rating. The selection of the input capacitor is mainly based on its maximum ripple current capability. The RMS value of the ripple current flowing through the input capacitor can be described as:

$$I_{RMS} = I_{LOAD} \sqrt{\frac{V_{OUT}}{V_{IN}} (1 - \frac{V_{OUT}}{V_{IN}})}$$

The worst-case condition occurs at  $V_{\text{IN}} = 2V_{\text{OUT}}$ , where  $I_{\text{RMS}} = I_{\text{LOAD}}/2$ . So, the input capacitor selected must be capable of handling this ripple current.

#### **Output Capacitor Selection**

The output capacitor keeps the output voltage ripple small and ensures regulation loop stability. The output capacitor impedance should be low at the switching frequency. The output voltage ripple can be estimated by:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{S}} \times L} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times \left(R_{\text{ESR}} + \frac{1}{8 \times f_{\text{S}} \times C_{\text{O}}}\right)$$

Where  $C_O$  is the output capacitance value and  $R_{ESR}$  is the equivalent series resistance (ESR) value of the output capacitor.

For tantalum or electrolytic capacitor application, the ESR dominates the impedance at the switching frequency. So the above formula can be approximated as:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{S}} \times L} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times R_{\text{ESR}}$$

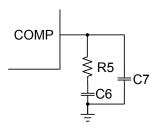

#### **Compensation Components**

The MP9928 employs current-mode control for easy compensation and fast transient response. The COMP pin controls system stability and transient response. The COMP pin is the output of the internal error amplifier. A series capacitor-resistor combination sets a pole-zero combination to control the control system's characteristics. The DC gain of the voltage feedback loop is:

$$A_{VDC} = R_{LOAD} \times G_{CS} \times A_O \times \frac{V_{FB}}{V_{OUT}}$$

Where  $A_O$  is the error-amplifier voltage gain 3000V/V,  $G_{CS}$  is the current-sense transconductance,  $1/(12xR_{SENSE})$  (A/V), and  $R_{LOAD}$  is the load resistor value.

Figure 7: COMP External Compensation

The system has two important poles: one from the compensation capacitor (C6) and the output resistor of error amplifier and the other tone from the output capacitor and the load resistor. These poles can be calculated by:

$$f_{\text{P1}} = \frac{G_{\text{m}}}{2\pi \times C6 \times A_{\text{O}}}$$

$$f_{P2} = \frac{1}{2\pi \times Co \times R_{LOAD}}$$

Where G<sub>m</sub> is the error-amplifier transconductance 500μA/V, and Co is the output capacitor.

The system has one important zero due to the compensation capacitor and the compensation resistor (R5). This zero is located at:

$$f_{z_1} = \frac{1}{2\pi \times C6 \times R5}$$

The system may have another significant zero if the output capacitor has a large capacitance or a high ESR value. This zero can be located at:

$$f_{ESR} = \frac{1}{2\pi \times Co \times R_{ESR}}$$

In this case, a third pole set by the compensation capacitor (C7) and the compensation resistor can compensate for the effect of the ESR zero. This pole is calculated by:

$$f_{_{P3}}=\frac{1}{2\pi\times C7\times R5}$$

The goal of the compensation design is to shape the converter transfer function for a desired loop gain. The system crossover frequency where the feedback loop has unity gain is important, since lower crossover frequencies result in slower line and load transient responses, and higher crossover frequencies lead to system instability. Set the crossover frequency to ~0.1×f<sub>SW</sub>.

Follow the below steps design the to compensation:

1. Choose R5 to set the desired crossover frequency:

$$R5 = \frac{2\pi \times Co \times f_C}{G_m \times G_{CS}} \times \frac{V_{OUT}}{V_{FB}}$$

Where, f<sub>C</sub> is the desired crossover frequency.

2. Choose C6 to achieve the desired phase margin. For applications with typical inductor values, set the compensation zero  $(f_{Z1})$  < 0.25 x f<sub>C</sub> to provide a sufficient phase margin. C6 is then:

$$C6 > \frac{4}{2\pi \times R5 \times f_{C}}$$

3. C7 is required if the ESR zero of the output capacitor is located at <0.5×f<sub>SW</sub>, or the following relationship is valid:

$$\frac{1}{2\pi \times Co \times R_{\text{ESR}}} < \frac{f_{\text{SW}}}{2}$$

If this is the case, use C7 to set the pole (f<sub>P3</sub>) at the location of the ESR zero. Determine C7:

$$C7 = \frac{Co \times R_{ESR}}{R5}$$

#### **PCB Layout Considerations**

For a controller, the layout is always an important step in design. A poor layout would result in reduced performance, EMI problems, resistive loss and even system instability. Following step would help to guarantee a good layout design:

- Input power loop between input capacitor, high-side MOSFET and low-side MOSFET should be as small as possible, SW trace should be as possible as short and wide. At the same time, one small decoupling capacitor should be placed close to the IC's IN and GND pins.

- 2. Feedback loop should be far away from noise source such as SW trace, the feedback divider resistor should be as close as possible to FB and GND pin.

- Route the sensing traces (SENSE+, SENSE-) in paired way with smallest closed area. Avoid crossing noisy areas such as SW or high-side gate drive traces. Place the filter capacitor for the current sense signal as close to the IC pins as possible.

- 4. A short and wide type resistor is recommend for current sense.

- 5. VCC1 and VCC2 capacitors should be placed as close as possible to VCC1 pin and VCC2 pin.

- Layout the gate drive traces as directly as possible. Layout the forward and return traces close together, either running side by side or on top of each other on adjacent layers to minimize the inductance of the gate drive path.

- The ground return of input/output capacitor should be tied close with large GND copper area, and then connect to IC GND pin through single point.

- 8. For heavy load, suggest layout large copper, more layers and more vias for heat sink.

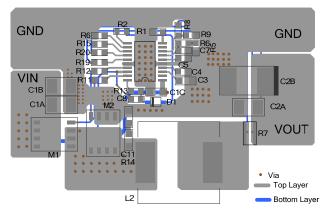

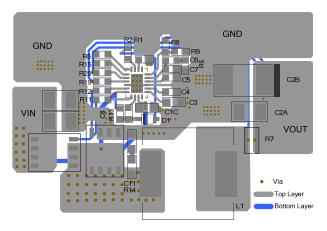

Figure 8 shows the recommended components place for MP9928 in TSSOP20-EP package. Figure 9 shows the recommended components place for MP9928 in QFN20 package. For the layout, the corresponding schematic can be found on Figure 10.

Figure 8: Layout Recommendation

Figure 9: Layout Recommendation

#### **Design Example**

Below is a design example following the application guidelines for the following specifications:

**Table 3: Design Example**

| <b>V</b> <sub>IN</sub> 6V to 60 V |       |  |

|-----------------------------------|-------|--|

| V <sub>out</sub>                  | 5V    |  |

| l <sub>out</sub>                  | 0A-7A |  |

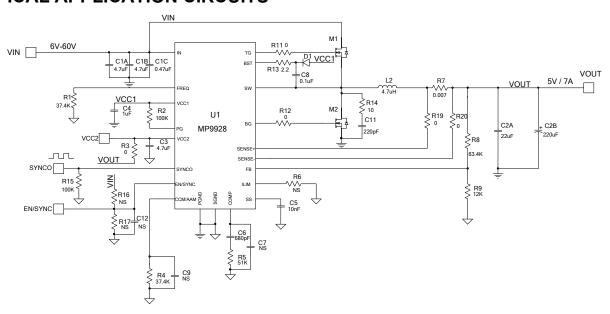

The typical application circuit for  $V_{OUT} = 5V$  in Figure 10 shows the detailed application schematic, and it is the basis for the typical performance waveforms. This circuit can work down to 4V after startup, but  $V_{OUT}$  may drop when  $V_{IN}$  is low due to maximum duty cycle limit. For more detailed device applications, please refer to the related Evaluation Board Datasheets

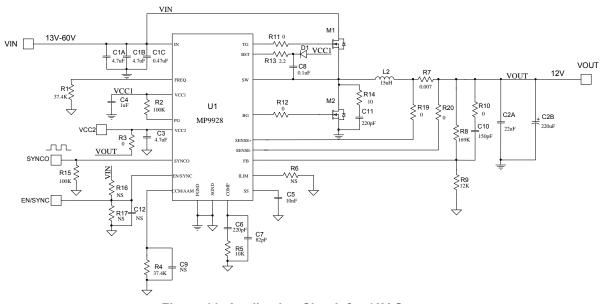

# **TYPICAL APPLICATION CIRCUITS**

Figure 10: Application Circuit for 5V Output

Figure 11: Application Circuit for 12V Output

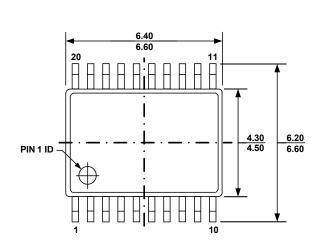

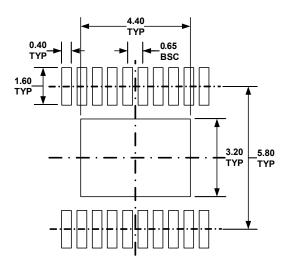

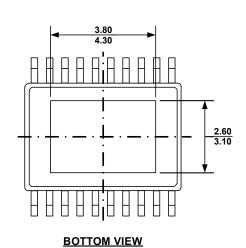

### **PACKAGE INFORMATION**

#### **TSSOP-20 EP**

**TOP VIEW**

RECOMMENDED LAND PATTERN

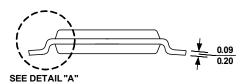

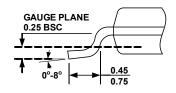

**FRONT VIEW**

SIDE VIEW

DETAIL "A"

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH PROTRUSION OR GATE BURR

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY(BOTTOM OF LEADS AFTER FORMING SHALL BE 0.10 MILLIMETERS MAX

- 5) DRAWING CONFORMS TO JEDEC MO153, VARIATION ACT.

- 6) DRAWING IS NOT TO SCALE