## **MPQ5850**

36V, Smart Diode Controller with Reverse Protection, AEC-Q100 Qualified

### DESCRIPTION

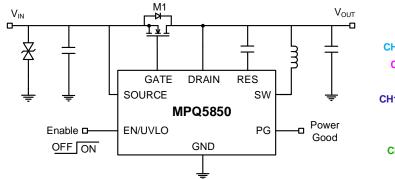

The MPQ5850 is a smart diode controller that can drive an external N-channel MOSFET to replace a Schottky diode for reverse input protection. The device's 20mV ultra-low dropout minimizes power loss and enables a low minimum input voltage, which makes the MPQ5850 well-suited for cold-crank conditions in automotive applications. The 4µA shutdown current also makes the device ideal for batterypowered applications. The ultra-fast transient response meets stringent ISO16750 requirements.

The MPQ5850 integrates an internal boost to provide a boost voltage that turns on the external N-channel MOSFET, even at a low input voltage ( $V_{IN}$ ). An open-drain, power good signal indicates when the external N-channel MOSFET is fully on.

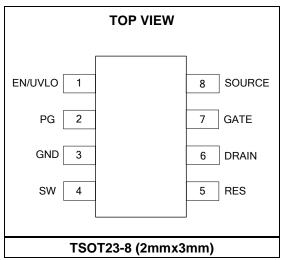

The MPQ5850 is available in a TSOT23-8 (2mmx3mm) package.

#### FEATURES

- Built to Handle Tough Automotive Transients:

- -36V Blocking Voltage

- Load Dump Up to 42V

- Cold Crank Down to 0V

- o Rectifies AC Frequency Up to 100kHz

- Strong Gate Drive Ability: 170mA Pull-Up and 430mA Pull-Down

- Extended Vehicle Battery Life:

- Low Quiescent Current in Standby Mode (4µA)

- Low Quiescent Current in Steady State (30µA)

- Reduced Board Size:

- Available in a TSOT23-8 (2mmx3mm) Package

- Additional Features:

- 20mV Ultra-Low Dropout

- Integrates a Boost Converter

- Power Good (PG) Indication for RES Out of Regulation, Fast Pull-Up, and Part Disabling

- Available in AEC-Q100 Grade 1

### **APPLICATIONS**

- Automotive System Protection

- Automotive ADAS Systems (Cameras)

- Automotive Infotainment Systems, Including Digital Clusters and Head Units

- Battery-Powered Systems

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

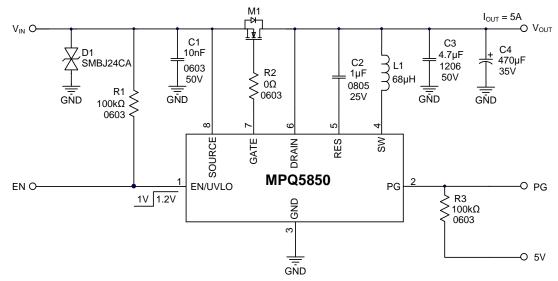

### **TYPICAL APPLICATION**

#### **ORDERING INFORMATION**

| Part Number*   | Package            | Top Marking | MSL Rating** |  |  |

|----------------|--------------------|-------------|--------------|--|--|

| MPQ5850GJ      |                    | See Delaw   |              |  |  |

| MPQ5850GJ-AEC1 | TSOT23-8 (2mmx3mm) | See Below   | Level 1      |  |  |

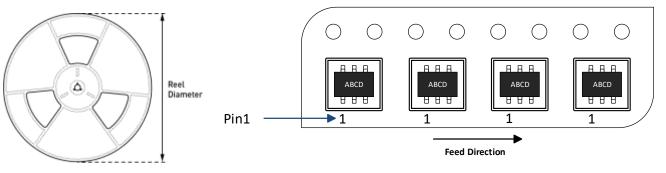

\* For Tape & Reel, add suffix -Z (e.g. MPQ5850GJ-Z). \*\* Moisture Sensitivity Level Rating

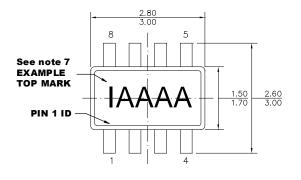

### TOP MARKING (MPQ5850GJ & MPQ5850GJ-AEC1)

#### BNNY

BNN: Product code of MPQ5850GJ and MPQ5850GJ-AEC1 Y: Year code

#### PACKAGE REFERENCE

### **PIN FUNCTIONS**

| Pin #                                               | Name    | Description                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                   | EN/UVLO | <b>Enable pin.</b> Pull EN below the specified threshold (1V) to shut down the chip. Pull EN above the threshold (1.2V) to enable the chip. A resistor divider connected between EN/UVLO and SOURCE can be used to raise the under-voltage lockout (UVLO) threshold. Do not float the EN/UVLO pin, and connect it to DRAIN if the shutdown feature not used. |

| 2                                                   | PG      | <b>Open-drain power good pin.</b> The PG pin asserts low if the device is disabled, the reservoir supply is out of regulation, or if the fast pull-up path is active for longer than 17µs. Float PG or connect it to GND if it is not used.                                                                                                                  |

| 3                                                   | GND     | Ground connection of the device. Connect GND to the ground plane of the board.                                                                                                                                                                                                                                                                               |

| 4                                                   | SW      | Switch node of internal boost regulator. Connect an inductor between the SW and DRAIN pins.                                                                                                                                                                                                                                                                  |

| 5                                                   | RES     | <b>Reservoir supply.</b> RES is the power supply for the external N-channel MOSFET gate driver. Connect a minimum $1\mu$ F ceramic capacitor between the RES and DRAIN pins.                                                                                                                                                                                 |

| 6                                                   | DRAIN   | <b>Drain connection.</b> Connect the DRAIN pin to the drain of the external power MOSFET. DRAIN is the power supply of the internal circuitry, and also controls the MOSFET's gate voltage. Connect a minimum $4.7\mu$ F capacitor from DRAIN to ground, and place this capacitor as close as possible to the device.                                        |

| 7 GATE Gate connection. Connect the GATE pin to the |         | Gate connection. Connect the GATE pin to the gate of the external power MOSFET.                                                                                                                                                                                                                                                                              |

| 8                                                   | SOURCE  | <b>Source connection.</b> Connect the SOURCE pin to the source of the external power MOSFET. The voltage sensed on this pin works with the DRAIN voltage to control the MOSFET gate.                                                                                                                                                                         |

### ABSOLUTE MAXIMUM RATINGS (1)

| DRAIN0.3V to +42V                                                   |

|---------------------------------------------------------------------|

| DRAIN - SOURCE2V to +52V                                            |

| GATE - SOURCE0.3V to +13V                                           |

| RES0.3V to V <sub>DRAIN</sub> + 13V                                 |

| SW0.3V to +57V                                                      |

| PG0.3V to +6V                                                       |

| Continuous power dissipation ( $T_A = 25^{\circ}C$ ) <sup>(2)</sup> |

| TSOT23-8 (2mmx3mm)1.5W                                              |

| Junction temperature 150°C                                          |

| Lead temperature260°C                                               |

#### Electrostatic Discharge (ESD) Ratings

Human body model (HBM) ...... Class 2 <sup>(3)</sup> Charged device model (CDM) ...... Class C2b <sup>(4)</sup>

#### **Recommended Operating Conditions**

Supply voltage (V<sub>IN</sub>) ...... 3.3V to 36VOperating junction temp (T<sub>J</sub>) .... -40°C to +150°C

# Thermal Resistance $\theta_{JA}$ $\theta_{JC}$ TOOTOD 0 (Commutant)

| 150123-8 (2mmx3mm)      |    |    |       |

|-------------------------|----|----|-------|

| JESD51-7 <sup>(5)</sup> | 85 | 20 | .°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can produce an excessive die temperature, and the device may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Per AEC-Q100-002.

- 4) Per AEC-Q100-011.

- 5) Measured on JESD51-7, 4-layer PCB. The values given in this table are only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

### **ELECTRICAL CHARACTERISTICS**

$V_{\text{SOURCE}} = V_{\text{EN/UVLO}} = 12V$ ,  $V_{\text{RES}} = 22V$ ,  $T_{\text{J}} = -40^{\circ}$ C to  $+150^{\circ}$ C, unless otherwise noted.

| Parameter                                      | Symbol                    | Condition                                                                                                                                   | Min                          | Тур  | Max | Units |

|------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-----|-------|

| Input Voltage                                  |                           |                                                                                                                                             |                              |      |     |       |

| Drain voltage at start-up                      | V <sub>DRAIN_UVLO</sub>   |                                                                                                                                             |                              | 2.8  | 3.2 | V     |

| Drain voltage UVLO<br>falling                  | Vdrain_uvlo_f             |                                                                                                                                             | 2.4                          | 2.6  | 2.8 | V     |

| Reservoir UVLO rising                          | V <sub>RES_UVLO</sub>     |                                                                                                                                             | 8                            | 11   | 13  | V     |

| Reservoir UVLO<br>hysteresis                   | V <sub>RES_UVLO_HYS</sub> |                                                                                                                                             |                              | 0.2  |     | V     |

|                                                |                           | $V_{EN} = 0V, T_J = 25^{\circ}C$                                                                                                            |                              | 4    | 10  | μA    |

|                                                | ISHDN                     | $V_{EN} = 0V, T_J = -40^{\circ}C \text{ to } +150^{\circ}C$                                                                                 |                              |      | 20  | μA    |

|                                                |                           | $V_{EN} = 2V$ , in regulation, system<br>input current, $T_J = 25^{\circ}C$                                                                 |                              | 30   | 50  | μA    |

| Quiescent current                              | lα                        | $V_{EN} = 2V$ , in regulation, system<br>input current,<br>$T_J = -40^{\circ}C$ to $+125^{\circ}C$ <sup>(6)</sup>                           |                              |      | 100 | μA    |

|                                                |                           | $V_{EN} = 2V$ , in regulation, system<br>input current,<br>$T_J = 125^{\circ}C$ to $150^{\circ}C$                                           |                              |      | 200 | μA    |

| Rectifier                                      |                           |                                                                                                                                             |                              | -    |     |       |

| Source to drain regulation voltage             | V <sub>SD</sub>           |                                                                                                                                             | 10                           | 20   | 30  | mV    |

| Source to drain fast pull-<br>up threshold     | Vsd_fpu                   |                                                                                                                                             | 50                           | 75   | 100 | mV    |

| Source to drain fast pull-<br>down threshold   | V <sub>SD_FPD</sub>       |                                                                                                                                             | -15                          | -4   | 0   | mV    |

| Drain current                                  | ID                        | Gate driver in regulation                                                                                                                   |                              | 50   |     | μA    |

| Source current                                 | Is_R                      | V <sub>SOURCE</sub> = -36V                                                                                                                  |                              |      | -1  | mA    |

| Fast pull up current                           | IFPU                      | V <sub>GATE-RES</sub> = -7V                                                                                                                 | 170                          |      |     | mA    |

| Fast pull down current                         | IFPD                      | $V_{GATE-SOURCE} = 5V$                                                                                                                      | 430                          |      |     | mA    |

| Reverse biased gate-                           | V <sub>GS_RB</sub>        | $V_{\text{SOURCE}} = -5V$ , $I_{\text{GATE}} = 1mA$                                                                                         |                              | 0.01 | 0.3 | V     |

| source voltage                                 | VGS_RB                    | $V_{SOURCE} = -36V, I_{GATE} = 1mA$                                                                                                         |                              | 0.01 | 0.3 | V     |

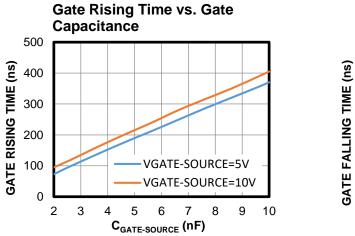

| Gate turn-on delay time                        | ton                       | Step (V <sub>SOURCE</sub> - V <sub>DRAIN</sub> ) from<br>-100mV to +3V, V <sub>RES-DRAIN</sub> = 13V,<br>C <sub>GATE-SOURCE</sub> = 10nF    |                              | 1.2  | 2   | μs    |

| Gate turn-off delay time                       | toff                      | Step (V <sub>SOURCE</sub> - V <sub>DRAIN</sub> ) from 3V to<br>-100mV, V <sub>RES-DRAIN</sub> = 13V,<br>C <sub>GATE-SOURCE</sub> = 10nF     |                              | 1    | 2   | μs    |

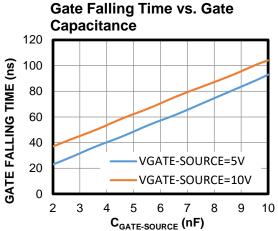

| Gate rising time                               | trising <sup>(6)</sup>    | Step (V <sub>SOURCE</sub> - V <sub>DRAIN</sub> ) from<br>-100mV to +3V, V <sub>RES-DRAIN</sub> = 13V,<br>C <sub>GATE-SOURCE</sub> = 10nF    | o +3V, Vres-drain = 13V, 300 |      |     | ns    |

| Gate falling time                              | tfalling <sup>(6)</sup>   | Step (V <sub>SOURCE</sub> - V <sub>DRAIN</sub> ) from 3V to<br>-100mV, V <sub>RES-DRAIN</sub> = 13V, C <sub>GATE-</sub><br>SOURCE = 10nF100 |                              |      | ns  |       |

| Maximum rectification frequency <sup>(6)</sup> | fmax                      | $V_{PP} = 6V, C_{GATE-SOURCE} = 15nF$<br>$V_{PP} = 2V, C_{GATE-SOURCE} = 15nF$                                                              | 50<br>100                    |      |     | kHz   |

### ELECTRICAL CHARACTERISTICS (continued)

#### $V_{\text{SOURCE}} = V_{\text{EN/UVLO}} = 12V$ , $V_{\text{RES}} = 22V$ , $T_{\text{J}} = -40^{\circ}$ C to $+150^{\circ}$ C, unless otherwise noted.

| Parameter                                     | Symbol              | Condition                        | Min | Тур | Max | Units |

|-----------------------------------------------|---------------------|----------------------------------|-----|-----|-----|-------|

| Boost Converter                               |                     |                                  |     |     |     |       |

| Reservoir regulation voltage                  | Vreg                |                                  | 10  | 12  | 14  | V     |

| Reservoir regulation<br>UVLO hysteresis       | VREG_UVLO_HYS       | Vreg - Vres_uvlo - Vres_uvlo_hys |     | 1.2 |     | V     |

| Boost current limit                           | IBOOST              |                                  | 160 | 220 | 280 | mA    |

| SW leakage                                    | Isw                 |                                  |     |     | 1   | μA    |

| Boost power switch on resistance              | Rsw                 |                                  |     | 1.5 | 3.5 | Ω     |

| Boost rectifier diode voltage drop            | Vdiode              | I <sub>DIODE</sub> = 220mA       |     | 0.9 |     | V     |

| Enable Pin                                    |                     | •                                |     |     |     |       |

| Enable threshold rising                       | VEN                 |                                  | 1.0 | 1.2 | 1.4 | V     |

| Enable threshold falling                      | Ven_f               |                                  | 0.8 | 1   | 1.2 | V     |

| Enable hysteresis                             | Ven_h               |                                  |     | 200 |     | mV    |

| Enable leakage                                | I <sub>EN</sub>     | $V_{EN} = 3V$                    |     |     | 1   | μA    |

| Power Good Flag                               |                     |                                  |     |     |     |       |

| PG output voltage low                         | Vpg_low             | Isink = 1mA                      |     | 0.1 | 0.3 | V     |

| Thermal shutdown (6)                          | T <sub>SD</sub>     |                                  |     | 175 |     | °C    |

| Thermal shutdown<br>hysteresis <sup>(6)</sup> | T <sub>SD_HYS</sub> |                                  |     | 25  |     | °C    |

Note:

6) Derived from bench characterization. Not tested in production.

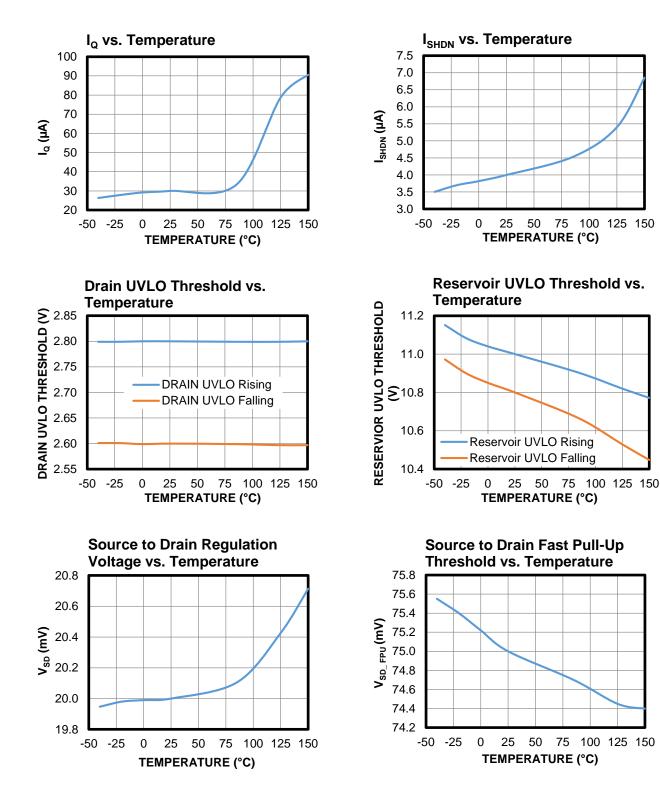

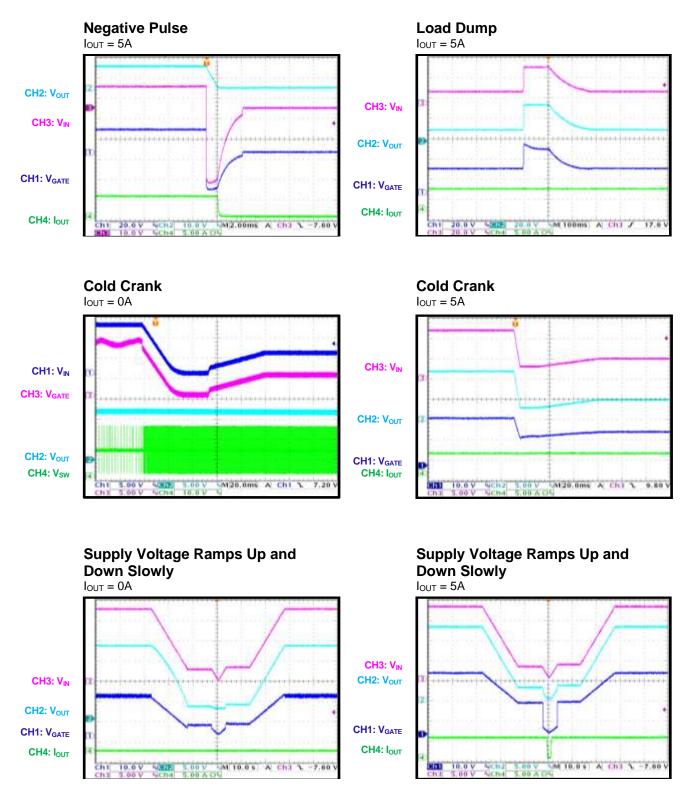

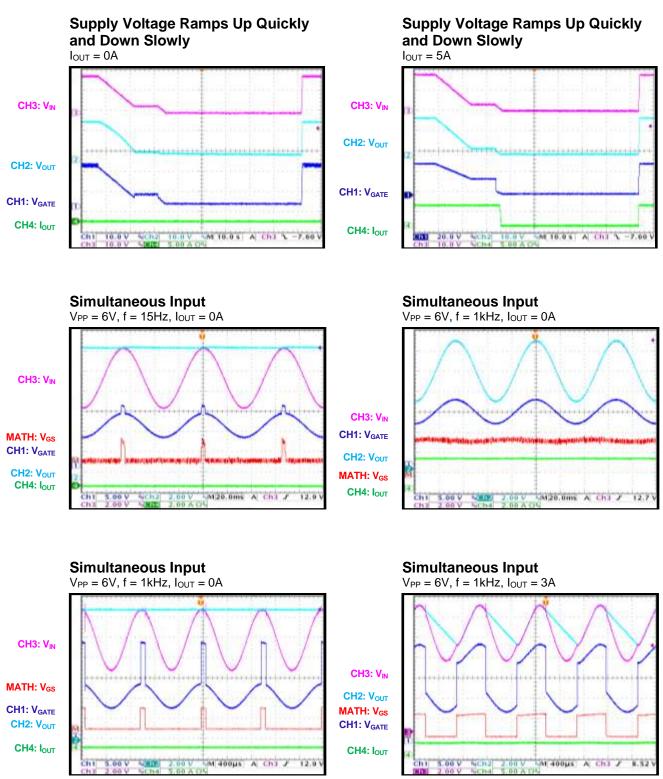

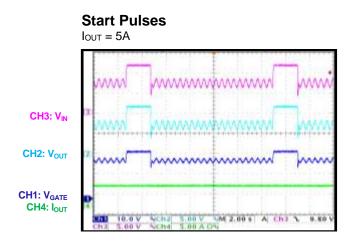

### **TYPICAL CHARACTERISTICS**

$V_{IN}$  = 12V, L = 68µH, T<sub>J</sub> = -40°C to +150°C, unless otherwise noted.

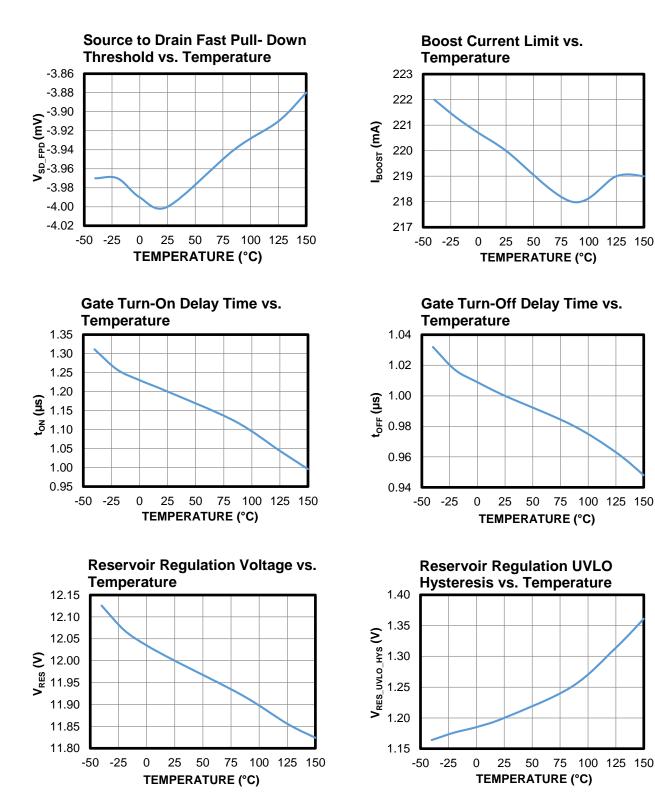

### **TYPICAL CHARACTERISTICS** (continued)

$V_{IN} = 12V$ , L = 68µH, T<sub>J</sub> = -40°C to +150°C, unless otherwise noted.

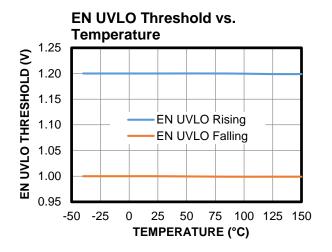

### **TYPICAL CHARACTERISTICS** (continued)

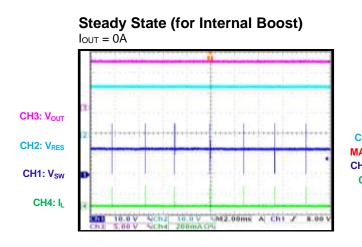

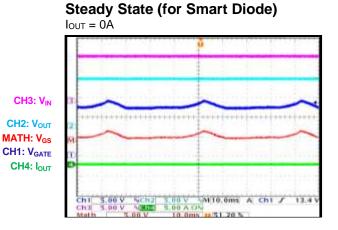

$V_{IN}$  = 12V, L = 68µH, T<sub>J</sub> = -40°C to +150°C, unless otherwise noted.

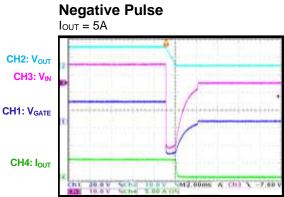

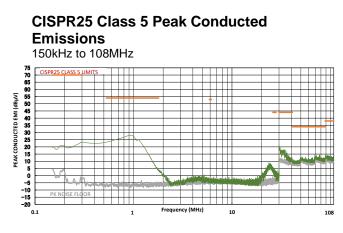

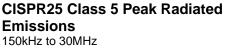

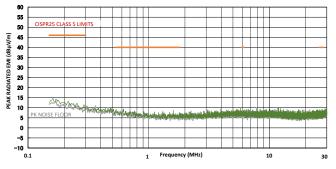

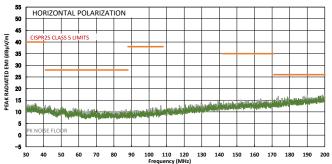

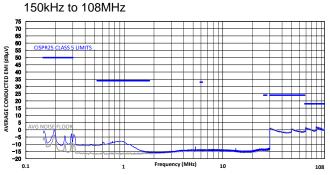

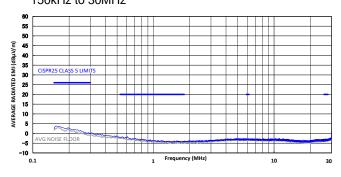

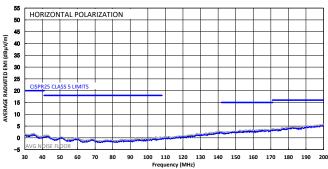

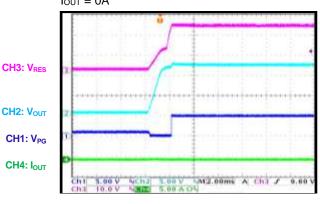

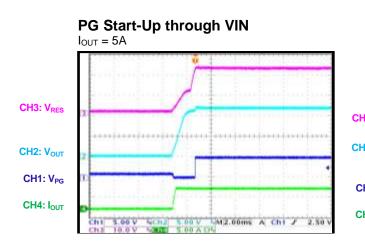

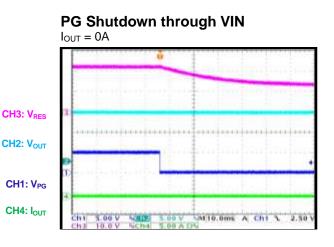

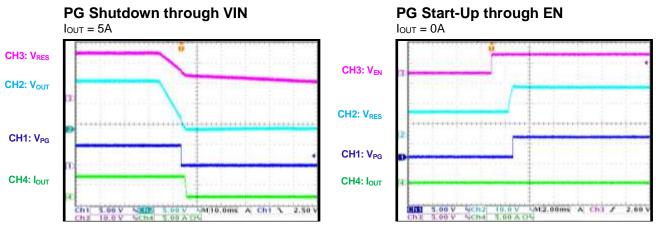

### **TYPICAL PERFORMANCE CHARACTERISTICS**

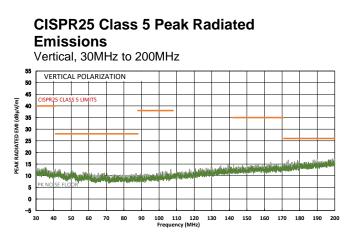

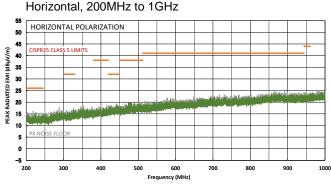

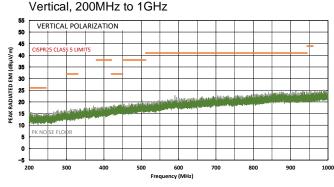

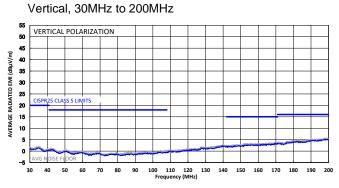

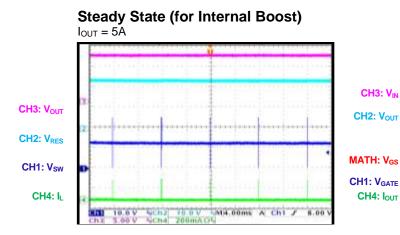

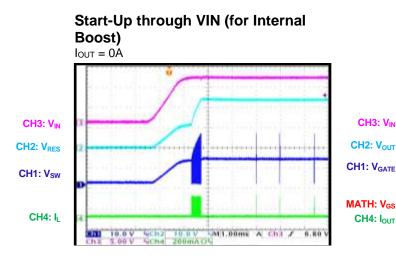

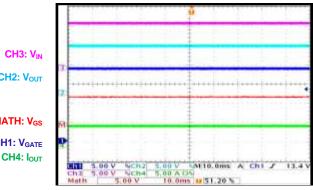

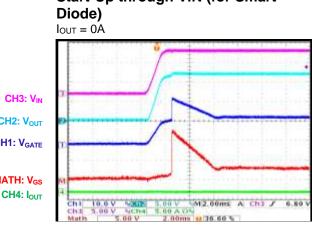

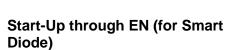

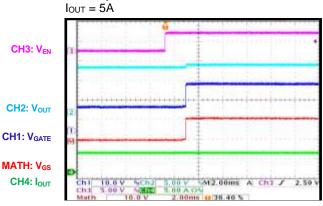

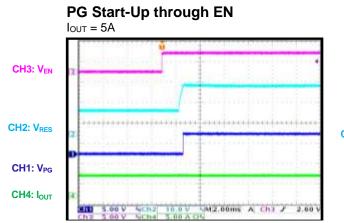

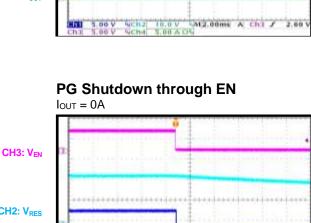

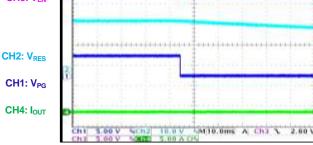

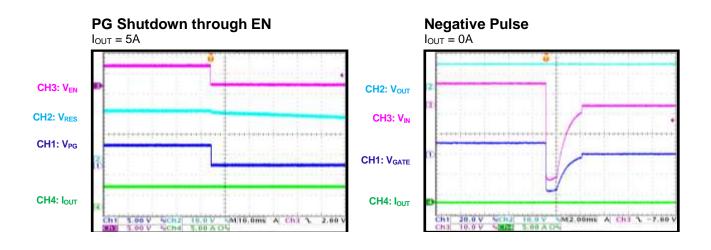

$V_{IN}$  = 12V,  $I_{OUT}$  = 5A, L = 68µH,  $C_{OUT}$  = 470µF,  $T_A$  = 25°C, unless otherwise noted. <sup>(7)</sup>

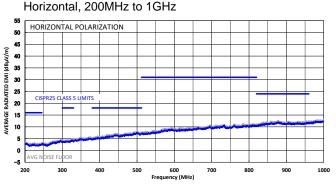

#### CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 30MHz to 200MHz

#### CISPR25 Class 5 Average Conducted Emissions

#### CISPR25 Class 5 Average Radiated Emissions 150kHz to 30MHz

#### CISPR25 Class 5 Average Radiated Emissions

Horizontal, 30MHz to 200MHz

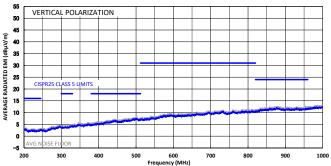

$V_{IN}$  = 12V,  $I_{OUT}$  = 5A, L = 68µH,  $C_{OUT}$  = 470uF,  $T_A$  = 25°C, unless otherwise noted. <sup>(7)</sup>

#### CISPR25 Class 5 Peak Radiated Emissions

#### CISPR25 Class 5 Peak Radiated Emissions

#### CISPR25 Class 5 Average Radiated Emissions

#### CISPR25 Class 5 Average Radiated Emissions

#### CISPR25 Class 5 Average Radiated Emissions

Vertical, 200MHz to 1GHz

#### Note:

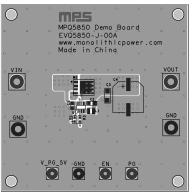

7) The EMC test results are based on the application circuit, and tested on the EVQ5850-J-00A (see Figure 4 on page 26).

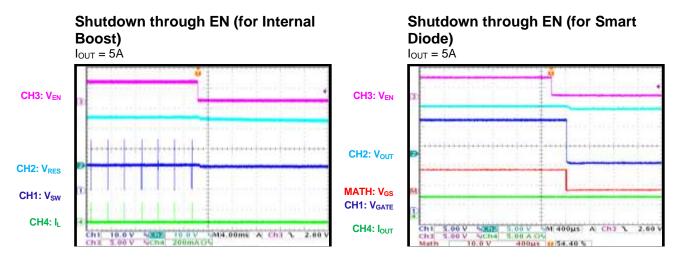

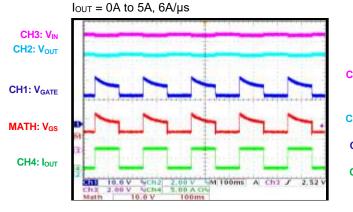

$V_{IN} = 12V$ ,  $I_{OUT} = 5A$ ,  $L = 68\mu$ H,  $T_A = 25^{\circ}$ C, unless otherwise noted.

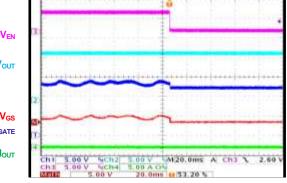

Steady State (for Smart Diode)  $I_{OUT} = 5A$

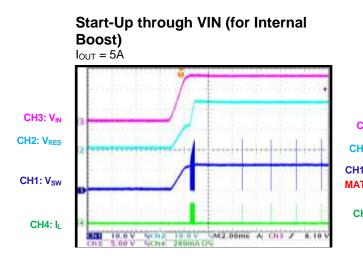

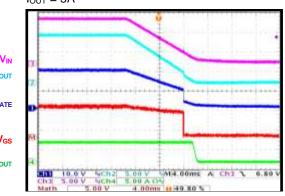

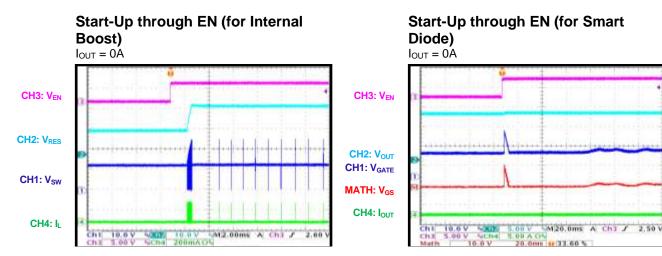

# Start-Up through VIN (for Smart

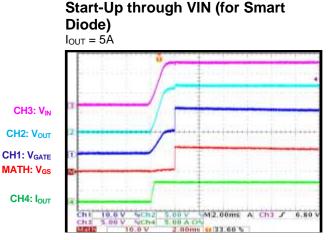

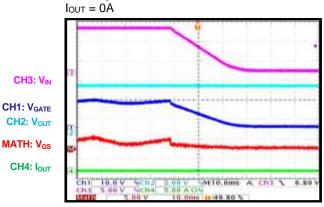

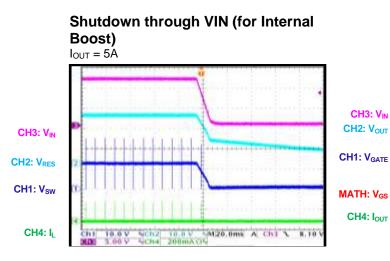

$V_{IN}$  = 12V,  $I_{OUT}$  = 5A, L = 68µH,  $T_A$  = 25°C, unless otherwise noted.

CH3:  $V_{IN}$ CH3:  $V_{IN}$ CH2:  $V_{RES}$ CH1:  $V_{SW}$ CH4:  $I_L$

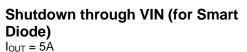

Shutdown through VIN (for Smart Diode)

Load Transient

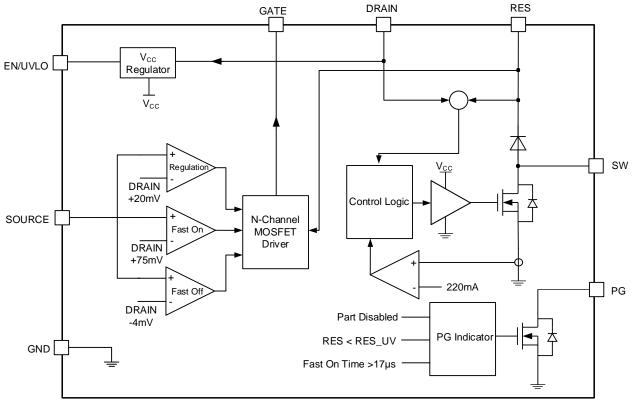

### FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

### **OPERATION**

The MPQ5850 is an 8-pin smart diode controller that drives an external N-channel MOSFET to minimize power loss, including DC forward loss and AC rectification loss.

#### **Smart Diode Operation**

During normal operation, when  $V_{SOURCE} > V_{DRAIN}$ , the MPQ5850 modulates the gate of the external N-channel MOSFET to regulate the source-todrain voltage to about 20mV. This minimizes power loss and allows small negative currents to be easily detected.

Generally, the source-to-drain voltage is regulated to about 20mV. When the load current rises, the GATE voltage rises until the MOSFET is fully on. If the load current drops, the GATE amplifier drives the MOSFET's gate lower to maintain a 20mV drop.

If the drain-to-source voltage exceeds 20mV, a large current modifies the GATE pin's voltage to regulate the drain-to-source voltage. If a negative current flows through the external Nchannel MOSFET, the device detects a sourceto-drain negative voltage drop. If the drop exceeds -4mV, the MPQ5850 pulls down the GATE pin to turn off the external N-channel MOSFET quickly. If a forward current flows through the external N-channel MOSFET (either the body or channel), the device detects a source-to-drain forward voltage drop. If the drop exceeds 75mV, the MPQ5850 pulls up the GATE pin to quickly turn on the external N-channel MOSFET. This allows high-frequency AC waveforms (up to 100kHz) to be rectified with minimal system and N-channel MOSFET power loss.

#### **Boost Converter**

The integrated boost converter uses fixed peak current mode control. When the reservoir floating supply is below 12V, the boost converter requests another turn-on pulse. This pulse terminates when the inductor current reaches 220mA.

The inductor current should reach 0mA before the next on cycle begins. This sets a maximum frequency ( $f_{MAX}$ ) depending on  $V_{DRAIN}$ .  $f_{MAX}$  can be calculated with Equation (1):

$$f_{MAX} = \frac{1}{t_{ON} + t_{OFF}}$$

(1)

Where  $t_{ON}$  is the on time and  $t_{OFF}$  is the off time.  $t_{ON}$  can be estimated with Equation (2):

$$t_{\rm ON} = \frac{I_{\rm PEAK} \times L}{V_{\rm DRAIN} - R_{\rm SW} \times \frac{I_{\rm PEAK}}{2}}$$

(2)

$t_{OFF}$  can be calculated with Equation (3):

$$t_{OFF} = \frac{I_{PEAK} \times L}{V_{RES} + V_{DIODE}}$$

(3)

#### Start-Up and Low-Voltage Operation

The MPQ5850 starts in the off state. In this state. the gate is passively pulled to SOURCE, and the boost converter is disabled. Once VDRAIN exceeds the under-voltage lockout (UVLO) threshold, the device enters the disabled state. The device is enabled when it enters a logic high state. In the disabled state, the gate is passively pulled to source, the boost converter is disabled, and the PG pin is pulled low. Once the EN/UVLO pin is pulled high, the device enters the start-up state, which causes the boost converter to turn on. When the reservoir capacitor exceeds the reservoir UVLO threshold, normal operation begins. During normal operation, the gate is actively modulated based on V<sub>SOURCE</sub> and V<sub>DRAIN</sub>, and the PG pin is high when the source-to-drain voltage is regulated.

The DRAIN pin is the power supply of the internal circuitry. DRAIN also controls the MOSFET's gate voltage. If V<sub>DRAIN</sub> exceeds its UVLO threshold, then the MPQ5850 operates normally, even in cold-crank conditions down to 0V. A large electrolytic output capacitor is required under these conditions.

If  $V_{DRAIN}$  drops below the UVLO threshold, the device pulls down the GATE pin to SOURCE until the voltage on the reservoir capacitor discharges below  $V_{RES_UVLO}$ . This allows the device to minimize forward voltage drops during temporary low voltage transients, such as under cold-crank conditions.

#### Power Good (PG)

The power good (PG) pin is an open-drain pin designed to indicate the status of the MPQ5850. PG asserts low when the fast pull-up current is active for longer than  $17\mu$ s, the reservoir capacitor is out of regulation, or the device is disabled. Otherwise, PG de-asserts, and the pin is pulled up to the external source through a pull-up resistor.

### **APPLICATION INFORMATION**

#### Selecting the Power MOSFET

The power MOSFET must support the maximum steady current during forward operation, and withstand the worst-case battery transients during reverse blocking operation.

The steady state power dissipation is based on the  $R_{DS(ON)}$  of the power MOSFET and the load current. If the load is light ( $I_{LOAD} \times R_{DS(ON)} < V_{SD}$ ), the forward drop is regulated to  $V_{SD}$  (typically 20mV). The power loss be calculated with Equation (4):

$$P_{\text{CONDUCTION}} = V_{\text{SD}} \times I_{\text{LOAD}}$$

(4)

Under heavy loads, the MOSFET is fully enhanced, so power dissipation depends on the  $R_{DS(ON)}$  of the MOSFET. The power loss can be estimated with Equation (5):

$$P_{\text{CONDUCTION}} = I_{\text{LOAD}}^{2} \times R_{\text{DS(ON)}}$$

(5)

As the high-amplitude ripple on the input is rectified, a MOSFET with the smallest total gate charge ( $Q_{GTOT}$ ) is required. A MOSFET with smaller  $Q_{GTOT}$  not only reduces reverse current during the turn-off delay but it also lowers driver loss.

The operating MOSFET's drain-to-source voltage must be able to support the worst-case conditions, such as when there is a voltage step or the battery voltage goes from a positive to negative voltage. The worst-case condition occurs when  $V_{IN}$  is in reverse and  $V_{OUT}$  is not discharged to low.  $V_{DSS}$  must meet the condition calculated with Equation (6):

$$V_{\text{DSS}} \ge V_{\text{OUT}} + \left| V_{\text{IN}} \right| \tag{6}$$

The gate-to-source voltage should be rated to be  $\pm 15V$  or greater.

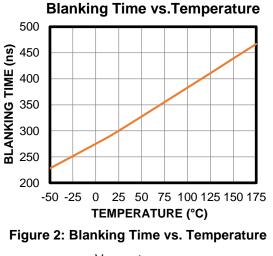

#### Selecting the Boost Inductor

The value of the inductor affects the driver's maximum current capability. There is a blanking time in the boost converter, and the inductor current is not detected during the blanking time. The relationship between the blanking time and temperature is shown in Figure 2. To ensure that the inductor current does not exceed 220mA during the blanking time, the inductor value (L) should meet the condition estimated with Equation (7):

$$L > \frac{V_{DRAIN} \times t_{ON\_BLANKING}}{I_{PEAK}}$$

(7)

Where  $V_{DRAIN}$  is the DRAIN pin's voltage (in V), and  $I_{PEAK}$  is the integrated boost converter's current limit (typically 220mA).

Based on the special application to select the required inductor, if  $V_{DRAIN}$  is 36V, the inductor should be greater than 49µH in 25°C temp. Consider the derating of the inductance at different temperatures and currents. It is recommended to select a minimum 68µH inductor with a saturation current exceeding 220mA and a RMS current greater than 80mA. Small-chip inductors (e.g. the LQH2MPZ series from Murata) are recommended. The LQH3NPN series inductors are also suitable.

#### Selecting the Reservoir Capacitor

Connect a minimum  $1\mu$ F capacitor, with a minimum 25V rating, from the RES pin to the DRAIN pin. A larger-value capacitor can support the IC if the DRAIN voltage is below its UVLO threshold. Calculate the minimum reservoir capacitance with Equation (8):

$$C_{\text{RES}} \ge \frac{I_{\text{GATE}} \times (t_{\text{S}} - t_{\text{ON}})}{V_{\text{RES}\_UVLO\_HYS}} \tag{8}$$

# Selecting the Electrolytic Capacitor and Ripple Voltage

During rectification, the electrolytic capacitor  $(C_{LOAD})$  reduces the load's ripple voltage. The load ripple voltage (V<sub>R</sub>) is determined by C<sub>LOAD</sub>, the source ripple frequency, the ripple amplitude, and the load current. The voltage drops with the

frequency.  $C_{LOAD}$  can be estimated with Equation (9):

$$C_{\text{LOAD}} \geq \frac{4 \times V_{\text{AC}} - V_{\text{R}}}{4 \times V_{\text{AC}} \times f \times V_{\text{R}}} \times I_{\text{LOAD}}$$

(9)

Where  $V_{AC}$  is the SOURCE voltage ripple amplitude (in V), f is the ripple frequency (in Hz),  $C_{LOAD}$  is the capacitance of the electrolytic capacitor (in F), and  $I_{LOAD}$  is the load current (in A).

If the ripple voltage (V<sub>R</sub>) is below 2V, f is 5kHz, V<sub>AC</sub> is 3V (6V<sub>PP</sub>), and I<sub>LOAD</sub> is 5A, then C<sub>LOAD</sub> is 417µF.

#### Selecting the TVS Diode

The MPQ5850 can be damaged by the negative pulse on the SOURCE pin, since the voltage of the SOURCE pin is limited to -36V. Connect a TVS diode between SOURCE and GND to The SMBJ24CA protect the part. is recommended, as it can protect the MPQ5850 from negative pulses and over-voltage conditions.

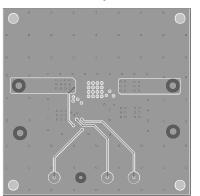

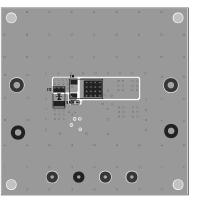

#### PCB Layout Guidelines (8)

An optimized PCB layout is very important for proper operation. A four-layer layout is strongly recommended to improve thermal performance. For the best results, refer to Figure 3 and follow the guidelines below:

- 1. Place SW close to the device with short, direct, and wide traces.

- 2. Use large copper areas to minimize conduction loss and thermal stress.

- 3. Place the ceramic input capacitors as close to the IN and GND pins as possible to minimize high-frequency noise.

- 4. Route SW away from sensitive analog areas.

- 5. Use multiple vias to connect the power planes to internal layer.

#### Note:

The recommended PCB layout is based on the circuit in Figure 4 on page 26.

Top Silk and Top Layer

Mid-Layer 1

Mid-Layer 2

Bottom Layer and Bottom Silk Figure 3: Recommended PCB Layout

### **TYPICAL APPLICATION CIRCUIT**

Figure 4: Typical Application Circuit of a 12V Automotive Battery with a 5A Load

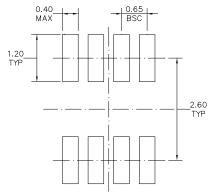

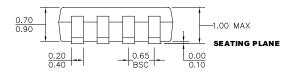

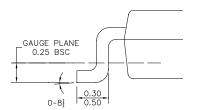

### PACKAGE INFORMATION

TSOT23-8 (2mmx3mm)

**TOP VIEW**

#### **RECOMMENDED LAND PATTERN**

SIDE VIEW

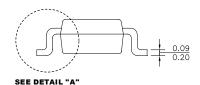

DETAIL "A"

#### NOTE:

ALL DIMENSIONS ARE IN MILLIMETERS.

PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION, OR GATE BURR.

PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

JEDEC REFERENCE IS MO-193, VARIATION BA.

DRAWING IS NOT TO SCALE.

PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

### CARRIER INFORMATION

| Part Number      | Package<br>Description | Quantity/<br>Reel | Quantity/<br>Tube | Reel<br>Diameter | Carrier<br>Tape<br>Width | Carrier<br>Tape<br>Pitch |

|------------------|------------------------|-------------------|-------------------|------------------|--------------------------|--------------------------|

| MPQ5850GJ-Z      | TSOT23-8               | 3000              | N/A               | Zin              | 8mm                      | 4mm                      |

| MPQ5850GJ-AEC1-Z |                        |                   |                   | 7in              |                          | 4mm                      |