Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

Rev. 12 — 9 June 2023

Product data sheet

## **1** General description

The MPXx5050 series piezoresistive transducer is a state-of-the-art monolithic silicon pressure sensor designed for a wide range of applications, but particularly those employing a microcontroller or microprocessor with A/D inputs. This patented, single element transducer combines advanced micromachining techniques, thin-film metallization, and bipolar processing to provide an accurate, high level analog output signal that is proportional to the applied pressure.

## 2 Feature and benefits

- 2.5 % Maximum Error over 0 ° to 85 °C

- Ideally suited for Microprocessor or Microcontroller-based systems

- Temperature compensated over –40 ° to +125 °C

- Patented silicon shear stress strain gauge

- Durable epoxy unibody element

- Easy-to-use chip carrier option

## 3 Ordering information

#### Table 1. Ordering information

| Type number   | Package  | Package                                                                                                                                      |            |  |  |  |  |  |

|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|

|               | Name     | Description                                                                                                                                  | Version    |  |  |  |  |  |

| MPX5050DP     | SENSOR4F | Pressure sensor, 5 V, 0/50 kPa, Port; Unibody package, 4 terminals; 2.54 mm pitch; 17.78 mm x 29.48 mm x 10.67 mm body                       | SOT1756-1  |  |  |  |  |  |

| MPXV5050DP    | SENSOR6F | Pressure sensor, 5 V, 0/50 kPa, Port, SO8, plastic, small outline package;<br>8 terminals; 2.54 mm pitch; 12.06 mm x 12.06 mm x 7.62 mm body | SOT1693-1  |  |  |  |  |  |

| MPXV5050GP    | SO8      | Pressure sensor, 5 V, 0/50 kPa, Port, 8 terminals; 2.54 mm pitch; 12.06 mm x 12.06 mm x 3.38 mm body body                                    | SOT1693-3  |  |  |  |  |  |

| MPXV5050GC6T1 | SO8      | Pressure sensor, 5 V, 0/540 kPa, small outline package, Port, 8 terminals; 2.54 mm pitch; 10.67 mm x 10.67 mm x 12.96 mm body                | SOT18454-1 |  |  |  |  |  |

### 3.1 Ordering options

#### Table 2. Ordering options

| ORDERING INFORMATION             |           |            |        |      |       |               |          |            |  |

|----------------------------------|-----------|------------|--------|------|-------|---------------|----------|------------|--|

| Device Name                      | Case      | # of Ports |        |      | F     | Pressure Type |          |            |  |

| Device Name                      | No.       | None       | Single | Dual | Gauge | Differential  | Absolute | Marking    |  |

| Unibody Package (MPX5050 Series) |           |            |        |      |       |               |          |            |  |

| MPX5050DP                        | 867C      |            |        | •    |       | •             |          | MPX5050DP  |  |

| Small Outline Packa              | age (MPX) | /5050 Sei  | ries)  |      |       |               |          |            |  |

| MPXV5050GP                       | 1369      |            | •      |      | •     |               |          | MPXV5050GP |  |

| MPXV5050DP                       | 1351      |            |        | •    |       | •             |          | MPXV5050DP |  |

| MPXV5050GC6T1                    | 482A      |            | •      |      | •     |               |          | MPXV5050G  |  |

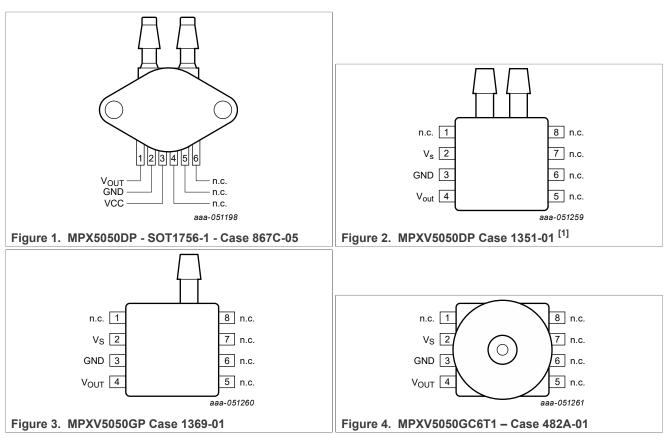

## 4 Pinning information

### 4.1 Pinning

[1] Refer to <u>Table 4</u> and style 2 in <u>Figure 13</u> in <u>Section 7 "Package outline"</u>

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

### 4.2 Pin description

#### Table 3. Pin descriptions - MPX5050DP

| Symbol           | Pin | Description      |

|------------------|-----|------------------|

| V <sub>OUT</sub> | 1   | V <sub>OUT</sub> |

| Ground           | 2   | Ground           |

| V <sub>CC</sub>  | 3   | Supply voltage   |

| N.C.             | 4   | No connection.   |

| N.C.             | 5   | No connection.   |

| N.C.             | 6   | No connection.   |

#### Table 4. Pin descriptions - MPXV5050GC6T1, MPXV5050DP, and MPXV5050GP

| Symbol           | Pin | Description      |

|------------------|-----|------------------|

| N.C.             | 1   | No connect       |

| V <sub>S</sub>   | 2   | Supply voltage   |

| Ground           | 3   | Ground           |

| V <sub>OUT</sub> | 4   | V <sub>OUT</sub> |

| N.C.             | 5   | No connect       |

| N.C.             | 6   | No connect       |

| N.C.             | 7   | No connect       |

| N.C.             | 8   | No connect       |

## 5 Limiting values

### Table 5. Limiting values <sup>[1]</sup>

| Rating                     | Symbol           | Value       | Unit |

|----------------------------|------------------|-------------|------|

| Maximum pressure (P1 > P2) | P <sub>max</sub> | 200         | kPa  |

| Storage temperature        | T <sub>stg</sub> | -40 to +125 | °C   |

| Operating temperature      | T <sub>A</sub>   | -40 to +125 | °C   |

[1] Exposure beyond the specified limits may cause permanent damage or degradation to the device.

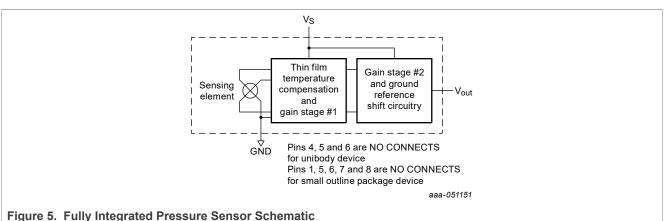

Figure 5 shows a block diagram of the internal circuitry integrated on a pressure sensor chip.

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

#### **Recommended operating conditions** 6

#### Table 6. Recommended operating conditions

(V<sub>S</sub> = 5.0 Vdc,  $T_A$  = 25 °C unless otherwise noted, P1 > P2. Decoupling circuit shown in Figure 8 required to meet electrical specifications.)

| Characteristic                                                                 | Symbol           | Min   | Тур  | Мах   | Unit              |

|--------------------------------------------------------------------------------|------------------|-------|------|-------|-------------------|

| Pressure Range <sup>[1]</sup>                                                  | P <sub>OP</sub>  | 0     | _    | 50    | kPa               |

| Supply Voltage <sup>[2]</sup>                                                  | Vs               | 4.75  | 5.0  | 5.25  | Vdc               |

| Supply Current                                                                 | Ι <sub>ο</sub>   |       | 7.0  | 10    | mAdc              |

| Minimum Pressure Offset <sup>[3]</sup> (0 °C to 85 °C)<br>@ $V_S = 5.0$ Volts  | V <sub>off</sub> | 0.088 | 0.2  | 0.313 | Vdc               |

| Full Scale Output <sup>[4]</sup> (0 °C to 85 °C)<br>@ $V_S = 5.0$ Volts        | V <sub>FSO</sub> | 4.587 | 4.7  | 4.813 | Vdc               |

| Full Scale Span <sup>[5]</sup> (0 °C to 85 °C)<br>@ V <sub>S</sub> = 5.0 Volts | V <sub>FSS</sub> |       | 4.5  |       | Vdc               |

| Accuracy <sup>[6]</sup> (0 °C to 85 °C)                                        | —                |       |      | ±2.5  | %V <sub>FSS</sub> |

| Sensitivity                                                                    | V/P              |       | 90   | _     | mV/kPa            |

| Response Time <sup>[7]</sup>                                                   | t <sub>R</sub>   |       | 1.0  | _     | ms                |

| Output Source Current at Full Scale Output                                     | I <sub>o+</sub>  |       | 0.1  | _     | mAdc              |

| Warm-Up Time <sup>[8]</sup>                                                    | _                |       | 20   | _     | ms                |

| Offset Stability <sup>[9]</sup>                                                | _                |       | ±0.5 | _     | %V <sub>FSS</sub> |

1.0 kPa (kiloPascal) equals 0.145 psi. [1]

Device is ratiometric within this specified excitation range. [2] [3]

Offset (Voff) is defined as the output voltage at the minimum rated pressure.

Full Scale Output (V<sub>FSO</sub>) is defined as the output voltage at the maximum or full rated pressure.

[4] [5] Full Scale Span (V<sub>FSS</sub>) is defined as the algebraic difference between the output voltage at full rated pressure and the output voltage at the minimum rated pressure.

[6] Accuracy (error budget) consists of the following:

Linearity: Output deviation from a straight line relationship with pressure over the specified pressure range.

Temperature Hysteresis: Output deviation at any temperature within the operating temperature range, after the temperature is cycled to and from the minimum or maximum operating temperature points, with zero differential pressure applied.

Pressure Hysteresis: Output deviation at any pressure within the specified range, when this pressure is cycled to and from the minimum or maximum rated pressure at 25 °C.

TcSpan: Output deviation over the temperature range of 0 °C to 85 °C, relative to 25 °C.

TcOffset: Output deviation with minimum pressure applied, over the temperature range of 0 °C to 85 °C, relative to 25 °C.

Variation from Nominal: The variation from nominal values, for Offset or Full Scale Span, as a percent of V<sub>FSS</sub> at 25 °C.

All information provided in this document is subject to legal disclaimers.

MPX5050

- [7] Response Time is defined as the time for the incremental change in the output to go from 10% to 90% of its final value when subjected to a specified step change in pressure.

- [8] Warm-up Time is defined as the time required for the product to meet the specified output voltage after the Pressure has been stabilized.

- [9] Offset Stability is the product's output deviation when subjected to 1000 hours of Pulsed Pressure, Temperature Cycling with Bias Test.

### 6.1 On-chip Temperature Compensation and Calibration

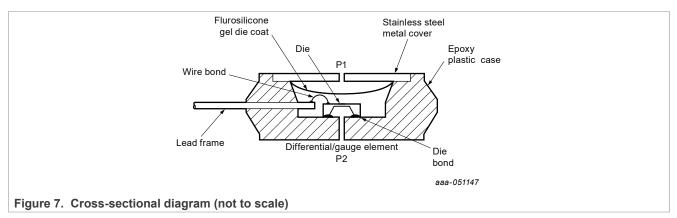

<u>Figure 7</u> illustrates the Differential/Gauge Sensing Chip in the basic chip carrier (Case 867). A fluorosilicone gel isolates the die surface and wire bonds from the environment, while allowing the pressure signal to be transmitted to the sensor diaphragm.

The MPX5050/MPXV5050G series pressure sensor operating characteristics, and internal reliability and qualification tests are based on use of dry air as the pressure media. Media, other than dry air, may have adverse effects on sensor performance and long-term reliability. Contact the factory for information regarding media compatibility in your application.

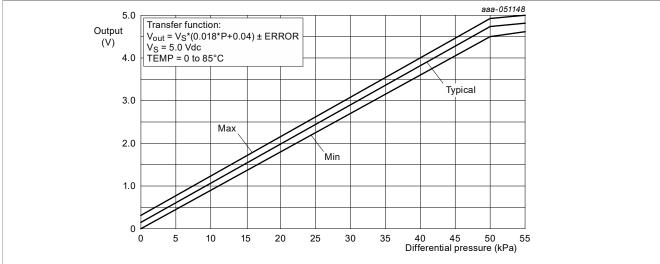

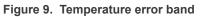

<u>Figure 6</u> shows the sensor output signal relative to pressure input. Typical, minimum, and maximum output curves are shown for operation over a temperature range of 0 °C to 85 °C using the decoupling circuit shown in <u>Figure 8</u>. The output will saturate outside of the specified pressure range.

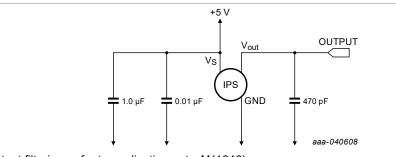

<u>Figure 8</u> shows the recommended decoupling circuit for interfacing the output of the integrated sensor to the A/D input of a microprocessor or microcontroller. Proper decoupling of the power supply is recommended.

Figure 6. Output vs. pressure differential

#### Nominal Transfer Value:

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

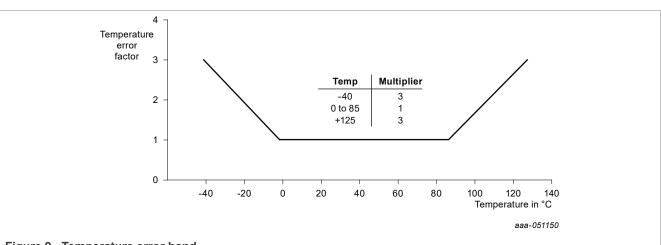

$V_{OUT} = V_S (P \times 0.018 + 0.04)$   $\pm (Pressure \ Error \times Temp. \ Factor \times 0.018 \quad V_S)$  $V_S = 5.0 \ V \ \pm 0.25 \ Vdc$

(For additional output filtering, refer to application note AN1646) Figure 8. Recommended power supply decoupling and output filtering

### 6.2 Pressure (P1)/Vacuum (P2) side identification table

NXP Semiconductors designates the two sides of the pressure sensor as the Pressure (P1) side and the Vacuum (P2) side. The Pressure (P1) side is the side containing fluorosilicone gel which protects the die from harsh media. The MPX pressure sensor is designed to operate with positive differential pressure applied, P1 > P2.

### The Pressure (P1) side may be identified by using <u>Table 7</u>:

#### Table 7. Pressure (P1) side identification

| Part Number    | Case Type | Pressure (P1) Side Identifier |

|----------------|-----------|-------------------------------|

| MPX5050DP      | 867C      | Side with Part Marking        |

| MPXV5050GP     | 1369      | Side with Port Attached       |

| MPXV5050DP     | 1351      | Side with Part Marking        |

| MPXV5050GC6/T1 | 482A      | Vertical Port Attached        |

### 7 Package outline

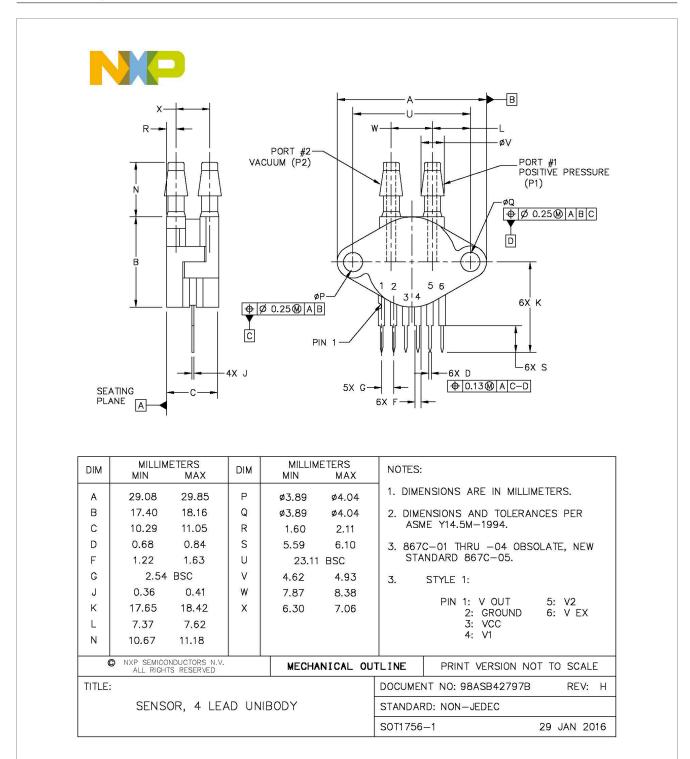

#### Figure 11. MPX5050DP - SOT17560-1 - Case 867C package outline <sup>1</sup>

<sup>1</sup> Refer to <u>Section 4.2 "Pin description"</u>, <u>Table 3</u>

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

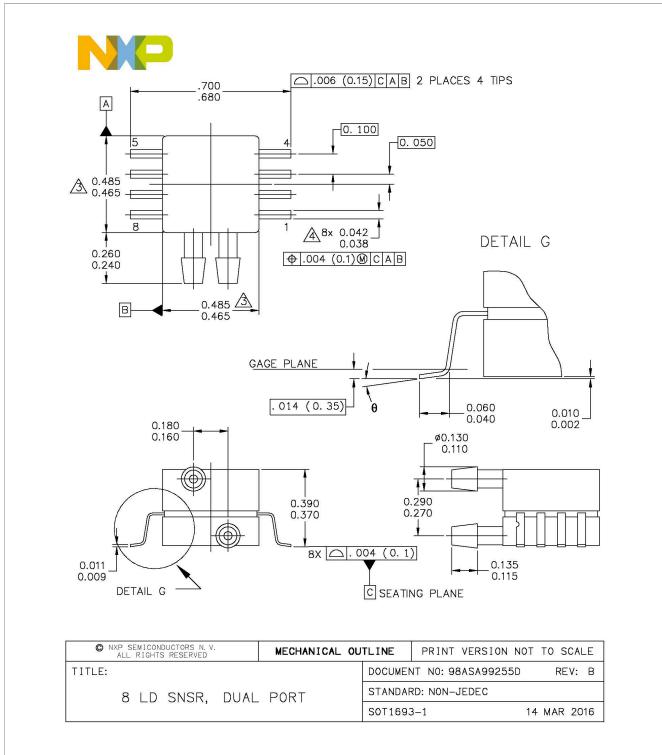

Figure 12. MPX5050DP - SOT1693-1 - Case 1351-01 package outline

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

| NOTES:                                                        |                                       |                                                        |                          |

|---------------------------------------------------------------|---------------------------------------|--------------------------------------------------------|--------------------------|

| 1. CONTROLLING DIMENSION: INCH                                |                                       |                                                        |                          |

| 2. INTERPRET DIMENSIONS AND TOL                               | ERANCES PER ASME                      | Y14.5M-                                                | 1994.                    |

| A DIMENSIONS DO NOT INCLUDE MO<br>MOLD FLASH AND PROTRUSIONS  | DLD FLASH OR PPRO<br>SHALL NOT EXCEED | TRUSIONS                                               | S.<br>R SIDE.            |

| A DIMENSION DOES NOT INCLUDE D<br>PROTRUSION SHALL BE .008 MA | AMBAR PROTRUSION<br>XIMUM.            | I. ALLOWA                                              | BLE DAMBAR               |

| STYLE 1:<br>PIN 1:<br>PIN 2:<br>PIN 3:<br>PIN 4:<br>PIN 5:    | GND<br>+Vout<br>Vs<br>-Vout           | E 2:<br>PIN 1:<br>PIN 2:<br>PIN 3:<br>PIN 4:<br>PIN 5: | Vs<br>GND<br>Vout        |

| PIN 6.<br>PIN 7:<br>PIN 7:<br>PIN 8:                          | N/C<br>N/C                            | PIN 5.<br>PIN 6:<br>PIN 7:<br>PIN 8:                   | N/C<br>N/C               |

|                                                               |                                       |                                                        |                          |

|                                                               |                                       |                                                        |                          |

|                                                               |                                       |                                                        |                          |

|                                                               |                                       |                                                        |                          |

|                                                               |                                       |                                                        |                          |

| NXP SEMICONDUCTORS N. V.<br>ALL RIGHTS RESERVED               | MECHANICAL OU                         | TLINE                                                  | PRINT VERSION NOT TO SCA |

| TITLE:                                                        | L                                     | DOCUMEN                                                | NT NO: 98ASA99255D REV:  |

| 8 LD SNSR, DUAL                                               | PORT                                  | STANDAR                                                | RD: NON-JEDEC            |

| 605049991 475369049 → 2450 930 15 1001-5                      |                                       | S0T1693                                                | 3-1 14 MAR 20            |

<sup>2</sup> Style 1 is not applicable for the parts covered by this data sheet.

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

Figure 14. MPX5050GP - SOT1693-3 - Case 1369-01 package outline

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

NOTES:

- 1. CONTROLLING DIMENSION: INCH

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

A DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PPROTRUSIONS. MOLD FLASH AND PROTRUSIONS SHALL NOT EXCEED .006 (0.152) PER SIDE.

A DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE .008 (0.203) MAXIMUM.

|      | INC                                                             | HES      | MILLIMETERS |             |         | 11      | NCHES                                 | MILLI    | METERS   |

|------|-----------------------------------------------------------------|----------|-------------|-------------|---------|---------|---------------------------------------|----------|----------|

| DIM  | MIN                                                             | MAX      | MIN         | MAX         | DIM     | MIN     | MAX                                   | MIN      | MAX      |

| А    | .300                                                            | .330     | 7.62        | 8.38        | θ       | 0.      | 7'                                    | 0.       | 7.       |

| A1   | .002                                                            | .010     | 0.05        | 0.25        | =       |         |                                       |          |          |

| ь    | .038                                                            | .042     | 0.96        | 1.07        |         |         | · · · · · · · · · · · · · · · · · · · |          |          |

| D    | .465                                                            | .485     | 11.81       | 12.32       | -       |         |                                       |          |          |

| E    | .717                                                            | BSC      | 18          | .21 BSC     | -       |         |                                       |          |          |

| E1   | .465                                                            | .485     | 11.81       | 12.32       | -       |         |                                       |          |          |

| е    | .100                                                            | BSC      | 2.          | 54 BSC      | <u></u> |         | 19 <u>11</u> 11                       |          | <u></u>  |

| F    | .245                                                            | .255     | 6.22        | 6.47        | -       |         |                                       |          |          |

| К    | .120                                                            | .130     | 3.05        | 3.30        | -       |         |                                       |          |          |

| L.   | .061                                                            | .071     | 1.55        | 1.80        | -       |         |                                       |          |          |

| м    | .270                                                            | .290     | 6.86        | 7.36        | -       |         |                                       |          |          |

| Ν    | .080                                                            | .090     | 2.03        | 2.28        | -       |         |                                       |          |          |

| Ρ    | .009                                                            | .011     | 0.23        | 0.28        | -       |         | 1 <u></u> 1                           |          |          |

| Т    | .115                                                            | .125     | 2.92        | 3.17        |         |         |                                       |          |          |

|      | © NXP SEMICONDUCTORS N. V.<br>ALL RIGHTS RESERVED MECHANICAL OU |          |             |             |         | TLINE   | PRINT VER                             | SION NOT | TO SCALE |

| TITL | -E:                                                             |          |             |             |         | DOCUMEN | NT NO: 98ASA                          | 99303D   | REV: E   |

|      | 8 LC                                                            | ) SOP, S | IDE PO      | DRT         |         | STANDAR | RD: NON-JEDE                          | С        |          |

|      |                                                                 |          |             | s of at red |         | S0T1693 | 3–3                                   | 14       | MAR 2016 |

Figure 15. MPX5050GP - SOT1693-3 - Case 1369-01 package outline notes

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

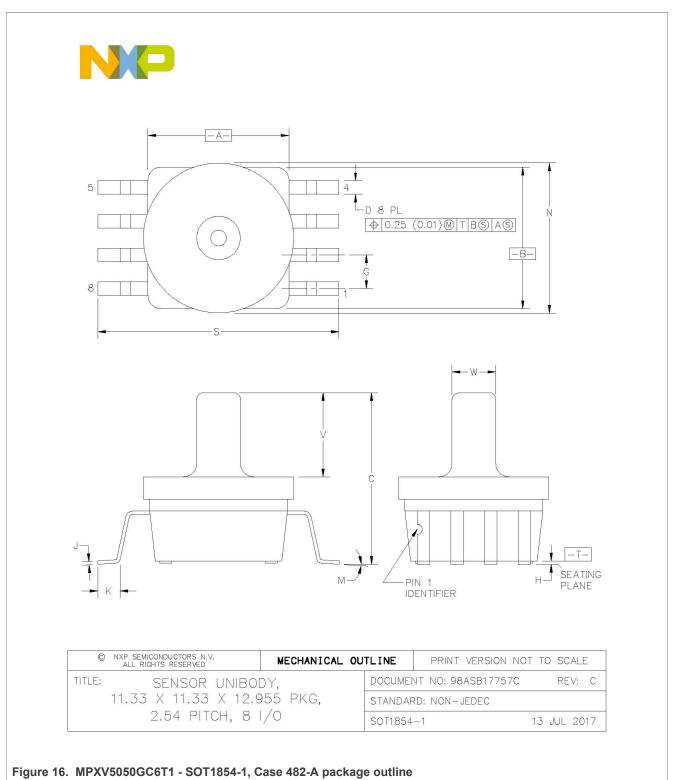

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M-1982.

- 2. CONTROLLING DIMENSION: INCH.

- 3. DIMENSION 'A' AND 'B' DO NOT INCLUDE MOLD PROTUSION.

- 4. MAXIMUM MOLD PROTRUSION 0.15 (0.006).

- 5. ALL VERTICAL SURFACES 5' TYPICAL DRAFT.

|        | INCH                       | IES         | MILLI    | METERS     |         |                    |             |

|--------|----------------------------|-------------|----------|------------|---------|--------------------|-------------|

| DIM    | MIN                        | MAX         | MIN      | MAX        |         |                    |             |

| А      | 0.415                      | 0.425       | 10.54    | 10.79      |         |                    |             |

| В      | 0.415                      | 0.425       | 10.54    | 10.79      |         |                    |             |

| С      | 0.500                      | 0.520       | 12.70    | 13.21      |         |                    |             |

| D      | 0.038                      | 0.042       | 0.96     | 1.07       |         |                    |             |

| G      | 0.100                      | BSC         | 2.54     | BSC        |         |                    |             |

| Н      | 0.002                      | 0.010       | 0.05     | 0.25       |         |                    |             |

| J      | 0.009                      | 0.011       | 0.23     | 0.28       |         |                    |             |

| К      | 0.061                      | 0.071       | 1.55     | 1.80       |         |                    |             |

| М      | 0°                         | 7°          | 0°       | 7°         |         |                    |             |

| N      | 0.444                      | 0.448       | 11.28    | 11.38      |         |                    |             |

| S      | 0.709                      | 0.725       | 18.01    | 18.41      |         |                    |             |

| V      | 0.245                      | 0.255       | 6.22     | 6.48       |         |                    |             |

| W      | 0.115                      | 0.125       | 2.92     | 3.17       |         |                    |             |

|        |                            |             |          |            |         |                    |             |

|        |                            |             |          |            |         |                    |             |

|        | NVD CENICOND               | UCTORS N.V. |          |            |         | Ĩ                  |             |

| ©      | NXP SEMICOND<br>ALL RIGHTS |             |          | MECHANICAL | OUTLINE | PRINT VERSION NO   | T TO SCALE  |

| TITLE: | SE                         | NSOR U      | INIBODY  | 1          | DOCUME  | NT NO: 98ASB17757C | REV: C      |

|        | 11.33 X                    |             |          |            | STANDA  | RD: NON-JEDEC      |             |

|        | 2.5                        | 54 PITCH    | H, 8 I/( | С          | SOT1854 | 1                  | 13 JUL 2017 |

Figure 17. MPXV5050GC6T1 - SOT1854-1, Case 482-A package outline notes

## 8 Revision history

#### Table 8. Revision history

| Document ID   | Release date                                                                                                                                                                                                            | Data sheet status                                                                                                                                                                                        | Change notice                                                                                                                                                       | Supersedes                                                                                                                  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| MPX5050 v.12  | 20230609                                                                                                                                                                                                                | Product data sheet                                                                                                                                                                                       |                                                                                                                                                                     | MPX5050 v.11                                                                                                                |

| Modifications | guidelines of NXF<br>name where appr<br>Revised all image<br><u>Section 3</u> , remove<br>MPVZ5050GW7U<br><u>Section 4</u> , section<br><u>Section 5</u> , renam<br><u>Semiconductors 6</u><br><u>Section 6</u> , renam | ropriate.<br>es to conform to NXP Se<br>ed MPX505D, MPX505C<br>J from the table.<br>rted new table.<br><u>n 4.1</u> , and <u>Section 4.2</u> , ir<br>ed "Maximum ratings" so<br>document heirarchy for o | I texts have been ad<br>miconductor image<br>GP, MPX505GP1, Ministred new sections<br>ection to "Limiting valuata sheets.<br>istics" to "Recomme<br>D and MPX5050GP | apted to the new company<br>guidelines.<br>PXV5050GC6U and<br>s.<br>llues" to conform to NXP<br>nded operating conditions". |

### 9 Legal information

### 9.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

### 9.2 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

### 9.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

## Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

Suitability for use in automotive applications - This NXP product has been qualified for use in automotive applications. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

### 9.4 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners. **NXP** — wordmark and logo are trademarks of NXP B.V.

MPX5050

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

### **Tables**

| Ordering information              | 1                                                                                                                                           |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Ordering options                  | 2                                                                                                                                           |

| Pin descriptions - MPX5050DP      | 3                                                                                                                                           |

| Pin descriptions - MPXV5050GC6T1, |                                                                                                                                             |

| MPXV5050DP, and MPXV5050GP        | 3                                                                                                                                           |

|                                   | Ordering information<br>Ordering options<br>Pin descriptions - MPX5050DP<br>Pin descriptions - MPXV5050GC6T1,<br>MPXV5050DP, and MPXV5050GP |

| Tab. 5. | Limiting values                   | 3 |

|---------|-----------------------------------|---|

| Tab. 6. | Recommended operating conditions  | 4 |

| Tab. 7. | Pressure (P1) side identification | 7 |

| Tab. 8. | Revision history1                 | 5 |

|         |                                   |   |

## **Figures**

| Fig. 1.  | MPX5050DP - SOT1756-1 - Case 867C-052   |

|----------|-----------------------------------------|

| Fig. 2.  | MPXV5050DP Case 1351-012                |

| Fig. 3.  | MPXV5050GP Case 1369-012                |

| Fig. 4.  | MPXV5050GC6T1 – Case 482A-012           |

| Fig. 5.  | Fully Integrated Pressure Sensor        |

|          | Schematic4                              |

| Fig. 6.  | Output vs. pressure differential5       |

| Fig. 7.  | Cross-sectional diagram (not to scale)5 |

| Fig. 8.  | Recommended power supply decoupling     |

|          | and output filtering6                   |

| Fig. 9.  | Temperature error band6                 |

| Fig. 10. | Pressure error band6                    |

| Fig. 11. | MPX5050DP - SOT17560-1 - Case 867C      |

| -        | package outline8                        |

| MPX5050DP - SOT1693-1 - Case 1351-01 |                                                                                                                                                                                                                                                                                                             |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| package outline                      | 9                                                                                                                                                                                                                                                                                                           |

| MPX5050DP - SOT1693-1 - Case 1351-01 |                                                                                                                                                                                                                                                                                                             |

| package outline notes                | 10                                                                                                                                                                                                                                                                                                          |

| MPX5050GP - SOT1693-3 - Case 1369-01 |                                                                                                                                                                                                                                                                                                             |

| package outline                      | 11                                                                                                                                                                                                                                                                                                          |

| MPX5050GP - SOT1693-3 - Case 1369-01 |                                                                                                                                                                                                                                                                                                             |

| package outline notes                | 12                                                                                                                                                                                                                                                                                                          |

| MPXV5050GC6T1 - SOT1854-1, Case      |                                                                                                                                                                                                                                                                                                             |

| 482-A package outline                | 13                                                                                                                                                                                                                                                                                                          |

| MPXV5050GC6T1 - SOT1854-1, Case      |                                                                                                                                                                                                                                                                                                             |

| 482-A package outline notes          | 14                                                                                                                                                                                                                                                                                                          |

|                                      | package outline<br>MPX5050DP - SOT1693-1 - Case 1351-01<br>package outline notes<br>MPX5050GP - SOT1693-3 - Case 1369-01<br>package outline<br>MPX5050GP - SOT1693-3 - Case 1369-01<br>package outline notes<br>MPXV5050GC6T1 - SOT1854-1, Case<br>482-A package outline<br>MPXV5050GC6T1 - SOT1854-1, Case |