### MR-BusiO-PHOTORELAY<sup>™</sup> BusiO Photo-Relay BOARD User Manual

## **GRAVITECH.US**

Copyright © 2007 MicroResearch GRAVITECH GROUP WWW.GRAVITECH.US

## MR-Busio-Photorelay Board User Manual

### **Description**

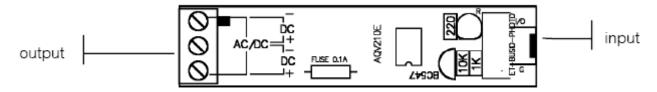

The MR-BuslO-PHOTORELAY is an experiment board for switching output by using AQV210E IC, PhotoMOS Relays. PhotoMOS Relays combined advantage of solid state relays and mechanical relays together, so efficient is perfect and better than other devices. The maximum peak value at the load is 350V, 130mA for both AC and DC.

The board can be use with MR-BusIO-MAIN board or stand-alone. PCB size is 0.63" x 2.80"

#### **Operation:**

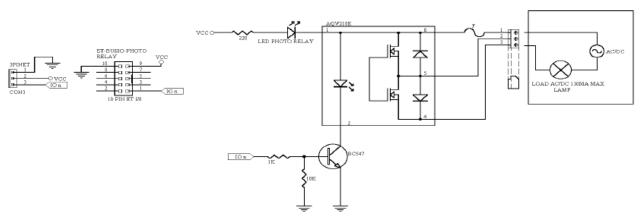

The main of the circuit is AQV210E IC. The internal of the IC consists of LED and Optoelectronic which use light for transmission. This make the input and output totally isolated.

The operation of this board starts when applying logic HIGH to an I/O pin. The voltage get divide down to turn on BC547 transistor which then activate AQV210E PhotoMOS and indicator LED. The current is then start flowing at the 3-PIN terminal block.

Please take a look at AQV210E datasheet for more information.

User can connect output AC or DC load up to 350V at 130mA. It can control various types of loads such as relays, motors, lamps and solenoids.

### **MR-BusiO-MAIN**

The MR-BusIO-MAIN is available for purchase via our website. If you don't see the item you need, please contract our sales department at <a href="mailto:sales@gravitech.us">sales@gravitech.us</a>

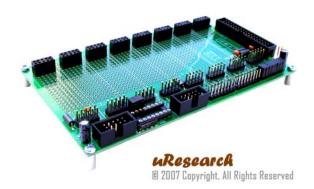

#### MR-Busio-MAIN

Experiment board which receives output signals from any microcontrollers. The signals then distribute to daughter boards for each experiment. It designed to connect directly with 10PIN MRconnect©. It is a quick and easy way to control up to 8 daughter boards.

Copyright © 2007 MicroResearch GRAVITECH GROUP WWW.GRAVITECH.US

# MR-BusiO-PHOTORELAY<sup>™</sup> BusiO Photo-Relay BOARD User Manual

FIG 1: MR-BusIO-PHOTORELAY Board Layout

FIG 2: MR-BusIO-PHOTORELAY Schematic