#### **FEATURES**

- +3.3 Volt power supply

- Fast 35ns read/write cycle (45ns for automotive temperature range)

- SRAM compatible timing

- Unlimited read & write endurance

- Data always non-volatile for >20 years at temperature

- RoHS-compliant small footprint 48-pin BGA and TSOP2 package

- All products meet MSL-3 moisture sensitivity level

- Commercial, Industrial and Automotive temperature ranges available

#### **BENEFITS**

- One memory replaces FLASH, SRAM, EEPROM, NVSRAM and BBSRAM in systems for simpler, more efficient designs

- Improves reliability by replacing battery-backed SRAM

#### INTRODUCTION

The MR5A16A is a 33,554,432-bit magnetoresistive random access memory (MRAM) device organized as 2,097,152 words of 16 bits. The MR5A16A offers SRAM compatible 35 ns read/write timing (45ns for automotive temperature option) with unlimited endurance. Data is always non-volatile for greater than 20 years. Data is automatically protected on power loss by low-voltage inhibit circuitry to prevent writes with voltage out of specification. To simplify fault tolerant design, the MR5A16A includes internal single bit error correction code with 7 ECC parity bits for every 64 data bits. The MR5A16A is the ideal memory solution for applications that must permanently store and retrieve critical data and programs quickly.

The **MR5A16A** is available in a small footprint 48-pin ball grid array (BGA) package and a 54-pin thin small outline package (TSOP Type 2). These packages are compatible with similar low-power SRAM products and other nonvolatile RAM products.

The **MR5A16A** provides highly reliable data storage over a wide range of temperatures. The product is offered with commercial temperature (0 to +70 °C), industrial temperature (-40 to +85 °C) and automotive temperature (-40 to +125°C) operating temperature options. These products are not AEC Q-100 qualified.

#### CONTENTS

| 1. | DEVICE PIN ASSIGNMENT     | 3  |

|----|---------------------------|----|

| 2. | ELECTRICAL SPECIFICATIONS | 4  |

| 3. | TIMING SPECIFICATIONS     | 7  |

| 4. | ORDERING INFORMATION      | 12 |

| 5. | MECHANICAL DRAWING        | 13 |

| 6. | REVISION HISTORY          | 14 |

| Но | w to Reach Us             | 15 |

|    |                           |    |

2M x 16 MRAM

32Mb MRAM

**MR5A16A**

### Copyright © 2023 Everspin Technologies, Inc.

1

#### **1. DEVICE PIN ASSIGNMENT**

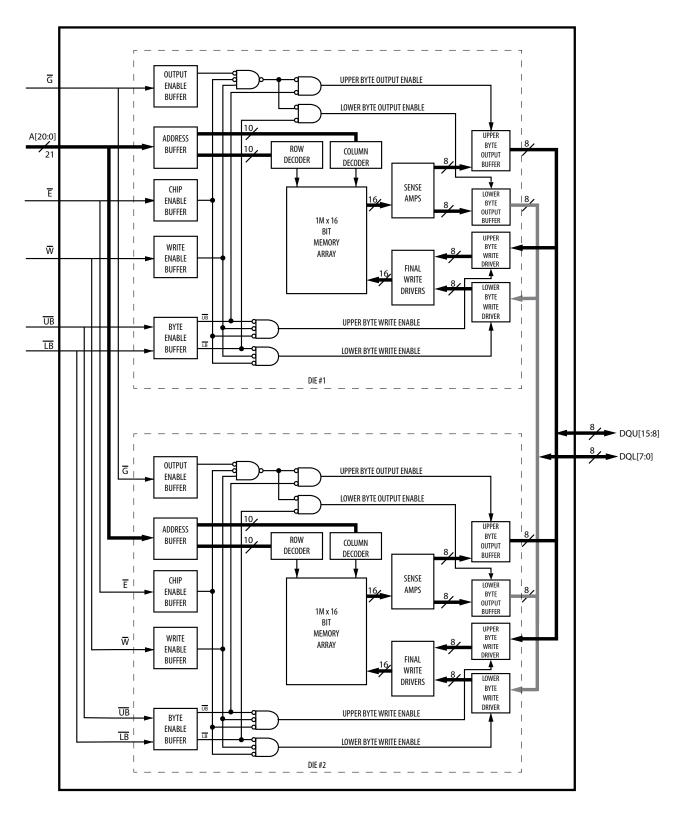

Figure 1.1 Block Diagram

2

#### **Table 1.1 Pin Functions**

| Signal Name     | Function          |

|-----------------|-------------------|

| А               | Address Input     |

| Ē               | Chip Enable       |

| W               | Write Enable      |

| G               | Output Enable     |

| UB              | Upper Byte Enable |

| LB              | Lower Byte Enable |

| DQ              | Data I/O          |

| V <sub>DD</sub> | Power Supply      |

| V <sub>ss</sub> | Ground            |

| DC              | Do Not Connect    |

| NC              | No Connection     |

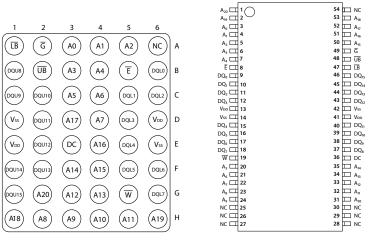

#### Table 1.2

(IB)

VDD

| Ē | <b>G</b> <sup>1</sup> | $\overline{\mathbf{W}}^{1}$ | LB <sup>1</sup> | UB <sup>1</sup> | Mode             | V <sub>DD</sub> Current             | DQL[7:0] <sup>2</sup> | DQU[15:8] <sup>2</sup> |

|---|-----------------------|-----------------------------|-----------------|-----------------|------------------|-------------------------------------|-----------------------|------------------------|

| Н | Х                     | Х                           | Х               | Х               | Not selected     | Ι <sub>SB1</sub> , Ι <sub>SB2</sub> | Hi-Z                  | Hi-Z                   |

| L | Н                     | Н                           | Х               | Х               | Output disabled  | I <sub>DDR</sub>                    | Hi-Z                  | Hi-Z                   |

| L | Х                     | Х                           | Н               | Н               | Output disabled  | I DDR                               | Hi-Z                  | Hi-Z                   |

| L | L                     | Н                           | L               | Н               | Lower Byte Read  | I <sub>DDR</sub>                    | D <sub>Out</sub>      | Hi-Z                   |

| L | L                     | Н                           | Н               | L               | Upper Byte Read  | I <sub>DDR</sub>                    | Hi-Z                  | D <sub>Out</sub>       |

| L | L                     | Н                           | L               | L               | Word Read        | I DDR                               | D <sub>Out</sub>      | D <sub>Out</sub>       |

| L | Х                     | L                           | L               | н               | Lower Byte Write | I <sub>DDW</sub>                    | D <sub>in</sub>       | Hi-Z                   |

| L | Х                     | L                           | Н               | L               | Upper Byte Write | I <sub>DDW</sub>                    | Hi-Z                  | D <sub>in</sub>        |

| L | Х                     | L                           | L               | L               | Word Write       | I <sub>DDW</sub>                    | D <sub>in</sub>       | D <sub>in</sub>        |

<sup>1</sup> H = high, L = low, X = don't care

<sup>2</sup> Hi-Z = high impedance

# **MR5A16A**

48-Pin BGA

54-Pin TSOP2

| Operating | Modes |

|-----------|-------|

|-----------|-------|

#### **Electrical Specifications**

|                 | 145                                 | he z.z Operating Condi |                   |         |                             |      |

|-----------------|-------------------------------------|------------------------|-------------------|---------|-----------------------------|------|

| Symbol          | Parameter                           | Temp Range             | Min               | Typical | Max                         | Unit |

| V <sub>DD</sub> | Power supply voltage                |                        | 3.0 <sup>1</sup>  | 3.3     | 3.6                         | V    |

| V <sub>wi</sub> | Write inhibit voltage               |                        | 2.5               | 2.7     | 3.0 <sup>1</sup>            | V    |

| V <sub>IH</sub> | Input high voltage                  |                        | 2.2               | -       | $V_{_{ m DD}}$ + 0.3 $^{2}$ | V    |

| V <sub>IL</sub> | Input low voltage                   |                        | -0.5 <sup>3</sup> | -       | 0.8                         | V    |

|                 |                                     | Commercial             | 0                 | -       | 70                          | °C   |

| T <sub>A</sub>  | Temperature under bias <sup>4</sup> | Industrial             | -40               | -       | 85                          | °C   |

|                 |                                     | Automotive             | -40               | -       | 125                         | °C   |

<sup>1</sup> There is a 2 ms startup time once  $V_{DD}$  exceeds  $V_{DD}$  (min). See **Power Up and Power Down Sequencing** below.

<sup>2</sup>  $V_{\mu\nu}(max) = V_{\mu\nu} + 0.3 V_{\mu\nu}$ ;  $V_{\mu\nu}(max) = V_{\mu\nu} + 2.0 V_{ee}$  (pulse width  $\leq 10$  ns) for  $l \leq 20.0$  mA.

<sup>3</sup>  $V_{\mu}(min) = -0.5 V_{pc}$ ;  $V_{\mu}(min) = -2.0 V_{Ac}$  (pulse width  $\leq 10$  ns) for  $I \leq 20.0$  mA.

<sup>4</sup> The ambient operature temperature rating assumes a 10% duty cycle (2 years out of 20 years life) for operating temperatures between +85°C and +125°C.

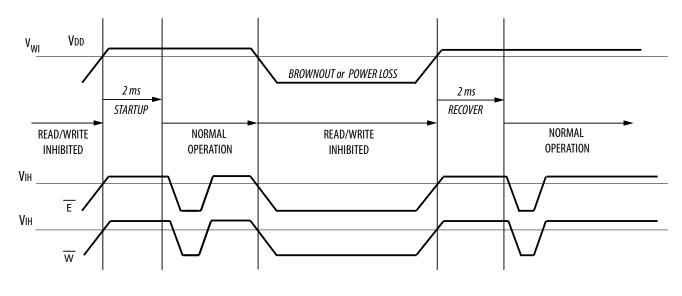

#### **Power Up and Power Down Sequencing**

supplies to stabilize.

should hold the signals high with a power-on reset signal for longer than the startup time.

observed when power returns above  $V_{pp}$  (min).

#### Figure 2.1 Power Up and Power Down Diagram

#### 2. ELECTRICAL SPECIFICATIONS

#### Absolute Maximum Ratings

This device contains circuitry to protect the inputs against damage caused by high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage greater than maximum rated voltages to these high-impedance (Hi-Z) circuits. The device also contains protection against external magnetic fields. Precautions should be taken to avoid application of any magnetic field greater than the maximum field intensity specified in the maximum ratings.

#### Table 2.1 Absolute Maximum Ratings<sup>1</sup>

| Symbol               | Parameter                                     | Conditions             | Value                     | Unit  |

|----------------------|-----------------------------------------------|------------------------|---------------------------|-------|

| $V_{DD}$             | Supply voltage <sup>2</sup>                   |                        | -0.5 to 4.0               | V     |

| V <sub>IN</sub>      | Voltage on an pin <sup>2</sup>                |                        | -0.5 to $V_{_{DD}}$ + 0.5 | V     |

| I <sub>OUT</sub>     | Output current per pin                        |                        | ±20                       | mA    |

| P <sub>D</sub>       | Package power dissipation <sup>3</sup>        |                        | 0.600                     | W     |

| т                    | Tommounture under bies                        | Commercial             | -10 to 85                 | °C    |

| T <sub>BIAS</sub>    | Temperature under bias                        | Industrial             | -45 to 95                 | °C    |

| $T_{stg}$            | Storage Temperature                           |                        | -55 to 150                | °C    |

| $T_{_{Lead}}$        | Lead temperature during solder (3 minute max) |                        | 260                       | °C    |

| $H_{_{\max\_write}}$ | Maximum magnetic field                        | During Write           | 8000                      | A/m   |

| $H_{max\_read}$      | Maximum magnetic field                        | During Read or Standby | 8000                      | A/III |

<sup>1</sup> Permanent device damage may occur if absolute maximum ratings are exceeded. Functional operation should be restricted to recommended operating conditions. Exposure to excessive voltages or magnetic fields could affect device reliability.

$^2\,$  All voltages are referenced to V\_{ss}. The DC value of V\_{IN} must not exceed actual applied V\_{DD}\, by more than 0.5V. The AC value of  $V_{IN}$  must not exceed applied  $V_{DD}$  by more than 2V for 10ns with  $I_{IN}$  limited to less than 20mA.

4

<sup>3</sup> Power dissipation capability depends on package characteristics and use environment.

# **MR5A1**

#### perating Conditions

The MRAM is protected from write operations whenever  $V_{DD}$  is less than  $V_{WI}$ . As soon as  $V_{DD}$  exceeds  $V_{DD}$  (min), there is a startup time of 2 ms before read or write operations can start. This time allows memory power

The  $\overline{E}$  and  $\overline{W}$  control signals should track  $V_{DD}$  on power up to  $V_{DD}$ - 0.2 V or  $V_{H}$  (whichever is lower) and remain high for the startup time. In most systems, this means that these signals should be pulled up with a resistor so that a signal remains high if the driving signal is Hi-Z during power up. Any logic that drives  $\overline{E}$  and  $\overline{W}$

During power loss or brownout where  $V_{DD}$  goes below  $V_{WV}$ , writes are protected and a startup time must be

### **Electrical Specifications**

# **MR5A16A**

#### Table 2.3 DC Characteristics

| Symbol              | Parameter                 | Conditions                | Min                   | Max                   | Unit |

|---------------------|---------------------------|---------------------------|-----------------------|-----------------------|------|

| l <sub>lkg(l)</sub> | Input leakage current     | All                       | -                     | ±1                    | μΑ   |

| l <sub>lkg(O)</sub> | Output leakage current    | All                       | -                     | ±1                    | μA   |

| M                   | Output louveltage         | $I_{OL} = +4 \text{ mA}$  | -                     | 0.4                   | V    |

| V <sub>ol</sub>     | Output low voltage        | I <sub>oL</sub> = +100 μA |                       | V <sub>ss</sub> + 0.2 | V    |

| Ň                   | O track birds and the res | I <sub>он</sub> = -4 mA   | 2.4                   | -                     | V    |

| V <sub>OH</sub>     | Output high voltage       | Ι <sub>οн</sub> = -100 μΑ | V <sub>DD</sub> - 0.2 | -                     | V    |

#### **Table 2.4 Power Supply Characteristics**

| Symbol           | Parameter                                                                                                                                                                         | Typical | Мах | Unit |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| I <sub>DDR</sub> | AC active supply current - read modes <sup>1</sup><br>(I <sub>OUT</sub> = 0 mA, V <sub>DD</sub> = max)                                                                            | 60      | 75  | mA   |

| I <sub>DDW</sub> | AC active supply current - write modes <sup>1</sup><br>(V <sub>DD</sub> = max)                                                                                                    | 152     | 180 | mA   |

| I <sub>SB1</sub> | AC standby current<br>$(V_{DD} = max, \overline{E} = V_{H})$<br><i>no other restrictions on other inputs</i>                                                                      | 18      | 28  | mA   |

| I <sub>SB2</sub> | CMOS standby current<br>$(\overline{E} \ge V_{DD} - 0.2 \text{ V and } V_{In} \le V_{SS} + 0.2 \text{ V or } \ge V_{DD} - 0.2 \text{ V})$<br>$(V_{DD} = \max, f = 0 \text{ MHz})$ | 10      | 18  | mA   |

<sup>1</sup> All active current measurements are measured with one address transition per cycle and at minimum cycle time.

6

## **3. TIMING SPECIFICATIONS**

| Symbol           | Parameter                 | Typical | Max | Unit |

|------------------|---------------------------|---------|-----|------|

| C <sub>In</sub>  | Address input capacitance | -       | 8   | рF   |

| C <sub>In</sub>  | Control input capacitance | -       | 8   | рF   |

| C <sub>I/O</sub> | Input/Output capacitance  | -       | 8   | рF   |

$^{1}$ f = 1.0 MHz, dV = 3.0 V, T<sub>A</sub> = 25 °C, periodically sampled rather than 100% tested.

| Parameter                                         | Value    | Unit     |

|---------------------------------------------------|----------|----------|

| Logic input timing measurement reference level    | 1.5      | V        |

| Logic output timing measurement reference level   | 1.5      | V        |

| Logic input pulse levels                          | 0 or 3.0 | V        |

| Input rise/fall time                              | 2        | ns       |

| Output load for low and high impedance parameters | See Fig  | jure 3.1 |

| Output load for all other timing parameters       | See Fig  | jure 3.2 |

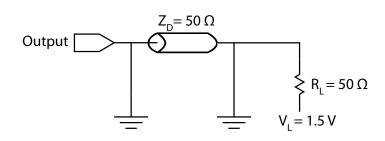

#### Figure 3.1 Output Load Test Low and High

#### Figure 3.2 Output Load Test All Others

Output 435 Ω

#### Table 3.1 Capacitance<sup>1</sup>

#### **Table 3.2 AC Measurement Conditions**

#### **Timing Specifications**

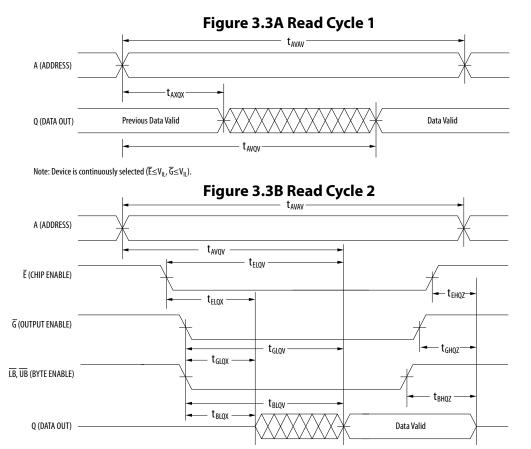

**Read Mode**

# **MR5A16A**

**Timing Specifications**

# Table 3.4 Write Cycle

| Symbol            | Parameter                                       | Min                  | Мах                  | Unit |

|-------------------|-------------------------------------------------|----------------------|----------------------|------|

| t <sub>avav</sub> | Read cycle time                                 | 35 [45] <sup>4</sup> | -                    | ns   |

| t <sub>AVQV</sub> | Address access time                             | -                    | 35 [45] <sup>4</sup> | ns   |

| t <sub>ELQV</sub> | Enable access time <sup>2</sup>                 | -                    | 35 [45] <sup>4</sup> | ns   |

| t <sub>GLQV</sub> | Output enable access time                       | -                    | 15                   | ns   |

| t <sub>BLQV</sub> | Byte enable access time                         | -                    | 15                   | ns   |

| t <sub>AXQX</sub> | Output hold from address change                 | 3                    | -                    | ns   |

| t <sub>ELQX</sub> | Enable low to output active <sup>3</sup>        | 3                    | -                    | ns   |

| t <sub>GLQX</sub> | Output enable low to output active <sup>3</sup> | 0                    | -                    | ns   |

| t <sub>BLQX</sub> | Byte enable low to output active <sup>3</sup>   | 0                    | -                    | ns   |

| t <sub>ehqz</sub> | Enable high to output Hi-Z <sup>3</sup>         | 0                    | 15                   | ns   |

| t <sub>GHQZ</sub> | Output enable high to output Hi-Z <sup>3</sup>  | 0                    | 10                   | ns   |

| t <sub>BHQZ</sub> | Byte high to output Hi-Z <sup>3</sup>           | 0                    | 10                   | ns   |

<sup>1</sup> W is high for read cycle. Power supplies must be properly grounded and decoupled, and bus contention conditions must be minimized or eliminated during read or write cycles.

Table 3.3 Read Cycle Timing <sup>1</sup>

<sup>2</sup> Addresses valid before or at the same time E goes low.

<sup>3</sup> This parameter is sampled and not 100% tested. Transition is measured ±200 mV from the steady-state voltage.

<sup>4</sup> Specification in square brackets [xx] applicable for automotive temperature range option only.

8

| Symbol                                 | Parameter                                            | Min                  | Мах | Unit |

|----------------------------------------|------------------------------------------------------|----------------------|-----|------|

| t <sub>AVAV</sub>                      | Write cycle time <sup>2</sup>                        | 35 [45] <sup>₄</sup> | -   | ns   |

| t <sub>AVWL</sub>                      | Address set-up time                                  | 0                    | -   | ns   |

| t <sub>avwh</sub>                      | Address valid to end of write ( $\overline{G}$ high) | 20 [30] <sup>4</sup> | -   | ns   |

| t <sub>avwh</sub>                      | Address valid to end of write ( $\overline{G}$ low)  | 20 [30] <sup>4</sup> | -   | ns   |

| t <sub>wlwh</sub><br>t <sub>wleh</sub> | Write pulse width ( $\overline{G}$ high)             | 15                   | -   | ns   |

| t <sub>wlwh</sub><br>t <sub>wleh</sub> | Write pulse width ( $\overline{G}$ low)              | 15                   | -   | ns   |

| t <sub>dvwh</sub>                      | Data valid to end of write                           | 10                   | -   | ns   |

| t <sub>wHDX</sub>                      | Data hold time                                       | 0                    | -   | ns   |

| t <sub>wLQZ</sub>                      | Write low to data Hi-Z <sup>3</sup>                  | 0                    | 15  | ns   |

| t <sub>wHQX</sub>                      | Write high to output active <sup>3</sup>             | 3                    | -   | ns   |

| t <sub>whax</sub>                      | Write recovery time                                  | 12                   | -   | ns   |

<sup>1</sup> All write occurs during the overlap of E low and W low. Power supplies must be properly grounded and decoupled and bus contention conditions must be minimized or eliminated during read and write cycles. If G goes low at the same time or after W goes low, the output will remain in a high impedance state. After W, E or UB/LB has been brought high, the signal must remain in steady-state high for a minimum of 2 ns. The minimum time between E being asserted low in one cycle to E being asserted low in a subsequent cycle is the same as the minimum cycle time allowed for the device.

<sup>2</sup> All write cycle timings are referenced from the last valid address to the first transition address.

<sup>3</sup> This parameter is sampled and not 100% tested. Transition is measured ±200 mV from the steady-state voltage. At any given voltage or temperate, t<sub>work</sub>(max) < t<sub>whox</sub>(min).

<sup>4</sup> Specification in square brackets [xx] applicable for automotive temperature range option only.

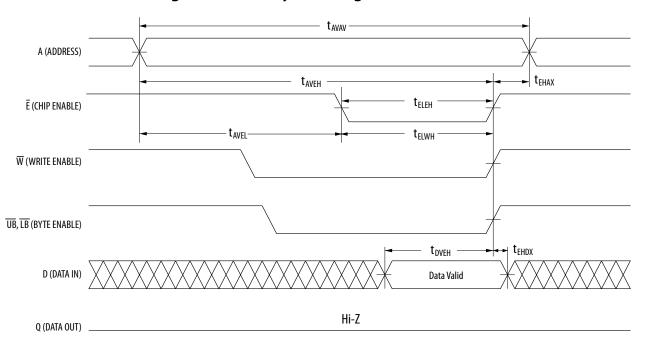

#### Figure 3.4 Write Cycle Timing 1 (W Controlled)

Copyright © 2023 Everspin Technologies, Inc.

# **MR5A16A**

| e Timing 1 (W Controlled) <sup>1</sup> |

|----------------------------------------|

|----------------------------------------|

#### **Timing Specifications**

# **MR5A16A**

#### **Timing Specifications**

#### . . . - 11 - -1\ 1

|                                        | Table 3.5 Write Cycle Timing 2 ( $\overline{E}$ C         |                      |     |      |

|----------------------------------------|-----------------------------------------------------------|----------------------|-----|------|

| Symbol                                 | Parameter                                                 | Min                  | Max | Unit |

| t <sub>AVAV</sub>                      | Write cycle time <sup>2</sup>                             | 35 [45] <sup>4</sup> | -   | ns   |

| $t_{_{AVEL}}$                          | Address set-up time                                       | 0                    | -   | ns   |

| t <sub>AVEH</sub>                      | Address valid to end of write ( $\overline{G}$ high)      | 20 [30] 4            | -   | ns   |

| t <sub>AVEH</sub>                      | Address valid to end of write ( $\overline{G}$ low)       | 20 [30] 4            | -   | ns   |

| t <sub>elen</sub><br>t <sub>elwn</sub> | Enable to end of write ( $\overline{G}$ high)             | 15                   | -   | ns   |

| t <sub>elen</sub><br>t <sub>elwn</sub> | Enable to end of write ( $\overline{G}$ low) <sup>3</sup> | 15                   | -   | ns   |

| t <sub>dveh</sub>                      | Data valid to end of write                                | 10                   | -   | ns   |

| t <sub>EHDX</sub>                      | Data hold time                                            | 0                    | -   | ns   |

| t <sub>EHAX</sub>                      | Write recovery time                                       | 12                   | -   | ns   |

<sup>1</sup> All write occurs during the overlap of E low and W low. Power supplies must be properly grounded and decoupled and bus contention conditions must be minimized or eliminated during read and write cycles. If G goes low at the same time or after W goes low, the output will remain in a high impedance state. After W, E or UB/ LB has been brought high, the signal must remain in steady-state high for a minimum of 2 ns. The minimum time between E being asserted low in one cycle to E being asserted low in a subsequent cycle is the same as the minimum cycle time allowed for the device.

<sup>2</sup> All write cycle timings are referenced from the last valid address to the first transition address.

<sup>3</sup> If E goes low at the same time or after W goes low, the output will remain in a high-impedance state. If E goes high at the same time or before W goes high, the output will remain in a high-impedance state.

<sup>4</sup> Specification in square brackets [xx] applicable for automotive temperature range option only.

#### Figure 3.5 Write Cycle Timing 2 (E Controlled)

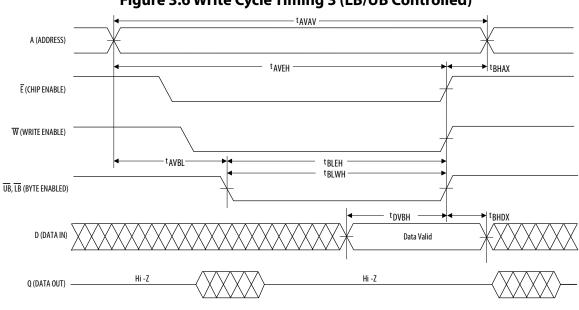

| Symbol                                 | Parameter                                            | Min                  | Max | Unit |

|----------------------------------------|------------------------------------------------------|----------------------|-----|------|

| t <sub>AVAV</sub>                      | Write cycle time <sup>2</sup>                        | 35 [45] <sup>3</sup> | -   | ns   |

| $t_{AVBL}$                             | Address set-up time                                  | 0                    | -   | ns   |

| t <sub>AVBH</sub>                      | Address valid to end of write ( $\overline{G}$ high) | 20 [30] <sup>3</sup> | -   | ns   |

| t <sub>AVBH</sub>                      | Address valid to end of write ( $\overline{G}$ low)  | 20 [30] <sup>3</sup> | -   | ns   |

| t <sub>bleh</sub><br>t <sub>blwh</sub> | Write pulse width ( $\overline{G}$ high)             | 15                   | -   | ns   |

| t <sub>bleh</sub><br>t <sub>blwh</sub> | Write pulse width ( $\overline{G}$ low)              | 15                   | -   | ns   |

| t <sub>DVBH</sub>                      | Data valid to end of write                           | 10                   | -   | ns   |

| t <sub>BHDX</sub>                      | Data hold time                                       | 0                    | -   | ns   |

| t <sub>BHAX</sub>                      | Write recovery time                                  | 12                   | -   | ns   |

<sup>1</sup> All write occurs during the overlap of E low and W low. Power supplies must be properly <u>gr</u>ounded and decoupled and bus contention conditions must be mini-mized or eliminated during read and write cycles. If G goes low at the same time or after W goes low, the output will remain in a high impedance state. After W, E or UB/LB has been brought high, the signal must remain in steady-state high for a minimum of 2 ns. If both byte control signals are asserted, the two signals must have no more than 2 ns skew between them. The minimum time between E being asserted low in one cycle to E being asserted low in a subsequent cycle is the same as the minimum cycle time allowed for the device.

- <sup>2</sup> All write cycle timings are referenced from the last valid address to the first transition address.

- <sup>3</sup> Specification in square brackets [xx] applicable for automotive temperature range option only.

Copyright © 2023 Everspin Technologies, Inc.

# **MR5A16A**

#### Figure 3.6 Write Cycle Timing 3 (LB/UB Controlled)

#### **4. ORDERING INFORMATION**

#### Figure 4.1 Part Numbering System

| MR | 5 | Α | 16 | Α | С | MA | 35                            | R |                      |                                         |

|----|---|---|----|---|---|----|-------------------------------|---|----------------------|-----------------------------------------|

|    |   |   |    |   |   |    |                               |   | Carrier              | Blank = Tray, R = Tape & Reel           |

|    |   |   |    |   |   |    |                               |   | Speed                | 35ns, 45ns                              |

|    |   |   |    |   |   |    |                               |   | Package              | MA = FBGA, YS = TSOP                    |

|    |   |   |    |   |   |    |                               |   | Temperature Range    | Blank= Commercial (0 to $+70$ °C),      |

|    |   |   |    |   |   |    | C = Industrial (-40 to +85°C) |   |                      |                                         |

|    |   |   |    |   |   |    |                               |   |                      | U= Automotive (-40 to $+125^{\circ}$ C) |

|    |   |   |    |   |   |    |                               |   | Revision             |                                         |

|    |   |   |    |   |   |    |                               |   | Data Width           | 16 = 16-bit                             |

|    |   |   |    |   |   |    |                               |   | Туре                 | A = Asynchronous                        |

|    |   |   |    |   |   |    |                               |   | Density              | 5=32Mb                                  |

|    |   |   |    |   |   |    |                               |   | Magnetoresistive RAM | 1                                       |

#### **Table 4.1 Available Parts**

| Grade                   | Temp Range Package Shipping<br>tainer |          | Shipping Con-<br>tainer | Order Part Number |

|-------------------------|---------------------------------------|----------|-------------------------|-------------------|

|                         |                                       | 48-BGA   | Trays                   | MR5A16AMA35       |

| Commercial              | 0 to 1 70 °C                          |          | Tape & Reel             | MR5A16AMA35R      |

| Commercial              | 0 to +70 °C                           | 54-TSOP2 | Trays                   | MR5A16AYS35       |

|                         |                                       | 54-130P2 | Tape & Reel             | MR5A16AYS35R      |

|                         | -40 to +85°C                          | 48-BGA   | Tray                    | MR5A16ACMA35      |

| Industrial              |                                       |          | Tape & Reel             | MR5A16ACMA35R     |

| industriai              |                                       | 54-TSOP2 | Tray                    | MR5A16ACYS35      |

|                         |                                       |          | Tape & Reel             | MR5A16ACYS35R     |

|                         |                                       | 48-BGA   | Tray                    | MR5A16AUMA45      |

|                         | 40 to 125%                            |          | Tape & Reel             | MR5A16AUMA45R     |

| Automotive <sup>1</sup> | -40 to +125°C                         | 54-TSOP2 | Tray                    | MR5A16AUYS45      |

|                         |                                       |          | Tape & Reel             | MR5A16AUYS45R     |

12

1. Not AEC Q-100 Qualified.

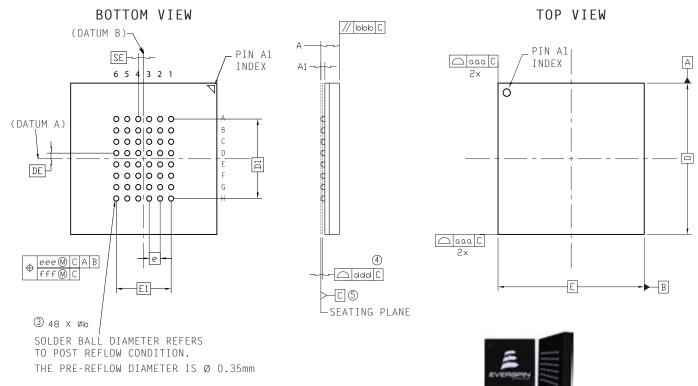

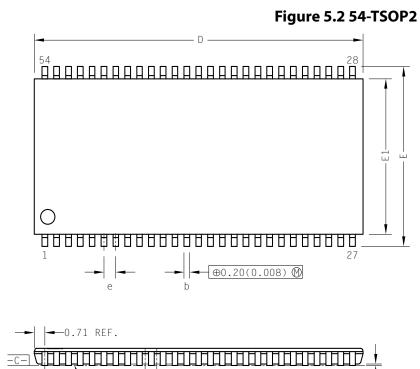

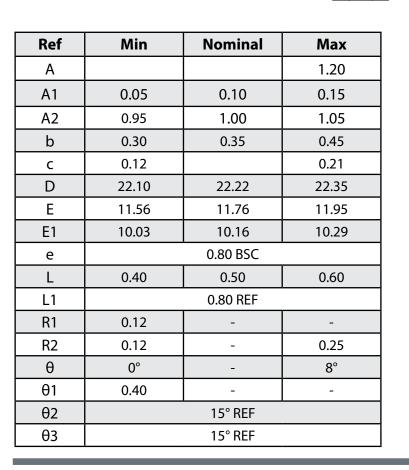

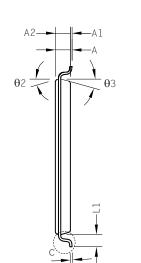

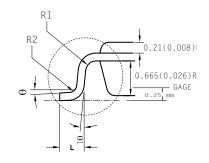

#### **5. MECHANICAL DRAWING**

| Ref | Min            | Nominal        | Мах      |  |  |  |  |

|-----|----------------|----------------|----------|--|--|--|--|

| А   | 1.19 1.27 1.35 |                |          |  |  |  |  |

| A1  | 0.22 0.27 0.32 |                |          |  |  |  |  |

| b   | 0.31           | 0.36           | 0.41     |  |  |  |  |

| D   | 10.00 BSC      |                |          |  |  |  |  |

| E   | 10.00 BSC      |                |          |  |  |  |  |

| D1  | 5.25 BSC       |                |          |  |  |  |  |

| E1  | 3.75 BSC       |                |          |  |  |  |  |

| DE  | 0.375 BSC      |                |          |  |  |  |  |

| SE  | 0.375 BSC      |                |          |  |  |  |  |

| е   | 0.75 BSC       |                |          |  |  |  |  |

|     |                |                |          |  |  |  |  |

| Ref | Toleranc       | e of, from and | position |  |  |  |  |

| 1   |                |                |          |  |  |  |  |

| Rei | Tolerance of, from and position |

|-----|---------------------------------|

| ааа | 0.10                            |

| bbb | 0.10                            |

| ddd | 0.10                            |

| eee | 0.15                            |

| fff | 0.08                            |

Copyright © 2023 Everspin Technologies, Inc.

# **MR5A16A**

#### Figure 5.1 48-FBGA

#### Print Version Not To Scale

- 1. Dimensions in Millimeters.

- 2. The 'e' represents the basic solder ball grid pitch.

- (3) 'b' is measurable at the maximum solder ball diameter in a plane parallel to datum C.

- (4) Dimension 'ddd' is measured parallel to primary datum C.

- 5 Primary datum C (seating plane) is defined by the crowns

of the solder balls.

6. Package dimensions refer to JEDEC MO-205 Rev. G.

#### **5. MECHANICAL DRAWING**

-SEATING PLANE

#### Print Version Not To Scale

- 1. Dimensions in Millimeters.

- 2. Package dimensions refer to JEDEC MS-024

#### **6. REVISION HISTORY**

| Rev | Date         | Description of Change              |

|-----|--------------|------------------------------------|

| 1.0 | Nov 20, 2019 | Released first version of the data |

| 1.1 | Jan 10, 2023 | Removed errata and restored M      |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

|     |              |                                    |

0.10 C

# **MR5A16A**

| heet |  |

|------|--|

| L-3  |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |

|      |  |