# Freescale Semiconductor, Inc.

Data Sheet: Technical Data

Document Number: MKW01Z128 Rev. 6, 04/2016

# **MKW01Z128**

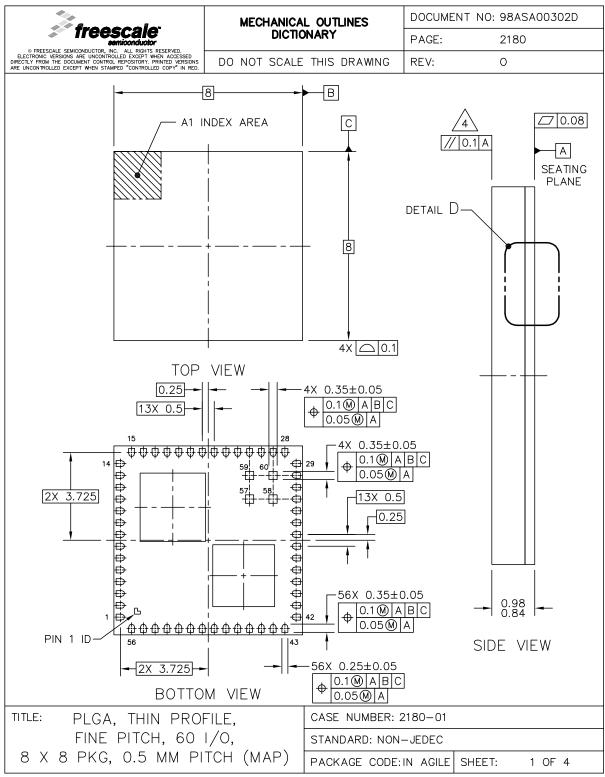

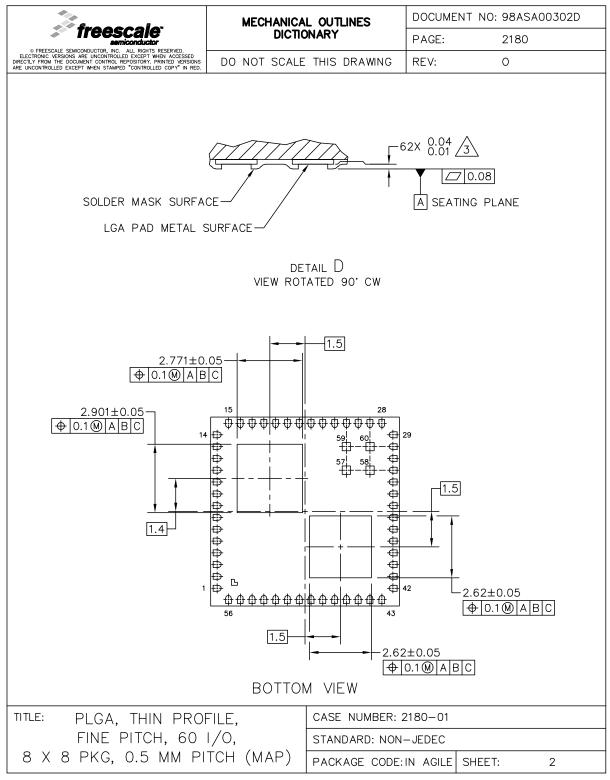

**Package Information**

#### **Ordering Information**

| Device       | Device Marking | Package |

|--------------|----------------|---------|

| MKW01Z128CHN | MKW01Z128CHN   | 60 LGA  |

# **MKW01Z128**

Highly-integrated, cost-effective single-package solution for sub-1 GHz applications

# 1 Introduction

The MKW01 device is highly-integrated, cost-effective, smart radio, sub-1 GHz wireless node solution composed of a transceiver supporting FSK, GFSK, MSK, or OOK modulations with a low-power ARM® Cortex M0+ CPU. The highly integrated RF transceiver operates over a wide frequency range including 315 MHz, 433 MHz, 470 MHz, 868 MHz, 915 MHz, 928 MHz, and 955 MHz in the license-free Industrial, Scientific and Medical (ISM) frequency bands. This configuration allows users to minimize the use of external components.

The MKW01 is targeted for the following low-power wireless applications:

- Automated Meter Reading

- Wireless Sensor Networks

- Home and Building Automation

- Wireless Alarm and Security Systems

- Industrial Monitoring and Control

Freescale supplements the MKW01 with tools and software that include hardware evaluation and

| Introduction                          | . 1                                                                                                                                                                                                                                                                                                        |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Features                              | . 2                                                                                                                                                                                                                                                                                                        |

| Software Solutions                    | . 5                                                                                                                                                                                                                                                                                                        |

| Smart Radio Sub-1 GHz Wireless Node   | . 5                                                                                                                                                                                                                                                                                                        |

| MKW01 Pin Assignments and Connections | 9                                                                                                                                                                                                                                                                                                          |

| System and Power Management           | 15                                                                                                                                                                                                                                                                                                         |

| Development Environment               | 20                                                                                                                                                                                                                                                                                                         |

| System Electrical Specification       | 20                                                                                                                                                                                                                                                                                                         |

| Typical Applications Circuit          | 25                                                                                                                                                                                                                                                                                                         |

| Mechanical Drawings                   | 28                                                                                                                                                                                                                                                                                                         |

| ppendix AMKW01 MCU Section Data Sheet | 30                                                                                                                                                                                                                                                                                                         |

|                                       | Features         Software Solutions         Smart Radio Sub-1 GHz Wireless Node         MKW01 Pin Assignments and Connections         System and Power Management         Development Environment         System Electrical Specification         Typical Applications Circuit         Mechanical Drawings |

development boards, software development IDE and applications, drivers, custom PHY usable with Freescale's IEEE 802.15.4 compatible MAC and SMAC.

# 2 Features

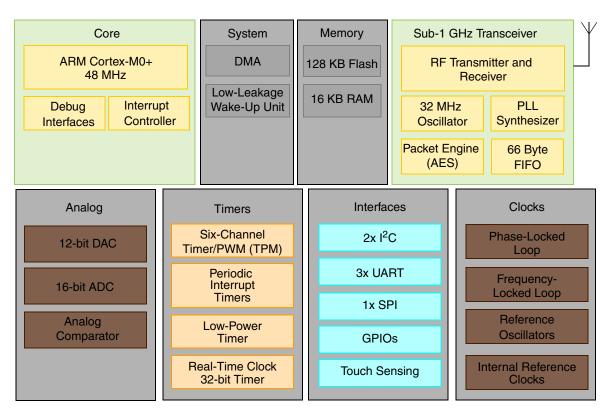

This section provides a simplified block diagram and highlights MKW01 features.

## 2.1 Block Diagram

Figure 1 shows a simplified block diagram of the MKW01.

Kinetis MKW01 Wireless MCU

## 2.2 Features Summary

#### • **RF Transceiver Features**

- Operating Voltage from 1.8V to 3.6V.

- Programmable bit rate up to 600kbps (FSK)

- High Sensitivity: down to -120 dBm at 1.2 kbps

- High Selectivity: 16-tap FIR Channel Filter

- Bullet-proof front end: IIP3 = -18 dBm, IIP2 = +35 dBm, 80 dB Blocking Immunity, no Image Frequency response

- Low current: Rx = 16mA, 100nA register retention

- Programmable Pout : -18 to +17 dBm in 1 dB steps

- Constant RF performance over voltage range of chip

- Fully integrated synthesizer with a resolution of 61 Hz

- FSK, GFSK, MSK, GMSK and OOK modulations

- Built-in Bit Synchronizer performing Clock recovery

- Incoming Sync Word Recognition

- Automatic RF Sense with ultra-fast AFC

- Packet engine with CRC, AES-128 encryption and 66-byte FIFO

- Built-in temperature sensor and Low battery indicator

- 32 MHz crystal oscillator clock source

- Dedicated I/O's for connection with an external 32 kHz crystal

- Can be configured to be compliant with the relevant sections of numerous world-wide standards, including but not limited to: ARIB-T108 and T67, FCC 15.231, 15.247, and 15.249, EN54-25, and ETSI 300 220.

MCU Features

System:

- 48 MHz Max. Central Processor Unit (CPU) frequency

- 24 MHz Max. Bus frequency

- Vectored Interrupt Controller (NVIC) with 32 core-vectored interrupts with 4 programmable interrupt priority levels

- Asynchronous Wake-up Interrupt Controller (AWIC)

- 4 channel Direct Memory Access (DMA)

- DMA request multiplex

- Non Maskable Interrupt (NMI)

- COP Watchdog

- Low leakage Wake-up Unit (LLWU)

- Debug and Trace

- 2-pin Serial Wire Debug (SWD)

- 80-bit wide ID number

#### Memory:

- 128 KB P-Flash with 64 byte flash cache

- 16 KB RAM

Clocks:

— External crystal oscillator or resonator:

- 32 40 kHz low range, low power or full swing

- 3 MHz 32 MHz high range, low power or full swing

- DC 48 MHz external square wave input clock

- Internal clock references:

- 31.25 kHz to 39.063 kHz oscillator with +/- 1.5% max. deviation from 0 to +70°C

- 4 MHz oscillator with +/- 3% max. deviation across temperature

- 1 kHz oscillator

- Phase Locked Loop (PLL) with up to 100 MHz VCO

- Frequency Locked Loop (FLL):

- Low range: 20 25 MHz

- Mid range: 40 48 MHz

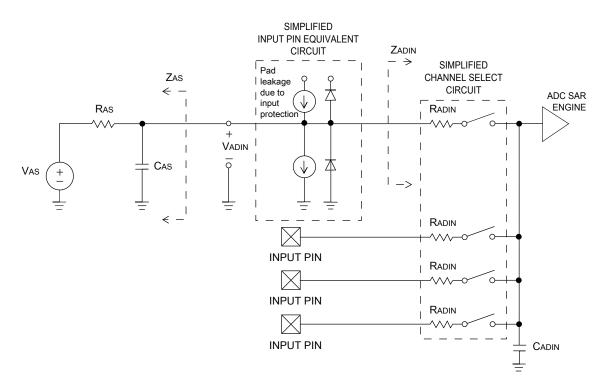

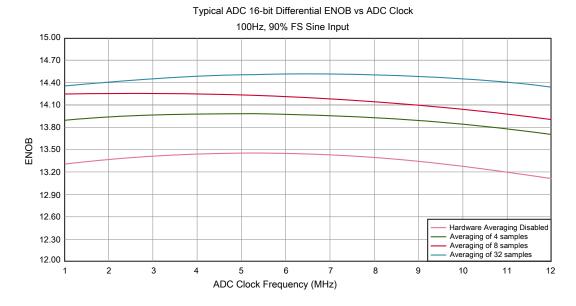

Analog:

— Power Management Controller (PMC) with low voltage warning (LVW) and detect with selectable trip points.

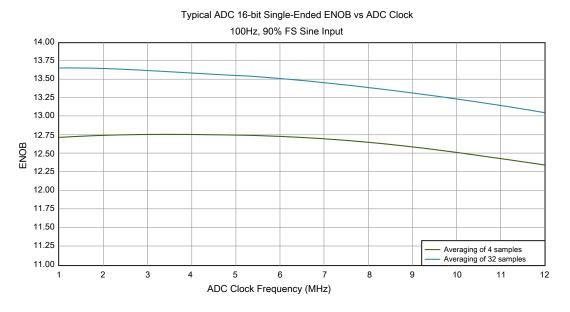

- 16-bit analog to digital converter

- 11 single ended channels available

- 2 status, control and results registers

- DMA support

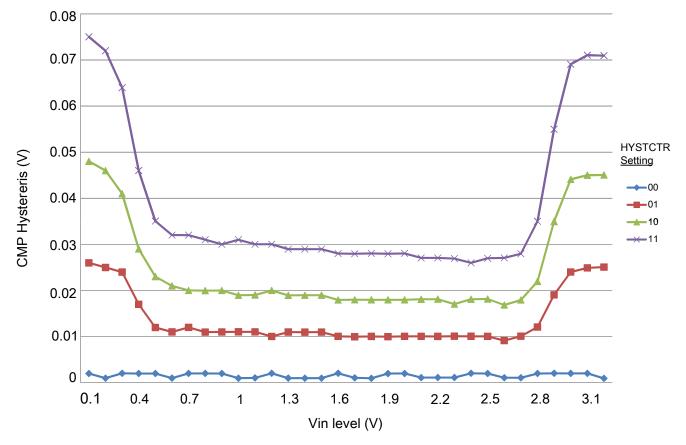

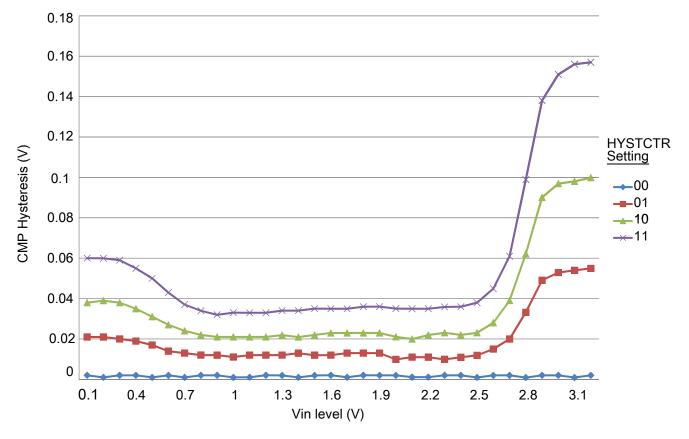

- 1 High Speed Comparator (HSCMP) with internal 6-bit digital to analog converters (DAC)

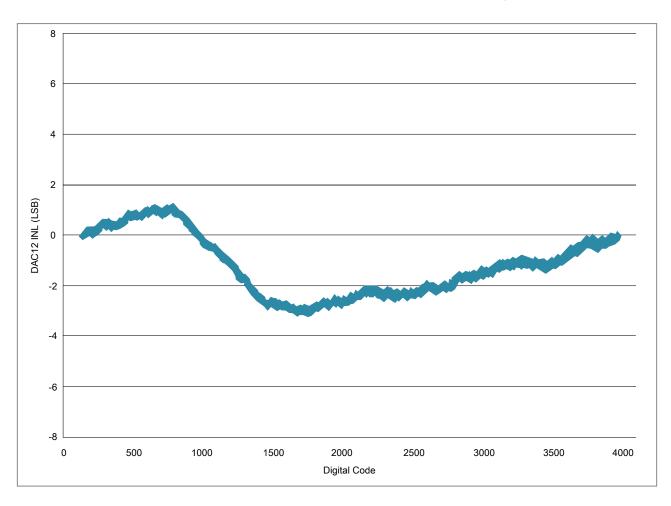

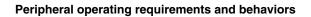

- One 12-bit DAC with DMA support and 2 word data buffer

Timers:

- Six channel Timer/PWM (TPM)

- Periodic interrupt timers

- 16-bit low-power timer (LPTMR) can be configured to operate as a time counter or as a pulse counter, across all power modes, including the low-leakage modes

- Real-time clock 32-bit timer

Wired Communication Interface:

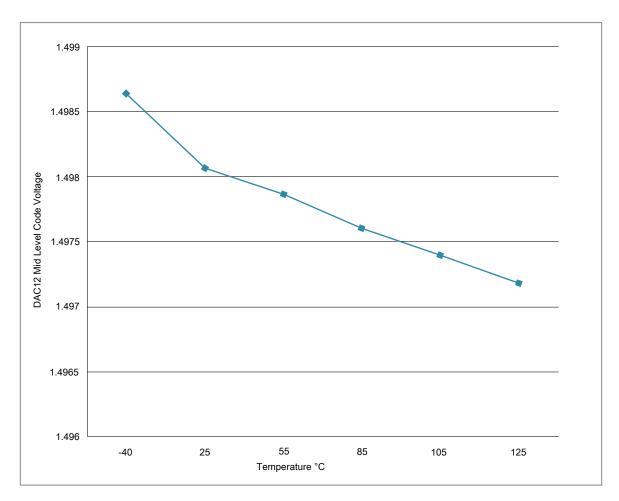

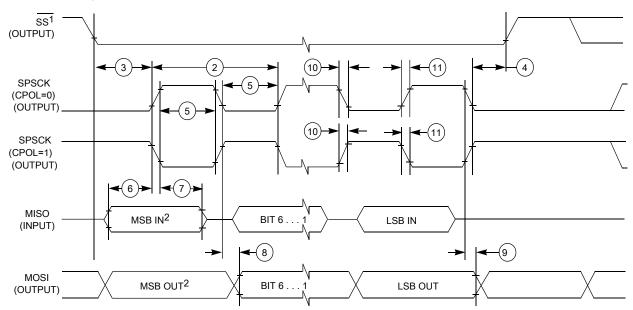

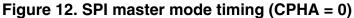

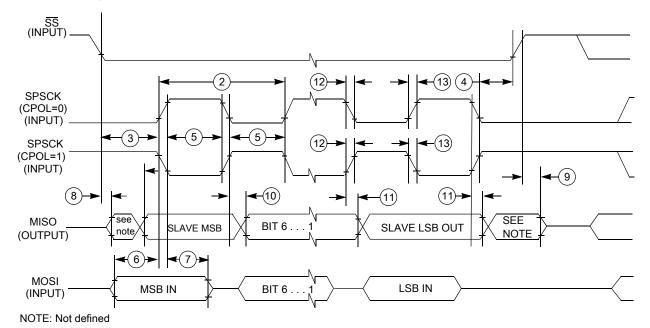

- One Serial Peripheral Interface (SPI) available externally

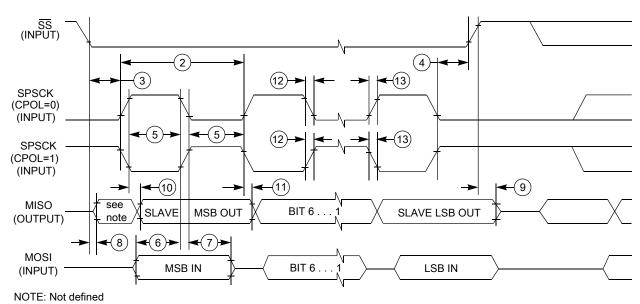

- Two Inter-Integrated Circuits (I<sup>2</sup>C) with DMA support

- Three Universal Asynchronous Receiver / Transmitter (UART) with DMA Support

- UART0 supports standard features plus:

- TxD pin can be configured as pseudo open drain for 1-wire half-duplex

- x4 to x32 oversampling

- Functional in VLPS mode

- LIN slave operation

- UART1 and UART2 support standard features

Human Machine Interface (HMI)

- General Purpose Input/Output (GPIO) supporting:

- Default to disabled (no leakage)

- 4 pins with 18 mA high current drive capability

- Hysteresis and configurable pull up device on all input pins

- Slew rate and drive strength fixed on all output pins

- Single cycle GPIO control via IOPORT

- Touch Sensor Inputs (TSI)

- 9-channel

- Selectable single channel wakeup source available in all modes

- DMA support

- Pin Interrupt

1.8 V to 3.6 V operating voltage with on-chip voltage regulators

Temperature range of -40°C to 85°C

60-pin LGA (8x8 mm) package

# 3 Software Solutions

Freescale will support the MKW01x128 platform with several software solutions:

- A radio utility GUI will be available that allows testing of various features and setting registers. A connectivity test firmware will allow a limited set of testing controlled with a terminal emulator on any computer.

- SMAC (Simple Media Access Controller) This codebase provides simple communication and test apps based on drivers/PHY utilities available as source code. This environment is useful for hardware and RF debug, hardware standards certification, and developing proprietary applications.

- Additional software will be available through 3rd party providers.

# 4 Smart Radio Sub-1 GHz Wireless Node

The MKW01 brings together a transceiver chip and an MCU chip on a single substrate to provide a small footprint, cost-effective sub-1 GHz wireless node. The transceiver is controlled by the MCU through a dedicated SPI interface. The SPI bus interface and some status signals are connected in-package the substrate to eliminate the need for external connections. The SPI supports bit order swapping providing hardware support for bit endianess reducing processing overhead.

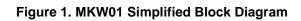

# 4.1 RF Transceiver

The transceiver (see Figure 2) is a single-chip integrated circuit ideally suited for today's high performance ISM band RF applications. Its advanced features set, including state of the art packet engine, greatly

simplifies system design while the high level of integration reduces the external RF component bill of material (BOM) to a handful of passive de-coupling and matching components. It is intended for use as a high-performance, low-cost FSK, GFSK, MSK, GMSK, and OOK RF transceiver for robust, frequency agile, half-duplex bi-directional RF links.

The MKW01 is intended for applications over a wide frequency range, including the 433 MHz, the 868 MHz European, and the 902-928 MHz North American ISM bands. Coupled with a link budget in excess of 135 dB, the transceiver advanced system features include a 66 byte TX/RX FIFO, configurable automatic packet handler, listen mode, temperature sensor and configurable DIO's which greatly enhance system flexibility while at the same time significantly reducing MCU requirements. The transceiver complies with both ETSI and FCC regulatory requirements.

Figure 2. MKW01 Transceiver Block Diagram

The major RF communication parameters of the MKW01 transceiver are programmable and most can be dynamically set. This feature offers the unique advantage of programmable narrow-band and wide-band communication modes without the need to modify external components. The transceiver is also optimized for low power consumption while offering high RF output power and channelized operation.

## 4.2 ARM ® 32-bit Cortex M0+ CPU

The in-package MCU integrated circuit features an ARM ® Cortex M0+ CPU, up to 16 KB RAM, 128 KB Flash memory, and a rich set of peripherals (see Section 2.2, "Features Summary"). The RF transceiver is controlled through the MCU SPI port which is dedicated to the RF device interface. Two of the transceiver status IO lines are also directly connected to the MCU GPIO to monitor the transceiver operation. In addition, the transceiver reset and additional status can be connected to the MCU through external connections.

Operational modes of the MKW01 are determined by the software running on the MCU. The MCU itself has a run mode as well as an array of low power modes that are coordinated by the PMC. The MCU in turn set the operational modes of the transceiver which include sleep, standby, and radio operational modes.

Two common application scenarios are:

- Low power, battery-operated standalone wireless node a common example of this configuration would be a remote sensor monitor. The wireless node programmed for standalone operation, typically has a low active-mode duty cycle, and is designed for long battery life, i.e., lowest power.

- Communication channel to a higher level controller in this example, the wireless node implements the lower levels of a communications stack and is subordinate to the primary controller. Typically the MKW01 is connected to the controller through a command channel implemented via a UART/SCI port or other serial communication port.

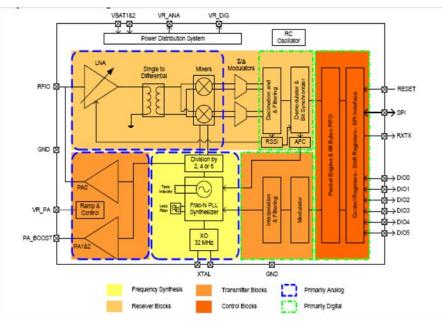

## 4.3 System Clock Configuration

The MKW01 device allows for various system clock configurations:

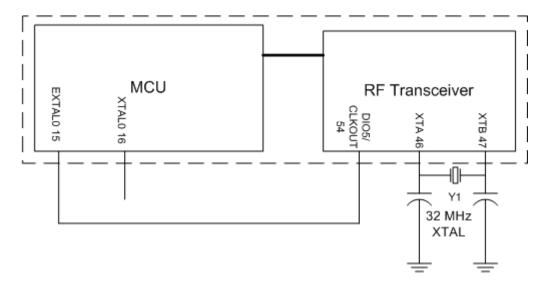

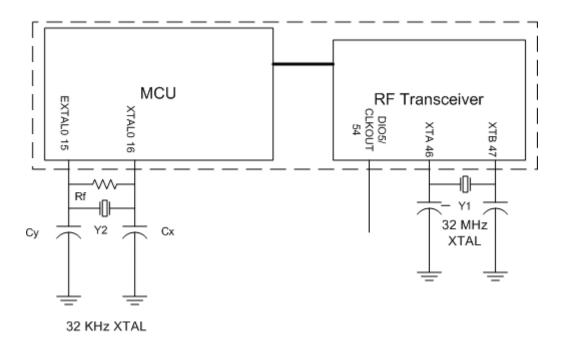

- Pins 46 & 47 are provided to input a 32 or 30 MHz crystal for the transceiver reference clock source (required) as shown in Figure 3.

- The transceiver can be programmed to provide a programmable frequency clock output (DIO5 which alternates as CLKOUT, pin 54) that can be used as an external source to the CPU (see Figure 3 and Figure 4). As a result, a single crystal system clock solution is possible where the transceiver reference clock source. Routing CLKOUT to the MCU without dividing it is recommended, but it can be divided by 2, 4, 8, 16 and 32.

- The MCU provides a trimmable internal reference clock and also supports an external clock source. An optional on-chip frequency locked loop (FLL) can be used with either clock source to support a CPU clock as high as 48 MHz at 3.6 V.

- Pins 16 and 15 are available to provide an external 32.768 kHz external clock source for the MCU.

Figure 3. MKW01 Single Crystal System Clock Connection

Figure 4. MKW01 Two Crystal System Clock Connection

# 5 MKW01 Pin Assignments and Connections

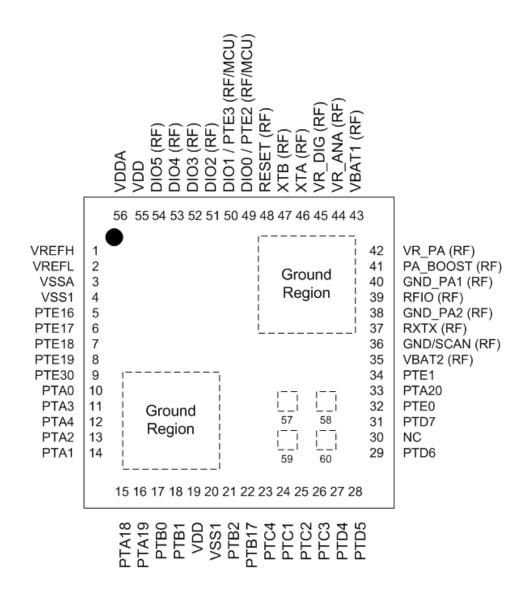

Figure 5 shows the MKW01 pinout.

2 ground regions and 4 pins on bottom:

| 57 | MISO / PTC7 (RF/MCU) |

|----|----------------------|

|    |                      |

- 58 NSS / PTD0 (RF/MCU)

- 59 SCK / PTC5 (RF/MCU)

- 60 MOSI / PTC6 (RF/MCU)

Figure 5. MKW01 Pinout (Top View)

MKW01Z128 Datasheet, Rev. 6, 04/2016

# 5.1 Pin Definitions

Table 1 details the MKW01 pinout and functionality.

| Pin | Pin Name <sup>1</sup>                                                         | Туре                      | Description                                                                                                                                                                                                    | Functionality     |

|-----|-------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1   | VREFH                                                                         | Input                     | MCU high reference voltage for ADC                                                                                                                                                                             |                   |

| 2   | VREFL                                                                         | Input                     | MCU low reference voltage for ADC                                                                                                                                                                              |                   |

| 3   | VSSA                                                                          | Power Input               | MCU ADC Ground                                                                                                                                                                                                 | Connect to ground |

| 4   | VSS                                                                           | Power Input               | MCU Ground                                                                                                                                                                                                     | Connect to ground |

| 5   | PTE16/ADC0_DP1/ADCO_S<br>E1/SPI0_PCS0/TPM/UART2_<br>TX                        | Digital Input /<br>Output | MCU Port E Bit 16 / ADC0 Single Ended<br>analog channel input DP1/ ADC0 Single<br>Ended analog channel input SE1 / SPI<br>module 0 PCS0 / TPM module Clock In 0 /<br>UART2_TX                                  |                   |

| 6   | PTE17/ADC0_DM1/ADCO_S<br>E5a/SPI0_SCK/<br>TPM_CLKIN1/UART2_RX/<br>LPTMR0_ALT3 | Digital Input /<br>Output | MCU Port E Bit 17 / ADC0 Single Ended<br>analog channel input DM1/ ADC0 Single<br>Ended analog channel input 5a / SPI<br>module 0 SCK / TPM module Clock In 1 /<br>UART2_RX / Low Power Timer Module 0<br>ALT3 |                   |

| 7   | PTE18/ADC0_DP2/ADC0_SE<br>2/SPI0_MOSI/IIC0_SDA/SPI0<br>_MISO                  | Digital Input /<br>Output | MCU Port E Bit 18 / ADC0 Single Ended<br>analog channel input DP2/ ADC0 Single<br>Ended analog channel input 2 / SPI module<br>0 MOSI / IIC0 Bus Data / SPI module 0<br>MISO                                   |                   |

| 8   | PTE19/ADC0_DM2/<br>ADC0_SE6a/SPI0_MISO<br>/IIC0_SCL/ SPI0_MOSI                | Digital Input /<br>Output | MCU Port E Bit 19 / ADC0 Single Ended<br>analog channel input DM2/ ADC0 Single<br>Ended analog channel input 6a / SPI<br>module 0 MISO / IIC0 Bus Clock / SPI<br>module 0 MOSI                                 |                   |

| 9   | PTE30/DAC0_OUT/<br>ADCO_SE23/<br>CMP0_IN4/TPM0_CH3/TPM_<br>CLKIN1             | Digit-I Input /<br>Output | MCU Port E Bit 30 / DAC0 Output/ ADC0<br>Single Ended analog channel input 23 /<br>Comparator 0 Analog Voltage Input 4/ TPM<br>Timer module 0 Channel 3 / TPM module<br>Clock In 1                             |                   |

| 10  | PTA0/SWD_CLK/TSI0_CH1/T<br>PM0_CH5                                            | Digital Input /<br>Output | MCU Port A Bit 0 / Serial Wire Data Clock<br>/ Touch Screen Interface Channel 1/ TPM<br>module 0 Channel 5                                                                                                     |                   |

| 11  | PTA3/SWD_DIO/TSI0_CH4/<br>IIC1_SCL/TPM0_CH0                                   | Digital Input /<br>Output | MCU Port A Bit 3 / Serial Wire Data DIO /<br>Touch Screen Interface Channel 4 / IIC1<br>Bus Clock / TPM module 0 Channel 0                                                                                     |                   |

| 12  | PTA4/NMI_b/TSI0_CH5/<br>IIC1_SDA/TPM0_CH1                                     | Digital Input /<br>Output | MCU Port A Bit 4/ / Non Maskable<br>Interrupt_ b/Touch Screen Interface<br>Channel 5 /IIC1 Bus Data / TPM module 0<br>Channel 1                                                                                |                   |

#### Table 1. Pin Function Description (Sheet 1 of 5)

| Pin | Pin Name <sup>1</sup>                                                | Туре                                        | Description                                                                                                                                                                                                     | Functionality                |

|-----|----------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 13  | PTA2/TSI0_CH3/UART0_TX/<br>TPM2_CH1                                  | Digital Input /<br>Output                   | MCU Port A Bit 2/Touch Screen Interface<br>Channel 3/UART module 0 Transmit / TPM<br>module 2 Channel 1                                                                                                         |                              |

| 14  | PTA1/TSI0_CH2/UART0_RX/<br>TPM2_CH0                                  | Digital Input /<br>Output                   | MCU Port A Bit 1/Touch Screen Interface<br>Channel 2/UART module 0 Receive / TPM<br>module Channel 0                                                                                                            |                              |

| 15  | PTA18/EXTAL0/UART1_RX/<br>TPM_CLKIN0                                 | Digital Input /<br>Output                   | MCU Port A Bit 18 / EXTAL0/ UART<br>module 1 Receive / TPM module Clock In 0                                                                                                                                    |                              |

| 16  | PTA19/XTAL0/UART1_TX/TP<br>M_CLKIN1/LPTMR0_ALT1                      | Digital Input /<br>Output                   | MCU Port A Bit 19 / XTAL0/ UART module<br>1 Transmit / TPM module Clock In 1<br>/Low Power Timer module 0 ALT1                                                                                                  |                              |

| 17  | PTB0/ADC0_SE8/TSI0_CH0/<br>LLWU_P5/IIC0_SCL/<br>TPM1_CH0             | Digital Input /<br>Output                   | MCU Port B Bit 0 / ADC0 Single Ended<br>analog channel input SE8 / Touch Screen<br>Interface Channel 0/ Low Leakage Wake<br>Up Port 5 / IIC0 Bus Clock / TPM module 1<br>Channel 0                              |                              |

| 18  | PTB1/ADCO_SE9/TSI0_CH6/<br>IIC0_SDA/ TPM1_CH1                        | Digital Input /<br>Output                   | MCU Port B Bit 1 / ADC0 Single Ended<br>analog channel input SE9 / Touch Screen<br>Interface Channel 6 / IIC0 Bus Data / TPM<br>module 1 Channel 1                                                              |                              |

| 19  | VDD                                                                  | Power Input                                 | MCU VDD supply input                                                                                                                                                                                            | Connect to system VDD supply |

| 20  | VSS                                                                  | Power Input                                 | MCU Ground                                                                                                                                                                                                      | Connect to ground            |

| 21  | PTB2/ADC0_SE12/TSI0_CH7<br>/IIC0_SCL/TPM2_CH0                        | Digital<br>Input/Output                     | MCU Port B Bit 2 / ADC0 Single Ended<br>analog channel input SE12 / Touch Screen<br>Interface Channel 7 / IIC0 Bus Clock / TPM<br>Timer module 2 Channel 0                                                      |                              |

| 22  | PTB17/TSI0_CH10/SPI1_MIS<br>O/UART0_TX/TPM_CLKIN1/<br>SPI1_MOSI      | Digital<br>Input/Output                     | MCU Port B Bit 17 / Touch Screen Interface<br>Channel 10/SPI1 MOSI or MISO/UART0<br>TX / TPM timer clock                                                                                                        |                              |

| 23  | PTC4/LLWU_P8/SPI0_PCS0/<br>UART1_TX/TPM0_CH3                         | Digital Input /<br>Output                   | MCU Port C bit 4 / Low leakage Wake Up<br>port 8 / SPI0 Chip Select / UART1 TX /<br>TPM Timer module 0 channel 3                                                                                                |                              |

| 24  | PTC1/ADC0_SE15/TSI0_CH1<br>4/LLWU_P6/RTC_CLKIN/<br>IIC1_SCL/TPM0_CH0 | Digital Input<br>Output /<br>Analog Input   | MCU Port C Bit 1 /ADC0 Single Ended<br>analog channel input SE15/ Touch Screen<br>Interface Channel 14/ Low Leakage Wake<br>Up Port 6 / Real Time Counter Clock Input/<br>IC1 Bus Clock/ TPM module 0 Channel 0 |                              |

| 25  | PTC2/ADC0_SE11/TSI0_CH1<br>5/IIC1_SDA/TPM0_CH1                       | Digital Input /<br>Output /<br>Analog Input | MCU Port C Bit 2 / ADC0 Single Ended<br>analog channel input SE11// Touch Screen<br>Interface Channel 15 / IIC1 Bus Data / TPM<br>module 0 Channel 1                                                            |                              |

#### Table 1. Pin Function Description (Sheet 2 of 5)

| Pin | Pin Name <sup>1</sup>                                        | Туре                                        | Description                                                                                                                                                  | Functionality                |

|-----|--------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 26  | PTC3/LLWU_P7/UART1_RX/<br>TPM0_CH2/CLKOUTa                   | Digital Input /<br>Output                   | MCU Port C Bit 3 / Low Leakage Wake Up<br>Port 7 / UART module 1 Receive / TPM<br>module 0 Channel 2/ Clock OutA                                             |                              |

| 27  | PTD4/LLWU_P14/SPI1_PCS0<br>/UART2_RX/TPM0_CH4                | Digital Input /<br>Output                   | MCU Port D Bit 4 / Low Leak Wake Up Port<br>14/ SPI module 1 PCS0 / UART2 Receiver<br>input / TPM module 0 Channel 4                                         |                              |

| 28  | PTD5/ADC0_SE6b/SPI1_SC<br>K/UART2_TX/TPM0_CH5                | Digital Input /<br>Output /<br>Analog Input | MCU Port D bit 5 / ADC0 Single Ended<br>analog channel input SE6b / SPI1 clock /<br>UART2 TX / TPM module 0 Channel 5                                        |                              |

| 29  | PTD6/ADC0_SE7b/LLWU_P1<br>5/SPI1_MOSI/UART0_RX/SPI<br>1_MISO | Digital Input /<br>Output /<br>Analog Input | MCU Port D bit 6 / ADC0 Single Ended<br>analog channel input SE7b / Low leakage<br>Wake Up port 15 / SPI1 MOSI / UART0 RX<br>/ SPI module 1 MISO             |                              |

| 30  | NC                                                           |                                             | No Connect                                                                                                                                                   |                              |

| 31  | PTD7/SPI0_MISO/UART0_TX<br>/SPI1_MOSI                        | Digital<br>Input/Output                     | MCU Port D Bit 7 / SPI module 0 MISO /<br>UART module 0 Transmit / SPI module 1<br>MOSI                                                                      |                              |

| 32  | PTE0/SPI1_MISO/UART1_TX<br>/RTC_CLKOUT/CMP0_OUT/<br>IIC1_SDA | Digital<br>Input/Output                     | MCU Port E Bit 0 / SPI module 1 MISO /<br>UART module 1 Transmit / Real Time<br>Counter Clock Output / Comparator 0<br>Analog voltage Output / IIC1 Bus Data |                              |

| 33  | PTA20/RESETB                                                 | Digital<br>Input/Output                     | MCU Port A Bit 20/MCU RESET                                                                                                                                  |                              |

| 34  | PTE1 / SPI1_MOSI /<br>UART1_RX /SPI1_MISO /<br>IIC1_SCL      | Digital<br>Input/Output                     | MCU Port E Bit 1 / SPI module 1 MOSI /<br>UART module 1 RX / SPI1_MISO /<br>IIC1_SCL                                                                         |                              |

| 35  | VBAT2 (RF)                                                   | Power Input                                 | Transceiver VDD                                                                                                                                              | Connect to system VDD supply |

| 36  | GND/SCAN (RF)                                                | Power Input                                 | Transceiver Ground                                                                                                                                           | Connect to ground            |

| 37  | RXTX (RF)                                                    | Digital<br>Output                           | Transceiver Rx / Tx RF Switch Control<br>Output; high when in TX                                                                                             |                              |

| 38  | GND_PA2 (RF)                                                 | Power Input                                 | Transceiver RF Ground                                                                                                                                        | Connect to ground            |

| 39  | RFIO (RF)                                                    | RF Input /<br>Output                        | Transceiver RF Input / Output                                                                                                                                |                              |

| 40  | GND_PA1 (RF)                                                 | Power Input                                 | Transceiver RF Ground                                                                                                                                        | Connect to ground            |

| 41  | PA_BOOST (RF)                                                | RF Output                                   | Transceiver Optional High-Power PA<br>Output                                                                                                                 |                              |

| 42  | VR_PA (RF)                                                   | Power<br>Output                             | Transceiver regulated output voltage for VR_PA use.                                                                                                          | De-coupling cap suggested.   |

| 43  | VBAT1 (RF)                                                   | Power Input                                 | Transceiver VDD for RF circuitry                                                                                                                             | Connect to system VDD supply |

| Table 1. Pin | Function  | Description | n (Sheet 3 of | 5)         |

|--------------|-----------|-------------|---------------|------------|

|              | i unotion | Description |               | <i>v</i> , |

| Pin | Pin Name <sup>1</sup>             | Туре                    | Description                                                                               | Functionality                                                                                                                             |

|-----|-----------------------------------|-------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 44  | VR_ANA (RF)                       | Power<br>Output         | Transceiver regulated output voltage for<br>analog circuitry.                             | Decouple to ground with<br>100 nF capacitor                                                                                               |

| 45  | VR_DIG (RF)                       | Power<br>Output         | Transceiver regulated output voltage for digital circuitry.                               | Decouple to ground with<br>100 nF capacitor                                                                                               |

| 46  | XTA (RF)                          | Xtal Osc                | Transceiver crystal reference oscillator                                                  | Connect to 32 MHz crystal and load capacitor                                                                                              |

| 47  | XTB (RF)                          | Xtal Osc                | Transceiver crystal reference oscillator                                                  | Connect to 32 MHz crystal and load capacitor                                                                                              |

| 48  | RESET (RF)                        | Digital Input           | Transceiver hardware reset input                                                          | Typically driven from<br>MCU GPIO                                                                                                         |

| 49  | DIO0/PTE2/SPI1_SCK                | Digital<br>Input/Output | Internally connected to Transceiver GPIO<br>bit 0 and MCU Port E bit 2 / SPI1 clock       | MCU IO and Transceiver<br>IO connected in-package                                                                                         |

| 50  | DIO1/PTE3/SPI1_MISO/SPI1<br>_MOSI | Digital<br>Input/Output | Internally connected to Transceiver GPIO bit 1 and MCU Port E bit 3 /SPI1 in or out       | MCU IO and Transceiver<br>IO connected in-package                                                                                         |

| 51  | DIO2                              | Digital<br>Input/Output | Transceiver GPIO Bit 2                                                                    |                                                                                                                                           |

| 52  | DIO3                              | Digital<br>Input/Output | Transceiver GPIO Bit 3                                                                    |                                                                                                                                           |

| 53  | DIO4                              | Digital<br>Input/Output | Transceiver GPIO Bit 4                                                                    |                                                                                                                                           |

| 54  | DIO5/CLKOUT                       | Digital<br>Input/Output | Transceiver GPIO Bit 5 / ClkOut                                                           | Commonly programmed<br>as ClkOut to supply MCU<br>clock; connect to Pin 15                                                                |

| 55  | VDD                               | Power Input             | MCU VDD supply                                                                            | Connect to VDD supply                                                                                                                     |

| 56  | VDDAD                             | Power Input             | MCU Analog supply                                                                         | Connect to Analog supply                                                                                                                  |

| 57  | MISO/PTC7/SPI0_MISO/SPI0<br>_MOSI | Digital<br>Input/Output | Internal SPI data connection from<br>Transceiver MISO bit 1 to MCU SPI0 (Port<br>C bit 7) | <ul> <li>MCU IO and<br/>Transceiver IO<br/>connected in-package</li> <li>MCU IO must be<br/>configured for this<br/>connection</li> </ul> |

| 58  | NSS/PTD0/SPI0_PCS0                | Digital<br>Input/Output | Internal SPI select connection between<br>Transceiver NSS and MCU SPI0 (Port D bit<br>0)  | <ul> <li>MCU IO and<br/>Transceiver IO<br/>connected in-package</li> <li>MCU IO must be<br/>configured for this<br/>connection</li> </ul> |

| 59  | SCK/PTC5/SPI0_SCK                 | Digital<br>Input/Output | Internal SPI clock connection between<br>Transceiver SCK and MCU SPI0 (port C bit<br>5)   | <ul> <li>MCU IO and<br/>Transceiver IO<br/>connected in-package</li> <li>MCU IO must be<br/>configured for this<br/>connection</li> </ul> |

| Pin  | Pin Name <sup>1</sup>             | Туре                    | Description                                                                          | Functionality                                                                                                                             |

|------|-----------------------------------|-------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 60   | MOSI/PTC6/SPI0_MOSI/<br>SPI0_MISO | Digital<br>Input/Output | Internal SPI data connection to Transceiver<br>MOSI bit 1 to MCU SPI0 (Port C bit 6) | <ul> <li>MCU IO and<br/>Transceiver IO<br/>connected in-package</li> <li>MCU IO must be<br/>configured for this<br/>connection</li> </ul> |

| FLAG | VSS                               | Power input             | External package flag. Common VSS                                                    | Connect to ground.                                                                                                                        |

Table 1. Pin Function Description (Sheet 5 of 5)

<sup>1</sup> Refer to ADD Table 1-3 for additional pin-out information on default and alternate setting selections.

## 5.2 Internal Functional Interconnects

The MCU provides control to the transceiver through the SPI Port and receives status from the transceiver from the DIOx pins. Certain interconnects between the devices are routed on chip. In addition, the signals are brought out to external pads.

| Pin | MCU Signal                        | Transceiver<br>Signal | Description                                                     |

|-----|-----------------------------------|-----------------------|-----------------------------------------------------------------|

| 49  | DIO0/PTE2/SPI1_<br>SCK            | DIO0                  | Transceiver DIO0 can be programmed to provide status to the MCU |

| 50  | DIO1/PTE3/SPI1_<br>MISO/SPI1_MOSI | DIO1                  | Transceiver DIO1 can be programmed to provide status to the MCU |

| 57  | MISO/PTC7/SPI0_<br>MISO/SPI0_MOSI | MISO                  | SPI data from transceiver to MCU                                |

| 58  | NSS/PTD0/SPI0_<br>PCS0            | NSS                   | SPI chip select                                                 |

| 59  | SCK/PTC5/SPI0_<br>SCK             | SCK                   | SPI Clock                                                       |

| 60  | MOSI/PTC6/SPI0_<br>MOSI/SPI0_MISO | MOSI                  | SPI data from MCU to transceiver                                |

Table 2. MKW01 Internal Functional Interconnects

#### NOTE

- As shown in Table 2, the MCU SPI Port pin selection must be configured by software.

- The transceiver DIO pins must be programmed to provide desired status.

- Enhanced performance can be achieved by additionally routing some DIO pins externally to other GPIO pins.

## 5.3 External Functional Interconnects

In addition to the in-package device interconnection, other external connections between the MCU and the transceiver are common:

MKW01Z128 Datasheet, Rev. 6, 04/2016

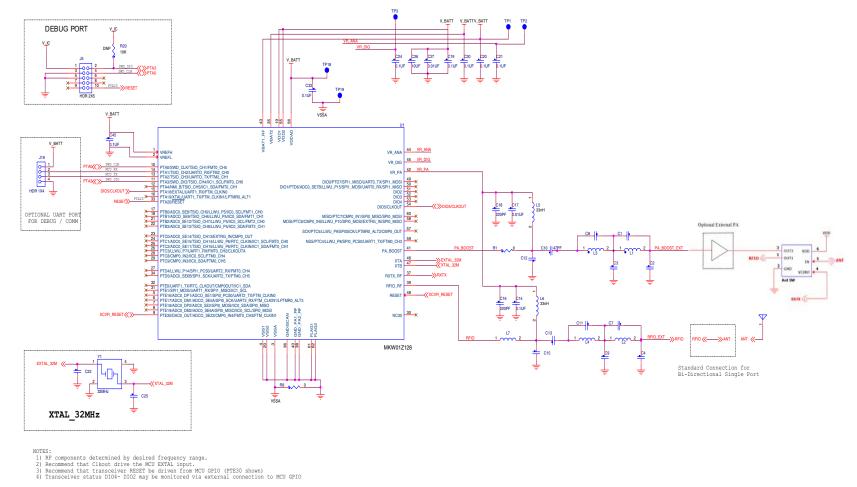

- 1. Freescale recommends driving/controlling the transceiver reset from an MCU GPIO This allows overriding control of the transceiver from the system application.

- 2. The other DIO2-DIO4 status and RXTX signals can prove useful for monitoring the transceiver operation the DIO2-DIO4 signals must be programmed to provide operational status. All signals must be connected externally to appropriate MCU GPIO for this function.

# 6 System and Power Management

The MKW01 consists of an independent transceiver and MCU. The MCU controls the transceiver through programming of the SPI Port, and sets its operational mode through this control channel. Total current draw for the MKW01 is dependent on the operation mode of both devices where different modes allow for different levels of power-down. Some additional features supported are:

- Transceiver Sleep with MCU set at the lowest power state.

- The transceiver mode selection being independent of the MCU's mode selection.

- The transceiver uses/powers-up the transmitter or receiver only as required.

- MCU peripheral control clock gating being disabled on a module-by-module basis to provide lowest power.

- RTC can be used as wake-up timer.

- LLWU (Low Leakage Wake-up Unit) available.

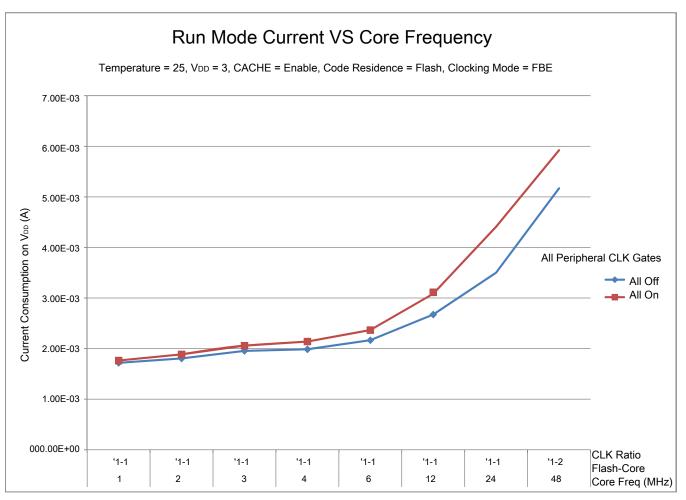

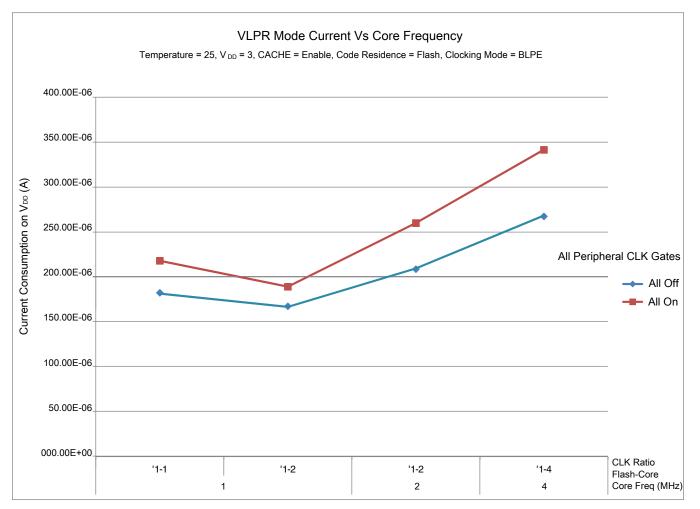

### 6.1 MCU Power Modes

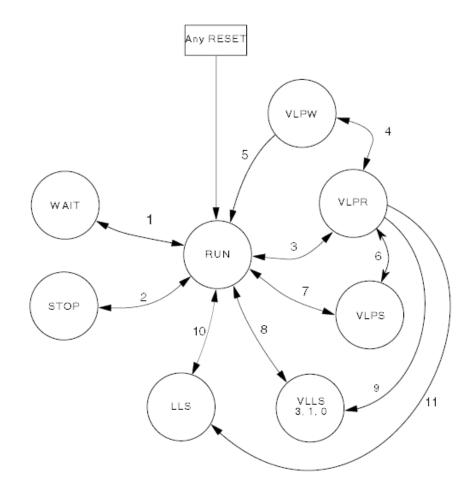

The MCU has 9 different modes of operation to allow the user to optimize power consumption for the level of functionality needed. Depending on the STOP requirements of the user application, a variety of STOP modes are available that provide state retention, partial power down or full power down of certain logic and/or memory. I/O states are held in all modes of operation. Table 3 outlines the various available power modes of MCU operation.

For each RUN mode there is a corresponding WAIT and STOP mode. WAIT modes are similiar to ARM sleep modes. STOP modes (VLPS, STOP) are similiar to ARM sleep deep mode. The very low power run (VLPR) operating mode can greatly reduce runtime power when the maximum bus frequency is not required to handle application needs. The 3 primary modes of operation are RUN, WAIT and STOP. The WFI instruction invokes both WAIT and STOP modes for the MCU. The primary modes are augmented in a number of ways to provide lower power based on application needs.

| Chip Power<br>Mode                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Core Mode  | Normal<br>Recovery<br>Method     |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------|

| Normal run                                | Allows maximum performance of chip. Default mode out of reset; onchip voltage regulator is on.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Run        | _                                |

| Normal Wait - via<br>WFI                  | Allows peripherals to function while the core is in sleep mode,<br>reducing power. NVIC remains sensitive to interrupts;<br>peripherals continue to be clocked.                                                                                                                                                                                                                                                                                                                                                                                        | Sleep      | Interrupt                        |

| Normal Stop - via<br>WFI                  | Places chip in static state. Lowest power mode that retains all registers while maintaining LVD protection. NVIC is disabled; AWIC is used to wake up from interrupt; peripheral clocks are stopped.                                                                                                                                                                                                                                                                                                                                                   | Sleep Deep | Interrupt                        |

| VLPR (Very Low<br>Power Run)              | On-chip voltage regulator is in a low power mode that supplies<br>only enough power to run the chip at a reduced frequency.<br>Reduced frequency Flash access mode (1 MHz); LVD off; in<br>BLPI clock mode, the fast internal reference oscillator is<br>available to provide a low power nominal 4 MHz source for the<br>core with the nominal bus and flash clock required to be <800<br>kHz; alternatively, BLPE clock mode can be used with an<br>external clock or the crystal oscillator providing the clock source.                             | Run        | _                                |

| VLPW (Very Low<br>Power Wait) -via<br>WFI | Same as VLPR but with the core in sleep mode to further reduce<br>power; NVIC remains sensitive to interrupts (FCLK = ON).<br>On-chip voltage regulator is in a low power mode that supplies<br>only enough power to run the chip at a reduced frequency.                                                                                                                                                                                                                                                                                              | Sleep      | Interrupt                        |

| VLPS (Very Low<br>Power Stop)-via<br>WFI  | Places chip in static state with LVD operation off. Lowest power<br>mode with ADC and pin interrupts functional. Peripheral clocks<br>are stopped, but OSC, LPTMR, RTC, CMP, TSI can be used.<br>TPM and UART can optionally be enabled if their clock source is<br>enabled. NVIC is disabled (FCLK = OFF); AWIC is used to wake<br>up from interrupt. On-chip voltage regulator is in a low power<br>mode that supplies only enough power to run the chip at a<br>reduced frequency. All SRAM is operating (content retained and<br>I/O states held). | Sleep Deep | Interrupt                        |

| LLS (Low<br>Leakage Stop)                 | State retention power mode. Most peripherals are in state retention mode (with clocks stopped), but OSC, LLWU, LPTMR, RTC, CMP,, TSI can be used. NVIC is disabled; LLWU is used to wake up.                                                                                                                                                                                                                                                                                                                                                           | Sleep Deep | Wakeup<br>Interrupt <sup>1</sup> |

|                                           | <b>NOTE:</b> The LLWU interrupt must not be masked by the interrupt controller to avoid a scenario where the system does not fully exit stop mode on an LLS recovery.                                                                                                                                                                                                                                                                                                                                                                                  |            |                                  |

|                                           | All SRAM is operating (content retained and I/O states held).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                                  |

#### Table 3. MCU power modes

| Chip Power<br>Mode                    | Description                                                                                                                                                                                                                                 | Core Mode  | Normal<br>Recovery<br>Method |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------|

| VLLS3 (Very<br>Low Leakage<br>Stop3)  | Most peripherals are disabled (with clocks stopped), but OSC,<br>LLWU, LPTMR, RTC, CMP, TSI can be used. NVIC is disabled;<br>LLWU is used to wake up.<br>SRAM_U and SRAM_L remain powered on (content retained<br>and I/O states held).    | Sleep Deep | Wakeup<br>Reset <sup>2</sup> |

| VLLS1 (Very<br>Low Leakage<br>Stop1)  | Most peripherals are disabled (with clocks stopped), but OSC,<br>LLWU, LPTMR, RTC, CMP, TSI can be used. NVIC is disabled;<br>LLWU is used to wake up. All of SRAM_U and SRAM_L are<br>powered off.                                         | Sleep Deep | Wakeup<br>Reset <sup>2</sup> |

| VLLS0 (Very<br>Low Leakage<br>Stop 0) | Most peripherals are disabled (with clocks stopped), but LLWU,<br>LPTMR, RTC, TSI can be used. NVIC is disabled; LLWU is used<br>to wake up.<br>All of SRAM_U and SRAM_L are powered off.<br>LPO disabled, optional POR brown-out detection | Sleep Deep | Wakeup<br>Reset <sup>2</sup> |

Resumes normal run mode operation by executing the LLWU interrupt service routine.

<sup>2</sup> Follows the reset flow with the LLWU interrupt flag set for the NVIC.

#### 6.1.1 Power mode transitions

Figure 6 shows power mode transitions. Any reset always brings the MCU back to normal state run. In RUN, WAIT and STOP modes active power regulation is enabled. The VLPx modes are limited in frequency but offer a lower power operating power mode than normal modes. The LLS and VLLSx modes are the lowest power stop modes based on the amount of logic or memory that is required to be reatined by the application.

Figure 6. Power mode state transition diagram

## 6.2 Transceiver modes of operation.

The transceiver can be set in numerous modes of operation as described in Table 4. By default, when switching from one mode to another various features are selectively turned on coordinated by a pre-defined optimized sequence using the automatic sequencer. Alternatively, these operating modes can be selected directly by disabling the automatic sequencer.

| l             |                                                |

|---------------|------------------------------------------------|

| Selected Mode | Enabled blocks                                 |

| Sleep         | None                                           |

| Stand-by      | Main regulator and crystal oscillator          |

| Idle          | Main regulator and RC oscillator               |

| FS            | Frequency synthesizer                          |

| Transmit      | Frequency synthesizer and transmitter          |

| Receive       | Frequency synthesizer and receiver             |

| Listen        | Periodical receive wake-up from Idle operation |

#### Table 4. Basic Transceiver modes

An overview of the transceiver modes of operation is described below:

- Sleep provides lowest power consumption and is the full power down state.

- Idle provides very low standby power consumption and has the main voltage regulator and the RC oscillator enabled.

- Standby similar to Idle with low standby power consumption but has the main voltage regulator and the crystal oscillator enabled.

- FS (Frequency synthesizer) the frequency synthesizer is alive to shorten startup time to transmit or receive states.

- Transmit transmitter is active.

- Receive receiver is active.

## 6.3 System Protection

The MKW01 provides numerous vehicles to maintain security or a high level of system robustness:

- Standard COP Watchdog reset with option to run from dedicated 1 kHz internal clock source or bus clock. The COP watchdog is intended to force a system reset when the application software fails to execute as expected.

- LVD protection with reset or interrupt; selectable trip points.

- HardFault exception on attempts to execute undefined instructions or access to undefined memory space.

- LOCKUP reset resource from core.

- Flash protection

# 7 Development Environment

Development support for the ARM® Cortex M0+ MCU on the MKW01 is configured to provide maximum flexibility as allowed by the restrictions of the pinout and other available resources. One debug interface is supported:

• Two-wire Serial Wire Debug (SWD) interface

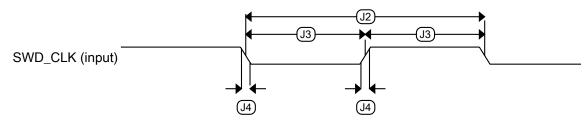

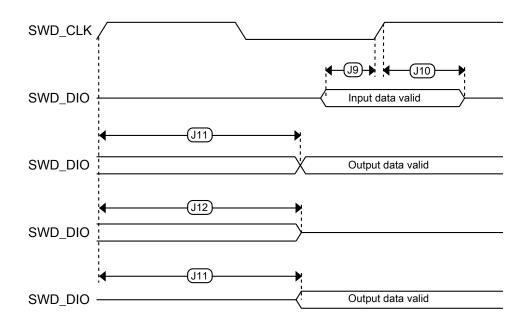

Table 5 presents a brief description of the serial wire debug description.

#### NOTE

Electrical specifications for the SWD lines can be found in the appendix.

| Module | Туре          | Description                                                                                                                                                    |

|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWCLK  | Input         | Serial Wire Clock. This pin is the clock for debug logic when in the Serial Wire Debug mode. This pin is pulled down internally.                               |

| SWDIO  | Input /Output | Serial Wire debug data input / output. The SWDIO pin is used by an external debug tool for communication and devive control. This pin is pulled up internally. |

Table 5. Debug Components Description

# 8 System Electrical Specification

This section details maximum ratings for the 60-pin LGA package and recommended operating conditions, DC characteristics, and AC characteristics for the modem, and the MCU.

## 8.1 LGA Package Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maximum rating is not guaranteed. Stress beyond the limits specified in Table 6 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ) or the programmable pull-up resistor associated with the pin is enabled.

Table 6 shows the maximum ratings for the 60-pin LGA package.

| Rating                       | Symbol                                 | Value                              | Unit |

|------------------------------|----------------------------------------|------------------------------------|------|

| Maximum Junction Temperature | TJ                                     | 95                                 | °C   |

| Storage Temperature Range    | T <sub>stg</sub>                       | -55 to 115                         | °C   |

| Power Supply Voltage         | V <sub>BATT</sub> , V <sub>DDINT</sub> | -0.3 to 3.8                        | Vdc  |

| Digital Input Voltage        | Vin                                    | -0.3 to (V <sub>DDINT</sub> + 0.3) |      |

| RF Input Power               | P <sub>max</sub>                       | 6                                  | dBm  |

#### Table 6. LGA Package Maximum Ratings

Note: Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics

or Recommended Operating Conditions tables.

Note: Meets Human Body Model (HBM) = 2 kV. RF input/output pins have no ESD protection.

### 8.2 ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with the JESD22 Stress Test Qualification for Commercial Grade Integrated Circuits. During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM) and the charge device model (CDM).

All latchup testing is in conformity with the JESD78 IC Latch-Up Test.

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification.

| Model         | Description                           | Symbol | Value | Unit |

|---------------|---------------------------------------|--------|-------|------|

|               | Series resistance                     | R1     | 1500  | Ω    |

| Human<br>Body | Storage capacitance                   | С      | 100   | pF   |

| Dody          | Number of pulses per pin <sup>1</sup> | _      | 1     |      |

|               | Series resistance                     | R1     | 0     | Ω    |

| Machine       | Storage capacitance                   | С      | 200   | pF   |

|               | Number of pulses per pin <sup>1</sup> | _      | 1     |      |

| Latch-up      | Minimum input voltage limit           |        | – 1.8 | V    |

| Later-up      | Maximum input voltage limit           |        | 4.32  | V    |

Table 7. ESD and Latch-up Test Conditions

<sup>1</sup> This number represents a minimum number for both positive pulse(s) and negative pulse(s)

| No. | Rating <sup>1</sup>                     | Symbol           | Min      | Max | Unit |

|-----|-----------------------------------------|------------------|----------|-----|------|

| 1   | Human body model (HBM)                  | V <sub>HBM</sub> | ± 2000   | _   | V    |

| 2   | Machine model (MM)                      | V <sub>MM</sub>  | $\pm200$ | _   | V    |

| 3   | Charge device model (CDM)               | V <sub>CDM</sub> | ± 500    | _   | V    |

| 4   | Latch-up current at $T_A = 85^{\circ}C$ | I <sub>LAT</sub> | ± 100    |     | mA   |

<sup>1</sup> Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

#### 8.3 Transceiver Electrical Characteristics

The tables below give the electrical specifications of the transceiver under the following conditions: Supply voltage VBAT1= VBAT2=VDD=3.3 V, temperature =  $25 \degree$ C, FXOSC = 32 MHz, FRF = 915 MHz, Pout = +13dBm, 2-level FSK modulation without pre-filtering, FDA = 5 kHz, Bit Rate = 4.8 kb/s and terminated in a matched 50 Ohm impedance, unless otherwise specified.

#### NOTE

Unless otherwise specified, the performances in the other frequency bands are similar or better.

### 8.3.1 Transceiver Recommended Operating Conditions

| Characteristic                                      | Symbol           | Min                                                   | Тур | Max                      | Unit |

|-----------------------------------------------------|------------------|-------------------------------------------------------|-----|--------------------------|------|

| Power Supply Voltage (V <sub>BATT</sub> )           |                  | 1.8                                                   |     | 3.6                      | Vdc  |

| Operating Temperature Range                         | T <sub>A</sub>   | -40                                                   | 25  | 85                       | °C   |

| Logic Input Voltage Low                             | V <sub>IL</sub>  | 0                                                     | -   | 20%<br>V <sub>BATT</sub> | V    |

| Logic Input Voltage High                            | V <sub>IH</sub>  | 80%<br>V <sub>BATT</sub>                              | -   | V <sub>BATT</sub>        | V    |

| Logic Output Voltage Low (I <sub>max</sub> = -1 mA) | V <sub>OL</sub>  | 0                                                     | -   | 10%<br>V <sub>BATT</sub> | V    |

| Logic Output Voltage High (I <sub>max</sub> = 1 mA) | V <sub>OH</sub>  | 90%<br>V <sub>BATT</sub>                              | -   | V <sub>BATT</sub>        | V    |

| Load capacitance on digital ports                   | CL               |                                                       |     | 25                       | pF   |

| SPI Clock Rate                                      | f <sub>SPI</sub> | -                                                     | -   | 8.0                      | MHz  |

| RF Input Power                                      | P <sub>max</sub> | -                                                     | -   | 0                        | dBm  |

| Crystal Reference Oscillator Frequency              | f <sub>ref</sub> | 32 MHz Only<br>(Some variants may use 30 MHz instead) |     |                          |      |

**Table 9. Recommended Operating Conditions**

# 8.3.2 Transceiver Power Consumption

Table 10. Power Supply Current

| Characteristic                                                                                                                                                                                                            | Conditions                 | Symbol  | Min         | Тур                        | Мах              | Unit                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------|-------------|----------------------------|------------------|----------------------------|

| Supply current in Sleep mode                                                                                                                                                                                              |                            | IDDSL   | -           | 0.1                        | 1                | μA                         |

| Supply current in Idle mode                                                                                                                                                                                               | RC oscillator enabled      | IDDIDLE | -           | 1.2                        | -                | μA                         |

| Supply current in Standby mode                                                                                                                                                                                            | Crystal oscillator enabled | IDDST   | -           | 1.25                       | 1.5              | mA                         |

| Supply current in Synthesizer mode                                                                                                                                                                                        |                            | IDDFS   | -           | 9                          | -                | mA                         |

| Supply current in Receive mode                                                                                                                                                                                            | 4.8 kbps<br>500 kbps       | IDDR    | -           | 16<br>17                   | -                | mA<br>mA                   |

| Supply current in Transmit mode with<br>appropriate matching, RF power<br>stable across VDD range, DC current<br>varies with VDD, lower IDDT at lower<br>VDD, typical numbers correspond to<br>mid-range VDD, about 2.7 V | · · · ·                    | IDDT    | -<br>-<br>- | 95<br>45<br>33<br>20<br>16 | -<br>-<br>-<br>- | mA<br>mA<br>mA<br>mA<br>mA |

### 8.3.3 Transceiver Frequency Synthesis

| Table 11. | Frequency | Synthesizer | Specification |

|-----------|-----------|-------------|---------------|

|-----------|-----------|-------------|---------------|

| Characteristic                                                     | Conditions                                                                                          | Symbol | Min               | Тур                                    | Max                        | Unit                                   |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------|-------------------|----------------------------------------|----------------------------|----------------------------------------|

| Synthesizer Frequency Range                                        | Programmable, 32 MHz clock                                                                          | FR     | 290<br>424<br>862 |                                        | 340<br>510<br>1020         | MHz<br>MHz<br>MHz                      |

| Crystal oscillator frequency                                       |                                                                                                     | FXOSC  | -                 | 32                                     | -                          | MHz                                    |

| Crystal oscillator wake-up time                                    |                                                                                                     | TS_OSC | -                 | 250                                    | 500                        | μs                                     |

| Frequency synthesizer wake-up time to PIILock signal               | From Standby mode                                                                                   | TS_FS  | -                 | 80                                     | 150                        | μs                                     |

| Frequency synthesizer hop time at most 10 kHz away from the target | 200 kHz step<br>1 MHz step<br>5 MHz step<br>7 MHz step<br>12 MHz step<br>20 MHz step<br>25 MHz step | TS_HOP |                   | 20<br>20<br>50<br>50<br>80<br>80<br>80 | -<br>-<br>-<br>-<br>-<br>- | μs<br>μs<br>μs<br>μs<br>μs<br>μs<br>μs |

| Frequency synthesizer step                                         | FSTEP = FXOSC/2 <sup>19</sup>                                                                       | FSTEP  | -                 | 61.0                                   | -                          | Hz                                     |

| RC Oscillator frequency                                            | After calibration                                                                                   | FRC    | -                 | 62.5                                   | -                          | kHz                                    |

| Bit rate, FSK                                                      | Programmable                                                                                        | BRF    | 1.2               | -                                      | 600                        | kbps                                   |

| Bit rate, OOK                                                      | Programmable                                                                                        | BRO    | 1.2               | -                                      | 32.768                     | kbps                                   |

| Frequency deviation, FSK                                           | Programmable<br>FDA + BRF/2 =< 500 kHz                                                              | FDA    | 0.6               | -                                      | 300                        | kHz                                    |

#### 8.3.4 Receiver

All receiver tests are performed with RxBw = 10 kHz (Single Side Bandwidth) as programmed in RegRxBw, receiving a PN15 sequence with a BER of 0.1% (Bit Synchronizer is enabled), unless otherwise specified. The LNA impedance is set to 200 Ohms, by setting bit LnaZin in RegLna to 1. Blocking tests are performed with an unmodulated interferer. The wanted signal power for the Blocking Immunity, ACR, IIP2, IIP3 and AMR tests is set 3 dB above the nominal sensitivity level.

| Characteristic                                                                              | Conditions                                                                               | Symbol            | Min         | Тур                  | Max         | Unit              |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------|-------------|----------------------|-------------|-------------------|

| FSK sensitivity, highest LNA gain                                                           | FDA = 5 kHz, BR = 1.2 kb/s<br>FDA = 5 kHz, BR = 4.8 kb/s<br>FDA = 40 kHz, BR = 38.4 kb/s | RFS_F             | -<br>-<br>- | -118<br>-114<br>-105 | -<br>-<br>- | dBm<br>dBm<br>dBm |

|                                                                                             | FDA = 5 kHz, BR = 1.2 kb/s <sup>1</sup>                                                  |                   | -           | -120                 | -           | dBm               |

| OOK sensitivity, highest LNA gain                                                           | BR = 4.8 kb/s                                                                            | RFS_O             | -           | -112                 | -109        | dBm               |

| Co-Channel Rejection                                                                        |                                                                                          | CCR               | -13         | -10                  | -           | dB                |

| Adjacent Channel Rejection                                                                  | Offset = +/- 25 kHz<br>Offset = +/- 50 kHz                                               | ACR               | -<br>37     | 42<br>42             | -           | dB<br>dB          |

| Blocking Immunity                                                                           | Offset = +/- 1 MHz<br>Offset = +/- 2 MHz<br>Offset = +/- 10 MHz                          | BI                | -<br>-<br>- | 66<br>71<br>79       | -<br>-<br>- | dB<br>dB<br>dB    |

| Blocking Immunity<br>Wanted signal at sensitivity +16dB                                     | Offset = +/- 1 MHz<br>Offset = +/- 2 MHz<br>Offset = +/- 10 MHz                          |                   | -<br>-<br>- | 62<br>65<br>73       | -<br>-<br>- | dB<br>dB<br>dB    |

| AM Rejection , AM modulated<br>interferer with 100% modulation<br>depth, fm = 1 kHz, square | Offset = +/- 1 MHz<br>Offset = +/- 2 MHz<br>Offset = +/- 10 MHz                          | AMR               | -<br>-<br>- | 66<br>71<br>79       | -<br>-<br>- | dB<br>dB<br>dB    |

| 2nd order Input Intercept Point<br>Unwanted tones are 20 MHz above<br>the LO                | Lowest LNA gain<br>Highest LNA gain                                                      | IIP2              | -           | +75<br>+35           | -           | dBm<br>dBm        |

| 3rd order Input Intercept point<br>Unwanted tones are 1MHz and 1.995<br>MHz above the LO    | Lowest LNA gain<br>Highest LNA gain                                                      | IIP3              | -<br>-23    | +20<br>-18           | -           | dBm<br>dBm        |

| Single Side channel filter BW                                                               | Programmable                                                                             | BW_SSB            | 2.6         | -                    | 500         | kHz               |

| Image rejection in OOK mode                                                                 | Wanted signal level = -106 dBm                                                           | IMR_<br>OOK       | 27          | 30                   | -           | dB                |

| Receiver wake-up time, from PLL locked state to <i>RxReady</i>                              | RxBw = 10 kHz, BR = 4.8 kb/s<br>RxBw = 200 kHz, BR = 100 kb/s                            | TS_RE             | -           | 1.7<br>96            | -           | ms<br>μs          |

| Receiver wake-up time, from PLL locked state, AGC enabled                                   | RxBw= 10 kHz, BR = 4.8 kb/s<br>RxBw = 200 kHz, BR = 100 kb/s                             | TS_RE_<br>AGC     | -           | 3.0<br>163           |             | ms<br>μs          |

| Receiver wake-up time, from PLL lock state, AGC and AFC enabled                             | RxBw= 10 kHz, BR = 4.8 kb/s<br>RxBw = 200 kHz, BR = 100 kb/s                             | TS_RE_<br>AGC&AFC |             | 4.8<br>265           |             | ms<br>μs          |

| FEI sampling time                                                                           | Receiver is ready                                                                        | TS_FEI            | -           | 4.T <sub>bit</sub>   | -           | -                 |

| AFC Response Time                                                                           | Receiver is ready                                                                        | TS_AFC            | -           | 4.T <sub>bit</sub>   | -           | -                 |

#### Table 12. Receiver Specification

| Characteristic     | Conditions             | Symbol  | Min | Тур                | Max | Unit       |

|--------------------|------------------------|---------|-----|--------------------|-----|------------|

| RSSI Response Time | Receiver is ready      | TS_RSSI | -   | 2.T <sub>bit</sub> | -   | -          |

| RSSI Dynamic Range | AGC enabled Min<br>Max | DR_RSSI | -   | -115<br>0          | -   | dBm<br>dBm |

<sup>1</sup> Set SensitivityBoost in RegTestLna to 0x2D to reduce the noise floor in the receiver

#### 8.3.5 Transmitter

| Characteristic                                                    | Conditions                                                               | Symbol         | Min    | Тур        | Max | Unit       |

|-------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|--------|------------|-----|------------|