Rev. V2

Designed for wideband large signal amplifier and oscillator applications Up to 400 MHz range, in either single-ended or push-pull configuration.

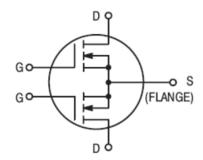

#### N-Channel enhancement mode

- Guaranteed 28 volt, 150 MHz performance

Output power = 30 Watts

Broadband gain = 14 dB (Typ.)

Efficiency = 54% (Typ.)

- Small– and large–signal characterization

- 100% tested for load mismatch at all phase angles with 30:1 VSWR

- Space saving package for push–pull circuit applications

- · Excellent thermal stability, ideally suited for Class A operation

- · Facilitates manual gain control, ALC and modulation techniques

**Product Image**

#### MAXIMUM RATINGS

| Rating                                                                | Sym            | lode                         | Value | Unit          |  |

|-----------------------------------------------------------------------|----------------|------------------------------|-------|---------------|--|

| Drain-Source Voltage                                                  | V <sub>D</sub> | V <sub>DSS</sub> 65          |       | Vdc           |  |

| Drain-Gate Voltage (R <sub>GS</sub> = 1.0 MΩ)                         | V <sub>D</sub> | ogr 65                       |       | Vdc           |  |

| Gate-Source Voltage                                                   | Vo             | V <sub>GS</sub> ±40          |       | Vdc           |  |

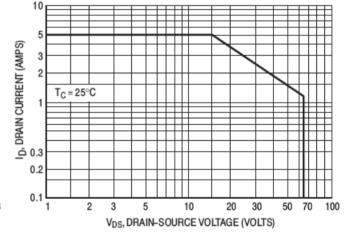

| Drain Current — Continuous                                            | I              | D                            | 5.0   | Adc           |  |

| Total Device Dissipation @ T <sub>C</sub> = 25°C<br>Derate above 25°C | Р              | P <sub>D</sub> 100 0.571     |       | Watts<br>W/°C |  |

| Storage Temperature Range                                             | Ts             | T <sub>stg</sub> -65 to +150 |       | °C            |  |

| Operating Junction Temperature                                        | Т              | T <sub>J</sub> 200           |       | °C            |  |

#### THERMAL CHARACTERISTICS

| Characteristic                       | Symbol           | Max  | Unit |

|--------------------------------------|------------------|------|------|

| Thermal Resistance, Junction to Case | R <sub>eJC</sub> | 1.75 | °C/W |

Handling and Packaging — MOS devices are susceptible to damage from electrostatic charge. Reasonable precautions in handling and packaging MOS devices should be observed.

1

<sup>\*</sup> Restrictions on Hazardous Substances, European Union Directive 2002/95/EC.

Rev. V2

#### ELECTRICAL CHARACTERISTICS (T<sub>C</sub> = 25°C unless otherwise noted.)

| Characteristic                                                                                                                                                   | Symbol               | Min                            | Тур | Max | Unit  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------|-----|-----|-------|

| OFF CHARACTERISTICS (1)                                                                                                                                          |                      |                                | •   | •   |       |

| Drain–Source Breakdown Voltage (V <sub>GS</sub> = 0, I <sub>D</sub> = 5.0 mA)                                                                                    | V <sub>(BR)DSS</sub> | 65                             | _   | _   | Vdc   |

| Zero-Gate Voltage Drain Current (V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0)                                                                                    | I <sub>DSS</sub>     | _                              | _   | 2.0 | mAdc  |

| Gate-Source Leakage Current (V <sub>GS</sub> = 40 V, V <sub>DS</sub> = 0)                                                                                        | lgss                 | _                              | _   | 1.0 | μAdc  |

| ON CHARACTERISTICS (1)                                                                                                                                           |                      |                                |     |     |       |

| Gate Threshold Voltage<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 25 mA)                                                                                       | V <sub>GS(th)</sub>  | 1.0                            | 3.0 | 6.0 | Vdc   |

| Forward Transconductance<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 250 mA)                                                                                    | 9fs                  | 250                            | 400 | _   | mmhos |

| DYNAMIC CHARACTERISTICS (1)                                                                                                                                      |                      |                                | •   | •   |       |

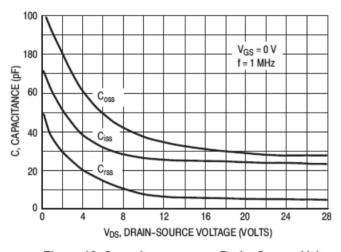

| Input Capacitance<br>(V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0, f = 1.0 MHz)                                                                                  | C <sub>iss</sub>     | _                              | 24  | _   | pF    |

| Output Capacitance<br>(V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0, f = 1.0 MHz)                                                                                 | C <sub>oss</sub>     | _                              | 27  | _   | pF    |

| Reverse Transfer Capacitance<br>(V <sub>DS</sub> = 28 V, V <sub>GS</sub> = 0, f = 1.0 MHz)                                                                       | C <sub>rss</sub>     | _                              | 5.5 | _   | pF    |

| FUNCTIONAL CHARACTERISTICS (2)                                                                                                                                   |                      |                                |     |     |       |

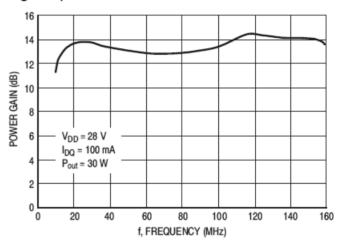

| Common Source Power Gain (Figure 1)<br>(V <sub>DD</sub> = 28 Vdc, P <sub>out</sub> = 30 W, f = 150 MHz, I <sub>DQ</sub> = 100 mA)                                | G <sub>ps</sub>      | 12                             | 14  | _   | dB    |

| Drain Efficiency (Figure 1)<br>(V <sub>DD</sub> = 28 Vdc, P <sub>out</sub> = 30 W, f = 150 MHz, I <sub>DQ</sub> = 100 mA)                                        | η                    | 50                             | 54  | _   | %     |

| Electrical Ruggedness (Figure 1)<br>(V <sub>DD</sub> = 28 Vdc, P <sub>out</sub> = 30 W, f = 150 MHz, I <sub>DQ</sub> = 100 mA,<br>VSWR 30:1 at all Phase Angles) | Ψ                    | No Degradation in Output Power |     |     |       |

#### NOTES:

- 1. Each side measured separately.

- 2. Measured in push-pull configuration.

Rev. V2

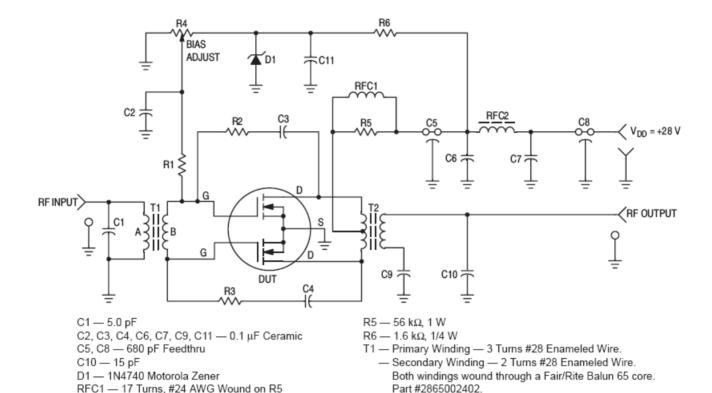

Figure 1. 30-150 MHz Test Circuit

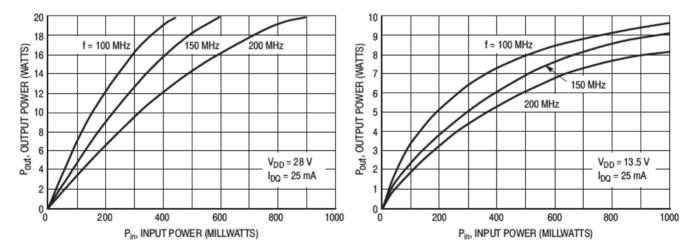

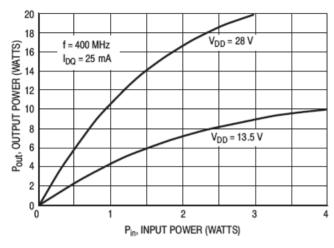

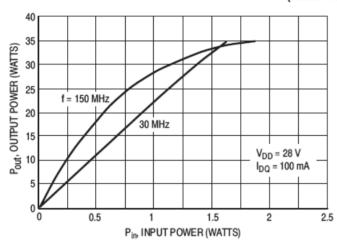

Figure 2. Output Power versus Input Power

RFC2 — Ferroxcube VK-200-19/4B or Equivalent

R1 — 10 kΩ, 1/4 W

R2, R3 — 560  $\Omega$ , 1/2 W R4 — 10 Turns, 10 k $\Omega$

Figure 3. Output Power versus Input Power

T2 - 1:1 Transformer Wound Bifilar - 2 Turns Twisted Pair

Board Material - 0.062" G10, 1 oz. Cu Clad, Double Sided

#24 Enameled Wire through a Indiana General Balun Q1 core. Part #18006-1-Q1. Primary winding center tapped.

Rev. V2

Figure 4. Output Power versus Input Power

Figure 5. Output Power versus Supply Voltage

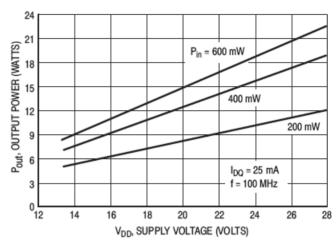

Figure 6. Output Power versus Supply Voltage

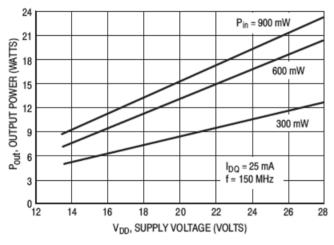

Figure 7. Output Power versus Supply Voltage

Rev. V2

I<sub>D</sub> = 750 mA 500 mA 250 mA 25 mA 100 125 75 150 175 T<sub>C</sub>, CASE TEMPERATURE (°C)

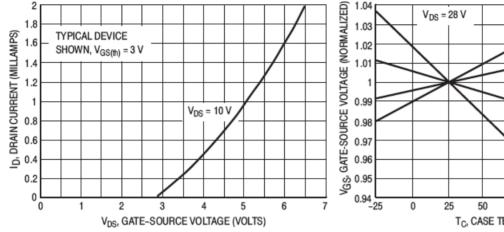

Figure 8. Drain Current versus Gate Voltage (Transfer Characteristics)\*

Figure 9. Gate-Source Voltage versus Case Temperature\*

Figure 10. Capacitance versus Drain-Source Voltage

Figure 11. DC Safe Operating Area

Rev. V2

### TYPICAL PERFORMANCE IN BROADBAND TEST CIRCUIT (Refer to Figure 1)

Figure 12. Output Power versus Input Power

Figure 13. Power Gain versus Frequency

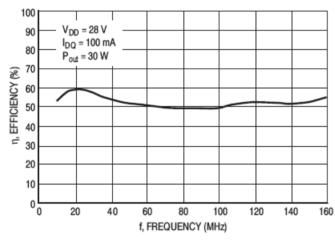

Figure 14. Drain Efficiency versus Frequency

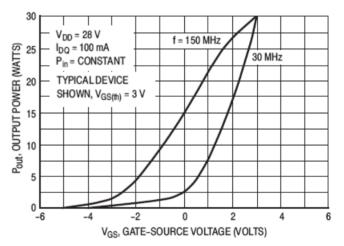

Figure 15. Output Power versus Gate Voltage

Rev. V2

#### TYPICAL 400 MHz PERFORMANCE

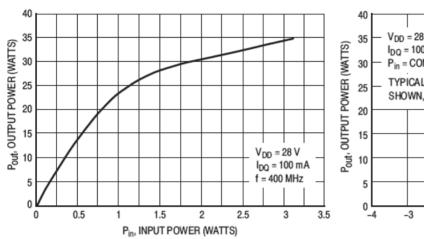

Figure 16. Output Power versus Input Power

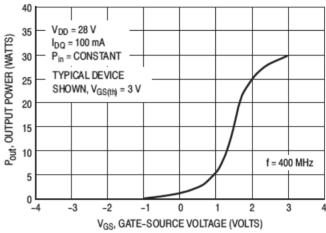

Figure 17. Output Power versus Gate Voltage

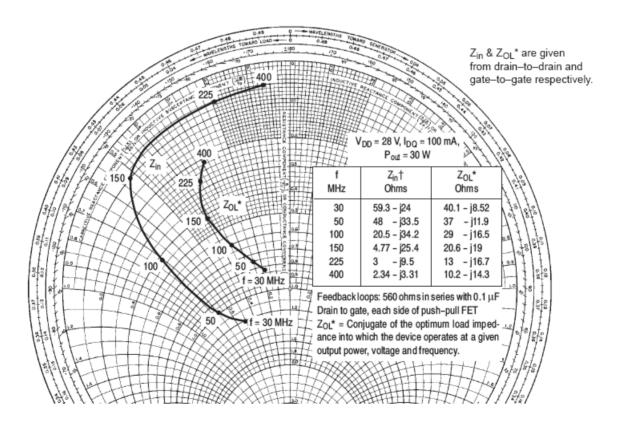

Figure 18. Input and Output Impedance

Rev. V2

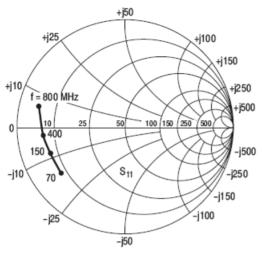

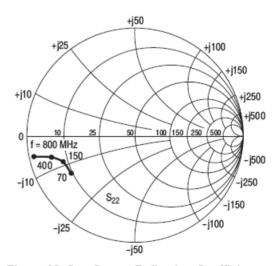

Figure 19. S<sub>11</sub>, Input Reflection Coefficient versus Frequency  $V_{DS} = 28 \text{ V}$  I<sub>D</sub> = 0.5 A

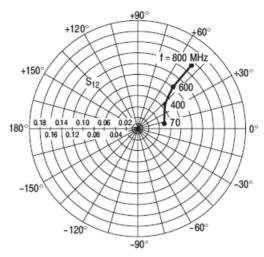

Figure 20.  $S_{12}$ , Reverse Transmission Coefficient versus Frequency  $V_{DS} = 28 \text{ V}$   $I_D = 0.5 \text{ A}$

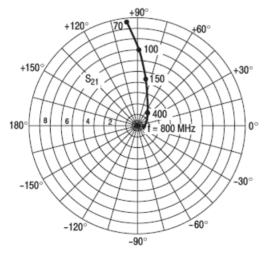

Figure 21.  $S_{21}$ , Forward Transmission Coefficient versus Frequency  $V_{DS}$  = 28 V  $I_D$  = 0.5 A

Figure 22.  $S_{22}$ , Output Reflection Coefficient versus Frequency  $V_{DS}$  = 28 V  $I_D$  = 0.5 A

Rev. V2

#### RF POWER MOSFET CONSIDERATIONS

#### **DESIGN CONSIDERATIONS**

The MRF136Y is a RF power N–Channel enhancement-mode field–effect transistor (FET) designed especially for VHF power amplifier applications. M/A-COM RF MOS FETs feature a vertical structure with a planar design, thus avoiding the processing difficulties associated with V–groove vertical power FETs.

M/A-COM Application Note AN211A, FETs in Theory and-Practice, is suggested reading for those not familiar with the construction and characteristics of FETs.

The major advantages of RF power FETs include high gain, low noise, simple bias systems, relative immunity from thermal runaway, and the ability to withstand severely mismatched loads without suffering damage. Power output can be varied over a wide range with a low power dc control signal, thus facilitating manual gain control, ALC and modulation.

#### DC BIAS

The MRF136Y is an enhancement mode FET and, therefore, does not conduct when drain voltage is applied. Drain current flows when a positive voltage is applied to the gate. See Figure 10 for a typical plot of drain current versus gate voltage. RF power FETs require forward bias for optimum performance.

The value of quiescent drain current (IDQ) is not critical formany applications. The MRF136Y was characterized at IDQ = 25 mA, which is the suggested minimum value of IDQ. For special applications such as linear amplification, IDQ may have to be selected to optimize the critical parameters.

The gate is a dc open circuit and draws no current. Therefore, the gate bias circuit may generally be just a simple

resistive divider network. Some special applications may require a more elaborate bias system.

#### **GAIN CONTROL**

Power output of the MRF136Y may be controlled from its rated value down to zero (negative gain) by varying the dc gate voltage. This feature facilitates the design of manual gain control, AGC/ALC and modulation systems. (See Figure 9.)

#### **AMPLIFIER DESIGN**

Impedance matching networks similar to those used with bipolar VHF transistors are suitable for MRF136Y. See M/A-COM Application Note AN721, Impedance Matching Networks Applied to RF Power Transistors. The higher input impedance of RF MOS FETs helps ease the task of broadband network design. Both small signal scattering parameters and large signal impedances are provided. While the s-parameters will not produce an exact design solution for high power operation, they do yield a good first approximation. This is an additional advantage of RF MOS power FETs.

RF power FETs are triode devices and, therefore, not unilateral. This, coupled with the very high gain of the MRF136Y, yields a device capable of self oscillation. Stability may be achieved by techniques such as drain loading, input shunt resistive loading, or output to input feedback. Two port parameter stability analysis with the MRF136Y sparameters provides a useful tool for selection of loading or feedback circuitry to assure stable operation. See M/A-COM Application Note AN215A for a discussion of two port network theory and stability.

#### **LOW NOISE OPERATION**

Input resistive loading will degrade noise performance, and noise figure may vary significantly with gate driving impedance. A low loss input matching network with its gate impedance optimized for lowest noise is recommended.

Rev. V2

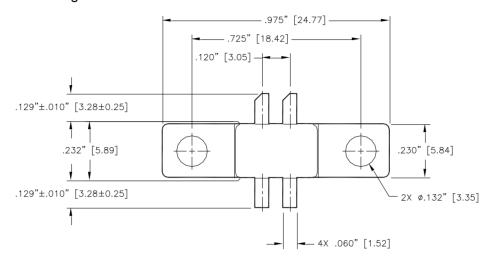

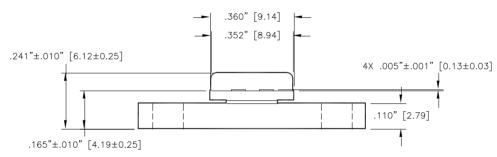

#### **Outline Drawing**

Unless otherwise noted, tolerances are inches  $\pm .005$ " [millimeters  $\pm 0.13$ mm]