# Evaluation Board User's Manual for NB4N11M

# **ON Semiconductor®**

http://onsemi.com

# **EVAL BOARD USER'S MANUAL**

#### Description

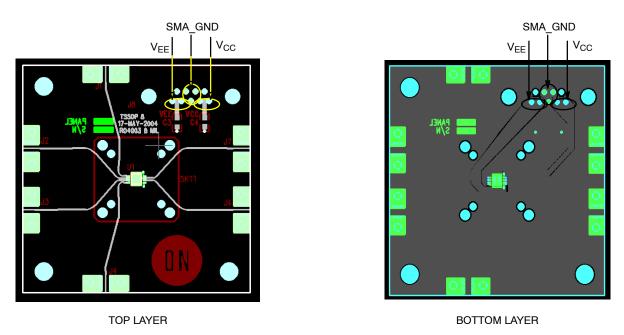

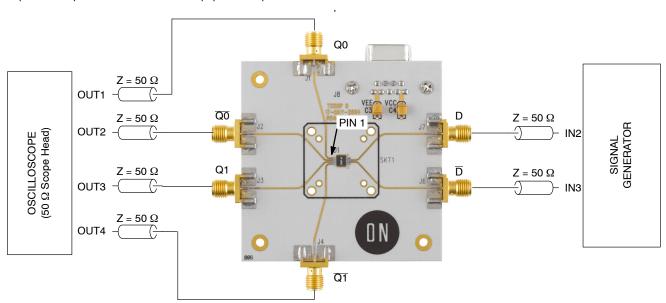

ON Semiconductor has developed an evaluation board for the NB4N11M device as a convenience for the customers interested in performing their own device engineering assessment. This board provides a high bandwidth 50  $\Omega$ controlled impedance environment. The pictures in Figure 1 show the top and bottom view of the evaluation board, which can be configured in several different ways.

This NB4N11M evaluation board manual contains:

- Appropriate Lab Setup

- Assembly Instructions

- Bill of Materials

This manual should be used in conjunction with the NB4N11M device data sheet, which contains full technical details on the device specifications and operation.

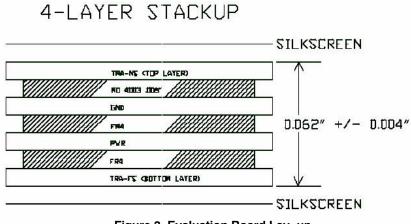

## Board Lay-Up

The NB4N11M evaluation board is implemented in four layers with split (dual) power supplies (Figure 7, Evaluation Board Lay–up). For standard lab setup, a split (dual) power supply is essential to enable the 50  $\Omega$  internal impedance in the oscilloscope as a devices termination. The first layer or primary trace layer is 0.005" thick Rogers RO4003 material, which is designed to have equal electrical length on all signal traces from the device under the test (DUT) to the sense output. The second layer is the 1.0 oz copper ground plane. The FR4 dielectric material is placed between second and third layer and between third and fourth layer. The third layer is also 1.0 oz copper ground plane. The fourth layer is the secondary trace layer.

Figure 1. Top and Bottom View of the NB4N11M Evaluation Board

Figure 3. Evaluation Board Lay-up

## **Connecting Power and Ground Planes**

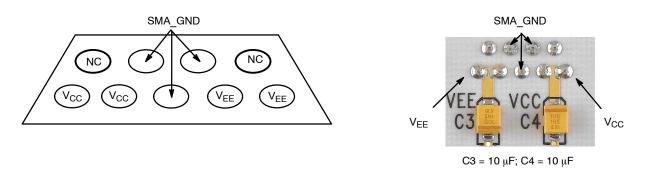

The side launch 9 pin power supply connector is wired as shown in Figure 4. Test points can be soldered on the top of

the PCB to accommodated easier connections. Exact values that need to be applied can be found in Table 1.

## Table 1. Power Supply Levels

| Power Supply Span | V <sub>TT</sub><br>(Termination) | V <sub>CC</sub><br>(Pin 8) | V <sub>EE</sub> / GND<br>(Pin 5) | SMA_GND<br>(PCB SMA Ground) |

|-------------------|----------------------------------|----------------------------|----------------------------------|-----------------------------|

| 3.3 V             | 1.8 V                            | 1.5 V                      | –1.8 V                           | 0 V                         |

| 3.3 V             | 2.5 V                            | 0.8 V                      | –2.5 V                           | 0 V                         |

| 3.3 V             | 3.3 V                            | 0 V                        | –3.3 V                           | 0 V                         |

Figure 4. Power Supply Connector – 9 Pin Side View (Left) and PCB Top View (Right)

#### **Stimulus (Generator) Termination**

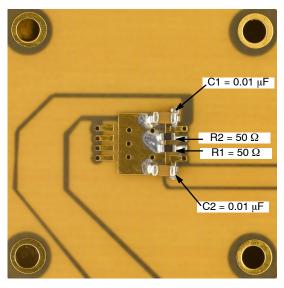

All ECL outputs need to be terminated to  $V_{TT}$  ( $V_{TT} = V_{CC} - 2.0 \text{ V} = \text{GND}$ ) via a 50  $\Omega$  resistor. The current board design utilizes the space for placement of the external termination resistors. (More information on termination is provided in AN8020). The 0402 chip resistor pads are

provided on the bottom side of the evaluation board. Solder the chip resistors to the bottom side of the board between the appropriate input of the device pin pads and the ground pads as shown in Figure 5 (for split power supply setup, PCB is assembled in this configuration).

Figure 5. Expanded Bottom View

Likewise for CML outputs, CML stimulus signal need to be terminated to  $V_{CC}$  via a 50  $\Omega$  resistor. To accomplish this configuration the external termination resistor has to be moved from SMA\_GND ring to  $V_{CC}$  ring on the bottom of the board.

For the LVDS configuration Input pin pads of the D0 or D1 input has to be shorted using 100  $\Omega$  resistor across differential lines.

### **DUT Termination**

For standard lab setup and test, a split (dual) power supply is required enabling the 50  $\Omega$  internal impedance in the oscilloscope to be used as a termination of the signals (in split power supply setup SMA\_GND as a system ground,  $V_{CC}$ , and  $V_{EE}$  are varied; see Table 1, Power Supply Levels).

#### **Board Components Configuration**

The NB4N11MDTEVB evaluation board requires six side SMA connectors. Placement locations are described in the Table 2 below.

| Device               | J1/Q0         | J2/Q0         | J3/Q1         | J4/Q1         | J5                 | J6/D         | J7/D         | J8                 |

|----------------------|---------------|---------------|---------------|---------------|--------------------|--------------|--------------|--------------------|

| Pin #                | 1             | 2             | 3             | 4             | 5                  | 6            | 7            | 8                  |

| Connector            | Yes           | Yes           | Yes           | Yes           | No                 | Yes          | Yes          | No                 |

| Resistor<br>(bottom) | 0402*<br>50 Ω | 0402*<br>50 Ω | 0402*<br>50 Ω | 0402*<br>50 Ω | 0402<br>0.01 μF    | 0402<br>50 Ω | 0402<br>50 Ω | 0402<br>0.01 μF    |

| Wire                 | No            | No            | No            | No            | to V <sub>EE</sub> | No           | No           | to V <sub>CC</sub> |

#### **Table 2. SMA Connector and Jumper Placement**

\*Optional components for 25  $\Omega$  load. Not populated in production

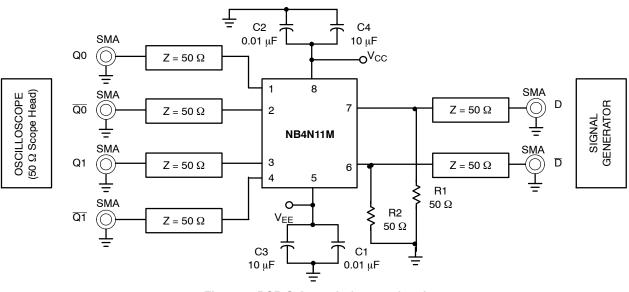

Figure 6. Lab Setup

- 1. Connect appropriate power supplies to V<sub>CC</sub>, V<sub>EE</sub>, and SMA\_GND (See Table 1)

- 2. Connect a signal generator to the input SMA connectors via matched cables. Setup input signal according to the device data sheet

- 3. Connect a test measurement device on the device output SMA connectors via matched cables.

- NOTE: The test measurement device must contain 50  $\Omega$  termination.

Figure 7. PCB Schematic for 50  $\Omega$  Load (PCB is assembled in this configuration)

\*50  $\Omega$  resistors must be added for 25  $\Omega$  load configuration

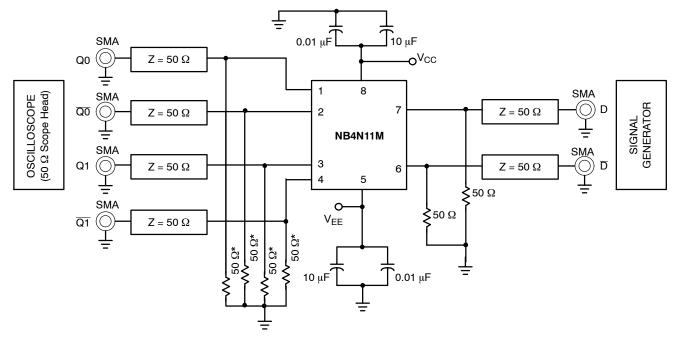

Figure 8. PCB Schematic for 25  $\Omega$  Load (50  $\Omega$  output resistors (Q0, Q0, Q1, Q1) not assembled )

#### Table 3. Bill of Materials

| Components                    | Manufacturer        | Description                                                       | Part Number    | Qty. | Web Site                         |

|-------------------------------|---------------------|-------------------------------------------------------------------|----------------|------|----------------------------------|

| SMA<br>Connector              | Johnson*            | SMA Connector – Side<br>Launch                                    | 142-0701-851   | 6    | http://www.johnsoncomponents.com |

| 9 Pin D–Sub<br>Receptacle     | Amphenol            | Connector, Female,<br>9–Pin, Right Angle                          | 788796–1       | 1    | http://www.amphenol.com          |

| Surface Mount<br>Test Points† | Keystone*           | SMT Miniature Test<br>Point                                       | 5015           | 3    | http://www.keyelco.com           |

|                               |                     | SMT Compact Test<br>Point                                         | 5016           |      |                                  |

| Chip                          | AVC                 | 0402 0.01 $\mu\text{F}~\pm~10\%$                                  | 04025C103KAT2A | 2    | http://www.avxcorp.com           |

| Capacitor                     | Corporation*        | 10 $\mu F$ $\pm$ 10%                                              | T491C106K016AS | 2    |                                  |

| Chip Resistor                 | Panasonic*          | 0402 50 $\Omega \pm 1\%$<br>Precision Thick Film<br>Chip Resistor | ERJ-2RKF49R9X  | 2    | http://www.panasonic.com         |

| Evaluation<br>Board           | ON<br>Semiconductor | Micro-10 Evaluation<br>Board                                      | N/A            | 1    | http://www.onsemi.com            |

| Device<br>Samples             | ON<br>Semiconductor | Micro-10 Package<br>Device                                        | NB4N11MM       | 1    | http://www.onsemi.com            |

\*Components are available through most distributors, i.e. www.newark.com, www.Digikey.com

+Surface Mount Test Points can be used for power supply connection in place of power supply cable connector. See Figure 4 for test point placement.

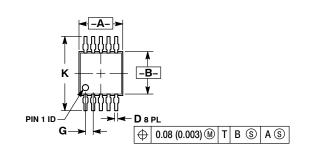

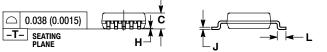

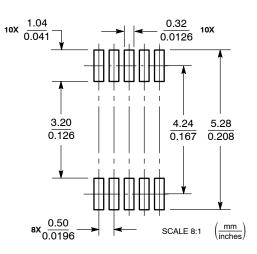

## PACKAGE DIMENSIONS

Micro-10 CASE 846B-03 ISSUE D

**SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

NOTES:

- VOTES:

DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSION "A" DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006)

- BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE. DIMENSION "B" DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE. 846B-01 OBSOLETE. NEW STANDARD 846B-02 4.

- 5.

|     | MILLIMETERS |      | INCHES    |       |  |

|-----|-------------|------|-----------|-------|--|

| DIM | MIN         | MAX  | MIN       | MAX   |  |

| Α   | 2.90        | 3.10 | 0.114     | 0.122 |  |

| В   | 2.90        | 3.10 | 0.114     | 0.122 |  |

| С   | 0.95        | 1.10 | 0.037     | 0.043 |  |

| D   | 0.20        | 0.30 | 0.008     | 0.012 |  |

| G   | 0.50 BSC    |      | 0.020 BSC |       |  |

| Н   | 0.05        | 0.15 | 0.002     | 0.006 |  |

| J   | 0.10        | 0.21 | 0.004     | 0.008 |  |

| Κ   | 4.75        | 5.05 | 0.187     | 0.199 |  |

| L   | 0.40        | 0.70 | 0.016     | 0.028 |  |