# **3.3 V Automotive Grade LVDS Line Receiver**

#### Description

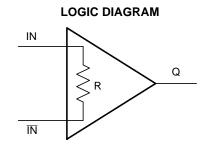

The NBA3N012C is a single LVCMOS Output Differential Line Receiver for Low Power and high data rate Automotive applications. The device is optimized to support data rate higher than 400 Mbps (200 MHz). The NBA3N012C accept directly LVDS signal as an input and translate it to LVCMOS output levels. The device includes an input termination resistor minimizing number of the external components for point to point interface.

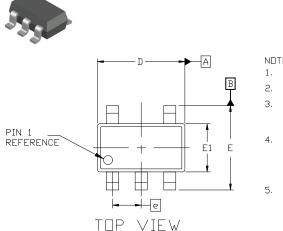

The NBA3N012C is offered in 5 lead SOT23 package and it is shipping in 3000 pcs tape & reel.

#### Features

- Compatible with TIA/EIA-644A Standard

- Automotive Grade AECQ-100 Grade 1

- > 400 Mbps (200 MHz) Data Rate

- Operating Range:  $V_{DD} = 3.3 \text{ V} \pm 0.3 \text{ V}$

- Typical 100 ps Differential Skew

- Maximum Propagation Delay of 3.5 ns

- Low Power Dissipation (Typical 20 mW @ 3.3 V)

- SOT23-5 Lead Package with Pinout optimized for easy PCB Layout

- Integrated Line Termination Resistor of  $100 \Omega$

- Power Down High Impedance on LVDS Pins

- Inputs Accept LVDS/CML/LVPECL Signals

- Temperature Operating Range –40°C to +125°C

- These are Pb–Free Devices

## **Typical Applications:**

- Automotive: Head Lamp Lighting for Cars

- Telecom: Wireless, Microwave and Optical

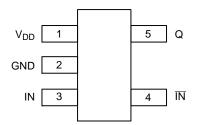

#### Table 1. PIN DESCRIPTION

| Pin Number | Pin Name        | I/O Type | Description             |

|------------|-----------------|----------|-------------------------|

| 1          | V <sub>DD</sub> |          | Power Supply Pin        |

| 2          | GND             |          | Ground Pin              |

| 3          | IN              | Input    | Non–Inverting Input Pin |

| 4          | ĪN              | Input    | Inverting Input Pin     |

| 5          | Q               | Output   | Output Pin              |

## Table 2. TRUTH TABLE

| Inputs                                  | Output |

|-----------------------------------------|--------|

| [IN] – [ <del>ĪN</del> ]                | Q      |

| V <sub>ID</sub> ≥ +0.1 V                | Н      |

| $V_{ID} \leq -0.1 V$                    | L      |

| Full Fail Safe OPEN/SHORT or terminated | H or L |

# **ON Semiconductor®**

#### www.onsemi.com

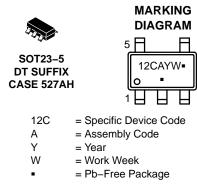

(Note: Microdot may be in either location)

#### PINOUT DIAGRAM

#### **ORDERING INFORMATION**

|       | Device     | Package              | Shipping <sup>†</sup> |

|-------|------------|----------------------|-----------------------|

| NBA3N | N012CSNT1G | SOT23–5<br>(Pb–Free) | 3000 / Tape &<br>Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

#### Table 3. ATTRIBUTES (Note 1)

|                     | Value                                                          |          |                                       |  |

|---------------------|----------------------------------------------------------------|----------|---------------------------------------|--|

| ESD Protection      | Human Body Model (JEDEC Standard 22, Method A114–E)            | All Pins | ≥ 8 kV                                |  |

|                     | Charge Device Model (JEDEC Standard 22, Method C101D) All Pins |          |                                       |  |

|                     | Moisture Sensitivity (Note 1)                                  |          | Level 1                               |  |

| Flammability Rating | Oxygen Index: 28 to 34                                         |          | UL 94 Code V–0 A<br>0.125 in 28 to 34 |  |

1. For additional information, see Application Note AND8003/D

#### Table 4. MAXIMUM RATINGS (Note 2)

| Symbol           | Parameter                                                                              | Rating                            | Unit |

|------------------|----------------------------------------------------------------------------------------|-----------------------------------|------|

| V <sub>DD</sub>  | Supply voltage                                                                         | $-0.30 \le V_{DD} \le +4.0$       | V    |

| V <sub>IN</sub>  | Input Voltage (IN, IN) LVDS                                                            | -0.30 to +3.90                    | V    |

| VQ               | Output Voltage (Pin Q) LVCMOS                                                          | –0.30 to (V <sub>DD</sub> + 0.30) | V    |

| I <sub>OS</sub>  | Output Short Circuit Current (Pin Q)                                                   | -100                              | mA   |

| Tj               | Maximum Junction Temperature                                                           | 135                               | °C   |

| Tstg             | Storage Temperature Range                                                              | -65 to +150                       | °C   |

| $\theta_{JC}$    | Thermal resistance (Junction-to-Case) - (Note 3)                                       | 107                               | °C/W |

| $\theta_{JA}$    | Thermal resistance (Junction-to-Ambient) - (Note 3)                                    | 138.5                             | °C/W |

| T <sub>sol</sub> | Lead Temperature Soldering (4 Seconds) – SOLDERRM/D                                    | 260                               | °C   |

| PD               | Package Power Dissipation @ $25^{\circ}C$ – Derating of 7.22 mW/°C above $25^{\circ}C$ | 794                               | mW   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.The maximum ratings applied are individual stress limit values and not valid simultaneously.

3. JEDEC standard multilayer board -2S2P (2 signal 2 power)

#### Table 5. DC CHARACTERISTICS V<sub>DD</sub> = 3.3 V $\pm$ 0.3 V, GND = 0 V, T<sub>A</sub> –40°C to +125°C (Note 4)

| Symbol          | Parameter                    | Test Conditions                                                                                  | Min  | Тур  | Max  | Unit |

|-----------------|------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>DD</sub> | No Load Supply Current       | Pin: V <sub>DD</sub> ; Inputs Open                                                               |      | 5.4  | 9    | mA   |

| V <sub>OH</sub> | Output High Voltage          | Pin: Q; $I_{OH} = -0.4 \text{ mA}$ ,<br>Inputs shorted or terminated, $V_{ID} = +200 \text{ mV}$ | 2.4  | 3.1  |      | V    |

| V <sub>OL</sub> | Output Low Voltage           | Pin: Q; $I_{OL}$ = 2 mA, $V_{ID}$ = -200 mV                                                      |      | 0.3  | 0.5  | V    |

| I <sub>OS</sub> | Output Short Circuit Current | Pin: Q; $V_Q = 0 V$                                                                              | –15  | -50  | -100 | mA   |

| V <sub>CL</sub> | Input Clamp Voltage          | I <sub>CL</sub> = -18 mA                                                                         | -1.5 | -0.7 |      | V    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

– minus sign indicated only direction. Current into the device is defined as positive. I<sub>OS</sub> is specified as magnitude only.

#### Table 6. ELECTRICAL CHARACTERISTICS V<sub>DD</sub> = $3.3 \text{ V} \pm 0.3 \text{ V}$ , GND = 0 V, T<sub>A</sub> -40°C to +125°C, Pin: IN/IN (Note 5)

| Symbol           | Parameter                         | Test Conditions                                    |                                  | Min | Тур | Max  | Unit |

|------------------|-----------------------------------|----------------------------------------------------|----------------------------------|-----|-----|------|------|

| V <sub>TH</sub>  | Differential Input High Threshold | V <sub>CM</sub> dependent                          | $V_{CM}$ dependent on $V_{DD}$   |     | +30 | +100 | mV   |

| V <sub>TL</sub>  | Differential Input Low Threshold  |                                                    |                                  |     | -30 |      | mV   |

| V <sub>CM</sub>  | Offset Voltage                    |                                                    |                                  | 0.1 |     | 2.35 | V    |

| I <sub>IN</sub>  | Input Current                     | V <sub>IN</sub> = +2.8 V                           | $V_{DD} = 0 V \text{ or } 3.6 V$ | -10 | ±1  | +10  | μΑ   |

|                  |                                   | $V_{IN} = 0 V$                                     |                                  | -10 | ±1  | +10  | μΑ   |

|                  |                                   | V <sub>IN</sub> = +3.6 V                           | $V_{DD} = 0 V$                   | -20 |     | +20  | μΑ   |

| I <sub>IND</sub> | Differential Input Current        | V <sub>IN</sub> = +0.4 V, V <sub>IN</sub>          | v +0 V                           | 3.0 | 3.9 | 4.4  | mA   |

|                  |                                   | V <sub>IN</sub> = +2.4 V, V <sub>IN</sub> = +2.0 V |                                  |     |     |      |      |

| R <sub>T</sub>   | Integrated Termination Resistor   |                                                    |                                  |     | 100 |      | Ω    |

| C <sub>IN</sub>  | Input Capacitance                 | $IN = \overline{IN} = GND$                         |                                  |     | 3   |      | pF   |

5. - minus sign indicated only direction. Current into the device is defined as positive.

## NBA3N012C

#### **Table 7. SWITCHING CHARACTERISTICS**

| Symbol                | Parameters                                                                | Min | Тур | Max | Unit |

|-----------------------|---------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>pHLD</sub>     | High to Low Differential Propagation Delay                                | 1.0 | 1.8 | 3.5 | ns   |

| t <sub>pLHD</sub>     | Low to High Differential Propagation Delay                                | 1.0 | 1.7 | 3.5 | ns   |

| t <sub>r</sub>        | Rise Time – Transition Low to High                                        |     | 350 | 800 | ps   |

| t <sub>f</sub>        | Fall Time – Transition High to Low                                        |     | 175 | 800 | ps   |

| t <sub>SKD(P)</sub>   | Differential Pulse Skew  t <sub>pHLD</sub> - t <sub>pLHD</sub>   (Note 7) | 0   | 100 | 400 | ps   |

| t <sub>SKD(PP)1</sub> | Part to Part Skew – (Note 8)                                              | 0   | 0.3 | 1.0 | ns   |

| t <sub>SKD(PP)2</sub> | Part to Part Skew – (Note 9)                                              | 0   | 0.4 | 2.5 | ns   |

| f <sub>MAX</sub>      | Maximum Operating Frequency – (Note 10)                                   |     | 250 |     | MHz  |

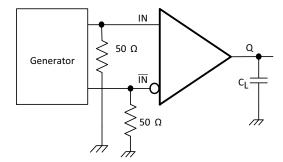

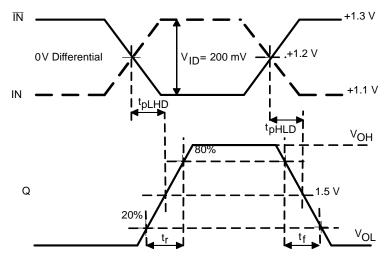

Test Conditions for the above – V<sub>ID</sub> = 200 mV, C<sub>L</sub> = 15 pF (includes Load & Jig Capacitance), Figures 1 and 2

|t<sub>PHLD</sub> – t<sub>PLHD</sub>|, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

8. Differential Part to Part Skew, is defined as the difference between the minimum and maximum specified differential propagation delays. This specification applies to devices at the same V<sub>DD</sub> and within 5°C of each other within the operating temperature range.

9. Part to part skew, is the differential channel to channel skew of any event between devices. This specification applies to devices over recommended operating temperature and voltage ranges, and across process distribution. t<sub>SKD2</sub> is defined as |Max - Min| differential propagation delay.

10.  $f_{MAX}$  Input Conditions:  $t_r = t_f < 1$  ns (0% to 100%), Duty Cycle 50%, differential (1.05 V to 1.35 V Peak to Peak).  $f_{MAX}$  Output Conditions:  $V_{OL}$  (Max 0.4 V),  $V_{OH}$  (min 2.4 V), Load = 15 pF (stray + probe), Duty Cycle 60%/40%

#### PARAMETER MEASUREMENT:

Figure 1. Receiver Propagation Delay & Transition Time Test Circuit

Figure 2. Receiver Propagation Delay & Transition Time Waveforms

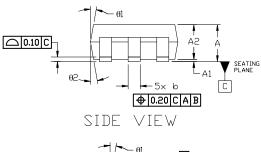

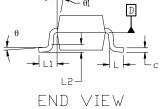

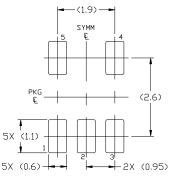

#### SOT-23, 5 Lead CASE 527AH **ISSUE A**

DATE 09 JUN 2021

NDTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 19894

- CONTROLLING DIMENSION: MILLIMETERS

- MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF THE BASE MATERIAL

- DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.25 PER SIDE. D AND E1 DIMENSIONS ARE DETERMINED AT DATUM D.

- DIMENSION 'b' DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE 'b' DIMENSION AT MAXIMUM MATERIAL CONDITION. MINIMUM SPACE BETWEEN PROTRUSION AND AN ADJACENT LEAD SHALL NOT BE LESS THAN 0.07mm.

GENERIC **MARKING DIAGRAM\***

XXX = Specific Device Code = Date Code М

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

|            | MILLIMETERS |          |      |  |  |

|------------|-------------|----------|------|--|--|

| DIM        | MIN.        | NDM.     | MAX. |  |  |

| Α          | 0.90        | _        | 1.45 |  |  |

| A1         | 0.00        | —        | 0.15 |  |  |

| A2         | 0.90        | 1.15     | 1.30 |  |  |

| b          | 0.30        | —        | 0.50 |  |  |

| С          | 0.08        | _        | 0.22 |  |  |

| D          | 2.90 BSC    |          |      |  |  |

| E          | 2.80 BSC    |          |      |  |  |

| E1         | 1.60 BSC    |          |      |  |  |

| е          | 0           | 0.95 BSC |      |  |  |

| L          | 0.30        | 0.45     | 0.60 |  |  |

| L1         | 0.60 REF    |          |      |  |  |

| L2         | 0.25 REF    |          |      |  |  |

| θ          | 0*          | 4°       | 8*   |  |  |

| 01         | 0*          | 10°      | 15°  |  |  |

| θ <b>2</b> | 0°          | 10°      | 15°  |  |  |

#### RECOMMENDED MOUNTING FOOTPRINT

For additional information on our Pb-Free strategy and soldering details, please download the DN Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON34320E    | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOT-23, 5 LEAD |                                                                                                                                                                                   | PAGE 1 OF 1 |  |

ON Semiconductor and 🔘 are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.