## onsemi

## Bluetooth<sup>®</sup> 5.2 Wireless MCU RSL15

#### Introduction

RSL15 is an ultra-low power secure Arm<sup>®</sup> Cortex<sup>®</sup>-M33 processor-based Bluetooth Low Energy 5.2 wireless MCU designed for connected smart devices in industrial and medical applications. The comprehensive, yet easy-to-use Software Development Kit (SDK) provides sample applications that demonstrate the hardware capabilities to enable security with the Cybersecurity Platform, acquire sensor data in Smart Sense mode, configure the built-in power management and utilize Bluetooth Low Energy features.

#### **Key Features**

- Bluetooth Low Energy 5.2 Certified with Key Features:

- Up to 10 simultaneous connections

- Long Range (Coded PHY)

- 2 Mbit PHY (High Speed)

- Angle of Arrival (AoA) and Angle of Departure (AoD)

- Extended Advertising

- Backwards compatibility and support for earlier Bluetooth Low Energy specifications including 5.1, 5.0, 4.2, 4.1 and 4.0

- Ultra-low Power Operation:

- Sleep Mode (GPIO Wakeup) @ 3 V VBAT: 36 nA

- Sleep Mode (Crystal Oscillator, RTC Timer Wakeup) @ 3 V VBAT: 57 nA

- Smart Sense Mode allows some digital and analog peripherals to remain active to monitor and acquire data from external sensors at a very low system–level power consumption

- Continuous ADC operation in Smart Sense Mode with wakeup on ADC threshold @ 3 V VBAT: 206 nA

- Peak Rx Current 1 Mbps @ 3 V VBAT: 2.7 mA

- Peak Tx Current 0 dBm Output Power @ 3 V VBAT: 4.3 mA

- Non-Connectable Advertising at 5 s Intervals @ 3 V VBAT: 1.1 μA (Average)

- Connectable Advertising at 5 s Intervals @ 3 V VBAT: 1.3 μA (Average)

- Rx Sensitivity (BLE Mode, 1 Mbps): -96 dBm

- Rx Sensitivity (BLE Mode, 2 Mbps): -94 dBm

- Configurable Tx Power: -17 dBm to +6 dBm

- Data Rate of 62.5 kbps to 2000 kbps

- Arm Cortex-M33 processor clocked up to 48 MHz

- Cybersecurity Platform with Arm CryptoCell<sup>™</sup>-312 for End-to-end Product Security with Secure Boot, Root of Trust, Lifecycle Management, Secure Key Management, and Application and Data Security

- Arm TrustZone<sup>®</sup> to enable secure execution zones

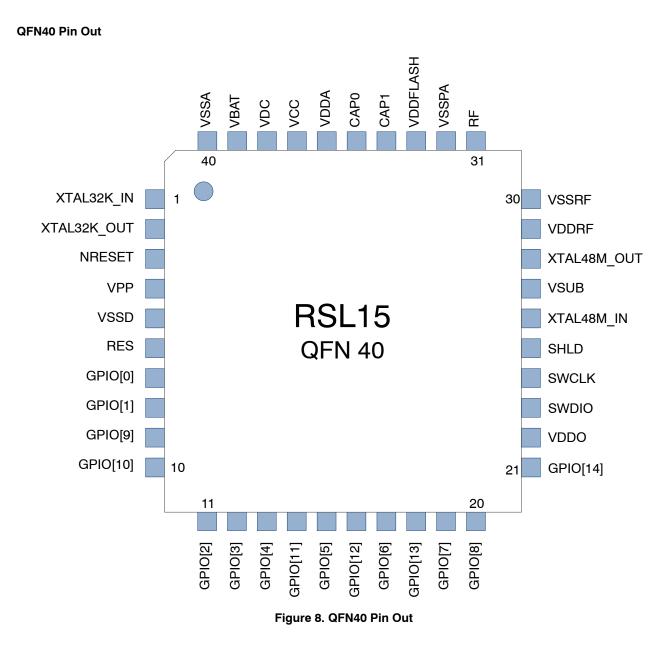

- Two flash memory sizes available, 284 KB Flash (QFN only) or 512 KB Flash

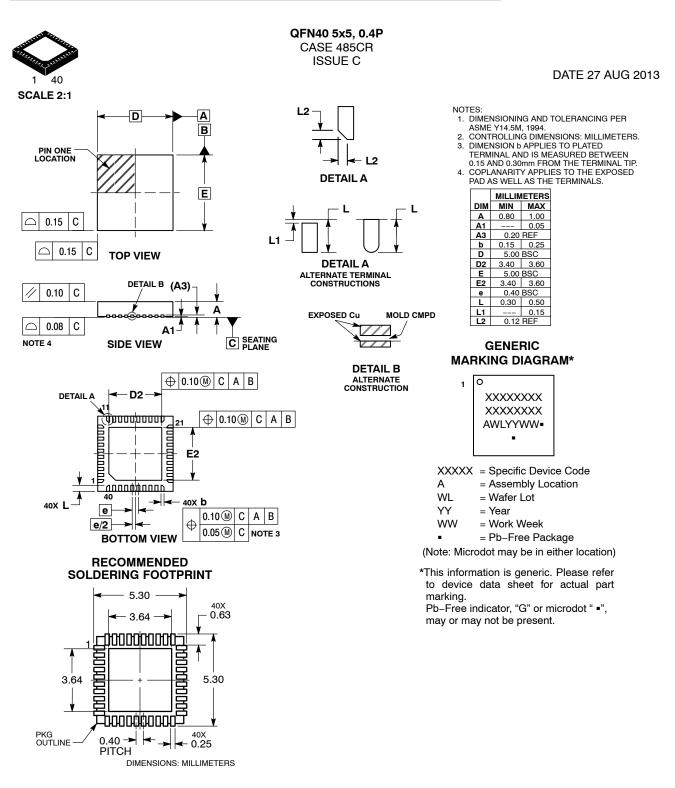

#### MARKING DIAGRAM

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

Throughout this document, in reference to memory sizes, the unit KB denotes 1024 Bytes.

#### Key Features (continued)

- 80 KB RAM (64 KB user RAM, 16 KB RAM for Baseband)

- Flexible Power Management: 1.2 V – 3.6 V VBAT. Directly connect 1.5 V Silver–oxide or 3 V Coin Cells without any external active components

- Two SPI ports with QSPI capability

#### **ORDERING INFORMATION**

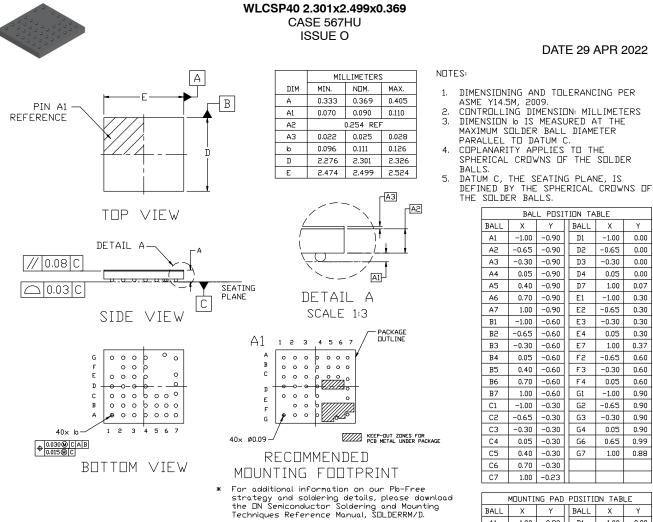

| Device                    | Flash Memory | Package | Shipping       |

|---------------------------|--------------|---------|----------------|

| NCH-RSL15-284-101Q40-ACG  | 284 KB       | QFN40   | 1500 Tape/Reel |

| NCH-RSL15-512-101Q40-ACG  | 512 KB       | QFN40   | 1500 Tape/Reel |

| NCH-RSL15-512-101WC40-ABG | 512 KB       | WLCSP40 | 1500 Tape/Reel |

#### **APPLICATIONS**

#### **Connected Device**

- Drug Injection Pens

- Blood Glucose Meters

- Wearable Bracelets

- Blood Analyzers

- Virus Detectors

- Smart Toothbrushes

- Heart Rate Monitors

- Bottle Caps

- Sleep Monitors

- Avalanche Detectors

- Electronic Pens

- Electronic Bikes

- Bicycle Computers

- Pet Trackers

- E-Stethoscopes

- Shavers

- Vacuum Cleaners

- SpO2 Monitors

- Wearable Head Bands

#### **Smart Building**

- Electronic Access Badges

- Air Filter Sensors

- Windows Surveillance

- Smoke Alarms

- Key Pads

- Energy Harvesting Switches

- HVAC Systems

- Vending Machines

- Lighting Control

#### **Smart Industry**

- Electronic Tags

- Power Tools

- Shopping Cart Trackers

- Coldchain Monitors

- Electronic Labels

- Beverage Dispensers

- Charge Control Systems

- Worker Safety Applications

- Battery Management Systems

- Machine Monitors

- Data Loggers

- Helmets

- Pellet Tracking

- Electronic Wheel Nuts

- Food Tracking Sensors

#### **Smart Home**

- Smart Circuit Breakers

- Smart Thermometers

- Smart Light Switches

- Smart Meters

- Coffee Makers

- Smart Refrigerators

- Air Purifiers

- Garage Door Controls

- Sprinkler Control Systems

#### **Smart City**

- People and Asset Tracking

- Door Access Control

- Fleet Management Systems

- Outdoor Robots

- Bioprocessing Equipment

- Educational Robots

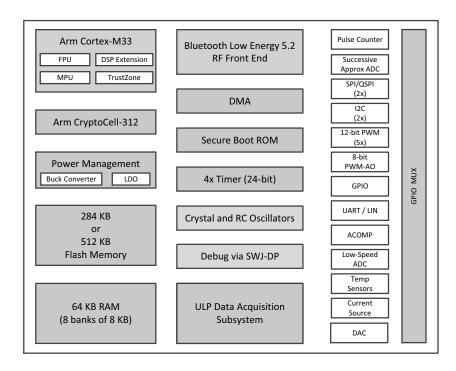

#### **HIGH-LEVEL BLOCK DIAGRAM**

Figure 1. High–Level Block Diagram

#### FEATURES

#### Arm Cortex-M33 Processor

The Cortex–M33 32–bit Armv8–M processor is designed for IoT and deeply embedded applications that require high performance, power efficiency and security. The processor has many features to execute high performance applications such a Floating–Point Unit (FPU), DSP extensions and Memory Protection Unit (MPU). Secure debug is done through the SWJ–DP which combines JTAG–DP and SW–DP for either JTAG probe or Serial Wire Debug (SWD) connection.

#### **Cybersecurity Platform**

The Cortex–M33 processor with TrustZone Armv8–M security extensions forms the basis of the security platform. The Arm CryptoCell–312 allows for end–to–end product security with Secure Boot with Root of Trust, secure lifecycle management, secure key management, and application and data encryption using symmetric or asymmetric cryptography. Arm TrustZone enables secure software access control. User available cryptographic services such as SHA1, SHA256, keyed–hash message authentication code (HMAC) and True Random Number Generator (TRNG) allow for development of custom proprietary security solutions. The TRNG conforms to NIST SP800–90B, NIST SP800–22, FIPS 140–2, and BSI AIS–31.

Please note that this mobile telecommunications Radio Access Network (RAN) equipment is designed for civil use, which also meet the provisions of paragraphs a.2 to a.4 of the Cryptography Note (Note 3 in Category 5—Part 2), having an RF output power limited to 0.1 W (20 dBm) or less, and supporting 16 or fewer concurrent users.

#### **RF Subsystem**

The RF architecture is based on a 2.4 GHz RF Front End that implements the physical layer of the BLE 5.2 standard as well as other proprietary or custom protocols. The modem is of the FSK type with a single–ended RF Port, which alleviates the need for an external balun.

#### **RF Operation**

Bluetooth 5.2 certified baseband and protocol stack has features such as 2 Mbps RF link, Angle–Of–Arrival, Angle–Of–Departure, and Coded PHY ("Long Range"). The hardware enables implementation of custom protocols.

#### Localization

RSL15 supports Angle-of-Arrival (AoA) and Angle-of-Departure (AoD) as defined by the Bluetooth Low Energy standard along with RSSI for enhanced localization capabilities.

#### **Flexible Power Management**

Built-in DC-DC converter with buck and LDO modes requiring few external passive components allows for a

broad voltage supply range. Any voltage in the range of 1.2 V to 3.6 V can be used directly without the need for external power conversion allowing for simple use of common coin cell batteries such as 3 V coins cells and 1.5 V silver oxide cells.

#### **Power Modes**

Several power modes are available to reduce power consumption while still maintaining system responsiveness. Each mode is configurable with RAM retention and wakeup sources. Smart Sense mode allows some digital and analog peripherals to remain active to monitor and acquire data from external sensors at a very low system–level power consumption.

#### Flexible Clocking

Two crystal oscillators and two internal RC oscillators are available on RSL15 to offer many clocking configurations. The primary oscillator is based on a 48 MHz crystal, which is necessary for any connected RF operation. The secondary oscillator is based on a 32 kHz crystal, which can be used for precision timing even in low power modes. When precision timing is not required, the internal fast RC oscillator can be used in place of the 48 MHz crystal oscillator for general non–RF processing. Likewise, the internal 32 kHz RC oscillator can be used in place of the 32 kHz crystal oscillator for certain use cases. Additionally, 48 MHz and 32 kHz external clocks can be driven into RSL15 from external clock sources.

#### Analog to Digital Converters (ADCs)

RSL15 has two ADCs, a high–speed 12–bit SAR ADC for fast conversion of analog inputs up to 2 Msps and Low Speed ADC for slower conversion up to 50 ksps. There is also an integrated temperature sensor that can be read by the Low Speed ADC.

#### Flexible I/O

General purpose I/O can be mapped to GPIO, SPI, QSPI, I2C, UART, LIN, PWM, PCM, pulse counter, clock input/output and analog functions. RSL15 facilitates an analog comparator, as well as a DAC for generating bias voltages for external components, and a current source output.

#### **Memory Architecture**

The memory architecture is centered around the Arm Cortex–M33. The flash memory contains application code as well as the protocol stack. The RAM architecture is flexible allowing for powering only the amount of memory needed for the application. A total of 64 KB user RAM is available, implemented as eight times 8 KB. An additional 16 KB is available for the digital baseband hardware. A DMA controller is available for easy data streaming between a peripheral/interface and memories.

#### Software Development Kit

Contains Eclipse-based **onsemi** IDE plus support for other industry standard development environments, Bluetooth protocol stack, sample applications, libraries and many other software components and tools to enable rapid application development.

#### **RoHS Compliant Device**

RSL15 is RoHS compliant.

#### ARCHITECTURE OVERVIEW

#### Introduction

RSL15 is a highly integrated secure Arm Cortex-M33 based Bluetooth Low Energy 5.2 wireless MCU system-on-chip with flash and RAM, built-in power

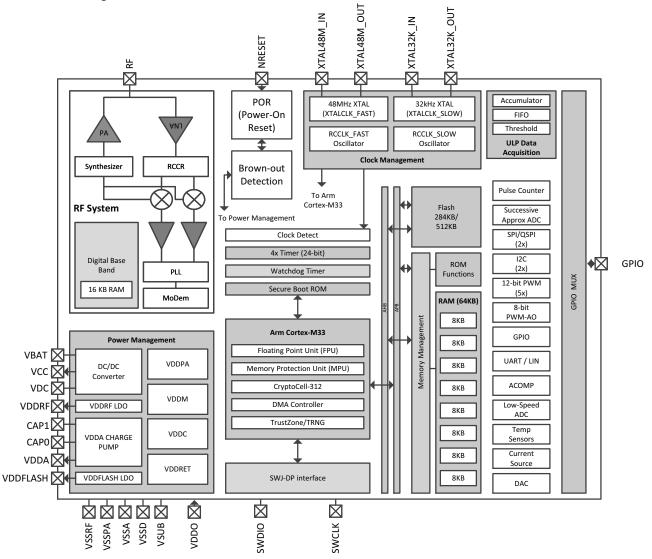

#### **Detailed Block Diagram**

Figure 2. RSL15 Detailed Block Diagram

#### Arm Cortex-M33 Processor

The Cortex–M33 32–bit Armv8–M processor is designed for IoT and deeply embedded applications that require high performance, power efficiency and security. The processor has many features to execute high performance applications such a Floating–Point Unit (FPU), DSP extensions and Memory Protection Unit (MPU). Secure debug is done through the dedicated Serial Wire Debug Port (SW–DP) interface.

#### **DMA Controller**

The Direct Memory Access (DMA) Controller allows background transfers between peripherals and memories without processor intervention. The processor can be in a low power state or used for other computational tasks while the transfer occurs. The DMA is connected to the processor, peripherals and RAM memories and has four independent channels.

management and an extensive set of peripherals. The wide

supply voltage input, flexible I/O and clocking scheme offer

maximum design flexibility.

#### **Cybersecurity Platform**

The Cortex–M33 processor with TrustZone Armv8–M security extensions forms the basis of the security platform that is extended with Arm CryptoCell–312.

#### Secure Boot with Root of Trust

The secure boot ROM authenticates firmware in flash with a certificate-based mechanism using a private-public key scheme. This is the basis of the hardware Root of Trust. This same mechanism ensures continuity of the hardware Root of Trust after secure Firmware-Over-The-Air (FOTA) update.

#### Data and Application Encryption

User available cryptographic services including AES-128, AES-256, SHA-256, Hash Message Authentication Code (HMAC), PKA (Public Key Accelerator), ChaCha and AIS-31 compliant True Random Number Generator (TRNG) allow for development of custom proprietary security solutions.

#### TrustZone

Enables secure software access control to protect critical software and hardware resources.

#### Secure Lifecycle State Management

Lifecycle states refers to the multiple states RSL15 could go through during its lifetime. The first lifecycle state is the Chip Manufacture (CM) Lifecycle State. The device manufacture transitions to the Device Manufacture (DM) Lifecycle State. At field deployment, it is transitioned to the Secure (SE) Lifecycle State. A Return to Manufacturer (RMA) State is also available. Lifecycle state management ensures the authenticity, integrity and confidentiality of code and data belonging to different stakeholders at each lifecycle.

In addition to the Secure Lifecycle States, an Energy Harvesting (EH) Mode is available for applications that require fast cold startup (initial application of VBAT) but do not require secure boot with Root of Trust. This mode is especially useful when RSL15 is used in energy harvesting systems.

#### **RF Subsystem**

The RSL15 2.4 GHz radio front-end implements the physical layer for the Bluetooth Low Energy standard and other standard, proprietary, or custom protocols.

It operates in the worldwide deployable 2.4 GHz ISM band (2.4000 to 2.4835 GHz).

#### RF Architecture

The 2.4 GHz radio front-end is based on a low-IF architecture and comprises the following building blocks:

- High performance single-ended RF port which alleviates the need for an external balun

- On-chip matching network with 50  $\Omega$  RF input

- Low power LNA (low noise amplifier), and mixer

- PA (Power Amplifier) with up to +6 dBm output power for Bluetooth

- RSSI (Received Signal Strength Indication) with 60 dB nominal range with 1 dB steps (not considering AGC)

- Fully integrated ultra-low power frequency synthesis with fast settling time, with direct digital modulation in transmission (pulse shape programmable)

- 48 MHz XTAL reference

- Fully-integrated FSK-based modem with programmable pulse shape, data rate, and modulation index

- Digital baseband (DBB) with link layer functionalities, including automatic packet handling with preamble & sync, CRC, and separate Rx and Tx 128-bytes FIFOs

- The 2.4 GHz radio front-end contains also a highly-flexible digital baseband – in terms of modulation schemes, configurability and programmability – in order to support Bluetooth Low Energy technology and proprietary protocols. It allows for programmable data rates from 62.5 kbps up to 2 Mbps, FSK with programmable pulse shape and modulation index.

- The 2.4 GHz radio front-end also includes Manchester encoding and Data whitening. The packet handling includes:

- Automatic preamble and sync word insertion

- Automatic packet length handler

- Basic address check

- Automatic CRC calculation and verification with a programmable CRC polynomial

- Multi-frame support

- Coexistence signals to identify the RF front-end is busy for Bluetooth or other traffic

#### Bluetooth Low Energy

RSL15 is Bluetooth 5.2 certified with the following Bluetooth LE features:

- Angle of Arrival (AoA) and Angle of Departure (AoD)

- LE Long Range (Coded PHY)

- 2 Mbit PHY (High Speed)

- LE Extended Advertising

- High Duty Cycle Non-Connectable Advertising

- LE Channel Selection Algorithm #2

- Advertising Channel Index

- GATT Caching

- HCI support for debug keys in LE Secure Connections

- Sleep clock accuracy update mechanism

- ADI field in scan response data

- Host channel classification for secondary advertising

- Periodic Advertising Sync Transfer

- Backwards compatibility and support for earlier Bluetooth Low Energy specifications including 5.1, 5.0, 4.2, 4.1 and 4.0

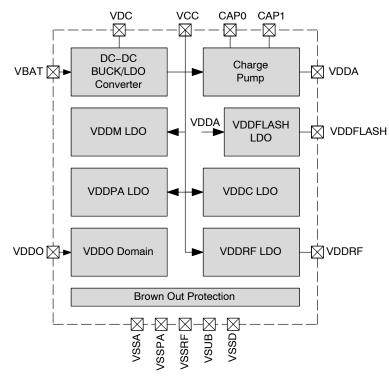

#### **Power Management**

The flexible power management of RSL15 allows for a wide range of battery voltages without the need for external power conversion. Two key modes of the DC–DC converter are:

1. BUCK Mode Operation

2. LDO Mode Operation

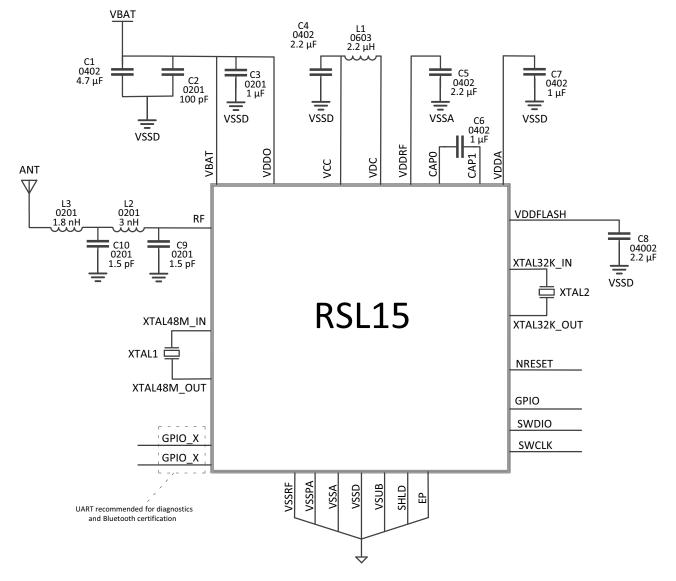

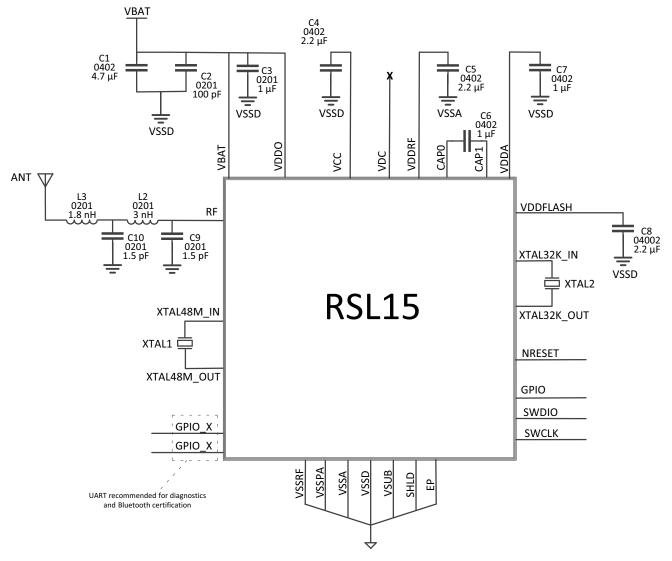

The power management unit is shown in Figure 3.

Figure 3. Power Management Unit

BUCK Mode can be used for battery voltages above 1.4 V. In this case the internal DC–DC converter regulates the battery voltage VBAT to a voltage VCC of approximately 1.2 V. The VCC voltage is then converted (using a charge pump) to an approximate 2.4 V voltage VDDA, which is used to power the analog blocks (excluding the RF Blocks). VCC and VDDA require external capacitors. Additionally, BUCK Mode Operation requires an inductor to be placed between the VCC and VDC pins.

LDO Mode is typically used for battery voltages at 1.4 V and below (but can be used for the entire operating voltage). In this case a linear LDO generates a voltage VCC of 1.2 V. A charge pump then generates a 2.4 V voltage for the analog blocks.

VDDRF is a regulated voltage used to supply the RF system. VDDRF is trimmed by **onsemi** as part of the device manufacturing process.

A separate supply exists for powering the flash, i.e. VDDFLASH. VDDFLASH is trimmed by **onsemi** as part of the device manufacturing process.

Three additional regulators generate voltages for the system (none require external components):

- VDDC is the voltage for the internal digital blocks excluding digital RAM and GPIOs. VDDC is trimmed by **onsemi** as part of the device manufacturing process

- VDDM is the voltage for the RAM blocks. VDDM is trimmed by **onsemi** as part of the device manufacturing process

- VDDPA is the voltage used to supply the RF power amplifier (used in RF Tx mode). The VDDPA setting depends on the output power level selected

VDDO is an input to the RSL15 and constitutes the logical high level for the digital I/Os, i.e. if VDDO is connected to VBAT the GPIO signal swing will be between GND and VBAT.

The RSL15 power management unit allows for operation across wide temperature and voltages ranges at low power consumption and monitors the battery voltage to ensure reliable operation. If the battery voltage dips below the Power–On Reset (POR) voltage, a POR is asserted to the system. This also prevents possible damage to RSL15 when the battery is inserted or removed.

#### Reset

The Power Management Unit automatically resets the internal systems during power supply disruptions such as insufficient battery voltage or during battery insertion/removal. Upon power supply rise (such as battery insertion), the system is held in Power–On–Reset until sufficient internal voltages are reached and stabilized. When POR is released, the boot ROM execution begins using the RCCLK clock @ 3 MHz.

A reset can also be issued by software, watchdog timer expiration, invalid or missing clock detected by the clock detector, or by asserting the nRESET pin.

#### **Power Modes Overview**

The power modes are available to reduce power consumption while still maintaining system responsiveness. The low power modes are Sleep, Standby, Smart Sense and Idle.

Sleep Mode is the lowest power mode but with the longest wakeup time.

Standby Mode is low power but with faster wakeup time than Sleep Mode.

Smart Sense mode takes advantage of the low power capability of Sleep Mode but also allows some digital and analog peripherals to remain active with minimal processor intervention. Smart Sense mode allows RSL15 to not only remain responsive to external events, but also monitor and acquire data from external sensors with very low system–level power consumption.

Idle Mode allows for some power savings with the fastest wakeup time through disabling of internal clocks.

Sleep, Standby and Smart Sense modes have the ability of RAM retention (configurable amount of RAM to be retained) and allow for configurable wakeup sources.

Wakeup sources include GPIO transition (pin-based wakeup), timer, comparator, ADC threshold or sample FIFO full.

An overview of the power modes is shown in Table 1. The peripherals and subsystems available in each power mode are described below.

| Table 1. POWER MODES OVERVIEW | Table 1. | POWER | MODES | OVERVIEW |

|-------------------------------|----------|-------|-------|----------|

|-------------------------------|----------|-------|-------|----------|

| Power Mode       | Description                                                                                                                                                                                                                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sleep Mode       | The lowest power mode. Processor and RF subsystem powered down and not clocked.<br>Only selected wakeup sources are powered. Memory retention (and amount of memory retained)<br>is optional. Some peripherals are available in Sleep Mode. On wakeup, the ROM restores the<br>system before program execution begins.                                                     |

| Smart Sense Mode | Smart Sense Mode takes advantage of the low power capability of Sleep Mode but also allows some digital and analog peripherals to remain active with minimal processor intervention. Smart Sense Mode allows RSL15 to not only remain responsive to external events, but also monitor and acquire data from external sensors at a very low system-level power consumption. |

| Standby Mode     | A low power mode with faster wakeup time than Sleep Mode. Processor and RF subsystem<br>powered with lower voltage and not clocked. Only selected wakeup sources are powered.<br>Memory retention (and amount of memory retained) is configurable. Some peripherals are<br>available in Standby Mode. On wakeup, the program is executed directly out of retained RAM.     |

| Idle Mode        | A mode to save power for a short period of time when very fast wakeup is required. Processor, RF subsystem and memory powered as in Run Mode but not clocked.                                                                                                                                                                                                              |

| Run Mode         | Processor, RF subsystem and memory powered normally – clocks are active, all peripherals available.                                                                                                                                                                                                                                                                        |

#### Peripherals and Subsystems Availability in Power Modes

The different power modes allow for low power operation in many types of applications. When applications utilize one or more external sensors that require continued biasing regardless of the power mode of RSL15, it may be possible to use the VDDA voltage for this purpose. VDDA can be kept active even in Sleep, Smart Sense and Standby Modes.

Table 2 describes the peripherals available in all power modes.

|                                   | Power Mode |      |           |             |           |  |  |  |  |

|-----------------------------------|------------|------|-----------|-------------|-----------|--|--|--|--|

| Component                         | Run        | ldle | Standby   | Smart Sense | Sleep     |  |  |  |  |

| Processor                         | On         | On   | Off       | Off         | Off       |  |  |  |  |

| Baseband/RF                       | On         | Off  | Off       | Off         | Off       |  |  |  |  |

| RAM Retention                     | n/a        | n/a  | Available | Available   | Available |  |  |  |  |

| CryptoCell                        | On         | On   | On or Off | On or Off   | On or Off |  |  |  |  |

| RTC                               | On         | On   | On or Off | On or Off   | On or Off |  |  |  |  |

| ULP Data Acquisition<br>Subsystem | On         | On   | On or Off | On or Off   | Off       |  |  |  |  |

| Successive Approximation<br>ADC   | On         | On   | On or Off | On or Off   | Off       |  |  |  |  |

| Pulse Counter                     | On         | On   | On or Off | On or Off   | Off       |  |  |  |  |

| Comparator                        | On         | On   | On or Off | On or Off   | On or Off |  |  |  |  |

| DAC                               | On         | On   | Off       | Off         | Off       |  |  |  |  |

| ACS-PWM                           | On         | On   | On or Off | On or Off   | On or Off |  |  |  |  |

| PWM                               | On         | On   | Off       | Off         | Off       |  |  |  |  |

| Low Speed ADC                     | On         | On   | Off       | Off         | Off       |  |  |  |  |

| 32k Clock Output                  | On         | On   | On or Off | On or Off   | On or Off |  |  |  |  |

| 12C                               | On         | On   | Off       | Off         | Off       |  |  |  |  |

| SPI                               | On         | On   | Off       | Off         | Off       |  |  |  |  |

| UART                              | On         | On   | Off       | Off         | Off       |  |  |  |  |

| LIN                               | On         | On   | Off       | Off         | Off       |  |  |  |  |

| PCM                               | On         | On   | Off       | Off         | Off       |  |  |  |  |

| Current Source                    | On         | On   | Off       | Off         | Off       |  |  |  |  |

| Temp Sensor                       | On         | On   | Off       | Off         | Off       |  |  |  |  |

#### Table 2. POWER MODE PERIPHERAL AVAILABILITY

#### **ULP Data Acquisition Subsystem**

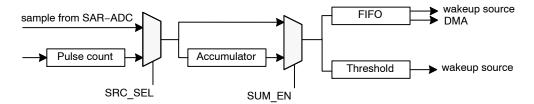

The ULP Data Acquisition Subsystem comprises a small FIFO, Accumulator and Threshold Comparator that can be used in combination with the Successive Approximation ADC and pulse counter to perform data acquisition and rudimentary data processing and decision making. Available in all power modes. This enables simple processing and storage of a limited number of samples from a pulse counter or the Successive Approximation ADC while in the low power mode, Smart Sense mode, for the lowest power operation.

Figure 4. ULP Data Acquisition Subsystem.

The ULP Data Acquisition Subsystem has various features to further reduce power consumption such as Burst Sampling Mode, which allows for bursts of high speed sampling followed by an adjustable delay between sampling bursts.

The pulse counter can be configured to accept inputs from any of GPIO[3:0]. It counts pulses from these GPIOs during a set window ranging from 1 to 1024 clock cycles (based on a 32 kHz clock).

Overall, the ULP Data Acquisition Subsystem operation can be summarized as follows:

#### Accumulation

- An accumulation can be done with a configured number of samples ranging from 1 to 16 samples

- This mode is enabled when SUM\_EN is set on Figure 4

- The accumulated value is stored in the FIFO

#### Threshold Detection

- Two thresholds can be configured: one when the input value goes higher than the threshold, and one when the input value goes lower than the threshold

- This mode allows the system to wake up after a configured number of consecutive samples generated are greater than or lower than the configurable threshold.

#### Acquisition

• Acquired samples are stored in the FIFO. FIFO size can be 1 to 16 samples

#### Clocking

#### Oscillators

The following oscillators are available:

- 48 MHz crystal oscillator (RFCLK) typically used in RUN Mode when RF operation is required. Prescalers exist to provide divided clocks (including system clock) to other parts of the system

- A fast RC oscillator (RCCLK) can provide an alternative to the 48 MHz crystal oscillator. However, RF operation is not possible using the fast RC Oscillator

- A 32 kHz crystal oscillator (XTAL32K) typically used in Sleep and Standby Modes for precision timing and to maintain the real-time clock (RTC)

- A slow RC oscillator (RC32) that can be an alternative to the 32 kHz crystal oscillator for certain use cases.

#### Clock Management

Flexible clock management allows the different clock sources to be used in power–efficient ways and to minimize external components. Internal RC oscillators can be used for fast startup and then easily switched to crystal oscillators when precision timing is required. Additionally, clocks can be sourced externally with the 48 MHz and 32 kHz clock inputs.

A built-in clock detector ensures a proper system reset in case the system clock goes below 2 kHz.

#### General Purpose Input/Output (GPIO)

RSL15 contains highly flexible general purpose input/output (GPIO) pins that can be configured as digital input or output, communication interfaces, clocks, wakeup sources or analog functions. Communication interfaces can be routed to any GPIO. Other functions are available on select GPIO, see section Pin Definition and Multiplexing.

Each GPIO has a software configurable pull up/down resistor, debounce LPF for I2C and four drive strengths options.

#### Analog

Successive Approximation ADC (SAR ADC)

The Successive Approximation ADC (SAR ADC) generates 12-bit samples up to 2 Msps sample frequency.

The SAR ADC is auto calibrated during operation for optimal INL/DNL performance.

#### Low Speed ADC Converter (LSAD)

This is a combined integrating and algorithmic ADC that has a resolution varying from 8 to 14 bits depending on configuration. While converting, the input signal can be integrated across one or more clock cycles (depending on configuration). ADC sampling rate can be up to 50 ksps. This ADC converter is also used to monitor the VBAT input voltage. It can also be configured to measure single ended or differential input voltages.

#### Pulse Counter

A pulse counter can be driven by one of GPIO[3:0]. It counts pulses from these GPIOs during a set interval.

#### Analog Comparator

RSL15 contains a low-power comparator that can be active in Standby, Sleep and Smart Sense mode. It has 3 different settings to trade off response time with power consumption, Low Power, Normal and High Speed, see section Analog Comparator Specifications (ACOMP).

#### DAC

RSL15 contains a low-power DAC that can be used for sensor biasing purposes. To optimize power consumption there is also a buffer that can be disabled if the load is high impedance.

#### **Current Source**

A built-in current source with adjustable output from  $1 \ \mu A$  to  $16 \ \mu A$ . The current source may be applied for temperature measurements using an external thermistor connected to a GPIO.

#### Peripherals

#### Timers

There are four independent 24-bit timers that can operate as single-shot, multi-shot or free-run. An interrupt can be generated on timer expiration. Also, a GPIO interrupt can capture and store the current timer value.

#### Watchdog

The independent watchdog timer cannot be disabled. It must be reloaded at regular intervals. At the first timer expiration, an interrupt is generated and the timer is reloaded. At the second timer expiration, a reset is issued to the system.

#### PWM

The PWM (Pulse Width Modulation) controller can output on five independent channels with configurable period, duty cycle and offset. The PWM has 12-bit resolution with an optional 8-bit dithering per channel for lighting applications.

Additionally, one 8-bit ACS-PWM channel fixed on GPIO[4] can be operational in low power modes.

#### I2C

The I2C controller consists of 2 independent channels of the two-wire interface including a bidirectional clock line (SCL) and bidirectional data line (SDA). The I2C interface supports both master and slave mode operation. 100 kHz, 400 kHz and 1 MHz modes are supported.

#### SPI

The SPI controller consists of 2 independent channels with the standard 4-wire interface of SCLK, MOSI, MISO and CS supporting master and slave mode. Each channel also supports dual (DSPI) and quad (QSPI) modes in half or full duplex mode.

#### UART

The general-purpose Universal Asynchronous Receiver-Transmitter (UART) uses a standard data format with one start bit, eight data bits and one stop bit.

#### LIN

The Local Interconnect Network (LIN) is an asynchronous 2–wire interface. The LIN module operates as a responder node on the bus, supporting version 2.2 of the LIN specification.

#### РСМ

The highly configurable PCM (Pulse Code Modulation) interface can be used to stream data in and out of RSL15.

#### RTC

The RTC timer consists of a 32-bit free-running up-counter, clocked by the 32 kHz clock.

#### Activity Counter

The activity counters help to analyze how long the system has been running, and how much the CPU and the flash have been used by the application in a period of time. This is useful information to estimate and optimize the power consumption of the application.

#### Asynchronous Clock Counter

The asynchronous clock counter measure the timing of a clock signal, such as STANDBYCLK or a clock provided on a GPIO input, relative to the system clock.

#### CRC

This block provides an implementation of two standard cyclic redundancy code (CRC) algorithms (CRC–CCITT and CRC–32) which, if used, can ensure data integrity of a user application's code and data.

Memory Map The RSL15 memory map is shown in Figure 5 (512 KB flash version only).

|                            | CPU access                            |

|----------------------------|---------------------------------------|

|                            | BB access                             |

|                            |                                       |

| 0x4005 3FFF                | Peripherals                           |

| 0x4000 0000                | 32-bit registers                      |

|                            | , , , , , , , , , , , , , , , , , , , |

|                            |                                       |

|                            |                                       |

| 0x2001 3FFF                |                                       |

|                            | BB_DRAM1<br>8 KB                      |

| 0x2001 2000<br>0x2001 1FFF | BB DRAMO                              |

| 0x2001 0000                | 8 KB                                  |

| 0x2000 FFFF                | DRAM7                                 |

| 0x2000 E000<br>0x2000 DFFF | 8 KB                                  |

|                            | DRAM6<br>8 KB                         |

| 0x2000 C000<br>0x2000 BFFF | DRAM5                                 |

| 0x2000 A000                | 8 KB                                  |

| 0x2000 9FFF                | DRAM4                                 |

| 0x2000 8000<br>0x2000 7FFF | 8 KB<br>DRAM3                         |

| 0x2000 6000                | 8 KB                                  |

| 0x2000 5FFF                | DRAM2                                 |

| 0x2000 4000                | 8 KB                                  |

| 0x2000 3FFF                | DRAM1                                 |

| 0x2000 2000<br>0x2000 1FFF | 8 KB<br>DRAMO                         |

| 0x2000 0000                | 8 KB                                  |

| 0x1FFF FFFF                | Chip ID                               |

| 0x1FFF FFFC                |                                       |

|                            |                                       |

|                            |                                       |

| 0x0017 FFFF                | Elach Arrow1                          |

|                            | Flash Array1<br>160 KB                |

| 0x0015 8000<br>0x0015 7FFF | Flash Array2                          |

| 0x0010 0000                | 352 KB                                |

| 0x0008 08FF                | Flash MNVR (trimming)                 |

| 0x0008 0800                | 128 B + 128 B (duplicated)            |

| 0x0008 07FF                | Flash NVR[0:7]                        |

| 0x0008 0000                | 8 * 256 B                             |

| 0x0006 11FF                | Flash Data redundancy1-2              |

| 0x0006 1000<br>0x0006 0FFF | 2 * 256 B                             |

|                            | Flash Code redundancy1-2              |

| 0x0006 0000                | 2 * 2 KB                              |

| 0x0000 7FFF                | PROM                                  |

| 0x0000 0000                | 32 KB                                 |

Figure 5. RSL15 Memory Map

#### **ELECTRICAL SPECIFICATIONS**

#### **Absolute Maximum Ratings**

#### **Table 3. ABSOLUTE MAXIMUM RATINGS**

| Symbol      | Parameter                              | Min        | Max        | Unit |

|-------------|----------------------------------------|------------|------------|------|

| VBAT        | Power supply voltage input             |            | 3.63       | V    |

| VDDO        | Digital I/O supply voltage input       |            | 3.63       | V    |

| VSSRF       | RF front-end ground                    | -0.3       |            | V    |

| VSSA        | Analog ground                          | -0.3       |            | V    |

| VSSC        | Digital ground                         | -0.3       |            | V    |

| Vin         | Voltage at any input pin               | VSSC-0.3   | VDDO + 0.3 | V    |

| Vin to LSAD | Voltage at GPIO selected as LSAD input | VSSA – 0.3 | VDDA + 0.3 | V    |

| RF          | Maximum RF Input Power                 |            | 18         | dBm  |

| T storage   | Storage temperature range (Note 1)     | -40        | 125        | °C   |

Stresses exceeding those listed in the Absolute Maximum Ratings table may damage the device.

CAUTION: Class 2 ESD Sensitivity, JESD22-A114-B HBM +/-2000 V on all pins

CDM ESD Compliance on all pins: ±500 V

Latch-up protection of ±100mA, EIA/JESD78E on all pins

1. Storage temperature applies after soldering to PCB.

#### **General Operating Conditions**

#### **Table 4. GENERAL OPERATING CONDITIONS**

| Parameter                                        | Symbol              | Conditions                                                      | Min           | Тур  | Max  | Unit |

|--------------------------------------------------|---------------------|-----------------------------------------------------------------|---------------|------|------|------|

| DC-DC Converter Input                            | VBAT                | BUCK Mode                                                       | 1.4           |      | 3.6  | V    |

| Voltage                                          |                     | LDO Mode                                                        | 1.2           |      | 3.6  |      |

| VBAT supply rise time                            |                     | Maximum rate of voltage rise                                    |               |      | 0.1  | V/µs |

| DC-DC Converter / LDO<br>Output Voltage (Note 2) | VCC                 |                                                                 | 1             | 1.2  | 1.32 | V    |

| Analog blocks supply<br>voltage output (Note 2)  | VDDA                | VDDA is generated by a charge pump that doubles the VCC voltage |               | 2.4  |      | V    |

| Flash supply voltage<br>output (Note 2)          | VDDFLASH            |                                                                 | 0.75          | 1.75 | 2.3  | V    |

| Digital I/O Supply Input<br>(Note 2)             | VDDO                |                                                                 | 1.2           |      | 3.6  | V    |

| RF Supply Output<br>(Note 2)                     | VDDRF               |                                                                 | 1.0           | 1.1  | 1.21 | V    |

| System Clock                                     | SYS_CLK             |                                                                 | 8<br>(Note 3) |      | 48   | MHz  |

| Operating Temperature                            |                     |                                                                 | -40           |      | 85   | °C   |

| POR Voltage                                      | VBAT <sub>POR</sub> |                                                                 | 0.4           | 0.8  | 1.0  | V    |

If any limits in the General Operating Conditions table are exceeded, device functionality should not be assumed. Exposure beyond maximum

VCC, VDDA, VDDFLASH and VDDRF Outputs are for connections to external filtering capacitors only. These regulated voltages are used internally and are not intended for powering external devices.

3. Minimum SYS\_CLK required for BLE Operation.

#### **Power Consumption**

#### **RF** Current Consumption

Table 5 shows key peak current consumption values for RF activity. Unless otherwise noted, the specifications

#### Table 5. RF CURRENT CONSUMPTION

mentioned in the table below are valid at  $25^{\circ}$ C, VBAT = VDDO (Buck mode for VBAT > 1.4 V, LDO mode for VBAT  $\leq$  1.4 V), 48 MHz (RFCLK) active, Radio ON and internal supplies trimmed to factory defaults.

| Operating Conditions                                       | VBAT   | DC Conversion | Min | Тур  | Max | Unit |

|------------------------------------------------------------|--------|---------------|-----|------|-----|------|

| Radio Receive Mode<br>Rx @ 125 kbps, 2.4 GHz               | 3.0 V  | BUCK Mode     |     | 2.9  |     | mA   |

| 8 MHz system clock<br>Cortex-M33 running BLE baseband only | 1.8 V  | BUCK Mode     |     | 4.4  |     |      |

| All Peripherals Disabled<br>64 KB RAM enabled              | 1.25 V | LDO Mode      |     | 6    |     |      |

| Radio Receive Mode<br>Rx @ 500 kbps, 2.4 GHz               | 3.0 V  | BUCK Mode     |     | 2.9  |     | mA   |

| 8 MHz system clock<br>Cortex–M33 running BLE baseband only | 1.8 V  | BUCK Mode     |     | 4.4  |     |      |

| All Peripherals Disabled<br>64 KB RAM enabled              | 1.25 V | LDO Mode      |     | 6    |     |      |

| Radio Receive Mode<br>Rx @ 1 Mbps, 2.4 GHz                 | 3.0 V  | BUCK Mode     |     | 2.7  |     | mA   |

| 3 MHz system clock<br>Cortex-M33 running BLE baseband only | 1.8 V  | BUCK Mode     |     | 4.3  |     |      |

| All Peripherals Disabled<br>64 KB RAM enabled              | 1.25 V | LDO Mode      |     | 5.8  |     |      |

| Radio Receive Mode<br>Rx @ 2 Mbps, 2.4 GHz                 | 3.0 V  | BUCK Mode     |     | 3.2  |     | mA   |

| 8 MHz system clock<br>Cortex-M33 running BLE baseband only | 1.8 V  | BUCK Mode     |     | 4.9  |     |      |

| All Peripherals Disabled<br>64 KB RAM enabled              | 1.25 V | LDO Mode      |     | 6.7  |     |      |

| Radio Transmit Mode<br>Tx @ 1 Mbps, 2.4 GHz, 0 dBm         | 3.0 V  | BUCK Mode     |     | 4.3  |     | mA   |

| 8 MHz system clock<br>Cortex-M33 running BLE baseband only | 1.8 V  | BUCK Mode     |     | 6.7  |     |      |

| All Peripherals Disabled<br>64 KB RAM enabled              | 1.25 V | LDO Mode      |     | 9.1  |     |      |

| Radio Transmit Mode<br>Tx @ 1 Mbps, 2.4 GHz, 3 dBm         | 3.0 V  | BUCK Mode     |     | 8    |     | mA   |

| 8 MHz system clock<br>Cortex–M33 running BLE baseband only | 1.8 V  | BUCK Mode     |     | 12.3 |     |      |

| All Peripherals Disabled<br>64 KB RAM enabled              | 1.25 V | LDO Mode      |     | 16.9 |     |      |

| Radio Transmit Mode<br>Tx @ 1 Mbps, 2.4 GHz, 5 dBm         | 3.0 V  | BUCK Mode     |     | 10.6 |     | mA   |

| 8 MHz system clock<br>Cortex-M33 running BLE baseband only | 1.8 V  | BUCK Mode     |     | 16.5 |     |      |

| All Peripherals Disabled<br>64 KB RAM enabled              | 1.25 V | LDO Mode      |     | 22.5 |     | 1    |

| Radio Transmit Mode<br>Tx @ 1 Mbps, 2.4 GHz, 6 dBm         | 3.0 V  | BUCK Mode     |     | 11.4 |     | mA   |

| 8 MHz system clock<br>Cortex–M33 running BLE baseband only | 1.8 V  | BUCK Mode     |     | 17.8 |     | 1    |

| All Peripherals Disabled<br>64 KB RAM enabled              | 1.25 V | LDO Mode      |     | 24.1 |     | 1    |

#### Run Mode Current Consumption

Table 6 shows key current consumption values for Run Mode. Unless otherwise noted, the specifications mentioned in the table below are valid at  $25^{\circ}$ C, VBAT = VDDO (Buck

mode for VBAT > 1.4 V, LDO mode for VBAT  $\leq$  1.4 V), 48 MHz (RFCLK) active, Radio OFF and internal supplies trimmed to factory defaults.

| Operating Conditions                                                                                  | VBAT   | DC<br>Conversion | Min | Тур | Max | Unit           |

|-------------------------------------------------------------------------------------------------------|--------|------------------|-----|-----|-----|----------------|

| 8 MHz system clock                                                                                    | 3.0 V  | BUCK Mode        |     | 49  |     | μA/MHz         |

| Executing CoreMark from Flash<br>All peripherals disabled                                             | 1.8 V  | BUCK Mode        |     | 76  |     | 1              |

| 64 KB RAM enabled                                                                                     | 1.25 V | LDO Mode         |     | 106 |     | 1              |

| 16 MHz system clock                                                                                   | 3.0 V  | BUCK Mode        |     | 39  |     | μA/MHz         |

| Executing CoreMark from Flash<br>All peripherals disabled                                             | 1.8 V  | BUCK Mode        |     | 58  |     | 1              |

| 64 KB RAM enabled                                                                                     | 1.25 V | LDO Mode         |     | 84  |     | 1              |

| 24 MHz system clock<br>Executing CoreMark from Flash<br>All peripherals disabled<br>64 KB RAM enabled | 3.0 V  | BUCK Mode        |     | 34  |     | μA/MHz         |

|                                                                                                       | 1.8 V  | BUCK Mode        |     | 54  |     |                |

|                                                                                                       | 1.25 V | LDO Mode         |     | 77  |     |                |

| 48 MHz system clock                                                                                   | 3.0 V  | BUCK Mode        |     | 30  |     | μ <b>A/MHz</b> |

| Executing CoreMark from Flash<br>All peripherals disabled                                             | 1.8 V  | BUCK Mode        |     | 46  |     | 1              |

| 64 KB RAM enabled                                                                                     | 1.25 V | LDO Mode         |     | 65  |     |                |

| 8 MHz system clock                                                                                    | 3.0 V  | BUCK Mode        |     | 33  |     | μA/MHz         |

| Executing CoreMark from RAM<br>All peripherals disabled                                               | 1.8 V  | BUCK Mode        |     | 50  |     |                |

| 64 KB RAM enabled                                                                                     | 1.25 V | LDO Mode         |     | 71  |     |                |

| 16 MHz system clock                                                                                   | 3.0 V  | BUCK Mode        |     | 26  |     | μA/MHz         |

| Executing CoreMark from RAM<br>All peripherals disabled                                               | 1.8 V  | BUCK Mode        |     | 39  |     |                |

| 64 KB RAM enabled                                                                                     | 1.25 V | LDO Mode         |     | 55  |     |                |

| 24 MHz system clock                                                                                   | 3.0 V  | BUCK Mode        |     | 20  |     | μA/MHz         |

| Executing CoreMark from RAM<br>All peripherals disabled                                               | 1.8 V  | BUCK Mode        |     | 31  |     |                |

| 64 KB RAM enabled                                                                                     | 1.25 V | LDO Mode         |     | 51  |     | ]              |

| 48 MHz system clock                                                                                   | 3.0 V  | BUCK Mode        |     | 21  |     | μA/MHz         |

| Executing CoreMark from RAM<br>All peripherals disabled                                               | 1.8 V  | BUCK Mode        |     | 34  |     | ]              |

| 64 KB RAM enabled                                                                                     | 1.25 V | LDO Mode         |     | 50  |     | 7              |

#### Table 6. RUN MODE CURRENT CONSUMPTION

Idle Mode Current Consumption

Table 7 shows key current consumption values for Idle Mode. Unless otherwise noted, the specifications mentioned in the table below are valid at  $25^{\circ}$ C, VBAT = VDDO (Buck

mode for VBAT > 1.4 V, LDO mode for VBAT  $\leq$  1.4 V), 48 MHz (RFCLK) active, Radio OFF and internal supplies trimmed to factory defaults.

#### Table 7. IDLE MODE CURRENT CONSUMPTION

| Operating Conditions | Wakeup<br>Source | VBAT   | DC Conversion | Min | Тур | Мах | Unit |

|----------------------|------------------|--------|---------------|-----|-----|-----|------|

| System clock stopped | GPIO             | 3.0 V  | BUCK Mode     |     | 128 |     | μΑ   |

| 64 KB RAM enabled    |                  | 1.8 V  | BUCK Mode     |     | 103 |     |      |

|                      |                  | 1.25 V | LDO Mode      |     | 156 |     |      |

#### Standby Mode Current Consumption

Table 8 shows key current consumption values for Standby Mode. Unless otherwise noted, the specifications mentioned in the table below are valid at  $25^{\circ}$ C, VBAT =

VDDO (Buck mode for VBAT > 1.4 V, LDO mode for VBAT  $\leq$  1.4 V), 48 MHz (RFCLK) inactive, Radio OFF and internal power supplies trimmed to factory defaults.

| Operating Conditions                                                         | Wakeup<br>Source | VBAT   | DC Conversion | Min | Тур  | Max | Unit |

|------------------------------------------------------------------------------|------------------|--------|---------------|-----|------|-----|------|

| Clocks stopped                                                               | GPIO             | 3.0 V  | BUCK Mode     | 1   | 17   |     | μΑ   |

| All peripherals disabled<br><b>8 KB RAM retained</b><br>32 kHz RC32 inactive |                  | 1.8 V  | BUCK Mode     |     | 20   |     |      |

| 32 kHz XTAL32K inactive                                                      |                  | 1.25 V | LDO Mode      |     | 26   |     |      |

| Clocks stopped                                                               | GPIO             | 3.0 V  | BUCK Mode     |     | 17.5 |     | μΑ   |

| All peripherals disabled<br>16 KB RAM retained                               |                  | 1.8 V  | BUCK Mode     | 1   | 21   |     |      |

| 32 kHz RC32 inactive<br>32 kHz XTAL32K inactive                              |                  | 1.25 V | LDO Mode      |     | 26   |     |      |

| Clocks stopped<br>All peripherals disabled<br>32 KB RAM retained             | GPIO             | 3.0 V  | BUCK Mode     | 1   | 17.6 |     | μΑ   |

|                                                                              |                  | 1.8 V  | BUCK Mode     | 1   | 21   |     | 1    |

| 32 kHz RC32 inactive<br>32 kHz XTAL32K inactive                              |                  | 1.25 V | LDO Mode      |     | 26   |     |      |

| Clocks stopped                                                               | GPIO             | 3.0 V  | BUCK Mode     | 1   | 18   |     | μΑ   |

| All peripherals disabled<br>64 KB RAM retained                               |                  | 1.8 V  | BUCK Mode     | 1   | 21   |     |      |

| 32 kHz RC32 inactive<br>32 kHz XTAL32K inactive                              |                  | 1.25 V | LDO Mode      | 1   | 26   |     |      |

| Clocks stopped                                                               | RTC<br>timer     | 3.0 V  | BUCK Mode     | 1   | 21   |     | μΑ   |

| All peripherals disabled<br>8 KB RAM retained                                | unier            | 1.8 V  | BUCK Mode     | 1   | 22   |     |      |

| 32 kHz RC32 active<br>32 kHz XTAL32K inactive                                |                  | 1.25 V | LDO Mode      | 1   | 29   |     |      |

| Clocks stopped                                                               | RTC<br>timer     | 3.0 V  | BUCK Mode     |     | 19   |     | μΑ   |

| All peripherals disabled<br>8 KB RAM retained                                | umer             | 1.8 V  | BUCK Mode     |     | 21   |     | 1    |

| 32 kHz RC32 inactive<br>32 kHz XTAL32K active                                |                  | 1.25 V | LDO Mode      | 1   | 28   |     |      |

#### Table 8. STANDBY MODE CURRENT CONSUMPTION

mode for VBAT > 1.4 V, LDO mode for VBAT  $\leq$  1.4 V),

48 MHz (RFCLK) inactive, Radio OFF and internal

supplies trimmed to factory defaults.

#### Sleep Mode Current Consumption

Table 9 shows key current consumption values for Sleep Mode. Unless otherwise noted, the specifications mentioned in the table below are valid at  $25^{\circ}$ C, VBAT = VDDO (Buck

Wakeup **Operating Conditions** Symbol Source VBAT **DC Conversion** Min Unit Тур Max Clocks stopped lds1 GPIO BUCK Mode 3.0 V 36 nA All peripherals disabled No RAM retained 1.8 V **BUCK Mode** 37 32 kHz RC32 inactive 32 kHz XTAL32K inactive 1.25 V LDO Mode 60 System clocks stopped lds2 RTC timer 3.0 V **BUCK Mode** 83 nΑ All peripherals disabled 1.8 V BUCK Mode No RAM retained 98 32 kHz RC32 active 1.25 V LDO Mode 147 32 kHz XTAL32K inactive System clocks stopped RTC timer 3.0 V lds3 **BUCK Mode** 57 nA All peripherals disabled No RAM retained 1.8 V **BUCK Mode** 66 32 kHz RC32 inactive 1.25 V LDO Mode 97 32 kHz XTAL32K active System clocks stopped lds4 RTC timer 3.0 V **BUCK Mode** 165 nA All peripherals disabled 8 KB RAM retained 1.8 V **BUCK Mode** 233 32 kHz RC32 inactive 1.25 V LDO Mode 32 kHz XTAL32K active 253 lds5 **RTC** timer System clocks stopped 3.0 V **BUCK Mode** 208 nA All peripherals disabled **BUCK Mode** 1.8 V 303 16 KB RAM retained 32 kHz RC32 inactive LDO Mode 1.25 V 473 32 kHz XTAL32K active System clocks stopped lds6 RTC timer 3.0 V BUCK Mode 303 nA All peripherals disabled 1.8 V BUCK Mode 32 KB RAM retained 448 32 kHz RC32 inactive 1.25 V LDO Mode 32 kHz XTAL32K active 701

#### Table 9. SLEEP MODE CURRENT CONSUMPTION

NOTES: • Buck mode measurements were captured with an additional 10 μF in parallel with VBAT and a 200 Ω resistor in series in order to obtain a more accurate measurement with the measurement device.

• Current values include increases due to workarounds imposed by errata in section 'RSL15 Errata for Chip Identification 2.02.00'.

#### ULP Data Acquisition Subsystem Performance

Table 10 shows key current consumption values for ULP Data Acquisition Subsystem in Smart Sense Mode. Unless otherwise noted, the specifications mentioned in the table below are valid at 25°C, VBAT = VDDO (Buck mode for VBAT > 1.4 V, LDO mode for VBAT  $\leq$  1.4 V), 48 MHz (RFCLK) inactive, Radio OFF and internal supplies trimmed to factory defaults.

| Operating Condition                                                                                                                                                                                                                                                                                                                                                            | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Continuous ADC operation in Smart Sense mode with wakeup on ADC threshold<br>Configuration/conditions: VBAT = 3 V, BUCK Mode,<br>Successive Approximation ADC enabled and selected,<br>XTAL32K, VREF = VBAT reference selected,<br>ADC Fs = 256 sps, accumulation 4 samples. Processor would wake to Run mode by ADC<br>threshold but this is not included in this measurement |     | 206 |     | nA   |

| Continuous ADC operation in Smart Sense mode, wakeup on FIFO full, transfer content to<br>RAM<br>Configuration/conditions: VBAT = 3 V, BUCK Mode, 16 KB RAM retained, XTAL32K, Succes-<br>sive Approximation ADC enabled, VREF = VBAT, ADC Fs = 1 ksps, accumulation 16 sam-<br>ples, FIFO Size 16. Processor wakes to Run mode every 256 ms to transfer samples to<br>RAM     |     | 2.1 |     | μΑ   |

| Continuous ADC operation in Smart Sense mode, wakeup on FIFO full, transfer content to<br>RAM<br>Configuration/conditions: VBAT = 3 V, BUCK Mode, 16 KB RAM retained. XTAL32K, Succes-<br>sive Approximation ADC enabled, VREF = VDDA, ADC Fs = 1 ksps,<br>Accumulation 16 samples, FIFO Size 16. Processor wakes to Run mode every 256 ms to<br>transfer samples to RAM       |     | 4.1 |     | μΑ   |

| Continuous Pulse Counter accumulation in Smart Sense mode, wakeup when FIFO full,<br>transfer content to RAM<br>Configuration/conditions: VBAT = 3 V, BUCK Mode, 16 KB RAM retained, XTAL32K, Pulse<br>Counter enabled, Pulse Count Interval 1000 ms, accumulation of 5 samples, result stored in<br>FIFO. Processor wakes to Run mode every 5 s to transfer sample to RAM     |     | 348 |     | nA   |

NOTE: Current values include increases due to workarounds imposed by errata in section 'RSL15 Errata for Chip Identification 2.02.00'.

#### Wakeup Timing Specifications

#### Table 11. WAKEUP TIMING SPECIFICATIONS

| Description                                                            | Symbol | Conditions                                                                                                                                                                                 | Min | Тур              | Max | Unit |

|------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|-----|------|

| Cold startup – VBAT applied to entering RUN mode                       |        | To start of startup code execution<br>(Energy Harvesting state)                                                                                                                            |     | 2.4              |     | ms   |

|                                                                        |        | To start of startup code execution<br>(Secure state) using secure bootloader<br>with two key certificates, one content<br>certificate, debug port locked and<br>application size of ~55 KB |     | 236              |     |      |

| GPIO wakeup from Sleep mode to RUN mode, RAM execution                 |        | To start of wakeup function execution<br>in RAM (startup code is not executed).<br>VDDM retained                                                                                           |     | 1.47<br>(Note 4) |     | ms   |

| GPIO wakeup from Sleep mode to RUN mode, flash execution               |        | To start of startup code execution                                                                                                                                                         |     | 1.55<br>(Note 4) |     | ms   |

| GPIO wakeup from Sleep mode to RUN mode, continuation from flash       |        | To start of execution from last program<br>counter address (startup code is not<br>executed). VDDM retained                                                                                |     | 1.49<br>(Note 4) |     | ms   |

| GPIO wakeup from Standby mode to RUN mode, continuation from flash     |        | To start of execution from last program<br>counter address (startup code is not<br>executed). VDDC retained                                                                                |     | 125              |     | μs   |

| GPIO wakeup from IDLE mode to RUN mode, continuation from RAM or flash |        | To start of execution from last program<br>counter address (startup code is not<br>executed). VDDC retained                                                                                |     | 90               |     | μs   |

4. Wakeup times may vary due to system capacitance and sleep period.

| Table 12. EEMBC BENCHMARK SCORES | (All RSL15 benchmark scores have been certified by EEM | 3C) |

|----------------------------------|--------------------------------------------------------|-----|

|----------------------------------|--------------------------------------------------------|-----|

| Description                          | Symbol | Conditions            | Min | Тур  | Max | Units    |

|--------------------------------------|--------|-----------------------|-----|------|-----|----------|

| EEMBC CoreMark                       |        |                       |     | 177  |     | CoreMark |

| EEMBC ULPMark <sup>™</sup> -CoreMark |        | Performance           |     | 60.5 |     |          |

|                                      |        | Energy, Fixed Voltage |     | 58.3 |     |          |

|                                      |        | Energy, Best Voltage  |     | 63.1 |     |          |

| EEMBC ULPMark™ –CoreProfile          |        | 1.8 V                 |     | 1220 |     |          |

|                                      |        | 3 V                   |     | 1070 |     |          |

#### **RF Specifications**

Table 13 shows key RF specifications. Unless otherwise noted, the specifications mentioned in the table below are

valid at 25°C, VBAT = VDDO (Buck mode for VBAT > 1.4 V, LDO mode for VBAT  $\leq$  1.4 V).

#### Table 13. RF SPECIFICATIONS

| Description                        | Symbol           | Conditions                                     | Min  | Тур  | Max  | Units |

|------------------------------------|------------------|------------------------------------------------|------|------|------|-------|

| GENERAL RADIO SPECIFICA            | TIONS            | •                                              |      | -    |      | -     |

| RF Input Impedance                 | Z <sub>in</sub>  |                                                |      | 50   |      | Ω     |

| Input reflection coefficient       | S <sub>11</sub>  |                                                |      |      | -8   | dB    |

| Data Rate                          | R <sub>FSK</sub> | FSK/MSK/GFSK (OQPSK as MSK)                    | 62.5 | 1000 | 3000 | kbps  |

|                                    |                  | 4-FSK                                          |      |      | 4000 | kbps  |

| SYNTHESIZER SPECIFICATI            | ONS              |                                                |      |      |      |       |

| Frequency Range                    | F <sub>RF</sub>  |                                                | 2360 |      | 2500 | MHz   |

| Rx Frequency Step                  |                  | Receive mode frequency synthesizer resolution  |      |      | 100  | Hz    |

| Tx Frequency Step                  |                  | Transmit mode frequency synthesizer resolution |      |      | 600  | Hz    |

| PLL Settling Time                  |                  | Receive Mode                                   |      | 15   | 25   | μs    |

| PLL Settling Time                  |                  | Transmit Mode                                  |      | 5    | 10   | μs    |

| RECEIVE MODE SPECIFICAT            | IONS             |                                                |      |      |      |       |

| BLE Sensitivity                    |                  | 1 Mbps, 0.1% BER                               |      | -96  |      | dBm   |

| LDO mode, VBAT = 1.8 V or<br>3.0 V |                  | 2 Mbps, 0.1% BER                               |      | -94  |      | dBm   |

|                                    |                  | 500 kbps, 0.1% BER, BLE Long Range             |      | -98  |      | dBm   |

| Buck mode, VBAT = 1.8 V            |                  | 125 kbps, 0.1% BER, BLE Long Range             |      | -102 |      | dBm   |

| BLE Sensitivity                    |                  | 1 Mbps, 0.1% BER                               |      | -96  |      | dBm   |

| Buck mode,<br>VBAT = 3.0 V (WLCSP) |                  | 2 Mbps, 0.1% BER                               |      | -94  |      | dBm   |

|                                    |                  | 500 kbps, 0.1% BER, BLE Long Range             |      | -98  |      | dBm   |

|                                    |                  | 125 kbps, 0.1% BER, BLE Long Range             |      | -102 |      | dBm   |

| BLE Sensitivity                    |                  | 1 Mbps, 0.1% BER                               |      | -94  |      | dBm   |

| Buck mode,<br>VBAT = 3.0 V (QFN)   |                  | 2 Mbps, 0.1% BER                               |      | -91  |      | dBm   |

|                                    |                  | 500 kbps, 0.1% BER, BLE Long Range             |      | -96  |      | dBm   |

|                                    |                  | 125 kbps, 0.1% BER, BLE Long Range             |      | -100 |      | dBm   |

| Rx sensitivity degradation VSWR1:4 |                  | Any phase relative to 50 $\Omega$              |      | 3.5  |      | dB    |

| RSSI effective range               |                  | Without AGC                                    |      | 60   |      | dB    |

| RSSI step size                     |                  |                                                |      | 2.4  |      | dB    |

| Rx AGC Range                       |                  |                                                |      | 48   |      | dB    |

#### Table 13. RF SPECIFICATIONS (continued)

| Description                                                   | Symbol | Conditions                                                           | Min  | Тур | Max                  | Units |

|---------------------------------------------------------------|--------|----------------------------------------------------------------------|------|-----|----------------------|-------|

| RECEIVE MODE SPECIFICAT                                       | IONS   |                                                                      | •    | •   | •                    |       |

| Rx AGC Step Size                                              |        | Programmable                                                         |      | 6   |                      | dB    |

| Max usable input signal level                                 |        | 0.1% BER                                                             |      | 0   |                      | dBm   |

| TRANSMIT MODE SPECIFICA                                       | TIONS  |                                                                      |      |     |                      |       |

| Transmit power range                                          |        | BLE, VDDPA is required for $\ge$ +3 dBm or in low voltage conditions | -17  |     | +6 <sup>note 5</sup> | dBm   |

| Transmit power step size                                      |        |                                                                      |      | 1   |                      | dBm   |

| Transmit power accuracy                                       |        | Tx power 0 dBm. Full band. Relative to the typical value.            | -1.5 |     | +1.5                 | dBm   |

|                                                               |        | Tx power 3 dBm. Full band. Relative to the typical value.            | -1.5 |     | +1.5                 | dBm   |

|                                                               |        | Tx power 6 dBm. Full band. Relative to the typical value.            | -1.5 |     | +1.5                 | dBm   |

| Power in 2 <sup>nd</sup> harmonic                             |        | 0 dBm output level                                                   |      | -35 |                      | dBm   |

| Power in 3rd harmonic                                         |        | 0 dBm output level                                                   |      | -40 |                      | dBm   |

| Power in 4 <sup>th</sup> harmonic                             |        | 0 dBm output level                                                   |      | -45 |                      | dBm   |

| Power in 2 <sup>nd</sup> harmonic with<br>EVB harmonic filter |        | 0 dBm output level                                                   |      | -55 |                      | dBm   |

| Power in 3 <sup>rd</sup> harmonic with<br>EVB harmonic filter |        | 0 dBm output level                                                   |      | -60 |                      | dBm   |

| Power in 4 <sup>th</sup> harmonic with<br>EVB harmonic filter |        | 0 dBm output level                                                   |      | -60 |                      | dBm   |

| Tx power degradation<br>VSWR 1:4                              |        | Any phase relative to 50 $\Omega$ , for 0 dBm output level           |      | 2.5 |                      | dB    |

5. At +6 dBm Tx power, an antenna gain of +2.2 dBi or less must be used to ensure out-of-band regulatory emissions compliance.

#### Flash Specifications

#### Table 14. FLASH SPECIFICATIONS

| Description                    | Symbol | Conditions          | Min | Тур | Max | Units   |

|--------------------------------|--------|---------------------|-----|-----|-----|---------|

| Flash sector endurance         |        | Code and Data Array | 100 |     |     | kcycles |

|                                |        | NVR Array           | 1   |     |     |         |

| Flash content retention period |        | T = 55°C            | 25  |     |     | years   |

| Sector erase time              |        |                     |     | 1   | 4   | ms      |

| Mass write time                |        |                     |     |     | 10  | ms      |

#### **Oscillator Specifications**

#### Table 15. 32 kHz CRYSTAL OSCILLATOR (XTAL32K)

| Parameter                 | Symbol  | Conditions                                                             | Min | Тур    | Max  | Unit |

|---------------------------|---------|------------------------------------------------------------------------|-----|--------|------|------|

| Crystal Frequency         | XTAL32K |                                                                        |     | 32.768 |      | kHz  |

| Startup time              |         | VBAT applied to stabilization                                          |     | 1      | 3    | s    |

| Internal load             |         | Internal capacity to match crystal unit load capacity. Steps of 0.4 pF | 0   |        | 25.2 | pF   |

| External load Capacitance |         | Maximum external capacity allowed (package, routing, etc.)             |     |        | 3.5  | pF   |

| Internal ESR              |         |                                                                        |     |        | 100  | kΩ   |

#### Table 15. 32 kHz CRYSTAL OSCILLATOR (XTAL32K) (continued)

| Parameter         | Symbol | Conditions                                        | Min | Тур | Max | Unit |

|-------------------|--------|---------------------------------------------------|-----|-----|-----|------|

| Operating current |        | Using optimal external component (low CL and ESR) |     | 25  |     | nA   |

| Duty cycle        |        |                                                   | 40  | 50  | 60  | %    |

#### Table 16. SLOW RC OSCILLATOR (RC32)

| Parameter                      | Symbol | Notes                                                                                                                                                  | Min | Тур    | Max | Unit |

|--------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|------|

| Factory trimmed<br>frequency   | RC32   |                                                                                                                                                        |     | 32.768 |     | kHz  |

| Calibrated frequency tolerance |        | Conditions:<br>• temperature constant within ± 0.5°C<br>• calibrating at least every 10 seconds<br>• averaging window > 7.8 ms<br>• defined as 3 sigma |     |        | 500 | ppm  |

| Startup time                   |        | After VBAT applied                                                                                                                                     |     |        | 2   | ms   |

| Current consumption            |        | Temperature comp enabled                                                                                                                               |     | 120    |     | nA   |

#### Table 17. 48 MHz CRYSTAL OSCILLATOR (RFCLK)

| Parameter                        | Symbol | Notes                                                                                                                                                                                                              | Min | Тур | Мах | Unit |

|----------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Crystal Frequency                | RFCLK  |                                                                                                                                                                                                                    |     | 48  |     | MHz  |

| Startup time                     |        | After VBAT Applied                                                                                                                                                                                                 |     |     | 1.5 | ms   |

| Recommended XTAL parameter ESR   |        | Equiv. Series res.                                                                                                                                                                                                 | 20  |     | 80  | Ω    |

| Recommended XTAL<br>parameter CL |        | Differential equivalent load capacitance. The effective differential capacitance (XTAL and parasitics) must be <1 pF, the remaining being capacitance to ground (parasitic completed by on-chip load capacitance). | 6   | 8   | 10  | pF   |

| Operating current                |        |                                                                                                                                                                                                                    |     | 100 |     | μΑ   |

| Duty cycle                       |        |                                                                                                                                                                                                                    | 40  |     | 60  | %    |

NOTE: RFCLK (48 MHz crystal) must be the clock source when writing to Flash.

#### Table 18. FAST RC OSCILLATOR (RCCLK)

| Parameter                                                 | Symbol | Notes                                       | Min  | Тур | Мах | Unit |