# **Smart Card Interface IC**

The NCN8024 is a single smart card interface IC. It is dedicated for 3.0 V/5.0 V smart card reader/writer applications.

The device is fully compatible with the ISO 7816-3 and EMV standards as well as with standards specifying conditional access in Set-Top-Box (STB) including NDS.

For details regarding device implementation refer to application note AND8452/D, available upon request (please contact your local ON Semiconductor sales office or representative).

#### **Features**

- Single IC Card Interface

- Fully Compatible with ISO 7816-3, EMV and Related Standards **Including NDS**

- Three Bidirectional Buffered I/O Level Shifters (C4, C7 and C8 Card

- 3.0 V or 5.0 V  $\pm$  5% Regulated Card Power Supply such as I<sub>CC</sub>  $\leq$ 75 mA at 3.3 V  $\leq$  V<sub>DDP</sub>  $\leq$  5.5 V

- Independent Power Supply Range on Controller Interface  $(2.7 \text{ V} < \text{V}_{DD} < 5.5 \text{ V})$

- Handles 3.0 V and 5.0 V Smart Cards

- Thermal and Short Circuit Protection on all Card Pins

- Support up to 18 MHz Clock with Internal Division Ratio 1/1, 1/2, 1/4 and 1/8 through CLKDIV1 and CLKDIV2 Pins

- ESD Protection on Card Pins up to 8 kV+ (Human Body Model)

- Activation/Deactivation Sequences (ISO7816)

- Fault Protection Mechanisms Enabling Automatic Device Deactivation in Case of Overload, Overheating, Card Take-off or Power Supply Drop-out

- Interrupt Signal INT for Card Presence and Faults

- External Undervoltage Lockout Threshold Adjustment on VDD (PORADJ Pin)

- Available in 2 Package Formats: SOIC-28 and TSSOP-28

- These are Pb-Free Devices

## **Typical Application**

- Set-Top Boxes Conditional Access & Pay-TV

- Conditional Access Modules (CAM)

- POS / ATM

- Access Control, Identification

## ON Semiconductor®

http://onsemi.com

#### **MARKING DIAGRAMS**

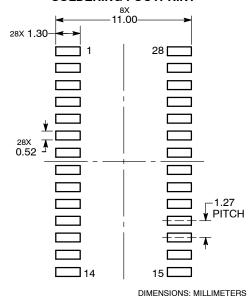

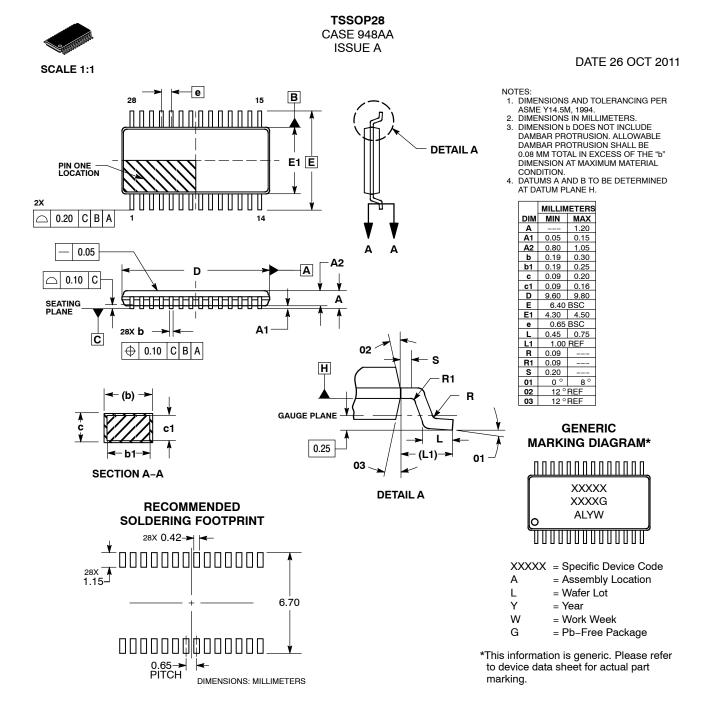

TSSOP-28 CASE 948AA

NCN8024 = Specific Device Code

= Assembly Location

= Wafer Lot WL, L YY, Y = Year WW, W = Work Week = Pb-Free Package

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 14 of this data sheet.

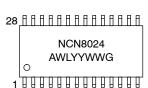

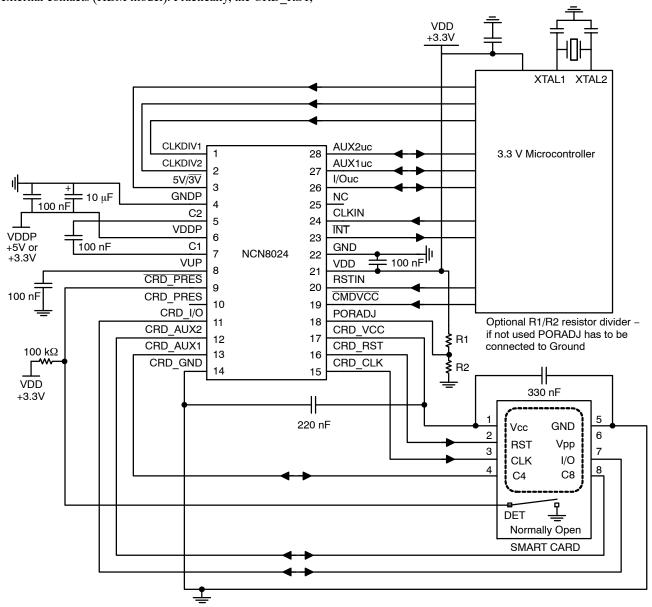

Figure 1. Typical Smart Card Interface Application

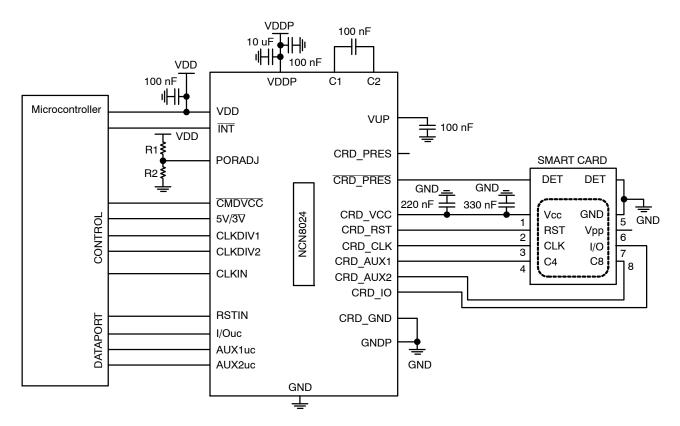

Figure 2. SOIC-28 and TSS0P-28 Pinout (Top View)

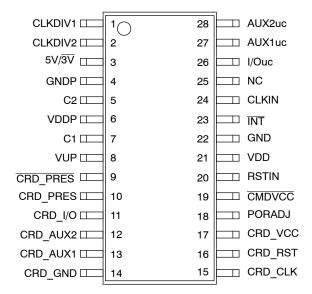

Figure 3. NCN8024 Block Diagram

## PIN FUNCTION AND DESCRIPTION

| Pin # | Name     | Туре  | Description                                                                                                                                                         |

|-------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | CLKDIV1  | Input | This pin coupled with CLKDIV2 is used to program the clock frequency division ratio (Table 1).                                                                      |

| 2     | CLKDIV2  | Input | This pin coupled with CLKDIV1 is used to program the clock frequency division ratio (Table 1).                                                                      |

| 3     | 5V/3V    | Input | Allows selecting card $V_{CC}$ power supply voltage. CRD_ $V_{CC}$ = 5 V when $5V/\overline{3V}$ = HIGH or 3 V when $5V/\overline{3V}$ = LOW                        |

| 4     | GNDP     | GND   | DC/DC Converter Power Supply Ground                                                                                                                                 |

| 5     | C2       | Power | DC/DC Converter Capacitor pin number 2 – A 100 nF capacitor is connected between this pin and pin C1. The capacitor has to feature an ESR lower than 100 m $\Omega$ |

| 6     | VDDP     | Power | DC/DC Converter Power Supply Voltage                                                                                                                                |

| 7     | C1       | Power | DC/DC Converter Capacitor pin number 1 – A 100 nF capacitor is connected between this pin and pin C2. The capacitor has to feature an ESR lower than 100 m $\Omega$ |

| 8     | VUP      | Power | Charge–pump output – a very low ESR 100 nF capacitor (ESR< 100 m $\Omega$ ) is connected between this pin and GNDP                                                  |

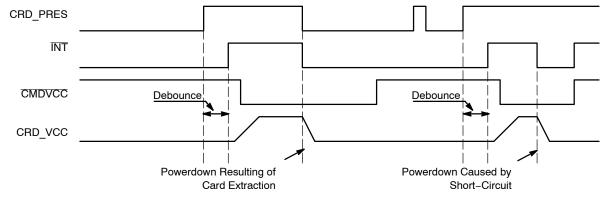

| 9     | CRD_PRES | Input | Card presence pin active (card present) when CRD_PRES = Low. A built-in debounce timer of about 8 ms is activated when a card is inserted.                          |

| 10    | CRD_PRES | Input | Card presence pin active (card present) when CRD_PRES = High. A built-in debounce timer of about 8 ms is activated when a card is inserted.                         |

## PIN FUNCTION AND DESCRIPTION

| Pin# | Name     | Type             | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|------|----------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | CRD_I/O  | Input/<br>Output | This pin handles the connection to the serial I/O (C7) of the card connector. A bi–directional level translator adapts the serial I/O signal between the card and the micro controller. An 11 k $\Omega$ (typical) pullup resistor to CRD_V <sub>CC</sub> provides a High impedance state for the smart card I/O link.                                                                                   |

| 12   | CRD_AUX2 | Input/<br>Output | This pin handles the connection to the chip card's serial auxiliary AUX2 I/O pin (C8). A bi–directional level translator adapts the serial I/O signal between the card and the micro controller. An 11 k $\Omega$ (typical) pullup resistor to CRD_V <sub>CC</sub> provides a High impedance state for the smart card C8 pin.                                                                            |

| 13   | CRD_AUX1 | Input/<br>Output | This pin handles the connection to the chip card's serial auxiliary AUX1 I/O pin (C4). A bi–directional level translator adapts the serial I/O signal between the card and the micro controller. An 11 k $\Omega$ (typical) pullup resistor to CRD_V <sub>CC</sub> provides a High impedance state for the smart card C4 pin.                                                                            |

| 14   | CRD_GND  | GND              | Card Ground                                                                                                                                                                                                                                                                                                                                                                                              |

| 15   | CRD_CLK  | Output           | This pin is connected to the CLOCK card connector's pin (Chip card's pin C3). The Clock signal comes from the CLKIN input through clock dividers and level shifter.                                                                                                                                                                                                                                      |

| 16   | CRD_RST  | Output           | This pin is connected to the chip card's RESET pin (C2) through the card connector. A level translator adapts the external Reset (RSTIN) signal to the smart card.                                                                                                                                                                                                                                       |

| 17   | CRD_VCC  | Power            | This pin is connected to the smart card power supply pin. An internal DC/DC converter is programmable using the pin $5V/\overline{3V}$ to supply either 5 V or 3 V output voltage. An external distributed ceramic capacitor (200 nF + 330 nF typical recommended) must be connected across CRD_V <sub>CC</sub> and CRD_GND. This set of capacitor (if distributed) must be low ESR (< 100 m $\Omega$ ). |

| 18   | PORADJ   | Input            | Power-on reset threshold adjustment input pin for changing the reset threshold with an external resistor power divider. Recommended to be connected to ground when unused.                                                                                                                                                                                                                               |

| 19   | CMDVCC   | Input            | Command VCC pin. Activation sequence Enable/Disable pin (active Low). The activation sequence is enabled by toggling CMDVCC High to Low and when a card is present.                                                                                                                                                                                                                                      |

| 20   | RSTIN    | Input            | This Reset input connected to the host and referred to $V_{DD}$ (microcontroller side), is connected to the smart card Reset pin through the internal level shifter which translates the level according to the $CRD\_V_{CC}$ programmed value.                                                                                                                                                          |

| 21   | VDD      | Power            | This pin is connected to the system controller power supply. It configures the level shifter input stage to accept the signals coming from the controller. A 0.1 $\mu$ F capacitor shall be used to bypass the power supply voltage. When $V_{DD}$ is below 2.35 V typical the card pins are disabled.                                                                                                   |

| 22   | GND      | GND              | Ground                                                                                                                                                                                                                                                                                                                                                                                                   |

| 23   | ĪNT      | Output           | The interrupt request is activated LOW on this pin. This is enabled when a card is present and the card presence is detected by CRD_PRES or $\overline{\text{CRD}}_{-}$ PRES pins. Similarly an interrupt is generated when CRD_VCC is overloaded. 20 k $\Omega$ typical integrated pullup resistor to VDD.                                                                                              |

| 24   | CLKIN    | Input            | Clock Input for External Clock                                                                                                                                                                                                                                                                                                                                                                           |

| 25   | NC       |                  | Unconnected                                                                                                                                                                                                                                                                                                                                                                                              |

| 26   | I/Ouc    | Input/<br>Output | This pin is connected to an external micro–controller. A bi–directional level translator adapts the serial I/O signal between the smart card and the external controller. A built–in constant 11 k $\Omega$ (typical) resistor provides a high impedance state.                                                                                                                                          |

| 27   | AUX1uc   | Input/<br>Output | This pin is connected to an external micro–controller. A bi–directional level translator adapts the serial C4 signal between the smart card and the external controller. A built–in constant 11 k $\Omega$ (typical) resistor provides a high impedance state.                                                                                                                                           |

| 28   | AUX2uc   | Input/<br>Output | This pin is connected to an external micro–controller. A bi–directional level translator adapts the serial C8 signal between the smart card and the external controller. A built–in constant 11 k $\Omega$ (typical) resistor provides a high impedance state.                                                                                                                                           |

#### **ATTRIBUTES**

| Characteristics                                                                                                                               | Values                         |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|

| ESD protection Human Body Model (HBM) (Note 1)                                                                                                |                                |  |  |  |

| Card Pins (Card Interface Pins 9 – 17) All Other Pins Machine Model (MM) Card Pins (Card Interface Pins 9 – 17) All Other Pins All Other Pins | 8 kV<br>2 kV<br>400 V<br>150 V |  |  |  |

| Moisture sensitivity (Note 2) SOIC-28 and TSSOP-28                                                                                            | Level 3                        |  |  |  |

| Flammability Rating Oxygen Index: 28 to 34                                                                                                    | UL 94 V-0 @ 0.125 in           |  |  |  |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch-up Test                                                                                       |                                |  |  |  |

- 1. Human Body Model (HBM), R = 1500  $\Omega$ , C = 100 pF.

- 2. For additional information, see Application Note AND8003/D.

## MAXIMUM RATINGS (Note 3)

| Rating                                            | Symbol              | Value                              | Unit |

|---------------------------------------------------|---------------------|------------------------------------|------|

| DC/DC Converter Power Supply Voltage              | $V_{\mathrm{DDP}}$  | $-0.3 \le V_{DDP} \le 5.5$         | V    |

| Power Supply from Microcontroller Side            | $V_{DD}$            | $-0.3 \le V_{DD} \le 5.5$          | V    |

| External Card Power Supply                        | CRD_V <sub>CC</sub> | $-0.3 \le CRD\_V_{CC} \le 5.5$     | V    |

| Charge Pump Output                                | V <sub>UP</sub>     | $-0.3 \le V_{UP} \le 5.5$          |      |

| Digital Input Pins                                | V <sub>in</sub>     | $-0.3 \le V_{in} \le V_{DD}$       | V    |

| Digital Output Pins (I/Ouc, AUX1uc, AUX2uc, ĪNT)  | V <sub>out</sub>    | $-0.3 \le V_{out} \le V_{DD}$      | V    |

| Smart Card Output Pins                            | V <sub>out</sub>    | $-0.3 \le V_{out} \le CRD\_V_{CC}$ | ٧    |

| Thermal Resistance Junction-to-Air SOIC-2 TSSOP-2 | 007                 | 75<br>76                           | °C/W |

| Operating Ambient Temperature Range               | T <sub>A</sub>      | -40 to +85                         | °C   |

| Operating Junction Temperature Range              | TJ                  | -40 to +125                        | °C   |

| Maximum Junction Temperature                      | T <sub>Jmax</sub>   | +125                               | °C   |

| Storage Temperature Range                         | T <sub>stg</sub>    | -65 to + 150                       | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

3. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at  $T_A = +25$ °C

## **POWER SUPPLY SECTION** ( $V_{DD}$ = 3.3 V; $V_{DDP}$ = 5 V; $T_{amb}$ = 25°C; $F_{CLKIN}$ = 10 MHz)

| Pin   | Symbol               | Rating                                                                                                                                                                                                                           | Min          | Тур          | Max          | Unit |

|-------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|------|

| 6     | V <sub>DDP</sub>     | DC/DC Converter Power Supply, CRD_V <sub>CC</sub> = 3 V and 5 V with DC Load Such as $ \begin{array}{c c}  I_{CC}  \leq 75 \text{ mA} \\  I_{CC}  \leq 20 \text{ mA} \end{array} $                                               | 3.3<br>3.0   | 5.0          | 5.5<br>5.5   | V    |

| 6     | V <sub>DDP</sub>     | NDS Conditions: DC/DC Converter Power Supply, CRD_V <sub>CC</sub> = 3 V and 5 V with 75 mA Load Transient from 100 Hz to 200 MHz and /CMDVCC Cycling (Note 4): $ I_{CC}  \le 75 \text{ mA}$                                      | 4.5          | 5.0          | 5.5          | V    |

|       |                      | $ I_{CC}  \le 73 \text{ mA}$                                                                                                                                                                                                     | 3.15         | 5.0          | 5.5<br>5.5   |      |

| 6     | I <sub>DDP</sub>     | Inactive Mode                                                                                                                                                                                                                    | -            | ı            | 0.3          | mA   |

| 6     | I <sub>DDP</sub>     | DC Operating Supply Current, F <sub>CLKIN</sub> = 10 MHz, Cout <sub>CRD_CLK</sub> = 33 pF, I I <sub>CRD_VCC</sub> = 0                                                                                                            | -            | I            | 5.0          | mA   |

| 6     | I <sub>DDP</sub>     | DC Operating Supply Current,  CRD_V <sub>CC</sub> = 5 V, I <sub>CRD_VCC</sub> = 75 mA  CRD_V <sub>CC</sub> = 3 V, I <sub>CRD_VCC</sub> = 75 mA                                                                                   | -            | I            | 200<br>200   | mA   |

| 21    | $V_{DD}$             | Operating Voltage                                                                                                                                                                                                                | 2.7          | -            | 5.5          | V    |

| 21    | $I_{VDD}$            | Inactive Mode 0 Standby Current                                                                                                                                                                                                  | -            | -            | 0.6          | mA   |

| 21    | I <sub>VDD</sub>     | Operating Current – F <sub>CLK_IN</sub> = 10 MHz,<br>Cout <sub>CRD_CLK</sub> = 33 pF, I <sub>ICRD_VCC</sub> = 0                                                                                                                  | -            | -            | 1            | mA   |

| 21    | UVLOV <sub>DD</sub>  | Undervoltage Lockout (UVLO), No External Resistor at Pin PORADJ (Connected to GND), Falling V <sub>DD</sub> Level                                                                                                                | 2.25         | 2.35         | 2.45         | V    |

| 21    | UVLOHys              | UVLO Hysteresis, No External Resistor at Pin PORADJ (Connected to GND)                                                                                                                                                           | 50           | 130          | 180          | mV   |

| PORAD | )J PIN               |                                                                                                                                                                                                                                  |              |              |              |      |

| 18    | V <sub>PORth+</sub>  | External Rising Threshold Voltage on $V_{DD}$ for Power On Reset – Pin PORADJ                                                                                                                                                    | 1.18         | 1.24         | 1.3          | V    |

| 18    | V <sub>PORth</sub>   | External Falling Threshold voltage on V <sub>DD</sub> for Power On Reset – Pin PORADJ                                                                                                                                            | 1.13         | 1.18         | 1.24         | V    |

| 18    | $V_{PORHys}$         | Hysteresis on V <sub>PORth</sub> (pin PORADJ)                                                                                                                                                                                    | 30           | 60           | 100          | mV   |

| 18    | t <sub>POR</sub>     | Width of Power-On Reset Pulse (Note 4) No External Resistor on PORADJ External Resistor on PORADJ                                                                                                                                | 4<br>4       | 8<br>8       | 12<br>12     | ms   |

| 18    | I <sub>IL</sub>      | Low Level Input Leakage Current, V <sub>IL</sub> <0.5 V (Pulldown Current Source)                                                                                                                                                |              | 5            |              | μΑ   |

| DC/DC | CONVERTER            |                                                                                                                                                                                                                                  | •            |              | •            |      |

|       | F <sub>CLK</sub>     | DC/DC Converter Clock Frequency when Card Active (Note 4)                                                                                                                                                                        | 2.2          |              | 3.2          | MHz  |

| 8     | V <sub>UP</sub>      | Output Voltage on pin V <sub>UP</sub> (average value)  CRD_V <sub>CC</sub> = 5V  CRD_V <sub>CC</sub> = 3V                                                                                                                        | 5.0<br>5.0   | 5.23<br>5.23 | 5.5<br>5.5   | V    |

| 17    | C <sub>CRD_VCC</sub> | Output Capacitance on card power supply CRD_V <sub>CC</sub> (Notes 4 and 5)                                                                                                                                                      | 300          | 220 +<br>320 | 1000         | nF   |

| 17    | CRD_V <sub>CC</sub>  | Output Card Supply Voltage @ $4.5 \text{ V} < \text{V}_{DDP} < 5.5 \text{ V}$ (including ripple)<br>$CRD\_V_{CC} = 3.0 \text{ V}$ @ $I_{load} \le 65 \text{ mA}$<br>$CRD\_V_{CC} = 5.0 \text{ V}$ @ $I_{load} \le 65 \text{ mA}$ | 2.85<br>4.75 | 3.00<br>5.00 | 3.15<br>5.25 | V    |

|       | 1                    | <u> </u>                                                                                                                                                                                                                         | 1            |              |              |      |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

<sup>4.</sup> Guaranteed by design and characterization

These values take into account the tolerance of the cms capacitor used. The allowed values are single or distributed capacitor combination not exceeding 1.0 μF with 220 nF + 330 nF typical and recommended. It is recommended to use X5R or X7R-type capacitors with very low ESR (< 100 mΩ) for optimal performances.</li>

**POWER SUPPLY SECTION** ( $V_{DD} = 3.3 \text{ V}$ ;  $V_{DDP} = 5 \text{ V}$ ;  $T_{amb} = 25^{\circ}\text{C}$ ;  $F_{CLKIN} = 10 \text{ MHz}$ )

| Pin   | Symbol                | Rating                                                                                                                                                                                                                                                                  | Min          | Тур          | Max          | Unit             |  |

|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|------------------|--|

| DC/DC | DC/DC CONVERTER       |                                                                                                                                                                                                                                                                         |              |              |              |                  |  |

| 17    | CRD_V <sub>CC</sub>   | Output Card Supply Voltage @ $3.6 \text{ V} \le \text{V}_{DDP} \le 5.5 \text{ V}$ with $ I_{CC}  \le 65 \text{ mA}$ load transient from 100 Hz to 200 MHz (including ripple) (Note 4) $ \frac{\text{CRD\_V}_{CC} = 3.0 \text{ V}}{\text{CRD\_V}_{CC} = 5.0 \text{ V}} $ | 2.76<br>4.65 | 3.00<br>5.00 | 3.20<br>5.25 | V<br>V           |  |

| 17    | CRD_V <sub>CC</sub>   | Output Card Supply Voltage @ $4.5 \text{ V} < \text{V}_{DDP} < 5.5 \text{ V}$ with Current—Load Pulses of 40 nAs/t < 400 ns and $ I_{CC}  < 200 \text{ mA}$ Peak Current (Including Ripple) (Note 4) $ CRD\_V_{CC} = 3.0 \text{ V} $ $ CRD\_V_{CC} = 5.0 \text{ V} $    | 2.76<br>4.65 | 3.00<br>5.00 | 3.20<br>5.25 | <b>&gt; &gt;</b> |  |

| 17    | I <sub>CRD_VCC</sub>  | Card Supply Current @ CRD_V <sub>CC</sub> = 3.0 V @ CRD_V <sub>CC</sub> = 5.0 V                                                                                                                                                                                         |              |              | 75<br>75     | mA               |  |

| 17    | ICRD_VCC_SC           | Short-Circuit Current - CRD_V <sub>CC</sub> Shorted to Ground                                                                                                                                                                                                           |              | 110          | 150          | mA               |  |

| 17    | $\Delta V_{CRD\_VCC}$ | Output Card Supply Voltage Ripple Peak-to-Peak - f <sub>ripple</sub> = 100 Hz to 200 MHz (Load Transient with 65 mA Peak Current) (Note 4)                                                                                                                              |              |              | 350          | mV               |  |

| 17    | CRD_V <sub>CCSR</sub> | Slew Rate on CRD_V <sub>CC</sub> Up or Down (Note 4)                                                                                                                                                                                                                    |              |              | 0.22         | V/μs             |  |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

4. Guaranteed by design and characterization

# DIGITAL INPUT/OUTPUT SECTION CLKIN, RSTIN, I/Oue, AUX1uc, AUX2uc, CLKDIV1, CLKDIV2, $\overline{\text{CMDVCC}}$ , 5V/3V ( $V_{DD} = 3.3 \text{ V}$ ; $V_{DDP} = 5 \text{ V}$ ; $T_{amb} = 25^{\circ}\text{C}$ ; $F_{CLKIN} = 10 \text{ MHz}$ )

| Pin                                   | Symbol             | Rating                                                                                                           | Min                   | Тур | Max                   | Unit |

|---------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| 24                                    | F <sub>CLKIN</sub> | Clock Frequency on Pin CLKIN (with Divider Ratio ≥ 2) (Note 6)                                                   | -                     | -   | 27                    | MHz  |

| 1, 2, 3, 19,<br>20, 24, 26,<br>27, 28 | V <sub>IL</sub>    | Input Voltage Level Low: CLKIN, RSTIN, I/Ouc, AUX1uc, AUX2uc, CLKDIV1, CLKDIV2, CMDVCC, 5V/3V                    | -0.3                  | -   | 0.3 x V <sub>DD</sub> | ٧    |

| 1, 2, 3, 19,<br>20, 24, 26,<br>27, 28 | V <sub>IH</sub>    | Input Voltage Level High: CLKIN, RSTIN, I/O, AUX1, AUX2, CLKDIV1, CLKDIV2, CMDVCC, 5V/3V                         | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.3 | V    |

| 1, 2, 3, 19,<br>20, 24                | I <sub>IL</sub>    | CLKDIV1, CLKDIV2, CMDVCC, RSTIN, CLKIN, 5V/3V Low Level Input Leakage Current, V <sub>IL</sub> = 0 V             | -                     | -   | 1.0                   | μΑ   |

| 1, 2, 3, 19,<br>20, 24                | I <sub>IH</sub>    | CLKDIV1, CLKDIV2, CMDVCC, RSTIN, CLKIN, 5V/3V Low Level Input Leakage Current, V <sub>IH</sub> = V <sub>DD</sub> | -                     | -   | 1.0                   | μΑ   |

| 26, 27, 28                            | I <sub>IL</sub>    | $I/Ouc$ , AUX1uc, AUX2uc Low Level Input Leakage Current, $V_{IL} = 0 \text{ V}$                                 | _                     | _   | 600                   | μΑ   |

| 26, 27, 28                            | I <sub>IH</sub>    | $I/Ouc$ , AUX1uc, AUX2uc High Level Input Leakage Current, $V_{IH} = V_{DD}$                                     | _                     | _   | 10                    | μΑ   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

6. Guaranteed by design and characterization

These values take into account the tolerance of the cms capacitor used. The allowed values are single or distributed capacitor combination not exceeding 1.0 μF with 220 nF + 330 nF typical and recommended. It is recommended to use X5R or X7R-type capacitors with very low ESR (< 100 mΩ) for optimal performances.</li>

DIGITAL INPUT/OUTPUT SECTION CLKIN, RSTIN, I/Ouc, AUX1uc, AUX2uc, CLKDIV1, CLKDIV2,  $\overline{\text{CMDVCC}}$ ,  $5V/\overline{3V}$  ( $V_{DD} = 3.3 \text{ V}$ ;  $V_{DDP} = 5 \text{ V}$ ;  $V_{CMD} = 25 \text{ C}$ ;  $V_{CMD} = 10 \text{ MHz}$ )

| Pin        | Symbol                                | Rating                                                                                                                                                                                    | Min                                             | Тур    | Max                                            | Unit   |

|------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------|------------------------------------------------|--------|

| 26, 27, 28 | V <sub>OH</sub>                       | I/Ouc, AUX1uc, AUX2uc data channels, @ Cs $\leq$ 30 pF High Level Output Voltage (CRD_I/O = CRD_AUX1 = CRD_AUX2 = CRD_V <sub>CC</sub> ) I <sub>OH</sub> = 0 I <sub>OH</sub> = $-40~\mu$ A | 0.9 x V <sub>DD</sub><br>0.75 x V <sub>DD</sub> | -<br>- | V <sub>DD</sub> + 0.1<br>V <sub>DD</sub> + 0.1 | V<br>V |

|            | V <sub>OL</sub><br>t <sub>Ri/Fi</sub> | Low Level Output Voltage (C_I/O= CRD_AUX1 = CRD_AUX2 = 0 V) $I_{OL} = +1 \text{ mA}$                                                                                                      | 0                                               | -      | 0.3                                            | V      |

|            |                                       | Input Rising/Falling Times (Note 6)                                                                                                                                                       | -                                               | -      | 1.2                                            | μs     |

|            | t <sub>Ro/Fo</sub>                    | Output Rising/Falling Times (Note 6)                                                                                                                                                      | -                                               | -      | 0.1                                            | μs     |

| 26, 27, 28 | F <sub>bidi</sub>                     | Maximum Frequency through Bidirectional I/O, AUX1 and AUX2 Channels (Note 6)                                                                                                              | -                                               | -      | 1                                              | MHz    |

| 26, 27, 28 | R <sub>pu</sub>                       | I/0uc, AUX1uc, AUX2uc Pullup Resistor                                                                                                                                                     | 8.0                                             | 11     | 16                                             | kΩ     |

| 23         | V <sub>OH</sub>                       | Output High Voltage<br>INT @ I <sub>OH</sub> = -15 μA (Source)                                                                                                                            | 0.75 x V <sub>DD</sub>                          | -      | -                                              | ٧      |

| 23         | V <sub>OL</sub>                       | Output Low Voltage    NT @ I <sub>OL</sub> = 2 mA (Sink)                                                                                                                                  | 0                                               | _      | 0.30                                           | ٧      |

| 23         | R <sub>INT</sub>                      | INT Pullup Resistor                                                                                                                                                                       | 14                                              | 20     | 26                                             | kΩ     |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

<sup>6.</sup> Guaranteed by design and characterization

##

| Pin           | Symbol                                                | Rating                                                                                                                                                            | Min                            | Тур    | Max                                                          | Unit                     |

|---------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------|--------------------------------------------------------------|--------------------------|

| 16            | V <sub>OH</sub><br>V <sub>OL</sub>                    | CRD_RST @ CRD_V <sub>CC</sub> = 3.0 V, 5.0 V<br>Output RESET V <sub>OH</sub> @ $I_{rst}$ = -200 $\mu$ A<br>Output RESET V <sub>OL</sub> @ $I_{rst}$ = 200 $\mu$ A | 0.9 x CRD_V <sub>CC</sub>      | -      | CRD_V <sub>CC</sub><br>0.20                                  | V<br>V                   |

|               | V <sub>OH</sub><br>V <sub>OL</sub>                    | Output RESET $V_{OH}$ @ $I_{rst}$ = -20 mA<br>Output RESET $V_{OL}$ @ $I_{rst}$ = 20 mA                                                                           | 0<br>CRD_V <sub>CC</sub> - 0.4 | -<br>- | 0.4<br>CRD_V <sub>CC</sub>                                   | V<br>V                   |

|               | t <sub>R</sub><br>t <sub>F</sub>                      | Output RESET Risetime @ C <sub>out</sub> = 100 pF (Note 7)<br>Output RESET Falltime @C <sub>out</sub> = 100 pF (Note 7)                                           | -<br>-                         | -<br>- | 100<br>100                                                   | ns<br>ns                 |

|               | t <sub>d</sub>                                        | RSTIN to CRD_RST Delay - Reset Enabled (Note 7)                                                                                                                   | -                              | -      | 2                                                            | μs                       |

| 15            |                                                       | CRD_CLK @ CRD_V <sub>CC</sub> = 3.0 V or 5.0 V                                                                                                                    |                                |        |                                                              |                          |

|               | F <sub>CRDCLK</sub>                                   | Output Frequency (Note 7)                                                                                                                                         | -                              | -      | 18                                                           | MHz                      |

|               | V <sub>OH</sub><br>V <sub>OL</sub>                    | Output CRD_CLK V <sub>OH</sub> @ I <sub>clk</sub> = -200 μA<br>Output CRD_CLK V <sub>OL</sub> @ I <sub>clk</sub> = 200 μA                                         | 0.9 x CRD_V <sub>CC</sub><br>0 | -<br>- | CRD_V <sub>CC</sub><br>+0.2                                  | V<br>V                   |

|               | V <sub>OH</sub><br>V <sub>OL</sub>                    | Output CRD_CLK V <sub>OH</sub> @ I <sub>clk</sub> = -70 mA<br>Output CRD_CLK V <sub>OL</sub> @ I <sub>clk</sub> = 70 mA                                           | 0<br>CRD_V <sub>CC</sub> -0.4  | -<br>- | 0.4<br>CRD_V <sub>CC</sub>                                   | V                        |

|               | F <sub>DC</sub>                                       | Output Duty Cycle (Note 7)                                                                                                                                        | 45                             | -      | 55                                                           | %                        |

|               | t <sub>rills</sub><br>t <sub>ulsa</sub>               | Rise & Fall time (Note 5) Output CRD_CLK Risetime @ C <sub>out</sub> = 30 pF Output CRD_CLK Falltime @ C <sub>out</sub> = 30 pF                                   | -<br>-                         | -<br>- | 16<br>16                                                     | ns<br>ns                 |

|               | SR                                                    | Slew Rate @ Cout = 33 pF (Note 7)                                                                                                                                 | 0.2                            | -      | -                                                            | V/ns                     |

| 11, 12,<br>13 |                                                       | CRD_AUX1, CRD_AUX2, CRD_IO @ CRD_V <sub>CC</sub> = 3.0 V, 5.0 V                                                                                                   |                                |        |                                                              |                          |

|               | V <sub>IH</sub><br>V <sub>IH</sub><br>V <sub>IL</sub> | Input Voltage High Level (5 V Mode)<br>Input Voltage High Level (3 V Mode)<br>Input Voltage Low Level                                                             | 2.5<br>1.6<br>0.30             | -<br>- | CRD_V <sub>CC</sub> +0.3<br>CRD_V <sub>CC</sub> +0.3<br>0.80 | V<br>V<br>V              |

|               | I <sub>IL</sub><br>I <sub>IH</sub>                    | Low Level Input Current $V_{IL} = 0 \text{ V}$<br>High Level Input Current $V_{IH} = CRD\_V_{CC}$                                                                 | -<br>-                         | -      | 600<br>10                                                    | μ <b>Α</b><br>μ <b>Α</b> |

|               | V <sub>OH</sub>                                       | Output V <sub>OH</sub><br>@ I <sub>OH</sub> = -40 μA                                                                                                              | 0.75 x CRD_V <sub>CC</sub>     | -      | CRD_V <sub>CC</sub> +0.1                                     | V                        |

|               | V <sub>OL</sub>                                       | Output V <sub>OL</sub><br>@ I <sub>OL</sub> = 1 mA, V <sub>IL</sub> = 0 V                                                                                         | 0                              | -      | 0.30                                                         | V                        |

|               | t <sub>Ri/Fi</sub>                                    | Input Rising/Falling Times                                                                                                                                        | -                              |        | 1.2                                                          | μs                       |

|               | t <sub>Ro/Fo</sub>                                    | Output Rising/Falling Times / C <sub>out</sub> = 80 pF                                                                                                            | -                              | _      | 0.1                                                          | μs                       |

| 11, 12,<br>13 | R <sub>PU</sub>                                       | CRD_AUX1, CRD_AUX2, CRD_IO Pullup Resistor                                                                                                                        | 8.0                            | 11     | 16                                                           | kΩ                       |

|               | t <sub>IO</sub>                                       | Propagation delay I <sub>Ouc</sub> -> CRD_IO and CRD_IO -> IOuc (Falling Edge) (Note 7)                                                                           | -                              | -      | 200                                                          | ns                       |

|               | t <sub>pu</sub>                                       | Active pull-up pulse width buffers I/O, AUX1 & AUX2 (Note 7)                                                                                                      | -                              | 200    | -                                                            | ns                       |

| 9, 10         | V <sub>IH</sub><br>V <sub>IL</sub>                    | CRD_PRES, CRD_PRES Card Presence Voltage High Level Card Presence Voltage Low Level                                                                               | 0.7 x V <sub>DD</sub><br>-0.3  |        | V <sub>DD</sub> + 0.3<br>0.3 x V <sub>DD</sub>               | V                        |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

<sup>7.</sup> Guaranteed by design and characterization

##

| Pin               | Symbol                | Rating                                                                                                                                                                                     | Min | Тур | Max               | Unit |

|-------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------------|------|

| 9, 10             | Piril                 | CRD_PRES, CRD_PRES High level input leakage current, V <sub>IH</sub> = V <sub>DD</sub> CRD_PRES CRD_PRES Low level input leakage current, V <sub>IL</sub> = 0 V CRD_PRES CRD_PRES CRD_PRES |     | 5   | 10<br>1<br>1<br>1 | μΑ   |

| 9, 10             | T <sub>debounce</sub> | Debounce Time CRD_PRES and CRD_PRES (Note 7)                                                                                                                                               | 5   | 8   | 11                | ms   |

| 11, 12,<br>13, 16 | I <sub>CRD_IO</sub>   | CRD_IO, CRD_AUX1, CRD_AUX2 Current Limitation                                                                                                                                              | -   | -   | 15                | mA   |

| 15                | I <sub>CRD_CLK</sub>  | CRD_CLK Current Limitation                                                                                                                                                                 | -   | -   | 70                | mA   |

| 16                | I <sub>CRD_RST</sub>  | CRD_RST Current Limitation                                                                                                                                                                 | -   | -   | 20                | mA   |

|                   | t <sub>act</sub>      | Activation Time (Note 7)                                                                                                                                                                   | 30  | _   | 100               | μs   |

|                   | t <sub>deact</sub>    | Deactivation Time (Note 7)                                                                                                                                                                 | 30  | _   | 250               | μs   |

|                   | Temp <sub>SD</sub>    | Shutdown Temperature                                                                                                                                                                       | -   | 160 | -                 | °C   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

7. Guaranteed by design and characterization

#### **POWER SUPPLY**

The NCN8024 smart card interface has two power supplies:  $V_{DD}$  and  $V_{DDP}$ .

$V_{DD}$  is usually common to the system controller and the interface. The applied  $V_{DD}$  ranges from 2.7 V up to 5.5 V. If  $V_{DD}$  goes below 2.35 V typical (UVLO<sub>VDD</sub>) a power–down sequence is automatically performed. In that case the interrupt  $(\overline{INT})$  pin is set Low.

A built-in charge-pump-based DC/DC converter followed by a Low Drop-Out (LDO) regulator is used to provide the 3 V or 5 V power supply voltage (CRD V<sub>CC</sub>) to the card. V<sub>DDP</sub> is the converter's input voltage. VUP is the charge-pump converter's output. It is connected to the LDO input. A reservoir capacitor of 100 nF is connected to VUP. CRD V<sub>CC</sub> is the LDO output. Even if the converter can operate with a single output reservoir capacitor as low as 100 nF at CRD V<sub>CC</sub>, it is recommended to use a capacitor of at least 320 nF in order to satisfy the datasheet specifications. The best recommended combination guaranteeing optimal performances consists in a distributed set of capacitors 220 nF + 330 nF (in particular recommended for optimally satisfying the NDS standard). To minimize dI/dt effects, the fly capacitor (100 nF) and the reservoir capacitors VUP and CRD\_VCC have to be connected as close as possible to the corresponding device's pin and feature very low ESR values (lower than 50 m $\Omega$ ). The fly capacitor is connected between C1 and C2. The decoupling capacitors on V<sub>DD</sub> and V<sub>DDP</sub> respectively 100 nF and  $10 \mu\text{F}$  have also to be connected close to the respective IC pins.

The CRD\_VCC pin can source up to 75 mA continuously over the  $V_{DDP}$  range (from 3.3 V to 5.5 V), the absolute

maximum current being internally limited below 150 mA (Typical at 110 mA). CRD\_VCC can stay in the range 4.6 V – 5.30 V during current transient up to 200 mA (peak current) over less than 400 ns of current pulse duration such as the charge transient is lower than 40 nAs.

There's no specific sequence for applying  $V_{DD}$  or  $V_{DDP}$ . They can be applied to the interface in any sequence. After powering the device  $\overline{INT}$  remains Low until a card is inserted.

#### SUPPLY VOLTAGE MONITORING

The supply voltage monitoring block includes the Power On Reset (POR) circuitry and the under voltage lockout (UVLO) detection ( $V_{DD}$  voltage dropout detection). PORADJ pin allows the user, according to the considered application, to adjust the  $V_{DD}$  UVLO threshold. If not used PORADJ pin is connected to Ground.

The input supply voltage is continuously monitored to prevent under voltage operation. At power up, the system initializes the internal logic during POR timing and no further signal can be provided or supported during this period. Such initialization takes place when the input voltage rises between 2 V to 2.6 V about typical.

The system is ready to operate when the input voltage has reached the minimum 2.7 V. Considering this, the NCN8024 will detect an Under–Voltage situation when the input supply voltage will drop below 2.35 V typical. When  $V_{DD}$  goes down below the UVLO falling threshold a deactivation sequence is performed.

The device is inactive during power–on and power–off of the  $V_{DD}$  supply (8 ms reset pulse).

PORADJ pin is used to modify the UVLO threshold according to the below relationship considering an external resistor divider R1 / R2 (see block diagram Figure 1):

$$UVLO = \frac{R1 + R2}{R2}V_{POR}$$

If PORADJ is connected to Ground the  $V_{DD}$  UVLO threshold ( $V_{DD}$  falling) is typically 2.35 V. In some cases it can be interesting to adjust this threshold at a higher value and by the way increase the  $V_{DD}$  supply dropout detection level which enables a deactivation sequence if the  $V_{DD}$  voltage is too low.

For example, there are microcontrollers for which the minimum supply voltage insuring a correct operating is higher than 2.55 V, increasing UVLO<sub>VDD</sub> (V<sub>DD</sub> falling) is consequently necessary. Considering for instance a resistor bridge with R1 = 56 k $\Omega$ , R2 = 42 k $\Omega$  and V<sub>POR</sub> = 1.18 V typical the V<sub>DD</sub> dropout detection level can be increased up to:

$$UVLO = \frac{59k + 42k}{42k} V_{POR-} = 2.75 V$$

The minimum dropout detection voltage should be higher than 2 V.

The maximum detection level may be up to VDD.

#### **CLOCK DIVIDER:**

The input clock can be divided by 1/1, 1/2, 1/4, or 1/8, depending upon the specific application, prior to be applied to the smart card driver. These division ratios are programmed using pins CLKDIV1 and CLKDIV2 (see Table 1). The input clock is provided externally to pin CLKIN.

**Table 1. Clock Frequency Programming**

| CLKDIV1 | CLKDIV2 | F <sub>CRD_CLK</sub> |

|---------|---------|----------------------|

| 0       | 0       | CLKIN/8              |

| 0       | 1       | CKLKIN / 4           |

| 1       | 0       | CLKIN                |

| 1       | 1       | CLKIN / 2            |

The clock input stage (CLKIN) can handle a 27 MHz maximum frequency signal (considering a division ratio  $\geq$  2). Of course, the ratio must be defined by the user to cope with Smart Card considered in a given application

In order to avoid any duty cycle out of the 45% / 55% range specification, the divider is synchronized by the last flip flop, thus yielding a constant 50% duty cycle, whatever be the divider ratio 1/2, 1/4 or 1/8. On the other hand, the output signal Duty Cycle cannot be guaranteed 50% if the division ratio is 1 and if the input Duty Cycle signal is not within the 46 - 56% range at the CLKIN input.

When the signal applied to CLKIN is coming from the external controller, the clock will be applied to the card under the control of the microcontroller or similar device after the activation sequence has been completed.

#### DATA I/O, AUX1 and AUX2 LEVEL SHIFTERS

The three bidirectional level shifters I/O, AUX1 and AUX2 adapt the voltage difference that might exist between the micro-controller and the smart card. These three channels are identical. The first side of the bidirectional level shifter dropping Low (falling edge) becomes the driver side until the level shifter enters again in the idle state pulling High CRD IO and I/Ouc.

Passive 11 k $\Omega$  pull-up resistors have been internally integrated on each terminal of the bidirectional channel. In addition with these pull-up resistors, an active pull-up circuit provides a fast charge of the stray capacitance.

The current to and from the card I/O lines is limited internally to 15 mA and the maximum frequency on these lines is 1 MHz.

#### STANDBY MODE

After a Power-on reset, the circuit enters the standby mode. A minimum number of circuits are active while waiting for the microcontroller to start a session:

- All card contacts are inactive

- Pins I/Ouc, AUX1uc and AUX2uc are in the high-impedance state (11 kΩ pull-up resistor to V<sub>DD</sub>)

- Card pins are inactive and pulled Low

- Supply Voltage monitoring is active

- The internal DC/DC converter oscillator is running.

#### POWER-UP

In the standby mode the microcontroller can check the presence of a card using the signals  $\overline{INT}$  and  $\overline{CMDVCC}$  as shown in Table 2:

**Table 2. Card Presence State**

| ĪNT  | CMDVCC | State            |

|------|--------|------------------|

| HIGH | HIGH   | Card present     |

| LOW  | HIGH   | Card not present |

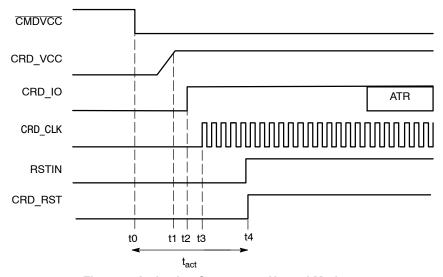

If a card is detected present ( $\overline{CRD\_PRES}$  or  $CRD\_PRES$  active) the controller can start a card session by pulling  $\overline{CMDVCC}$  Low. Card activation is run (t0, Figure 5). This Power–Up Sequence makes sure all the card related signals are LOW during the  $CRD\_V_{CC}$  positive going slope. These lines are validated when  $CRD\_V_{CC}$  is stable and above the minimum voltage specified. When the  $CRD\_V_{CC}$  voltage reaches the programmed value (3.0 V or 5.0 V), the circuit activates the card signals according to the following sequence (Figure 5):

- CRD\_V<sub>CC</sub> is powered-up at its nominal value (t1)

- I/O, AUX1 and AUX2 lines are activated (t2)

- Then Clock channel is activated and the clock signal is applied to the card (t3)

- Finally the Reset level shifter is enabled (t4)

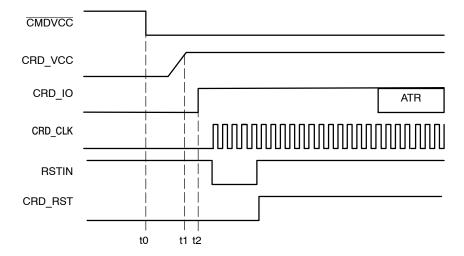

The clock can also be applied to the card using a RSTIN mode allowing controlling the clock starting by setting RSTIN Low (Figure 4). Before running the activation sequence, that is before setting Low CMDVCC RSTIN is set High. In these initial conditions CRD\_CLK starts when RSTIN is pulled Low. This allows a precise count of clock pulses before toggling CRD\_RST High for ATR (Answer To Reset) request.

The internal activation sequence activates the different channels according to a specific hardware built—it sequencing internally defined but at the end the actual activation sequencing is the responsibility of the application software and can be redefined by the micro—controller to comply with the different standards and the different ways the standards manage this activation (for example light differences exist between the EMV and the ISO7816 standards).

Figure 4. Activation Sequence - RSTIN mode (RSTIN Starting High)

Figure 5. Activation Sequence - Normal Mode

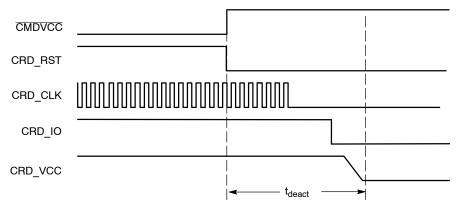

#### **POWER-DOWN**

When the communication session is completed the NCN8024 runs a deactivation sequence by setting High CMDVCC. The below power down sequence is executed:

• CRD\_RST is forced to Low

- CRD CLK is set Low 12 µs after CRD RST.

- CRD IO, CRD AUX1 and CRD AUX2 are pulled Low

- Finally CRD\_V<sub>CC</sub> supply can be shut-off.

Figure 6. Deactivation Sequence

#### **FAULT DETECTION**

In order to protect both the interface and the external smart card, the NCN8024 provides security features to prevent failures or damages as depicted here after.

- Card extraction detection

- V<sub>DD</sub> under voltage detection

- Short-circuit or overload on CRD\_V<sub>CC</sub>

- Card pin current limitation: in the case of a short circuit to ground. No feedback is provided to the external MPU.

- DC/DC operation: the internal circuit continuously senses the CRD\_V<sub>CC</sub> voltage (in the case of either over or under voltage situation).

- DC/DC operation: under-voltage detection on V<sub>DDP</sub> or overload on VUP

- Overheating

Figure 7. Fault Detection and Interrupt Management

## **Interrupt Pin Management:**

A card session is opened by toggling  $\overline{\text{CMDVCC}}$  High to Low.

Before a card session,  $\overline{CMDVCC}$  is supposed to be in a High position.  $\overline{INT}$  is Low if no card is present in the card connector (Normally open or normally closed type).  $\overline{INT}$  is High if a card is present. If a card is inserted ( $\overline{INT}$  = High) and if  $V_{DD}$  drops below the UVLO threshold then  $\overline{INT}$  pin drops Low immediately. It turns back High when  $V_{DD}$  increases again over the UVLO limit (including hysteresis), a card being still present.

During a card session,  $\overline{CMDVCC}$  is Low and  $\overline{INT}$  pin goes Low when a fault is detected. In that case a deactivation is immediately and automatically performed (see Figure 6). When the microcontroller resets  $\overline{CMDVCC}$  to High it can sense the  $\overline{INT}$  level again after having got completed the deactivation.

As illustrated by Figure 7 the device has a debounce timer of 8 ms typical duration. When a card is inserted, output  $\overline{\text{INT}}$  goes High only at the end of the debounce time. When the card is removed a deactivation sequence is automatically and immediately performed and  $\overline{\text{INT}}$  goes Low.

#### **ESD PROTECTION**

The NCN8024 includes devices to protect the pins against the ESD spikes voltages. To cope with the different ESD voltages developed across these pins, the built in structures have been designed to handle either 2 kV, when related to the micro controller side, or 8 kV when connected with the external contacts (HBM model). Practically, the CRD RST,

CRD\_CLK, CRD\_IO, CRD\_AUX1, CRD\_AUX2, CRD\_PRES and CRD\_PRES pins can sustain 8 kV. The CRD\_VCC pin has the same ESD protection and can source up to 75 mA continuously, the absolute maximum current being internally limited with a max at 150 mA. The CRD VCC current limit depends on VDDP and CRD VCC.

Figure 8. Application Schematic

## **ORDERING INFORMATION**

| Device         | Package               | Shipping <sup>†</sup> |

|----------------|-----------------------|-----------------------|

| NCN8024DWR2G   | SOIC-28<br>(Pb-Free)  | 1000 / Tape & Reel    |

| NCN8024DTBR2G* | TSSOP-28<br>(Pb-Free) | 2500 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>\*</sup>Consult Sales Office

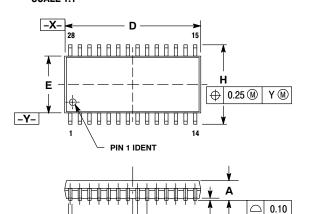

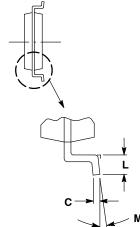

SOIC-28 WB CASE 751F **ISSUE J**

**DATE 23 SEP 2015**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSION

MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

DIMENSION B DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBER

PRSOTRUSION SHALL NOT BE 0.13 TOTATL IN

EXCESS OF B DIMENSION AT MAXIMUM

MATERIAL CONDITION MATERIAL CONDITION.

|     | MILLIMETERS |       |  |

|-----|-------------|-------|--|

| DIM | MIN         | MAX   |  |

| Α   | 2.35        | 2.65  |  |

| A1  | 0.13        | 0.29  |  |

| В   | 0.35        | 0.49  |  |

| С   | 0.23        | 0.32  |  |

| D   | 17.80       | 18.05 |  |

| E   | 7.40        | 7.60  |  |

| G   | 1.27 BSC    |       |  |

| Н   | 10.05       | 10.55 |  |

| L   | 0.41        | 0.90  |  |

| M   | 0 °         | 8 °   |  |

## **SOLDERING FOOTPRINT**

$| \bigoplus |$  0.025 M | T | X S | YS

-T-

SEATING PLANE

## **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location

WL = Wafer Lot Υ = Year WW = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: | 98ASB42345B       | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-28 WIDE BODY |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

| DESCRIPTION:     | 28 LEAD TSSOP. 9.7X4.4X1.0 MM. 0.65 PITCH |                                                                                                                                                                                   | PAGE 1 OF 1 |

|------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DOCUMENT NUMBER: | 98AON13023D                               | Electronic versions are uncontrolled except when accessed directly from the Document Repository.  Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.