# **Dual-Channel/Multi-Phase Controller for DrMOS**

## NCP81232

The NCP81232, a dual-channel/multi-phase synchronous buck controller, provides power management solutions for various applications supported by DrMOS. It has 8 programmable power-stage configurations, differential voltage and current sense, flexible power sequence programming, and comprehensive protections.

#### **Features**

- Vin = 4.5~20 V with Input Feedforward

- Integrated 5.35 V LDO

- Vout =  $0.6 \text{ V} \sim 5.3 \text{ V}$

- Fsw =  $200k \sim 1.2 \text{ MHz}$

- PWM Output Compatible to 3.3 V and 5 V DrMOS

- Flexible 8 Combinations of Power Stage Configurations (1~2 Output Rails, 1~4 Phases)

- DDR Power Mode Option

- Interleaved Operation

- Differential Output Voltage Sense

- Differential Current Sense Compatible for both Inductor DCR Sense and DrMOS Iout

- 2 Enables with Programmable Input UVLO

- Programmable DrMOS Power Ready Detection (DRVON)

- 2 Power Good Indicators

- Comprehensive Fault Indicator

- Externally Programmable Soft Start and Delay Time

- Programmable Hiccup Over Current Protection

- Hiccup Under Voltage Protection

- Recoverable Over Voltage Protection

- Hiccup Over Temperature Protection

- Thermal Shutdown Protection

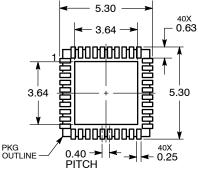

- QFN-40, 5x5 mm, 0.4 mm Pitch Package

- This is a Pb-Free Device

## **Typical Applications**

- Telecom Applications

- Server and Storage System

- Multiple Rail Systems

- DDR Applications

## ON Semiconductor®

www.onsemi.com

## QFN40 CASE 485CR

## MARKING DIAGRAM

A = Assembly Location

WL = Wafer Lot YY = Year WW = Work Week ■ Pb-Free Package

(Note: Microdot may be in either location)

## **ORDERING INFORMATION**

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NCP81232MNTXG | QFN40<br>(Pb-Free) | 5000 /<br>Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

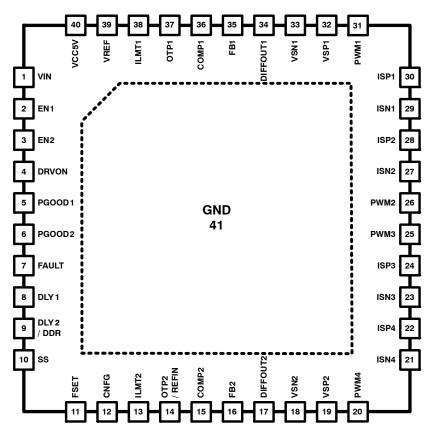

Figure 1. Pin Configuration

## **PIN DESCRIPTION**

| Pin | Name         | Туре         | Description                                                                                                                                                                                                                                                   |

|-----|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VIN          | Power Input  | Power Supply Input. Power supply input pin of the device, which is connected to the integrated 5V LDO. 4.7 $\mu\text{F}$ or more ceramic capacitors must bypass this input to power ground. The capacitors should be placed as close as possible to this pin. |

| 2   | EN1          | Analog Input | Enable 1. Logic high enables channel 1 and logic low disables channel 1. Input supply UVLO can be programmed at this pin for channel 1.                                                                                                                       |

| 3   | EN2          | Analog Input | Enable 2. Logic high enables channel 2 and logic low disables channel 2. Input supply UVLO can be programmed at this pin for channel 2.                                                                                                                       |

| 4   | DRVON        | Logic Input  | Driver On. Logic high input means drivers' power is ready.                                                                                                                                                                                                    |

| 5   | PGOOD1       | Logic Output | Power GOOD 1. Open-drain output. Provides a logic high valid power good output signal, indicating the regulator's output is in regulation window of channel 1.                                                                                                |

| 6   | PGOOD2       | Logic Output | Power GOOD 2. Open-drain output. Provides a logic high valid power good output signal, indicating the regulator's output is in regulation window of channel 2.                                                                                                |

| 7   | FAULT        | Logic Output | Fault. Digital output to indicate fault mode.                                                                                                                                                                                                                 |

| 8   | DLY1         | Analog Input | Delay 1. A resistor from this pin to GND programs delay time of soft start for channel 1.                                                                                                                                                                     |

| 9   | DLY2<br>/DDR | Analog Input | Delay 2 / DDR. A resistor from this pin to GND programs delay time of soft start for channel 2. Short to GND to have DDR operation mode.                                                                                                                      |

| 10  | SS           | Analog Input | Soft Start Time. A resistor from this pin to ground programs soft start time for both channels.                                                                                                                                                               |

| 11  | FSET         | Analog Input | Frequency Selection. A resistor from this pin to ground programs switching frequency.                                                                                                                                                                         |

| 12  | CNFG         | Analog Input | Configuration. A resistor from this pin to ground programs configuration of power stages.                                                                                                                                                                     |

| 13  | ILIMT2       | Analog Input | Limit of Current 2. Voltage at this pin sets over-current threshold for channel 2.                                                                                                                                                                            |

## **PIN DESCRIPTION**

| Pin | Name           | Туре          | Description                                                                                                                                                                                                                                |

|-----|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | OTP2<br>/REFIN | Analog Input  | Over Temperature Protection 2 / Reference Input. Voltage at this pin sets over–temperature threshold for channel 2. Reference input pin in DDR mode.                                                                                       |

| 15  | COMP2          | Analog Output | Compensation 2. Output pin of error amplifier of channel 2.                                                                                                                                                                                |

| 16  | FB2            | Analog Input  | Feedback 2. Inverting input of internal error amplifier for channel 2.                                                                                                                                                                     |

| 17  | DIFFOUT2       | Analog Output | Differential Amplifier Output 2. Output pin of differential voltage sense amplifier of channel 2.                                                                                                                                          |

| 18  | VSN2           | Analog Input  | Voltage Sense Negative Input 2. Inverting input of differential voltage sense amplifier of channel 2.                                                                                                                                      |

| 19  | VSP2           | Analog Input  | Voltage Sense Positive Input 2. Non-inverting input of differential voltage sense amplifier of channel 2.                                                                                                                                  |

| 20  | PWM4           | Analog Output | PWM 4. PWM output of phase 4.                                                                                                                                                                                                              |

| 21  | ISN4           | Analog Input  | Current Sense Negative Input 4. Inverting input of differential current sense amplifier of phase 4.                                                                                                                                        |

| 22  | ISP4           | Analog Input  | Current Sense Positive Input 4. Non-inverting input of differential current sense amplifier of phase 4.                                                                                                                                    |

| 23  | ISN3           | Analog Input  | Current Sense Negative Input 3. Inverting input of differential current sense amplifier of phase 3.                                                                                                                                        |

| 24  | ISP3           | Analog Input  | Current Sense Positive Input 3. Non-inverting input of differential current sense amplifier of phase 3.                                                                                                                                    |

| 25  | PWM3           | Analog Output | PWM 3. PWM output of phase 3.                                                                                                                                                                                                              |

| 26  | PWM2           | Analog Output | PWM 2. PWM output of phase 2.                                                                                                                                                                                                              |

| 27  | ISN2           | Analog Input  | Current Sense Negative Input 2. Inverting input of differential current sense amplifier of phase 2.                                                                                                                                        |

| 28  | ISP2           | Analog Input  | Current Sense Positive Input 2. Non-inverting input of differential current sense amplifier of phase 2.                                                                                                                                    |

| 29  | ISN1           | Analog Input  | Current Sense Negative Input 1. Inverting input of differential current sense amplifier of phase 1.                                                                                                                                        |

| 30  | ISP1           | Analog Input  | Current Sense Positive Input 1. Non-inverting input of differential current sense amplifier of phase 1.                                                                                                                                    |

| 31  | PWM1           | Analog Output | PWM 1. PWM output of phase 1.                                                                                                                                                                                                              |

| 32  | VSP1           | Analog Input  | Voltage Sense Positive Input 1. Non-inverting input of differential voltage sense amplifier of channel 1.                                                                                                                                  |

| 33  | VSN1           | Analog Input  | Voltage Sense Negative Input 1. Inverting input of differential voltage sense amplifier of channel 1.                                                                                                                                      |

| 34  | DIFFOUT1       | Analog Output | Differential Amplifier Output 1. Output pin of differential voltage sense amplifier of channel 1.                                                                                                                                          |

| 35  | FB1            | Analog Input  | Feedback 1. Inverting input of internal error amplifier for channel 1.                                                                                                                                                                     |

| 36  | COMP1          | Analog Output | Compensation 1. Output pin of error amplifier of channel 1.                                                                                                                                                                                |

| 37  | OTP1           | Analog Input  | Over Temperature Protection 1. Voltage at this pin sets over-temperature threshold for channel 1.                                                                                                                                          |

| 38  | ILIMT1         | Analog Input  | Limit of Current 1. Voltage at this pin sets over-current threshold for channel 1.                                                                                                                                                         |

| 39  | VREF           | Analog Output | Output of Reference. Output of 0.6 V reference. A 10nF ceramic capacitor bypasses this input to GND. This capacitor should be placed as close as possible to this pin.                                                                     |

| 40  | VCC5V          | Analog Power  | Voltage Supply of Controller. Output of integrated 5.35V LDO and power supply input pin of control circuits. A 4.7 $\mu$ F ceramic capacitor bypasses this input to GND. This capacitor should be placed as close as possible to this pin. |

| 41  | THERM<br>/GND  | Analog Ground | Thermal Pad and Analog Ground. Ground of internal control circuits. Must be connected to the system ground.                                                                                                                                |

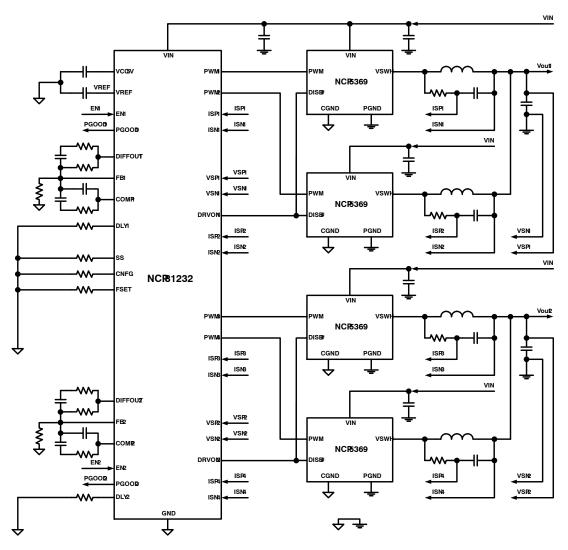

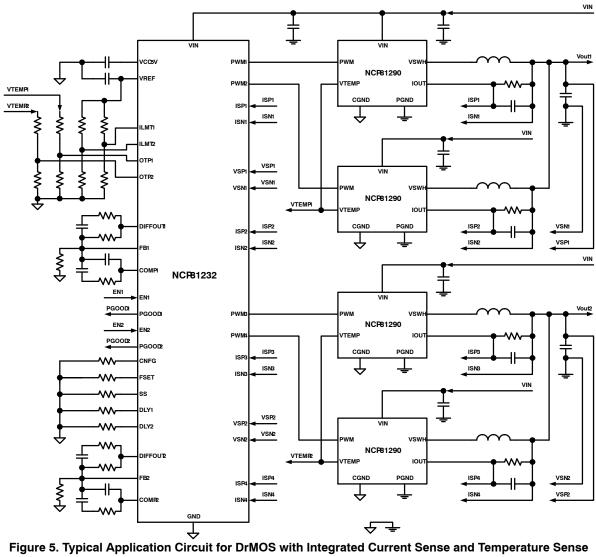

Figure 2. Typical Application Circuit for Dual Channel Applications (2 Phase + 2 Phase)

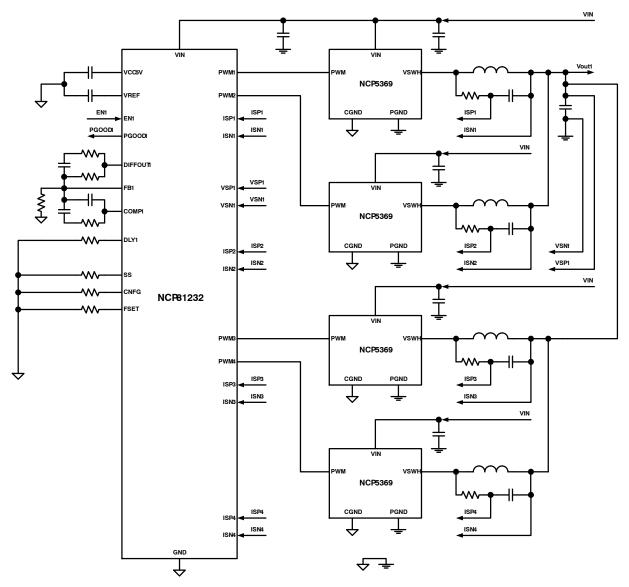

Figure 3. Typical Application Circuit for Single Channel Applications (4 Phase)

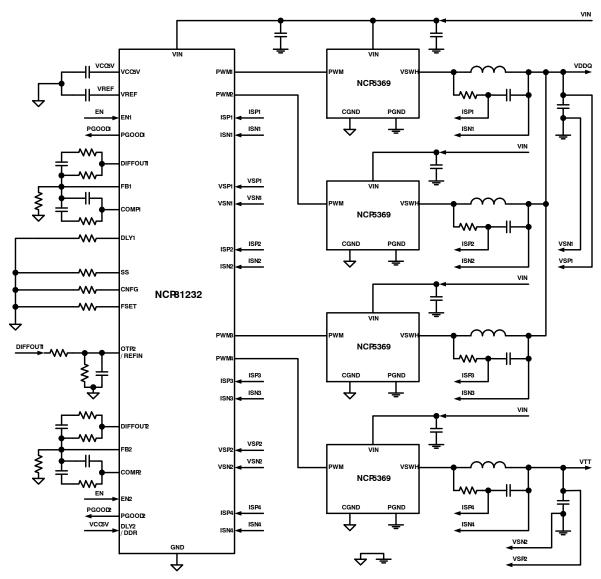

Figure 4. Typical Application Circuit for DDR Applications (3 Phase + 1 Phase)

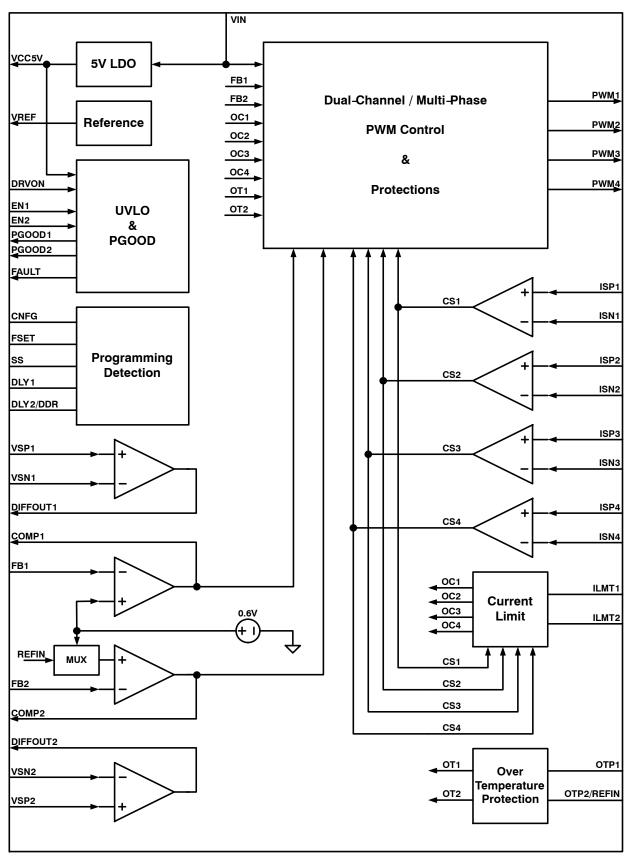

Figure 6. Functional Block Diagram

#### **MAXIMUM RATINGS**

|                                                                       |                    | \           | Value       |      |  |

|-----------------------------------------------------------------------|--------------------|-------------|-------------|------|--|

| Rating                                                                | Symbol             | Min         | Max         | Unit |  |

| Power Supply Voltage to PGND                                          | $V_{VIN}$          |             | 30          | V    |  |

| Supply Voltage VCC5V to GND                                           | V <sub>VCC5V</sub> | -0.3        | 6.5         | V    |  |

| VSNx to GND                                                           | $V_{VSN}$          | -0.2        | 0.2         | V    |  |

| Other Pins to GND                                                     |                    | -0.3        | VCC5V + 0.3 | V    |  |

| Human Body Model (HBM) ESD Rating (Note 1)                            | ESD HBM            |             | 4000        | V    |  |

| Machine Model (MM) ESD Rating (Note 1)                                | ESD MM             |             | 400         | V    |  |

| Charge Device Mode (CDM) ESD Rating (Note 1)                          | ESD CDM            |             | 2000        | V    |  |

| Latch up Current: (Note 2) All pins, except digital pins Digital pins | I <sub>LU</sub>    | -100<br>-10 | 100<br>10   | mA   |  |

| Operating Junction Temperature Range (Note 3)                         | T <sub>J</sub>     | -40         | 125         | °C   |  |

| Operating Ambient Temperature Range                                   | T <sub>A</sub>     | -40         | 100         | °C   |  |

| Storage Temperature Range                                             | T <sub>STG</sub>   | -55         | 150         | °C   |  |

| Thermal Resistance Junction to Top Case (Note 4)                      | $R_{\PsiJC}$       | 5.0         |             | °C/W |  |

| Thermal Resistance Junction to Board (Note 4)                         | $R_{\PsiJB}$       | 3.5         |             | °C/W |  |

| Thermal Resistance Junction to Ambient (Note 4)                       | $R_{	hetaJA}$      | 38          |             | °C/W |  |

| Power Dissipation (Note 5)                                            | $P_{D}$            |             | 2.63        |      |  |

| Moisture Sensitivity Level (Note 6)                                   | MSL                |             | 1           | -    |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- This device is ESD sensitive. Handling precautions are needed to avoid damage or performance degradation.

Latch up Current per JEDEC standard: JESD78 class II.

The thermal shutdown set to 150°C (typical) avoids potential irreversible damage on the device due to power dissipation.

JEDEC standard JESD 51-7 (1S2P Direct-Attach Method) with 0 LFM. It is for checking junction temperature using external measurement.

- The maximum power dissipation (PD) is dependent on input voltage, maximum output current and external components selected. T<sub>A</sub> = 25°C, T<sub>J</sub> max = 125°C, PD = (T<sub>J</sub> max-T amb)/Theta JA

Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

**ELECTRICAL CHARACTERISTICS** ( $V_{IN}$  = 12 V, typical values are referenced to  $T_A$  = 25°C, Min and Max values are referenced to  $T_A$  from -40°C to 125°C. unless other noted.)

| Characteristics                         | Test Cond                                                                        | Symbol                        | Min                  | Тур          | Max        | Unit                 |      |

|-----------------------------------------|----------------------------------------------------------------------------------|-------------------------------|----------------------|--------------|------------|----------------------|------|

| SUPPLY VOLTAGE                          |                                                                                  |                               |                      |              |            |                      |      |

| VIN Supply Voltage Range                | (Note                                                                            | 7)                            | V <sub>IN</sub>      | 4.5          | 12         | 20                   | V    |

| VCC5V Under-Voltage (UVLO)<br>Threshold | VCC5V f                                                                          | VCC5V falling                 |                      | 3.7          |            |                      | V    |

| VCC5V OK Threshold                      | VCC5V                                                                            | rising                        | V <sub>CCOK</sub>    |              |            | 4.3                  | V    |

| VCC5V UVLO Hysteresis                   |                                                                                  |                               | V <sub>CCHYS</sub>   |              | 260        |                      | mV   |

| VCC5V Regulator                         |                                                                                  |                               | •                    |              | -          | •                    |      |

| Output Voltage                          | 6 V < VIN < 20 V, I<br>(External), EN1                                           |                               | V <sub>CC</sub>      | 5.2          | 5.35       | 5.5                  | V    |

| Load Regulation                         | I <sub>VCC5V</sub> = 5 mA to 25 m<br>EN2 =                                       |                               |                      | -2.0         | 0.2        | 2.0                  | %    |

| Dropout Voltage                         | VIN = 5 V, I <sub>VCC5V</sub> = 2<br>EN1 = EN2                                   | 25 mA (External),<br>2 = Low  | V <sub>DO_VCC</sub>  |              |            | 200                  | mV   |

| SUPPLY CURRENT                          |                                                                                  |                               | •                    |              |            |                      |      |

| VIN Quiescent Current                   | EN1 high, 1 channel<br>EN1 and EN2 high,<br>phase per                            | 2 channel and 2               | I <sub>QVIN</sub>    | -<br>-       | 15<br>18   | 20<br>25             | mA   |

| VIN Shutdown Current                    | EN1 and E                                                                        | N2 low                        | I <sub>sdVIN</sub>   | -            | 8          | 10                   | mA   |

| REGULATION REFERENCE                    |                                                                                  |                               |                      |              |            |                      |      |

| Regulated Feedback Voltage              | Include offset of error amplifier                                                | 0°C to 85°C<br>-40°C to 125°C | V <sub>FB</sub>      | 596<br>594   | 600<br>600 | 604<br>606           | mV   |

| REFERENCE OUTPUT                        |                                                                                  |                               |                      |              |            |                      |      |

| VREF Output Voltage                     | I <sub>VREF</sub> = 5                                                            | Αμ 00                         | $V_{VREF}$           | 594          | 600        | 606                  | mV   |

| Load Regulation                         | I <sub>VREF</sub> = 0 m/                                                         | A to 2 mA                     |                      | -1.0         |            | 1.0                  | %    |

| DIFFERENTIAL VOLTAGE-SENSE A            |                                                                                  |                               | I.                   |              |            | <u> </u>             |      |

| Input Common Mode Voltage Range         | (Note                                                                            | 7)                            |                      | -0.2         |            | V <sub>CC</sub> -1.8 | V    |

| Output Voltage Swing                    | (Note                                                                            | 7)                            |                      |              |            | V <sub>CC</sub> -1.8 | V    |

| DC Gain                                 | VSP-VSN = 0.6                                                                    | V to V <sub>CC</sub> -1.8     | GAIN_DVA             | 0.995        | 1.0        | 1.005                | V/V  |

| -3dB Gain Bandwidth                     | C <sub>L</sub> = 20 pF to GND, F<br>(Note                                        |                               | BW_DVA               |              | 10         |                      | MHz  |

| Input Impedance                         | VSP – VSN                                                                        | I = 3.5 V                     | R <sub>VSEN</sub>    | 1.0          |            |                      | МΩ   |

| Input Bias Current                      | VSP,VSN                                                                          | = 2.0 V                       | I <sub>VS</sub>      | -400         |            | 400                  | nA   |

| Input Offset Voltage                    | VSP – VSN = 0.6 V to V <sub>CC</sub> – 1.8 V<br>–40°C to 100°C<br>–40°C to 125°C |                               | V <sub>osCS</sub>    | -1.3<br>-1.9 |            | 1.3<br>1.9           | mV   |

| VOLTAGE ERROR AMPLIFIER                 | •                                                                                |                               |                      |              | •          |                      |      |

| Open-Loop DC Gain                       | (Note 7)                                                                         |                               | GAIN <sub>EA</sub>   |              | 80         |                      | dB   |

| Unity Gain Bandwidth                    | (Note 7)                                                                         |                               | GBW <sub>EA</sub>    |              | 20         |                      | MHz  |

| Slew Rate                               | (Note 7)                                                                         |                               | SR <sub>COMP</sub>   |              | 20         |                      | V/μs |

| COMP Voltage Swing                      | I <sub>COMP</sub> (source                                                        | e) = 2 mA                     | V <sub>maxCOMP</sub> | 3.2          | 3.4        | -                    | V    |

|                                         | I <sub>COMP</sub> (sink)                                                         | = 2 mA                        | $V_{minCOMP}$        | -            | 1.05       | 1.15                 |      |

| FB, REFIN Bias Current                  | V <sub>FB</sub> = V <sub>REFI</sub>                                              | <sub>N</sub> = 1.0 V          | I <sub>FB</sub>      | -400         |            | 400                  | nA   |

**ELECTRICAL CHARACTERISTICS** ( $V_{IN}$  = 12 V, typical values are referenced to  $T_A$  = 25°C, Min and Max values are referenced to  $T_A$  from -40°C to 125°C. unless other noted.)

| Characteristics                  | Test Cond                                                                                                                        | Symbol                                                                                                 | Min                | Тур                                                   | Max                                                                  | Unit                                                    |     |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------|-----|

| DIFFERENTIAL CURRENT-SENSE A     | MPLIFIER                                                                                                                         |                                                                                                        |                    | -                                                     | •                                                                    |                                                         |     |

| DC Gain                          |                                                                                                                                  |                                                                                                        | GAIN <sub>CA</sub> |                                                       | 6                                                                    |                                                         | V/V |

| -3dB Gain Bandwidth              | (Note                                                                                                                            | 7)                                                                                                     | BW <sub>CA</sub>   |                                                       | 10                                                                   |                                                         | MHz |

| Input Common Mode Voltage Range  | (Note                                                                                                                            | 7)                                                                                                     |                    | -0.2                                                  |                                                                      | V <sub>CC</sub> +0.1                                    | V   |

| Differential Input Voltage Range | (Note                                                                                                                            | 7)                                                                                                     |                    | -60                                                   | -                                                                    | 60                                                      | mV  |

| Input Bias Current               | ISP,ISN =                                                                                                                        | 2.5 V                                                                                                  | I <sub>CS</sub>    | -100                                                  |                                                                      | 100                                                     | nA  |

| SWITCHING FREQUENCY              |                                                                                                                                  |                                                                                                        |                    | -                                                     | •                                                                    |                                                         |     |

| Switching Frequency              | Rfs = 5<br>Floa<br>Rfs = 8<br>Short to<br>Rfs = 1<br>Rfs = 2                                                                     | Rfs = 2.7k<br>Rfs = 5.1k<br>Float<br>Rfs = 8.2k<br>Short to GND<br>Rfs = 13k<br>Rfs = 20k<br>Rfs = 33k |                    | 180<br>270<br>360<br>450<br>540<br>720<br>900<br>1080 | 200<br>300<br>400<br>500<br>600<br>800<br>1000<br>1200               | 220<br>330<br>440<br>550<br>660<br>880<br>1100<br>1320  | kHz |

| Source Current                   |                                                                                                                                  |                                                                                                        | I <sub>FS</sub>    | 45                                                    | 50                                                                   | 55                                                      | μΑ  |

| SYSTEM RESET TIME                | •                                                                                                                                |                                                                                                        | •                  |                                                       | •                                                                    | •                                                       |     |

| System Reset Time                | Measured from EN to<br>with T <sub>DL</sub> =                                                                                    |                                                                                                        | T <sub>RST</sub>   | 1.8                                                   | 2.0                                                                  | 2.2                                                     | ms  |

| DELAY TIME                       |                                                                                                                                  |                                                                                                        |                    | •                                                     | •                                                                    | -                                                       |     |

| Delay Time                       | Float Rdl = 33k Rdl = 20k Rdl = 13k Rdl = 8.2k Rdl = 5.1k Rdl = 2.7k Short to GND (DLY1 Only) Short to GND (DDR Mode, DLY2 Only) | (Note 7)                                                                                               | T <sub>DL</sub>    | -<br>0.9<br>1.8<br>2.7<br>3.6<br>7.2<br>10.8<br>18    | 0<br>1.0<br>2.0<br>3.0<br>4.0<br>8.0<br>12<br>20<br>T <sub>DL1</sub> | -<br>1.1<br>2.2<br>3.3<br>4.4<br>8.8<br>13.2<br>22<br>- | ms  |

| Source Current                   |                                                                                                                                  |                                                                                                        | I <sub>DL</sub>    | 45                                                    | 50                                                                   | 55                                                      | μΑ  |

| SOFT START TIME                  | •                                                                                                                                |                                                                                                        |                    | _                                                     | •                                                                    |                                                         |     |

| Soft Start Time                  | OTP Configuration 1<br>(Note 7)                                                                                                  | Rss = 13k<br>Float<br>Rss = 20k<br>Rss = 33k                                                           | T <sub>SS</sub>    | 0.9<br>2.7<br>3.6<br>5.4                              | 1.0<br>3.0<br>4.0<br>6.0                                             | 1.1<br>3.3<br>4.4<br>6.6                                | ms  |

|                                  | OTP Configuration 2<br>(Note 7)                                                                                                  | Rss = 2.7k<br>Short to GND<br>Rss = 5.1k<br>Rss = 8.2k                                                 |                    | 0.9<br>2.7<br>3.6<br>5.4                              | 1.0<br>3.0<br>4.0<br>6.0                                             | 1.1<br>3.3<br>4.4<br>6.6                                |     |

| Source Current                   |                                                                                                                                  |                                                                                                        | I <sub>SS</sub>    | 45                                                    | 50                                                                   | 55                                                      | μΑ  |

**ELECTRICAL CHARACTERISTICS** ( $V_{IN}$  = 12 V, typical values are referenced to  $T_A$  = 25°C, Min and Max values are referenced to  $T_A$  from -40°C to 125°C. unless other noted.)

| Characteristics                                        | Test Cond                                  | Symbol                                 | Min                   | Тур                                                           | Max         | Unit  |       |

|--------------------------------------------------------|--------------------------------------------|----------------------------------------|-----------------------|---------------------------------------------------------------|-------------|-------|-------|

| CONFIGURATION                                          |                                            |                                        |                       |                                                               |             |       |       |

| PWM Configuration                                      |                                            | (Note 7)                               | С                     | hannel 1                                                      |             | Chan  | nel 2 |

|                                                        | Float                                      |                                        | PWM1<br>PWM1, PWM2    |                                                               |             | PWM4  |       |

|                                                        | Rcnfg = 2.7k                               |                                        |                       |                                                               | PWM4        |       |       |

|                                                        | Rcnfg = 5.1k                               |                                        | PWM1,                 | PWM2, PV                                                      | VM3         | PWM4  |       |

|                                                        | Short to GND                               |                                        | PW                    | M1, PWM2                                                      | 2           | PWM3, | PWM4  |

|                                                        | Rcnfg = 8.2k                               |                                        |                       | PWM1                                                          |             |       |       |

|                                                        | Rcnfg = 13k                                |                                        | PW                    | M1, PWM2                                                      | 2           |       |       |

|                                                        | Rcnfg = 20k                                |                                        | PWM1,                 | PWM2, PV                                                      | VM3         |       |       |

|                                                        | Rcnfg = 33k                                |                                        | PWM1, PW              | M2, PWM3                                                      | B, PWM4     |       |       |

| Source Current                                         |                                            | <u> </u>                               | I <sub>CNFG</sub>     | G 45 50                                                       |             |       | μΑ    |

| PGOOD                                                  | •                                          |                                        |                       | •                                                             |             |       |       |

| PGOOD Startup Delay                                    | Measured from end<br>PGOOD as              |                                        | T <sub>d_PGOOD</sub>  |                                                               | 100         |       | μs    |

| PGOOD Shutdown Delay                                   |                                            | Measured from EN to PGOOD de-assertion |                       |                                                               | 240         |       | ns    |

| PGOOD Low Voltage                                      | I <sub>PGOOD</sub> = 4 r                   | nA (sink)                              | V <sub>IPGOOD</sub>   | -                                                             | -           | 0.3   | V     |

| PGOOD Leakage Current                                  | PGOOD                                      | = 5 V                                  | I <sub>lkgPGOOD</sub> | -                                                             | _           | 1.0   | μΑ    |

| FAULT                                                  |                                            |                                        |                       |                                                               |             |       |       |

| FAULT Output High Voltage                              | I <sub>sourse</sub> = 0                    | ).5 mA                                 | V <sub>FAULT_H</sub>  | V <sub>CC</sub> -0.5                                          |             |       | V     |

| FAULT Output Low Voltage                               | $I_{sink} = 0.$                            | 5 mA                                   | V <sub>FAULT_L</sub>  |                                                               |             | 0.5   | V     |

| PROTECTIONS                                            | •                                          |                                        |                       |                                                               |             |       |       |

| Positive Current Limit Threshold                       | to GND                                     | ISP-ISN = 50 mV                        | V <sub>OCTH+</sub>    | 285                                                           | 300         | 315   | mV    |

|                                                        |                                            | ISP-ISN = 20 mV                        | 1                     | 110                                                           | 120         | 130   |       |

| Negative Current Limit Threshold                       | Measured from ILIMT to GND (only active in | ISP-ISN =<br>-50 mV                    | V <sub>OCTH</sub> -   | 285                                                           | 300         | 315   | mV    |

|                                                        | non-latched OVP)                           | ISP-ISN =<br>-20 mV                    |                       | 110                                                           | 120         | 130   |       |

| Positive Over Current Protection (OCP) Debounce Time   | (Note                                      | 7)                                     |                       |                                                               | 8<br>Cycles |       | μs    |

| Under Voltage Protection (UVP)<br>Threshold            | Voltage from F                             | B to GND                               | V <sub>UVTH</sub>     | 500                                                           | 510         | 520   | mV    |

| Under Voltage Protection (UVP)<br>Hysteresis           | Voltage from F                             | V <sub>UVHYS</sub>                     |                       | 20                                                            |             | mV    |       |

| Under Voltage Protection (UVP)<br>Debounce Time        | (Note                                      |                                        |                       | 1.5                                                           |             | us    |       |

| Shutdown Time in Hiccup Mode                           | UVP (No<br>OCP (No<br>OTP (No              |                                        |                       | 12*T <sub>SS</sub><br>16*T <sub>SS</sub><br>8*T <sub>SS</sub> |             | ms    |       |

| First–Level Over Voltage Protection (OVP_L) Threshold  | Voltage from F                             | B to GND                               | V <sub>OVTH_L</sub>   | 650                                                           | 660         | 670   | mV    |

| First-Level Over Voltage Protection (OVP_L) Hysteresis | Voltage from F                             | B to GND                               | V <sub>LOVHYS</sub>   |                                                               | -20         |       | mV    |

**ELECTRICAL CHARACTERISTICS** ( $V_{IN}$  = 12 V, typical values are referenced to  $T_A$  = 25°C, Min and Max values are referenced to  $T_A$  from -40°C to 125°C. unless other noted.)

| Characteristics                                            | Test Conditions                                                                      | Symbol                 | Min                  | Тур | Max  | Unit |

|------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------|----------------------|-----|------|------|

| PROTECTIONS                                                |                                                                                      | •                      |                      |     |      | •    |

| First-Level Over Voltage Protection (OVP_L) Debounce Time  | (Note 7)                                                                             |                        |                      | 1.0 |      | μs   |

| Second-Level Over Voltage Protection (OVP_H) Threshold     | Voltage from FB to GND                                                               | V <sub>OVTH_H</sub>    | 710                  | 720 | 730  | mV   |

| Second-Level Over Voltage Protection (OVP_H) Hysteresis    | Voltage from FB to GND                                                               | V <sub>HOVHYS</sub>    |                      | -20 |      | mV   |

| Second-Level Over Voltage Protection (OVP_H) Debounce Time | (Note 7)                                                                             |                        |                      | 1.0 |      | us   |

| Offset Voltage of OTP Comparator                           | V <sub>ILMT</sub> = 200 mV                                                           | V <sub>OS_OTP</sub>    | -2                   |     | 2    | mV   |

| OTP Source Current                                         |                                                                                      | I <sub>OTP</sub>       | 9                    | 10  | 11   | μΑ   |

| OTP Debounce Time                                          | (Note 7)                                                                             |                        |                      | 160 |      | ns   |

| Thermal Shutdown (TSD) Threshold                           | (Note 7)                                                                             | T <sub>sd</sub>        | 140                  | 165 |      | °C   |

| Recovery Temperature Threshold                             | (Note 7)                                                                             | T <sub>rec</sub>       |                      | 125 |      | °C   |

| Thermal Shutdown (TSD) Debounce Time                       | (Note 7)                                                                             |                        |                      | 120 |      | ns   |

| ENABLE                                                     |                                                                                      |                        |                      |     |      |      |

| EN ON Threshold                                            |                                                                                      | V <sub>EN_TH</sub>     | 0.75                 | 8.0 | 0.85 | V    |

| Hysteresis Source Current                                  | VCC5V is OK                                                                          | I <sub>EN_HYS</sub>    | 25                   | 30  | 35   | μΑ   |

| DRVON                                                      |                                                                                      |                        |                      |     |      |      |

| DRVON ON Threshold                                         |                                                                                      | V <sub>DRVON_TH</sub>  | 0.75                 | 0.8 | 0.85 | V    |

| Hysteresis Source Current                                  | VCC5V is OK                                                                          | I <sub>DRVON_HYS</sub> | 25                   | 30  | 35   | μΑ   |

| PWM MODULATION                                             |                                                                                      |                        |                      |     |      |      |

| Minimum On Time                                            | (Note 7)                                                                             | T <sub>on_min</sub>    |                      |     | 50   | ns   |

| Minimum Off Time                                           | (Note 7)                                                                             | T <sub>off_min</sub>   | 160                  |     |      | ns   |

| 0% Duty Cycle                                              | COMP voltage when the PWM outputs remain Lo (Note 7)                                 |                        |                      | 1.3 |      | ٧    |

| 100% Duty Cycle                                            | COMP voltage when the PWM outputs remain HI, V <sub>in</sub> = 12.0 V (Note 7)       |                        |                      | 2.5 |      | ٧    |

| Ramp Feed – forward Voltage Range                          | (Note 7)                                                                             |                        | 4.5                  |     | 20   | V    |

| PWM OUTPUT                                                 |                                                                                      |                        |                      |     |      |      |

| PWM Output High Voltage                                    | I <sub>sourse</sub> = 0.5 mA                                                         | V <sub>PWM_H</sub>     | V <sub>CC</sub> -0.2 |     |      | V    |

| PWM Output Low Voltage                                     | I <sub>sink</sub> = 0.5 mA                                                           | V <sub>PWM_L</sub>     |                      |     | 0.2  | ٧    |

| Rise and Fall Times                                        | C <sub>L</sub> (PCB) = 50 pF, measured between 10% & 90% of V <sub>CC</sub> (Note 7) |                        |                      | 10  |      | ns   |

| Leakage Current in Hi-Z Stage                              |                                                                                      | I <sub>LK_PWM</sub>    | -1.0                 |     | 1.0  | μΑ   |

Table 1. RESISTOR OPTIONS FOR FUNCTION PROGRAMMING

| Resi  | stance Range (k | Ω)    | Resistor Options (kΩ) |       |      |      |      |  |

|-------|-----------------|-------|-----------------------|-------|------|------|------|--|

| Min   | Тур             | Max   | ±5%                   | 6 ±1% |      |      |      |  |

| 2.565 | 2.7             | 2.835 | 2.7                   | 2.61  | 2.67 | 2.74 | 2.80 |  |

| 4.845 | 5.1             | 5.355 | 5.1                   | 4.87  | 4.99 | 5.11 | 5.23 |  |

| 7.79  | 8.2             | 8.61  | 8.2                   | 7.87  | 8.06 | 8.25 | 8.45 |  |

| 12.35 | 13              | 13.65 | 13                    | 12.4  | 12.7 | 13   | 13.3 |  |

| 19    | 20              | 21    | 20                    | 19.1  | 19.6 | 20   | 20.5 |  |

| 31.35 | 33              | 34.65 | 33                    | 31.6  | 32.4 | 33.2 | 34   |  |

#### **DETAILED DESCRIPTION**

## General

The NCP81232, a dual-channel/multi-phase synchronous buck controller, provides power management solutions for various applications supported by DrMOS. It has 8 programmable power-stage configurations, differential voltage and current sense, flexible power sequence programming, and comprehensive protections.

same channel are paralleled together in output of power stage with a common voltage-sense feedback. All the input pins of voltage sense and current senses in unused channel and phases can be left float. For single-channel configuration, EN2 pin is recommended to be pulled low to ground.

## **Operation Modes**

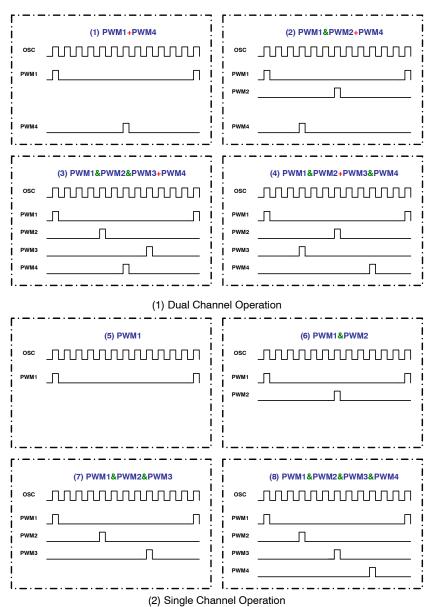

The NCP81232 has eight programmable operation configurations as shown in Figure 7. All the phases in the

Figure 7. 8 Programmable Configurations and Interleaved Operation Among Phases

## Soft Start

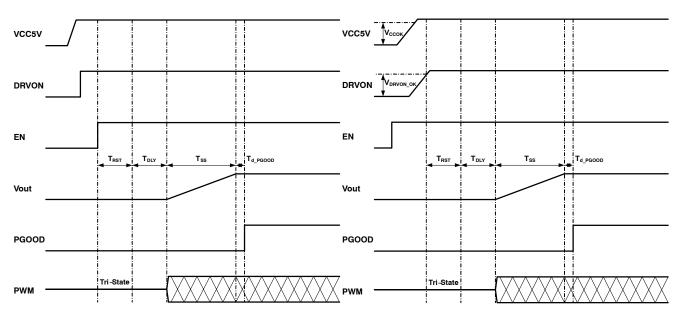

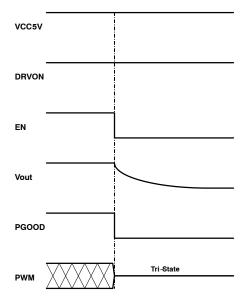

The NCP81232 has a soft start function and the soft start time is externally programmed at SS pin. The output starts to ramp up following a system reset period TRST and a programmable delay time TDLY after the device is enabled and both VCC5V and DRVON are ready. The device is able to start up smoothly under an output pre-biased condition without discharging the output before ramping up.

(1) VCC5V and DRVON Ready before EN

(2) VCC5V and DRVON Ready after EN

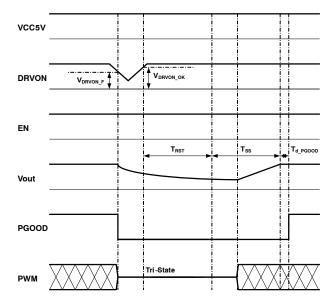

Figure 8. Timing Diagrams of Power Up Sequence

Figure 9. Timing Diagram of Power Down Sequence

Figure 10. Timing Diagram of DRVON UVLO

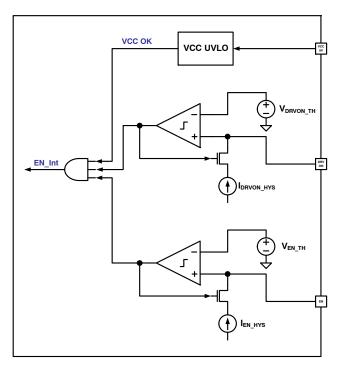

Figure 11. Enable, DRVON, and VCC UVLO

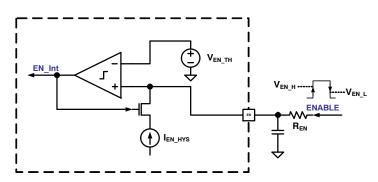

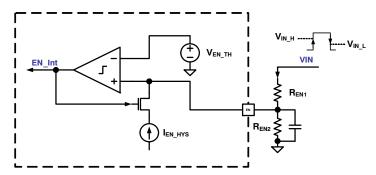

## **Enable and Input UVLO**

The NCP81232 is enabled when the voltage at EN pin is higher than an internal threshold  $VEN\_TH = 0.8~V$ . A hysteresis can be programmed by an external resistor REN connected to EN pin as shown in Figure 12. The high threshold in ENABLE signal is

$$V_{EN\ H}=V_{EN\ TH}$$

(eq. 1)

The low threshold in ENABLE signal is

$$V_{EN\ L} = V_{EN\ TH} - V_{EN\ HYS}$$

(eq. 2)

The programmable hysteresis in ENABLE signal is

$$V_{EN\_HYS} = I_{EN\_HYS} \cdot R_{EN}$$

(eq. 3)

Figure 12. Enable and Hysteresis Programming

A UVLO function for input power supply can be implemented at EN pins. As shown in Figure 13, the UVLO thresholds and hysteresis can be programmed by two external resistors.

$$V_{IN\_H} = \left(\frac{R_{EN1}}{R_{EN2}} + 1\right) \cdot V_{EN\_TH}$$

(eq. 4)

$$V_{IN\ L} = V_{IN\ H} - V_{IN\ HYS}$$

(eq. 5)

$$V_{IN\_HYS} = I_{EN\_HYS} \cdot R_{EN1}$$

(eq. 6)

Figure 13. Enable and Input Supply UVLO Circuit

To avoid undefined operation, EN pins cannot be left float in applications.

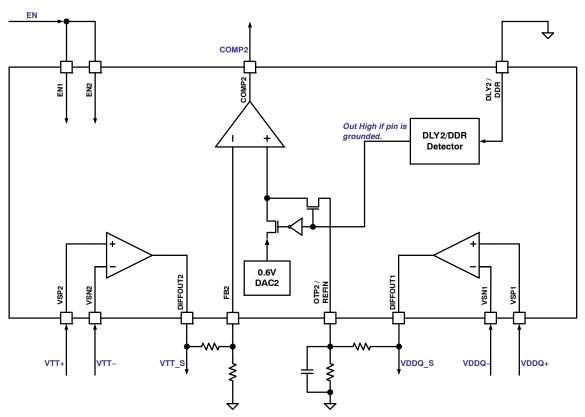

## **DDR Mode Operation**

Figure 14. Block Diagram of DDR Mode Operation

If DLY2/DDR pin is shorted to GND before the NCP81232 starts up, as shown in Figure 14, the device is internally configured to operate in DDR mode. In DDR mode, the channel 1 provides power for VDDQ rail and the channel 2 provides power for VTT rail. The two enable pins need to be connected together, and the CNFG pin can be programmed to be one of the four dual-channel options (1+1, 2+1, 3+1, 2+2). The both channels have the same delay time programmed at DLY1 pin, and VTT rail always tracks with VDDQ/2. An external resistor divider, which is connected from DIFFOUT1 to GND, is employed to get 0.6V at REFIN pin in steady-state operation. Another

external resistor divider, which is connected from DIFFOUT2 to GND, is applied to obtain an expected VTT voltage considering FB2 voltage is 0.6V as REFIN.

In DDR mode, two channels have independent fault detections and protections but have hiccup together if anyone of them needs to start a hiccup.

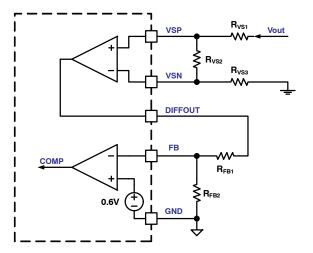

## **Output Voltage Sensing and Regulation**

The NCP81233 has a differential voltage-sense amplifier. As shown in Figure 15, the remote voltage sensing points are connected to input pins VSP and VSN of the differential

voltage-sense amplifier via a resistor network composed by RVS1, RVS2, and RVS3.

In most of cases, RVS3 = 0  $\Omega$  or 100  $\Omega$ . To have enough operation headroom for the input pins of the differential amplifier, usually the input voltage VSP–VSN is designed to be not higher than 2.5 V. If  $V_{OUT}$  > 2.5 V, VSP–VSN is divided down to be 2.5 V by the resistor network. With a given RVS2 like 1 k $\Omega$ , then the value of RVS1 can be obtained by

$$R_{VS1} = \frac{(V_{OUT} - 2.5) \cdot R_{VS2}}{2.5} - R_{VS3}$$

(eq. 7)

If VOUT  $\leq$  2.5 V, RVS1 = 0  $\Omega$  and RVS2 can be left open. DIFFOUT pin, the output of the differential amplifier, is fed to FB pin of the error amplifier in the same channel. The resistance of RFB1 between DIFFOUT and FB can be selected in a range from 500  $\Omega$  to 50 k $\Omega$  having a typical value of 10 k $\Omega$ . The resistance of RFB2 from FB to GND can be calculated by

$$R_{FB2} = \frac{0.6 \cdot R_{FB1}}{V_{OUT} \cdot \frac{R_{VS2}}{R_{VS1} + R_{VS2} + R_{VS3}} - 0.6}$$

(eq. 8)

Figure 15. Output Voltage Sensing and Regulation

## **Over Voltage Protection (OVP)**

A two-level recoverable over voltage protection is employed in the NCP81232, which is based on voltage detection at FB pin. If FB voltage is over VOVTH L (660 mV typical) for more than 1us, the first over voltage protection OVPL is triggered and PGOOD is pulled low. In the meanwhile, all the high-side MOSFETs are turned off and all the low-side MOSFETs are turned on. A negative current protection in low-side MOSFETs is active in this protection level, and it turns off low-side MOSFET for at least 50 ns if negative current is over the limit. However, in a worse case that FB voltage rises to be over VOVTH H (720 mV typical) for more than 1us, the second level over voltage protection OVPH takes in charge. As same as the first level OVP, all the high-side MOSFETs are turned off and all the low-side MOSFETs are turned on, but the negative current protection is disabled. The over voltage protection can be cleared once FB voltage drops 20 mV lower than VOVTH L, and then the system comes back to normal operation.

OVPH detection starts from the beginning of soft-start time TSS and ends in shutdown and idle time of hiccup mode caused by other protections, while OVPL detection starts after PGOOD delay (Td\_PGOOD) is expired and ends at the same time as OVPH.

## **Under Voltage Protection (UVP)**

The NCP81232 pulls PGOOD low and turns off both high-side and low-side MOSFETs once FB voltage drops below VUVTH (540 mV typical) for more than 1.5 µs. Under voltage protection operates in a hiccup mode. A normal power up sequence happens after a hiccup interval.

UVP detection starts when PGOOD delay (Td\_PGOOD) is expired right after a soft start, and ends in shutdown and idle time of hiccup mode.

#### **Over Current Protection (OCP)**

The NCP81232 senses phase currents by differential current sense amplifiers and provides a cycle-by-cycle over current protection for each phase. If OCP happens in all the phases of the same channel and lasts for more than 8 times of switching cycle, the channel shuts down and enters into a hiccup mode. The channel may enter into hiccup mode sooner due to the under voltage protection in a case if the output voltage drops down very fast.

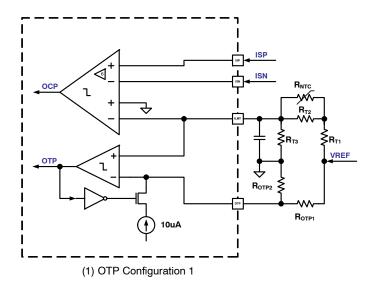

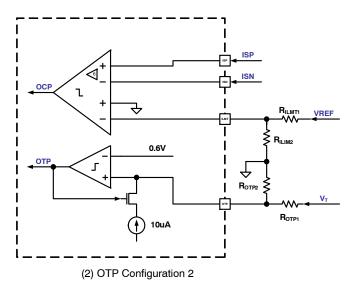

Figure 16. Over-Current Protection and Over-Temperature Protection

The over-current threshold can be externally programmed at the ILIM pin for each channel. As shown in Figure 16 (1), a NTC resistor RNTC can be employed for temperature compensated over current protection. The peak current limit per phase can be calculated by

$$V_{ISP} - V_{ISN} = \frac{1}{6} \cdot \frac{R_{T3}}{R_{T1} + \frac{R_{T2} \cdot R_{NTC}}{R_{T2} + R_{NTC}} + R_{T3}} \cdot V_{REF}^{\text{(eq. 9)}}$$

If no temperature compensation is needed, as shown in Figure 16 (2), the peak current limit per phase can be simply set by

$$V_{ISP} - V_{ISN} = \frac{1}{6} \cdot \frac{R_{ILIM2}}{R_{ILIM1} + R_{ILIM2}} \cdot V_{REF}$$

(eq. 10)

OCP detection starts from the beginning of soft-start time TSS, and ends in shutdown and idle time of hiccup mode.

#### **Over Temperature Protection (OTP)**

The NCP81232 provides over temperature protection for each channel. To serve different types of DrMOS, one of two internal configurations of OTP detection can be selected at SS pin combined with a soft start time programming.

With OTP Configuration 1, as shown in Figure 16 (1), the NTC resistor RNTC senses the hot–spot temperature and changes the voltage at ILMT pin. Both over–temperature threshold and hysteresis are externally programmed at OTP pin by a resistor divider. Once the voltage at ILMT pin is higher than the voltage at OTP pin, OTP trips and the channel is shut down. The channel will have a normal start up after a hiccup interval in condition that the temperature drops below the OTP reset threshold. The OTP assertion threshold VOTP and reset threshold VOTP\_RST can be calculated by

$$V_{OTP} = \frac{V_{REF} + I_{OTP\_HYS} \cdot R_{OTP1}}{1 + \frac{R_{OTP1}}{R_{OTP2}}}$$

(eq. 11)

$$V_{OTP\_RST} = \frac{V_{REF} \cdot R_{OTP2}}{R_{OTP1} + R_{OTP2}}$$

(eq. 12)

The corresponding OTP temperature TOTP and reset temperature TOTP RST can be calculated by

$$T_{OTP} = \frac{1}{\frac{\ln(R_{NTC}/R_{NTC})}{B} + \frac{1}{25 + 273.15}} - 273.15$$

(eq. 13)

$$T_{OTP\_RST} = \frac{1}{\frac{\ln(R_{NTC\_OTPRST}/R_{NTC})}{B} + \frac{1}{25 + 273.15}} - 273.15$$

(eq. 14)

where

$$R_{NTC\_OTP} = \frac{1}{\frac{1}{R_{T \text{ OTP}} - R_{T1}} - \frac{1}{R_{T2}}}$$

(eq. 15)

$$R_{NTC\_OTPRST} = \frac{1}{\frac{1}{R_{T\_OTPRST} - R_{T1}} - \frac{1}{R_{T2}}}$$

(eq. 16)

$$R_{T\_OTP} = \left(\frac{V_{REF}}{V_{OTP}} - 1\right) \cdot R_{T3} \qquad (eq. 17)$$

$$R_{T\_OTPRST} = \left(\frac{V_{REF}}{V_{OTP\_RST}} - 1\right) \cdot R_{T3} \quad \text{(eq. 18)}$$

With OTP Configuration 2, as shown in Figure 16 (2), the NCP81232 receives an external signal VT linearly representing temperature and compares to an internal 0.6 V reference voltage. If the voltage is over the threshold OTP

happens. The OTP assertion threshold VOTP and reset threshold VOTP\_RST in this configuration can be obtained by

$$V_{T\_OTP} = \left(1 + \frac{R_{OTP1}}{R_{OTP2}}\right) \cdot 0.6 \qquad \text{(eq. 19)}$$

$$V_{T\_OTP\_RST} = \left(\frac{0.6}{R_{OTP2}} - I_{OTP\_HYS}\right) \cdot R_{OTP1} + 0.6$$

(eq. 20

OTP detection starts from the beginning of soft-start time TSS, and ends in shutdown and idle time of hiccup mode.

## Thermal Shutdown (TSD)

The NCP81232 has an internal thermal shutdown protection to protect the device from overheating in an extreme case that the die temperature exceeds 150°C. TSD detection is activated when VCC5V and at least one of ENs are valid. Once the thermal protection is triggered, the whole chip shuts down and all PWM signals are in high impedance. If the temperature drops below 125°C, the system automatically recovers and a normal power sequence follows.

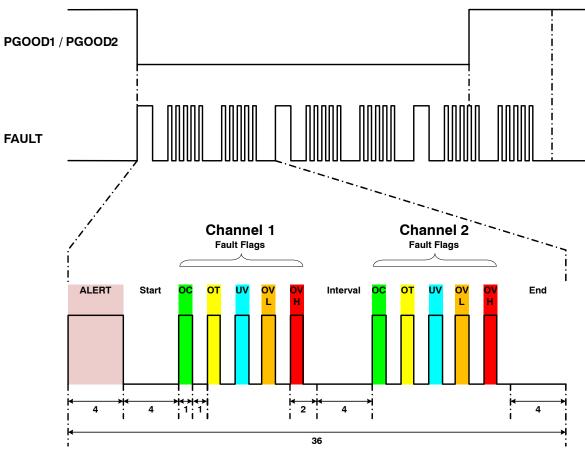

#### **FAULT Indicator**

The NCP81232 has a comprehensive fault indicator by means of a cycle-by-cycle fault signal output from FAULT pin. Figure 17 shows a typical timing diagram of FAULT signal. FAULT signal is composed of ALEART and two portions of fault flags for the two channels, having a total cycle period of 36 µs. A corresponding fault flag is asserted to high once the fault happens. The periodic fault signal starts from the point where any fault has been confirmed and ends after PGOOD is asserted again. Note the last FAULT cycle has to be complete after PGOOD assertion.

Figure 17. Timing Diagram of FAULT Signal

## **LAYOUT GUIDELINES**

## **Electrical Layout Considerations**

Good electrical layout is a key to make sure proper operation, high efficiency, and noise reduction. Electrical layout guidelines are:

- Power Paths: Use wide and short traces for power paths (such as VIN, VOUT, SW, and PGND) in power stages to reduce parasitic inductance and high-frequency loop area. It is also good for efficiency improvement.

- Power Supply Decoupling: The devices should be well decoupled by input capacitors and input loop area should be as small as possible to reduce parasitic inductance, input voltage spike, and noise emission. Usually, a small low-ESL MLCC is placed very close to VIN and PGND pins.

- VCC Decoupling: Place decoupling caps as close as possible to VCC5V pin of the NCP81232 and VCCP pins of DrMOS.

- Switching Node: Each SW node in power stages should be a copper pour, but compact because it is also a noise source.

- Bootstrap: The bootstrap cap and an option resistor per phase need to be very close and directly connected between bootstrap pin and SW pin of DrMOS.

- Ground: It would be good to have separated ground planes for power ground PGND and analog ground GND and connect the two planes at one point.

- Voltage Sense: Use Kelvin sense pair and arrange a

"quiet" path for the differential output voltage sense.

Careful layout for multi-phase locations and output

capacitor distribution would help to get even voltage

ripple at the voltage sensing point, and have better

current balance as well.

- Current Sense: Use Kelvin sense pair and arrange a

"quiet" path for the differential current sense per phase.

Careful layout for current sensing is critical for jitter

minimization, accurate current limiting, and good

current balance. The current–sense filter capacitors and

resistors should be close to the controller. The

temperature compensating thermistor should be placed

as close as possible to the inductor. The wiring path

should be kept as short as possible but well away from

the switch nodes.

- Compensation Network: The small feedback capacitor from COMP to FB should be as close to the controller as possible. Keep the FB traces short to minimize their capacitance to ground.

## **Thermal Layout Considerations**

Good thermal layout helps high power dissipation from a small package with reduced temperature rise. Thermal layout guidelines are:

- The exposed pads must be well soldered on the board.

- A four or more layers PCB board with solid ground planes is preferred for better heat dissipation.

- More free vias are welcome to be around DrMOS and underneath the exposed pads to connect the inner ground layers to reduce thermal impedance.

- Use large area copper pour to help thermal conduction and radiation.

- Do not put the inductor to be too close to the DrMOS, thus the heat sources are decentralized.

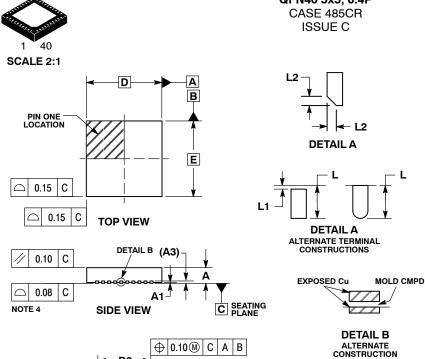

## **MECHANICAL CASE OUTLINE**

**DETAIL A**

40X L

|⊕|0.10@| C | A | B

0.10 M C A B

0.05 M C NOTE 3

E2

QFN40 5x5, 0.4P

**DATE 27 AUG 2013**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994. CONTROLLING DIMENSIONS: MILLIMETERS.

- CONTROLLING DIMENSIONS: MILLIMETERS

DIMENSION & APPLIES TO PLATED

TERMINAL AND IS MEASURED BETWEEN

0.15 AND 0.30mm FROM THE TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED

- PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 0.80        | 1.00 |  |  |

| A1  |             | 0.05 |  |  |

| А3  | 0.20        | REF  |  |  |

| b   | 0.15        | 0.25 |  |  |

| D   | 5.00        | BSC  |  |  |

| D2  | 3.40        | 3.60 |  |  |

| Е   | 5.00        | BSC  |  |  |

| E2  | 3.40        | 3.60 |  |  |

| е   | 0.40 BSC    |      |  |  |

| L   | 0.30        | 0.50 |  |  |

| L1  |             | 0.15 |  |  |

| L2  | 0.12        | REF  |  |  |

#### GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code = Assembly Location

WL = Wafer Lot YY = Year ww = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part

Pb-Free indicator, "G" or microdot " ■", may or may not be present.

## **RECOMMENDED SOLDERING FOOTPRINT**

**BOTTOM VIEW**

е

e/2

D<sub>2</sub>

<del>doooo</del>oood

**DIMENSIONS: MILLIMETERS**

Electronic versions are uncontrolled except when accessed directly from the Document Repository. **DOCUMENT NUMBER:** 98AON83971E Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. **DESCRIPTION:** QFN40, 5x5, 0.4P **PAGE 1 OF 1**

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.