# Multi-Phase Controller with I<sup>2</sup>C Interface for DrMOS

The NCP81233, a multi-phase synchronous buck controller with an I<sup>2</sup>C interface, provides power management solutions for applications supported by DrMOS. It supports 1-, 2-, 3-, 4-, or 6-phase operation and provides differential voltage and current sense, flexible programming, and comprehensive protections.

# Features

- Selectable 1-, 2-, 3-, 4-, or 6-Phase Operation

- Support up to 12-Phase Operation with Phase Doublers

- I<sup>2</sup>C Interface with 8 Programmable Addresses

- Vin =  $4.5 \text{ V} \sim 20 \text{ V}$  with Input Feedforward

- Integrated 5.35 V LDO and 3.3 V LDO

- Fsw = 200 k ~ 1.2 MHz

- Vout = 0.6 V ~ 5.3 V with 0.25 V~1.52 V DAC (5 mV/step)

- Programmable Vboot Voltage 0.6V ~ 1.23V (10mV/step) with Restore Function

- DVID Slew Rate Options (0.125 mV/us, 0.25 mV/us, 0.5 mV/us, 1 mV/us, 2 mV/us, 4 mV/us, 8 mV/us, 16 mV/us)

- Programmable External Reference Input

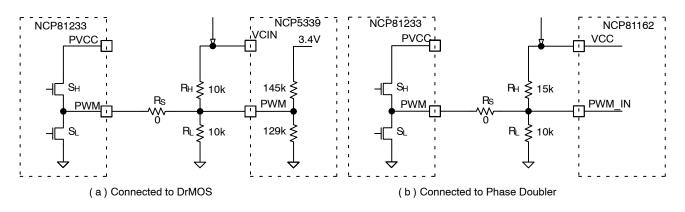

- PWM Output Compatible to 3.3 V and 5 V DrMOS

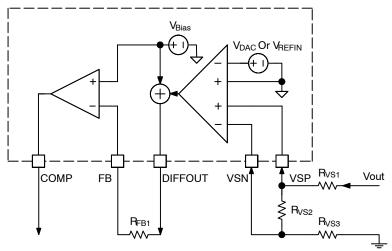

- Differential Output Voltage Sense

- Differential Current Sense Compatible for both Inductor DCR Sense and DrMOS Iout Signal

- Programmable Load Line

- Report of Vout and Iout

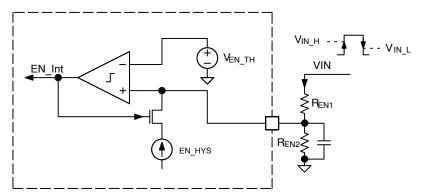

- Enable with Programmable Input UVLO

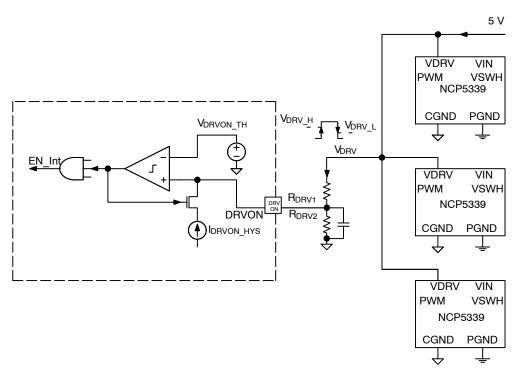

- DrMOS Power Ready Detection (DRVON)

- Externally Programmable Soft Start

- Power Saving Interface

- Power Good Indicator

- Programmable Over Current Protection

- Programmable Over/Under Voltage Protection

- Hiccup Over Temperature Protection

- Thermal Shutdown Protection

- This is a Pb-Free Device

# **Typical Applications**

- Telecom Applications

- Server and Storage System

- Graphics Card Applications

- Multiphase DC-DC Power Management

# **ON Semiconductor®**

www.onsemi.com

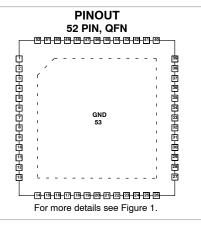

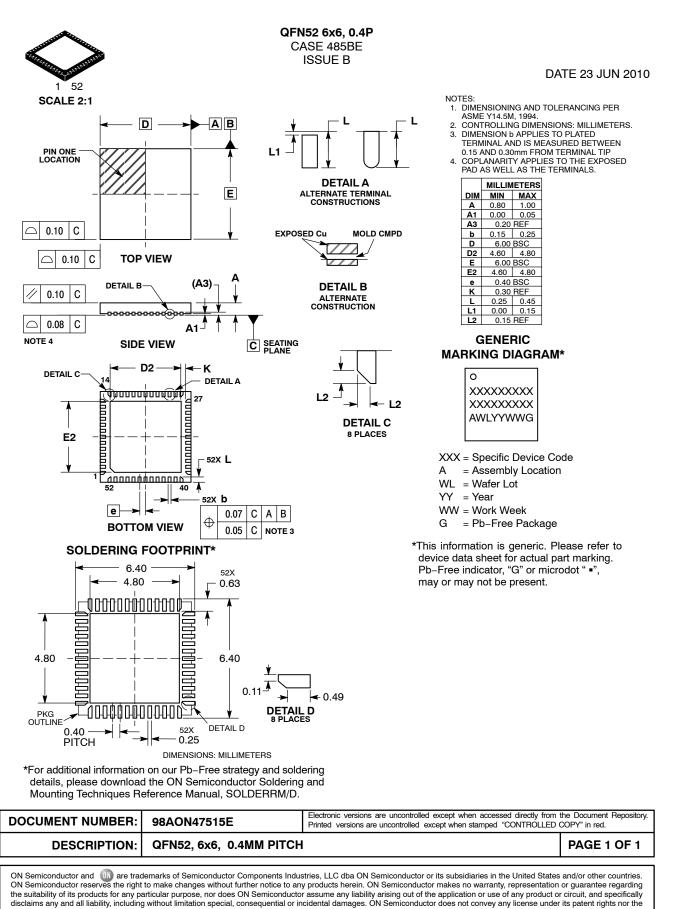

GFN52 6x6, O.4P CASE 485BE

# MARKING DIAGRAM\*

- A = Assembly Location

- WL = Wafer Lot

- YY = Year

- WW = Work Week

- G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

#### **ORDERING INFORMATION**

| Device        | Package            | Shipping†          |

|---------------|--------------------|--------------------|

| NCP81233MNTXG | QFN52<br>(Pb-Free) | 2500 / Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

Figure 1. Pin Configuration

# **TABLE 1. PIN DESCRIPTION**

| Pin | Name             | Туре                | Description                                                                                                                                                                                                                                                                                            |

|-----|------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IMON             | Analog Output       | OUT Current Monitor. Provides output signal representing output current by connecting a capacitor from this pin to ground.                                                                                                                                                                             |

| 2   | IMAX             | Analog Input        | Current Maximum. A resistor from this pin to ground programs IMAX.                                                                                                                                                                                                                                     |

| 3   | VBOOT1           | Analog Input        | Boot-Up Voltage 1. A resistor from this pin to ground programs boot voltage                                                                                                                                                                                                                            |

| 4   | VBOOT2           | Analog Input        | Boot-Up Voltage 2. A resistor from this pin to ground programs boot voltage.                                                                                                                                                                                                                           |

| 5   | SS               | Analog Input        | Soft-Start Slew Rate. A resistor from this pin to ground programs soft-start slew rate.                                                                                                                                                                                                                |

| 6   | FSET             | Analog Input        | Frequency Selection. A resistor from this pin to ground programs switching frequency per phase.                                                                                                                                                                                                        |

| 7   | CONFIG           | Analog Input        | Configuration. A resistor from this pin to ground programs configuration of power stages.                                                                                                                                                                                                              |

| 8   | MODE1            | Analog Input        | Mode Programming 1. A resistor from this pin to ground programs configuration of operation functions.                                                                                                                                                                                                  |

| 9   | MODE2            | Analog Input        | Mode Programming 2. A resistor from this pin to ground programs configuration of operation functions.                                                                                                                                                                                                  |

| 10  | ADDR             | Analog Input        | Address. A resistor from this pin to ground programs address of I <sup>2</sup> C interface.                                                                                                                                                                                                            |

| 11  | SDA              | Logic Bidirectional | Serial Data I/O Port. Data port of I <sup>2</sup> C interface.                                                                                                                                                                                                                                         |

| 12  | ALERT#           | Logic Output        | ALERT. Open-drain output. Provides a logic low valid alert signal.                                                                                                                                                                                                                                     |

| 13  | SCL              | Logic Input         | Serial Clock. Clock input of I <sup>2</sup> C interface.                                                                                                                                                                                                                                               |

| 14  | PGOOD            | Logic Output        | Power GOOD. Open-drain output. Provides a logic high valid power good output signal, indicating the regulator's output is in regulation window.                                                                                                                                                        |

| 15  | DRVON            | Analog Input        | Driver On. High input voltage means power supply of DrMOS's driver is ready.                                                                                                                                                                                                                           |

| 16  | EN               | Analog Input        | Enable. Logic high enables controller while logic low disables controller. Input supply UVLO can be programmed at this pin.                                                                                                                                                                            |

| 17  | VIN              | Power Input         | Power Supply Input. Power supply input pin of the device, which is connected to the integrated 5.35 V LDO and 3.3 V LDO. 4.7 $\mu F$ or more ceramic capacitors must bypass this input to power ground. The capacitors should be placed as close as possible to this pin.                              |

| 18  | VCC5V            | Analog Power        | Voltage Supply of Controller. Output of integrated 5.35 V LDO and power input pin of analog circuits. A 4.7 $\mu F$ ceramic capacitor bypasses this input to GND. This capacitor should be placed as close as possible to this pin.                                                                    |

| 19  | VCC3V            | Analog Power        | 3.3 V Voltage Supply. Output of integrated 3.3 V LDO. A 4.7 $\mu F$ ceramic capacitor bypasses this input to GND. This capacitor should be placed as close as possible to this pin.                                                                                                                    |

| 20  | PVCC             | Analog Power        | Voltage Supply of PWM Drivers. Power supply input pin of internal PWM drivers and digital circuits, which is connected to VCC5 V via a 4.7 $\Omega$ resistor. A 1 $\mu F$ or larger ceramic capacitor bypasses this input to ground. This capacitor should be placed as close as possible to this pin. |

| 21  | PWM6             | Analog Output       | PWM 6. PWM output of phase 6.                                                                                                                                                                                                                                                                          |

| 22  | PWM5             | Analog Output       | PWM 5. PWM output of phase 5.                                                                                                                                                                                                                                                                          |

| 23  | PWM4             | Analog Output       | PWM 4. PWM output of phase 4.                                                                                                                                                                                                                                                                          |

| 24  | PWM3             | Analog Output       | PWM 3. PWM output of phase 3.                                                                                                                                                                                                                                                                          |

| 25  | PWM2             | Analog Output       | PWM 2. PWM output of phase 2.                                                                                                                                                                                                                                                                          |

| 26  | PWM1             | Analog Output       | PWM 1. PWM output of phase 1.                                                                                                                                                                                                                                                                          |

| 27  | VB_RST# /<br>PSI | Logic Input         | VBOOT Restore. Logic low restores output to boot voltage.<br>Power Saving Interface. Logic high enables Multi-phase CCM operation, and logic<br>low enables 1-phase CCM operation.<br>Pin function is programmed at MODE2 pin.                                                                         |

| 28  | ISP6             | Analog Input        | Current Sense Positive Input 6. Non-inverting input of differential current sense amplifier of phase 6.                                                                                                                                                                                                |

# TABLE 1. PIN DESCRIPTION (continued)

| Pin | Name      | Туре          | Description                                                                                                                                                             |

|-----|-----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29  | ISN6      | Analog Input  | Current Sense Negative Input 6. Inverting input of differential current sense amplifier of phase 6.                                                                     |

| 30  | ISN5      | Analog Input  | Current Sense Negative Input 5. Inverting input of differential current sense amplifier of phase 5.                                                                     |

| 31  | ISP5      | Analog Input  | Current Sense Positive Input 5. Non-inverting input of differential current sense amplifier of phase 5.                                                                 |

| 32  | ISP4      | Analog Input  | Current Sense Positive Input 4. Non-inverting input of differential current sense amplifier of phase 4.                                                                 |

| 33  | ISN4      | Analog Input  | Current Sense Negative Input 4. Inverting input of differential current sense amplifier of phase 4.                                                                     |

| 34  | ISN3      | Analog Input  | Current Sense Negative Input 3. Inverting input of differential current sense amplifier of phase 3.                                                                     |

| 35  | ISP3      | Analog Input  | Current Sense Positive Input 3. Non-inverting input of differential current sense amplifier of phase 3.                                                                 |

| 36  | ISP2      | Analog Input  | Current Sense Positive Input 2. Non-inverting input of differential current sense amplifier of phase 2.                                                                 |

| 37  | ISN2      | Analog Input  | Current Sense Negative Input 2. Inverting input of differential current sense amplifier of phase 2.                                                                     |

| 38  | ISN1      | Analog Input  | Current Sense Negative Input 1. Inverting input of differential current sense amplifier of phase 1.                                                                     |

| 39  | ISP1      | Analog Input  | Current Sense Positive Input 1. Non-inverting input of differential current sense amplifier of phase 1.                                                                 |

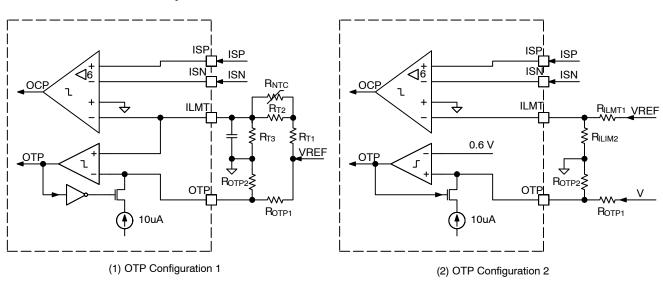

| 40  | ILMT      | Analog Input  | Limit of Current. Voltage at this pin sets over-current threshold.                                                                                                      |

| 41  | OTP       | Analog Input  | Over Temperature Protection. Voltage at this pin sets over-temperature threshold.                                                                                       |

| 42  | VREF      | Analog Output | Output of Reference. Output of 0.6 V reference. A 10 nF ceramic capacitor bypasses this input to GND. This capacitor should be placed as close as possible to this pin. |

| 43  | CSSUM     | Analog Output | Current Sense SUM. Output of current sum amplifier.                                                                                                                     |

| 44  | VDFB      | Analog Output | Droop Amplifier Feedback. Inverting input of droop amplifier                                                                                                            |

| 45  | VDRP      | Analog Output | Droop Amplifier Output. Output of droop amplifier.                                                                                                                      |

| 46  | NC        | No Connection |                                                                                                                                                                         |

| 47  | COMP      | Analog Output | Compensation. Output pin of error amplifier.                                                                                                                            |

| 48  | FB        | Analog Input  | Feedback. Inverting input of internal error amplifier.                                                                                                                  |

| 49  | DIFFOUT   | Analog Output | Differential Amplifier Output. Output pin of differential voltage sense amplifier.                                                                                      |

| 50  | VSP       | Analog Input  | Voltage Sense Positive Input. Non-inverting input of differential voltage sense amplifier.                                                                              |

| 51  | VSN       | Analog Input  | Voltage Sense Negative Input. Inverting input of differential voltage sense amplifier.                                                                                  |

| 52  | REFIN     | Analog Input  | Reference Voltage Input. External reference voltage input.                                                                                                              |

| 53  | THERM/GND | Analog Ground | Thermal Pad and Analog Ground. Ground of internal control circuits. Must be connected to the system ground.                                                             |

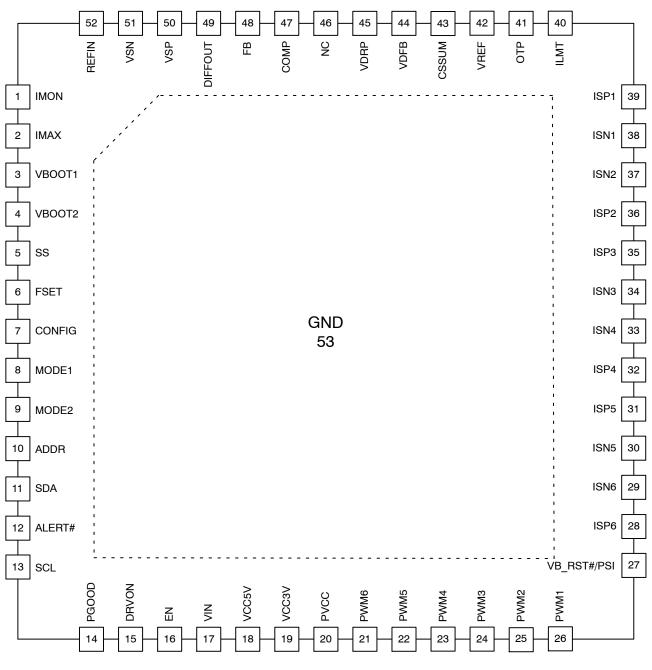

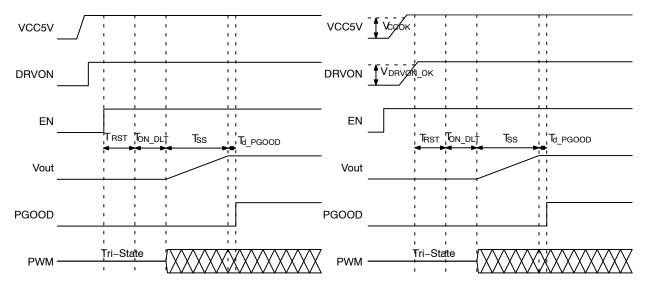

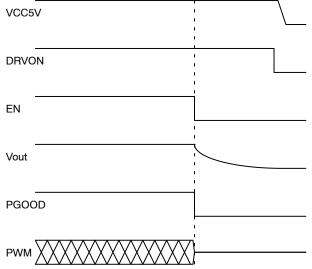

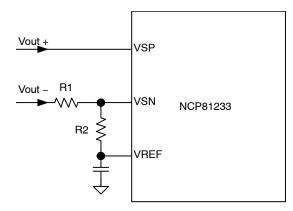

Figure 2. Typical Application Circuit with Programmed Boot Voltage

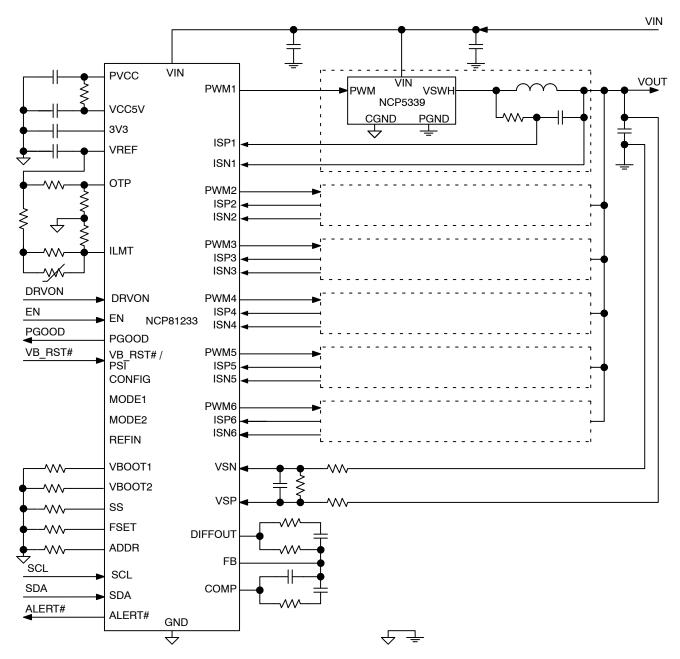

Figure 3. Typical Application Circuit with External Reference Input

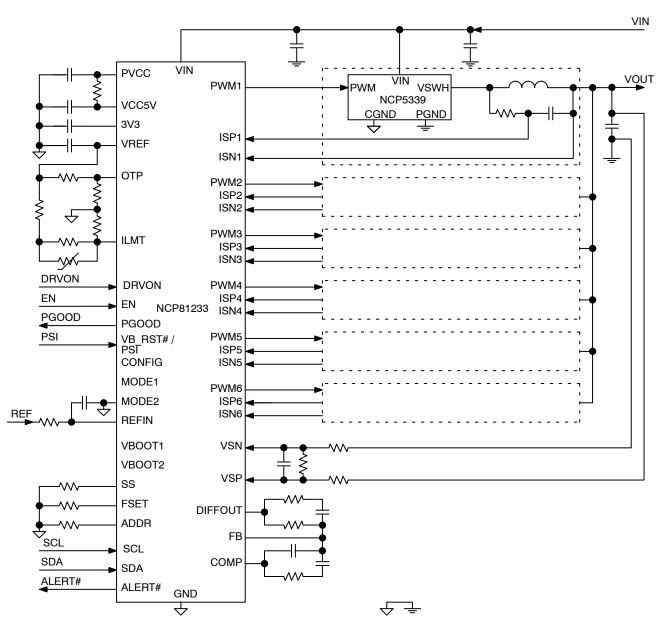

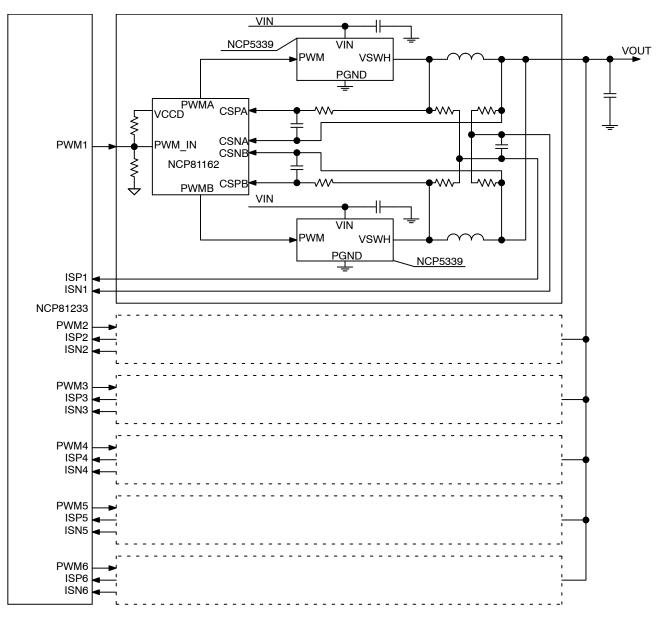

Figure 4. Application Circuit with Phase Doublers

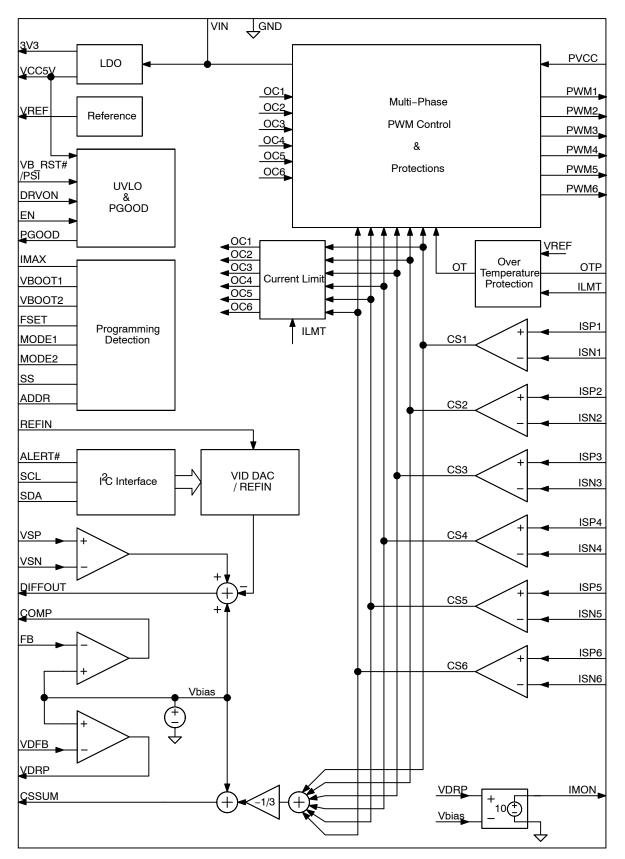

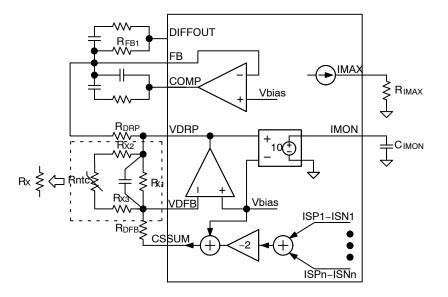

Figure 5. Functional Block Diagram

#### **TABLE 2. MAXIMUM RATINGS**

|                                                   |                    | V    | alue       |      |

|---------------------------------------------------|--------------------|------|------------|------|

| Rating                                            | Symbol             | MIN  | MAX        | Unit |

| Power Supply Voltage to PGND                      | V <sub>VIN</sub>   |      | 30         | V    |

| Supply Voltage VCC5V to GND                       | V <sub>VCC5V</sub> | -0.3 | 6.5        | V    |

| VSNx to GND                                       | V <sub>VSN</sub>   | -0.2 | 0.2        | V    |

| Other Pins to GND                                 |                    | -0.3 | VCC5 V+0.3 | V    |

| Human Body Model (HBM) ESD Rating are (Note 1)    | ESD HBM            |      | 2500       | V    |

| Charge Device Model (CDM) ESD Rating are (Note 1) | ESD CDM            |      | 2000       | V    |

| Latch up Current: (Note 2)                        | I <sub>LU</sub>    | -100 | 100        | mA   |

| Operating Junction Temperature Range (Note 3)     | TJ                 | -40  | 125        | °C   |

| Operating Ambient Temperature Range               | T <sub>A</sub>     | -40  | 100        | °C   |

| Storage Temperature Range                         | T <sub>STG</sub>   | -55  | 150        | °C   |

| Thermal Resistance Junction to Top Case(Note 4)   | R <sub>ΨJC</sub>   |      | 1.65       | °C/W |

| Thermal Resistance Junction to Board (Note 4)     | R <sub>ΨJB</sub>   |      | 3.2        | °C/W |

| Thermal Resistance Junction to Ambient (Note 4)   | R <sub>θJA</sub>   | (    | 67.4       | °C/W |

| Power Dissipation (Note 5)                        | PD                 |      | 1.48       | W    |

| Moisture Sensitivity Level (Note 6)               | MSL                |      | 1          | -    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

This device is ESD sensitive. Handling precautions are needed to avoid damage or performance degradation.

Latch up Current per JEDEC standard: JESD78 class II.

3. The thermal shutdown set to 150°C (typical) avoids potential irreversible damage on the device due to power dissipation.

JEDEC standard JESD 51–7 (1S2P Direct-Attach Method) with 0 LFM. It is for checking junction temperature using external measurement.

The maximum power dissipation (PD) is dependent on input voltage, maximum output current and external components selected. Tambient

= 25°C, Tjunc\_max = 125°C, PD = (Tjunc\_max-T\_amb)/Theta JA

6. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

#### **TABLE 3. ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 12 \text{ V}, \text{ typical values are referenced to } T_A = T_J = 25^{\circ}\text{C}$ , Min and Max values are referenced to  $T_A = T_J = -40^{\circ}\text{C}$  to 100°C. unless other noted.)

| Characteristics                         | Test Conditions                                      | Symbol               | MIN  | ТҮР  | MAX | UNITS |

|-----------------------------------------|------------------------------------------------------|----------------------|------|------|-----|-------|

| SUPPLY VOLTAGE                          |                                                      | ·                    | -    |      |     |       |

| VIN Supply Voltage Range                | (Note 7)                                             | V <sub>IN</sub>      | 4.5  | 12   | 20  | V     |

| VCC5V Under-Voltage (UVLO)<br>Threshold | VCC5V falling                                        | V <sub>CCUV-</sub>   | 3.7  |      |     | V     |

| VCC5V OK Threshold                      | VCC5V rising                                         | V <sub>CCOK</sub>    |      |      | 4.3 | V     |

| VCC5V UVLO Hysteresis                   |                                                      | V <sub>CCHYS</sub>   |      | 270  |     | mV    |

| VCC3V Under-Voltage (UVLO)<br>Threshold | VCC3V falling                                        | V <sub>CC3UV</sub> - | 2.6  |      |     | V     |

| VCC3V OK Threshold                      | VCC3V rising                                         | V <sub>CC3OK</sub>   |      |      | 2.9 | V     |

| VCC3V UVLO Hysteresis                   |                                                      | V <sub>CC3HYS</sub>  |      | 135  |     | mV    |

| VCC5V REGULATOR                         |                                                      | ·                    | -    |      |     |       |

| Output Voltage                          | 6V < VIN < 20V,<br>IVCC5V = 15mA (External),EN = Low | V <sub>CC</sub>      | 5.2  | 5.35 | 5.5 | V     |

| Load Regulation                         | IVCC5V = 5mA to 25mA (External),<br>EN = Low         |                      | -2.0 | 0.2  | 2.0 | %     |

| Dropout Voltage                         | VIN = 5V, IVCC5V = 25mA (External),<br>EN = Low      | V <sub>DO_VCC</sub>  |      |      | 200 | mV    |

| VCC3V REGULATOR                         | · · ·                                                | •                    |      |      | •   | J     |

| Output Voltage                          | IVCC3V = 5 mA (External), EN = Low                   | V <sub>3V3</sub>     | 3.1  | 3.3  | 3.5 | V     |

**TABLE 3. ELECTRICAL CHARACTERISTICS** (continued) ( $V_{IN} = 12 V$ , typical values are referenced to  $T_A = T_J = 25^{\circ}C$ , Min and Max values are referenced to  $T_A = T_J = -40^{\circ}C$  to 100°C. unless other noted.)

| Characteristics                       | Test Conditions                                |                                                  | Symbol               | MIN  | TYP      | MAX      | UNITS    |

|---------------------------------------|------------------------------------------------|--------------------------------------------------|----------------------|------|----------|----------|----------|

| VCC3V REGULATOR                       |                                                |                                                  | •                    | 1    | •        |          |          |

| Load Regulation                       | IVCC3V = 0.5 mA to<br>EN = Low                 | IVCC3V = 0.5 mA to 10 mA (External),<br>EN = Low |                      | -3.0 |          | 3.0      | %        |

| SUPPLY CURRENT                        |                                                |                                                  |                      |      |          |          |          |

| VIN Quiescent Current                 | EN high, 1-phase onl<br>EN high, 6-phase       |                                                  |                      | -    | 11<br>17 | 20<br>28 | mA<br>mA |

| VIN Shutdown Current                  | EN low                                         |                                                  | I <sub>sdVIN</sub>   | -    | 5        | 9        | mA       |

| VREF                                  |                                                |                                                  | ·                    |      |          |          |          |

| VREF Output Voltage                   | IVREF = 500 μA                                 |                                                  | V <sub>VREF</sub>    | 594  | 600      | 606      | mV       |

| Load Regulation                       | IVREF = 0 mA to 2 m.                           | A                                                |                      | -1.0 |          | 1.0      | %        |

| REFIN                                 |                                                |                                                  | ·                    |      |          |          |          |

| Maximum REFIN Voltage                 | (Note 7)                                       |                                                  |                      |      |          | 1.53     | V        |

| REFIN Bias Current                    | V <sub>REFIN</sub> = 1.0 V                     |                                                  | I <sub>REFIN</sub>   | -100 |          | 100      | nA       |

| SYSTEM VOLTAGE ACCURACY               |                                                |                                                  | ·                    |      |          |          |          |

| System Voltage Accuracy               | $1.0 \text{ V} < \text{V} \le 1.52 \text{ V}$  | –40°C to 85°C                                    |                      | -7   |          | 7        | mV       |

| $(V = V_{DAC} \text{ or } V_{REFIN})$ |                                                | –40°C to 125°C                                   |                      | -10  |          | 10       |          |

|                                       | $0.7~V \leq V \leq 1.0~V$                      | –40°C to 85°C                                    |                      | -0.5 |          | 0.5      | %        |

|                                       |                                                | –40°C to 125°C                                   |                      | -1.0 |          | 1.0      |          |

|                                       | $0.5 \text{ V} \le \text{V} < 0.7 \text{ V}$   | –40°C to 85°C                                    |                      | -7   |          | 7        | mV       |

|                                       |                                                | –40°C to 125°C                                   |                      | -10  |          | 10       | <u> </u> |

|                                       | $0.25 \text{ V} \leq \text{V} < 0.5 \text{ V}$ | –40°C to 85°C                                    |                      | -8   |          | 8        | mV       |

|                                       |                                                | –40°C to 125°C                                   |                      | -12  |          | 12       |          |

| DIFFERENTIAL VOLTAGE-SENS             | E AMPLIFIER                                    |                                                  |                      |      |          |          |          |

| VSP Input Voltage Range               | (Note 7)                                       |                                                  |                      | -0.2 |          | 1.72     | V        |

| VSN Input Voltage Range               | (Note 7)                                       |                                                  |                      | -0.2 |          | 0.2      | V        |

| DC Gain                               | VSP-VSN = 0 V to 1.                            | 52 V                                             | GAIN_DVA             |      | 1.0      |          | V/V      |

| -3dB Gain Bandwidth                   | CL = 20 pF to GND, F<br>GND (Note 7)           | RL = 10 KΩ to                                    | BW_DVA               |      | 10       |          | MHz      |

| Input Bias Current                    | VSP = 1.72, VSN = -(                           | 0.2 V                                            | I <sub>VS</sub>      | -400 |          | 400      | nA       |

| VOLTAGE ERROR AMPLIFIER               |                                                |                                                  |                      |      |          |          |          |

| Open-Loop DC Gain                     | (Note 7)                                       |                                                  | GAIN <sub>EA</sub>   |      | 80       |          | dB       |

| Unity Gain Bandwidth                  | (Note 7)                                       |                                                  | GBW <sub>EA</sub>    |      | 20       |          | MHz      |

| Slew Rate                             | (Note 7)                                       |                                                  | SR <sub>COMP</sub>   |      | 20       | 1        | V/μs     |

| COMP Voltage Swing                    | I <sub>COMP</sub> (source) = 2 mA              | A                                                | V <sub>maxCOMP</sub> | 3.2  | 3.4      | -        | V        |

|                                       | I <sub>COMP</sub> (sink) = 2 mA                | TRBST is<br>Enabled                              | V <sub>minCOMP</sub> |      |          | 0.3      | V        |

|                                       |                                                | TRBST is<br>Disabled                             |                      | -    | 1.1      |          |          |

| FB Bias Current                       | V <sub>FB</sub> = 1.3V                         | •                                                | I <sub>FB</sub>      | -400 |          | 400      | nA       |

| DIFFERENTIAL CURRENT-SENS             | EAMPLIFIER                                     |                                                  |                      |      |          |          |          |

|                                       |                                                |                                                  |                      | 1    | 1        |          | 1        |

| DC Gain             |          | GAIN <sub>CA</sub> | 6  | V/V |

|---------------------|----------|--------------------|----|-----|

| -3dB Gain Bandwidth | (Note 7) | BW <sub>CA</sub>   | 10 | MHz |

**TABLE 3. ELECTRICAL CHARACTERISTICS** (continued) ( $V_{IN}$  = 12 V, typical values are referenced to  $T_A$  =  $T_J$  = 25°C, Min and Max values are referenced to  $T_A$  =  $T_J$  = -40°C to 100°C. unless other noted.)

| Characteristics                    | Test Conditions                                                                         | Symbol                | MIN  | ТҮР                                                                       | MAX     | UNITS |

|------------------------------------|-----------------------------------------------------------------------------------------|-----------------------|------|---------------------------------------------------------------------------|---------|-------|

| DIFFERENTIAL CURRENT-SENSE AM      | PLIFIER                                                                                 |                       |      |                                                                           | •       |       |

| Input Common Mode Voltage Range    | (Note 7)                                                                                |                       | -0.2 |                                                                           | Vcc+0.1 | V     |

| Differential Input Voltage Range   | (Note 7)                                                                                |                       | -60  | -                                                                         | 60      | mV    |

| Input Bias Current                 | ISP, ISN = 1.0 V                                                                        | I <sub>CS</sub>       | -100 |                                                                           | 100     | nA    |

| CURRENT SUMMING AMPLIFIER          |                                                                                         |                       |      |                                                                           |         |       |

| DC Gain                            | From (ISPn – ISNn) to (CSSUM – Vbias)                                                   | GAIN <sub>CSSUM</sub> |      | -2                                                                        |         | V/V   |

| -3dB Gain Bandwidth                | $CL = 10 \text{ pF to GND}, \text{ RL} = 10 \text{ k}\Omega \text{ to GND}$<br>(Note 7) | BW <sub>CSSUM</sub>   |      | 5                                                                         |         | MHz   |

| CSSUM Output Offset                | All (ISPn – ISNn) = 0 V (Note 7)                                                        | V <sub>osCSSUM</sub>  | -7   | 0                                                                         | 7       | mV    |

| Maximum CSSUM Output Voltage       | I <sub>CSSUM</sub> (source) = 1 mA (Note 7)                                             |                       |      | 2.02                                                                      |         | V     |

| Minimum CSSUM Output Voltage       | I <sub>CSSUM</sub> (sink) = 1 mA (Note 7)                                               |                       |      | 0.56                                                                      |         | V     |

| DROOP AMPLIFIER                    |                                                                                         |                       |      |                                                                           |         |       |

| Open-Loop DC Gain                  | (Note 7)                                                                                | GAIN <sub>DA</sub>    |      | 80                                                                        |         | dB    |

| Unity Gain Bandwidth               | (Note 7)                                                                                | GBW <sub>DA</sub>     |      | 10                                                                        |         | MHz   |

| Input Offset Voltage               | (Note 7)                                                                                | V <sub>osDA</sub>     | -2.5 |                                                                           | 2.5     | mV    |

| Input Bias Current                 | V <sub>DFB</sub> = 1.3V                                                                 | I <sub>DFB</sub>      | -200 |                                                                           | 200     | nA    |

| Maximum VDRP Output Voltage        | I <sub>VDRP</sub> (source) = 2 mA (Note 7)                                              |                       |      | 3.0                                                                       |         | V     |

| Minimum VDRP Output Voltage        | I <sub>VDRP</sub> (sink) = 2 mA (Note 7)                                                |                       |      | 1.0                                                                       |         | V     |

| IMON AMPLIFIER                     |                                                                                         |                       |      |                                                                           |         |       |

| DC Gain                            |                                                                                         | GAIN <sub>IMON</sub>  |      | 10                                                                        |         | V/V   |

| -3dB Gain Bandwidth                | (Note 7)                                                                                | BWIMON                |      | 2                                                                         |         | MHz   |

| Input Offset Voltage               | (Note 7)                                                                                | V <sub>osIMON</sub>   | -2   |                                                                           | 2       | mV    |

| Output Impedance                   | (Note 7)                                                                                | R <sub>IMON</sub>     |      | 20                                                                        |         | kΩ    |

| IMAX                               |                                                                                         |                       |      |                                                                           |         |       |

| SourceCurrent                      | VIMAX = 1V                                                                              |                       | 47.5 | 50                                                                        | 52.5    | μA    |

| I <sup>2</sup> C INTERFACE ADDRESS |                                                                                         |                       |      |                                                                           |         |       |

| Address                            | Float<br>Short to GND<br>2.7k<br>5.1k<br>8.2k<br>13k<br>20k<br>33k                      | -                     | _    | 1110000<br>1110001<br>1110010<br>1110011<br>1110100<br>1110101<br>1110110 |         | -     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

**TABLE 3. ELECTRICAL CHARACTERISTICS** (continued) ( $V_{IN} = 12 V$ , typical values are referenced to  $T_A = T_J = 25^{\circ}C$ , Min and Max values are referenced to  $T_A = T_J = -40^{\circ}C$  to 100°C. unless other noted.)

| Characteristics      | Test Conditions                                                          | Symbol           | MIN                                                   | ТҮР                                                                          | MAX                                                    | UNITS |

|----------------------|--------------------------------------------------------------------------|------------------|-------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------|-------|

| VBOOT CODE           |                                                                          |                  |                                                       |                                                                              |                                                        |       |

| VBOOT1               | Float<br>Short to GND<br>2.7 k<br>5.1 k<br>8.2 k<br>13 k<br>20 k<br>33 k | _                | _                                                     | 000XXX<br>001XXX<br>010XXX<br>011XXX<br>100XXX<br>101XXX<br>110XXX<br>111XXX | _                                                      | -     |

| VBOOT2               | Float<br>Short to GND<br>2.7 k<br>5.1 k<br>8.2 k<br>13 k<br>20 k<br>33 k | _                | -                                                     | XXX000<br>XXX01<br>XXX010<br>XXX011<br>XXX100<br>XXX101<br>XXX110<br>XXX111  | _                                                      | -     |

| Source Current       |                                                                          | I <sub>VBT</sub> | 45                                                    | 50                                                                           | 55                                                     | μA    |

| SWITCHING FREQUENCY  |                                                                          |                  |                                                       |                                                                              |                                                        |       |

| Switching Frequency  | 2.7 k<br>5.1 k<br>Float<br>8.2 k<br>Short to GND<br>13 k<br>20 k<br>33 k | Fsw              | 180<br>270<br>360<br>450<br>540<br>720<br>900<br>1080 | 200<br>300<br>400<br>500<br>600<br>800<br>1000<br>1200                       | 220<br>330<br>440<br>550<br>660<br>880<br>1100<br>1320 | kHz   |

| Source Current       |                                                                          | I <sub>FS</sub>  | 45                                                    | 50                                                                           | 55                                                     | μA    |

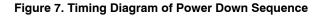

| SYSTEM RESET TIME    |                                                                          |                  |                                                       |                                                                              |                                                        |       |

| System Reset Time    | Measured from EN to start of soft start.                                 | T <sub>RST</sub> |                                                       | 2.0                                                                          |                                                        | ms    |

| SOFT START           |                                                                          |                  |                                                       |                                                                              |                                                        |       |

| Soft-Start Slew Rate | Float                                                                    | SSSR             |                                                       | 0.125                                                                        |                                                        | mV/us |

|                      | 33 k                                                                     |                  |                                                       | 0.25                                                                         |                                                        |       |

|                      | 20 k                                                                     |                  |                                                       | 0.5                                                                          |                                                        |       |

|                      | 13 k                                                                     |                  |                                                       | 1.0                                                                          |                                                        |       |

|                      | 8.2 k                                                                    |                  |                                                       | 2.0                                                                          |                                                        |       |

|                      | 5.1 k                                                                    |                  |                                                       | 4.0                                                                          |                                                        |       |

|                      | 2.7 k                                                                    |                  |                                                       | 8.0                                                                          |                                                        |       |

|                      | Short to GND                                                             |                  |                                                       | 16                                                                           |                                                        |       |

| Source Current       |                                                                          | I <sub>SS</sub>  | 45                                                    | 50                                                                           | 55                                                     | μA    |

| DVID                 |                                                                          | -                |                                                       |                                                                              | T                                                      |       |

| DVID Slew Rate       | 000                                                                      | SR               |                                                       | 0.125                                                                        |                                                        | mV/us |

|                      | 001                                                                      |                  |                                                       | 0.25                                                                         |                                                        |       |

|                      | 010                                                                      |                  |                                                       | 0.5                                                                          |                                                        |       |

|                      | 011                                                                      |                  |                                                       | 1.0                                                                          |                                                        |       |

|                      | 011                                                                      |                  |                                                       |                                                                              | 1                                                      |       |

|                      | 100                                                                      | -                |                                                       | 2.0                                                                          |                                                        |       |

|                      |                                                                          | -                |                                                       | 2.0<br>4.0                                                                   |                                                        |       |

|                      | 100                                                                      | -                |                                                       |                                                                              |                                                        |       |

|  | Logic High Input Voltage | Vih(sda, s | L) 1.5 |  |  | V | I |

|--|--------------------------|------------|--------|--|--|---|---|

|--|--------------------------|------------|--------|--|--|---|---|

**TABLE 3. ELECTRICAL CHARACTERISTICS** (continued) ( $V_{IN} = 12 V$ , typical values are referenced to  $T_A = T_J = 25^{\circ}C$ , Min and Max values are referenced to  $T_A = T_J = -40^{\circ}C$  to 100°C. unless other noted.)

| Characteristics                                      | Test Conditions                         |                  | Symbol                | MIN  | TYP      | MAX | UNITS |

|------------------------------------------------------|-----------------------------------------|------------------|-----------------------|------|----------|-----|-------|

| I <sup>2</sup> C INTERFACE                           |                                         |                  |                       |      |          |     |       |

| Logic Low Input Voltage                              |                                         |                  | VIL(SDA, SCL)         |      |          | 0.7 | V     |

| Hysteresis                                           |                                         |                  |                       |      | 350      |     | mV    |

| SDA Output Low Voltage                               | ISDA = -4 mA                            |                  | Vol                   |      |          | 0.3 | V     |

| Input Current                                        |                                         |                  | lih; li∟              | -1.0 |          | 1.0 | μA    |

| Input Capacitance                                    | (Note 7)                                |                  | CSCL, SDA             |      | 5.0      |     | pF    |

| Clock Frequency                                      | (Note 7)                                |                  | fscl                  |      |          | 400 | kHz   |

| SCL Falling Edge to SDA Valid Time                   | (Note 7)                                |                  |                       |      |          | 1.0 | μs    |

| ALERT# Low Voltage                                   | I <sub>ALERT</sub> = -4 mA              |                  | V <sub>LALERT</sub>   |      |          | 0.3 | V     |

| ALERT# Leakage Current                               | ALERT# = 5 V                            |                  | I <sub>lkgALERT</sub> |      |          | 1.0 | μA    |

| PGOOD                                                |                                         |                  |                       |      |          |     |       |

| PGOOD Startup Delay                                  | Measured from end<br>PGOOD assertion (N |                  | T <sub>d_PGOOD</sub>  |      | 100      |     | μs    |

| PGOOD Shutdown Delay                                 | Measured from EN to<br>de-assertion     | o PGOOD          |                       |      | 250      |     | ns    |

| PGOOD Low Voltage                                    | I <sub>PGOOD</sub> = -4 mA              |                  | V <sub>IPGOOD</sub>   |      |          | 0.3 | V     |

| PGOOD Leakage Current                                | PGOOD = 5 V                             |                  | I <sub>lkgPGOOD</sub> |      |          | 1.0 | μA    |

| PROTECTIONS                                          | 1                                       |                  |                       |      |          |     |       |

| Current Limit Threshold                              | Measured from                           | ISP-ISN = 50 mV  | V <sub>OCTH</sub>     | 285  | 300      | 315 | mV    |

|                                                      | ILIMT to GND                            | ISP-ISN = 2 0 mV |                       | 110  | 120      | 130 |       |

| Over Current Protection (OCP)<br>Debounce Time       | (Note 7)                                |                  |                       |      | 8 Cycles |     | us    |

| Under Voltage Threshold Below DAC                    | VSP falling                             |                  | V <sub>UVTH</sub>     | 250  | 300      | 350 | mV    |

| Under Voltage Protection (UVP)<br>Hysteresis         |                                         |                  | V <sub>UVHYS</sub>    |      | 25       |     | mV    |

| Under-voltage Debounce Time                          | (Note 7)                                |                  |                       |      | 5        |     | μs    |

| Shutdown Time in Hiccup Mode                         | UVP (Note 7)                            |                  |                       |      | 30       |     | ms    |

|                                                      | OCP (Note 7)                            |                  |                       |      | 40       |     |       |

|                                                      | OTP (Note 7)                            |                  |                       |      | 20       |     |       |

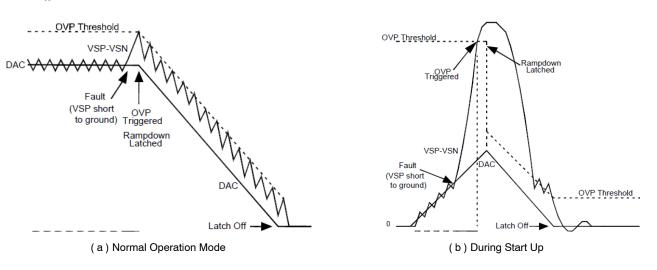

| Absolute Over Voltage Threshold During<br>Soft-Start | VSP-GND                                 |                  |                       | 2.0  | 2.1      | 2.2 | V     |

| Absolute Over Voltage Threshold<br>Hysteresis        |                                         |                  |                       |      | -25      |     | mV    |

| Over Voltage Threshold Above DAC                     | VSP rising                              |                  | V <sub>OVTH</sub>     | 175  | 200      | 225 | mV    |

| Over Voltage Protection Hysteresis                   | VSP falling                             |                  | V <sub>OVHYS</sub>    |      | -25      |     | mV    |

| Over Voltage Debounce Time                           | VSP rising to GH low                    | v                |                       |      | 1.0      |     | us    |

| Offset Voltage of OTP Comparator                     | VILMT = 200 mV                          |                  | V <sub>OS_OTP</sub>   | -2   |          | 2   | mV    |

| OTP Source Current                                   |                                         |                  | I <sub>OTP</sub>      | 9    | 10       | 11  | μA    |

| OTP Debounce Time                                    | (Note 7)                                |                  |                       |      | 140      |     | ns    |

| Thermal Shutdown (TSD) Threshold                     | (Note 7)                                |                  | T <sub>sd</sub>       | 140  | 150      |     | °C    |

| Recovery Temperature Threshold                       | (Note 7)                                |                  | T <sub>rec</sub>      |      | 125      |     | °C    |

|                                                      | (Note 7)<br>(Note 7)                    |                  |                       | 1    | 120      | 1   | ns    |

**TABLE 3. ELECTRICAL CHARACTERISTICS** (continued) ( $V_{IN}$  = 12 V, typical values are referenced to  $T_A$  =  $T_J$  = 25°C, Min and Max values are referenced to  $T_A$  =  $T_J$  = -40°C to 100°C. unless other noted.)

| Characteristics                 | Test Conditions                                                    | Symbol                 | MIN                     | TYP | MAX  | UNITS |

|---------------------------------|--------------------------------------------------------------------|------------------------|-------------------------|-----|------|-------|

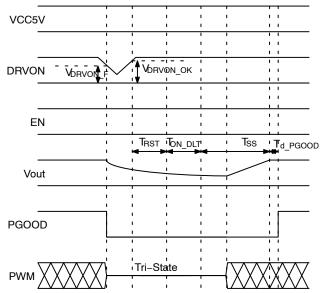

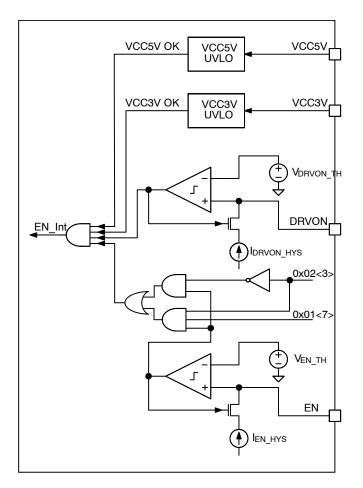

| ENABLE                          | -                                                                  |                        |                         |     |      |       |

| EN Operation Voltage Range      |                                                                    |                        | 0                       |     | 3.5  | V     |

| EN ON Threshold                 |                                                                    | V <sub>EN_TH</sub>     | 0.7                     | 0.8 | 0.85 | V     |

| Hysteresis Source Current       | VCC5V is OK                                                        | I <sub>EN_HYS</sub>    | 25                      | 30  | 35   | μA    |

| DRVON                           |                                                                    |                        |                         |     |      |       |

| DRVON Operation Voltage Range   |                                                                    |                        | 0                       |     | 2.0  | V     |

| DRVON ON Threshold              |                                                                    | V <sub>DRVON_TH</sub>  | 0.75                    | 0.8 | 0.85 | V     |

| Hysteresis Source Current       | VCC5V is OK                                                        | I <sub>DRVON_HYS</sub> | 25                      | 30  | 35   | μA    |

| VB_RST# and PSI                 |                                                                    |                        |                         |     |      |       |

| High Threshold                  |                                                                    | V <sub>highRST</sub>   | 1.5                     | -   | -    | V     |

| Low Threshold                   |                                                                    | VlowRST                | -                       | _   | 0.7  | V     |

| Hysteresis                      |                                                                    | V <sub>hysRST</sub>    |                         | 350 |      | mV    |

| Input Bias Current              | External 1 K pull-up to 3.3 V                                      | I <sub>biasRST</sub>   | -                       | -   | 1.0  | μA    |

| PWM MODULATION                  |                                                                    |                        |                         |     |      |       |

| Minimum On Time                 | (Note 7)                                                           | T <sub>on_min</sub>    |                         |     | 50   | ns    |

| Minimum Off Time                | (Note 7)                                                           | T <sub>off_min</sub>   | 160                     |     |      | ns    |

| 0% Duty Cycle                   | COMP voltage when the PWM outputs remain Lo (Note 7)               |                        |                         | 1.3 |      | V     |

| 100% Duty Cycle                 | COMP voltage when the PWM outputs remain HI, Vin = 12.0 V (Note 7) |                        |                         | 2.5 |      | V     |

| Ramp Feed-forward Voltage Range | (Note 7)                                                           |                        | 4.5                     |     | 20   | V     |

| PWM OUTPUT                      |                                                                    |                        |                         |     |      |       |

| PWM Output High Voltage         | Isource = 0.5 mA                                                   | V <sub>PWM_H</sub>     | V <sub>CC</sub><br>-0.2 |     |      | V     |

| PWM Output Low Voltage          | lsink = 0.5 mA                                                     | V <sub>PWM_L</sub>     |                         |     | 0.2  | V     |

| Rise and Fall Times             | CL (PCB) = 50 pF, measured between<br>10% & 90% of Vcc (Note 7)    |                        |                         | 10  |      | ns    |

| Leakage Current in Hi-Z Stage   |                                                                    | I <sub>LK_PWM</sub>    | -1.0                    |     | 1.0  | μA    |

7. Guaranteed by design, not tested in production.

# **Table 4. RESISTOR OPTIONS FOR FUNCTION PROGRAMMING**

| Res   | sistance Range ( | kΩ)   | Resistor Options (kΩ) |      |      |      |      |  |  |  |  |

|-------|------------------|-------|-----------------------|------|------|------|------|--|--|--|--|

| MIN   | ТҮР              | МАХ   | ±5%                   |      | ±1   | %    |      |  |  |  |  |

| 2.565 | 2.7              | 2.835 | 2.7                   | 2.61 | 2.67 | 2.74 | 2.80 |  |  |  |  |

| 4.845 | 5.1              | 5.355 | 5.1                   | 4.87 | 4.99 | 5.11 | 5.23 |  |  |  |  |

| 7.79  | 8.2              | 8.61  | 8.2                   | 7.87 | 8.06 | 8.25 | 8.45 |  |  |  |  |

| 12.35 | 13               | 13.65 | 13                    | 12.4 | 12.7 | 13   | 13.3 |  |  |  |  |

| 19    | 20               | 21    | 20                    | 19.1 | 19.6 | 20   | 20.5 |  |  |  |  |

| 31.35 | 33               | 34.65 | 33                    | 31.6 | 32.4 | 33.2 | 34   |  |  |  |  |

# TABLE 5. VBOOT CODES

| V | воот |   | v v | воот | 2 | Voltage(V) | HEX | v | воот | 1 | \<br>\ | воот | 2 | Voltage(V) | HEX |

|---|------|---|-----|------|---|------------|-----|---|------|---|--------|------|---|------------|-----|

| 0 | 0    | 0 | 0   | 0    | 0 | 0.6        | 00  | 1 | 0    | 0 | 0      | 0    | 0 | 0.92       | 20  |

| 0 | 0    | 0 | 0   | 0    | 1 | 0.61       | 01  | 1 | 0    | 0 | 0      | 0    | 1 | 0.93       | 21  |

| 0 | 0    | 0 | 0   | 1    | 0 | 0.62       | 02  | 1 | 0    | 0 | 0      | 1    | 0 | 0.94       | 22  |

| 0 | 0    | 0 | 0   | 1    | 1 | 0.63       | 03  | 1 | 0    | 0 | 0      | 1    | 1 | 0.95       | 23  |

| 0 | 0    | 0 | 1   | 0    | 0 | 0.64       | 04  | 1 | 0    | 0 | 1      | 0    | 0 | 0.96       | 24  |

| 0 | 0    | 0 | 1   | 0    | 1 | 0.65       | 05  | 1 | 0    | 0 | 1      | 0    | 1 | 0.97       | 25  |

| 0 | 0    | 0 | 1   | 1    | 0 | 0.66       | 06  | 1 | 0    | 0 | 1      | 1    | 0 | 0.98       | 26  |

| 0 | 0    | 0 | 1   | 1    | 1 | 0.67       | 07  | 1 | 0    | 0 | 1      | 1    | 1 | 0.99       | 27  |

| 0 | 0    | 1 | 0   | 0    | 0 | 0.68       | 08  | 1 | 0    | 1 | 0      | 0    | 0 | 1          | 28  |

| 0 | 0    | 1 | 0   | 0    | 1 | 0.69       | 09  | 1 | 0    | 1 | 0      | 0    | 1 | 1.01       | 29  |

| 0 | 0    | 1 | 0   | 1    | 0 | 0.7        | 0A  | 1 | 0    | 1 | 0      | 1    | 0 | 1.02       | 2A  |

| 0 | 0    | 1 | 0   | 1    | 1 | 0.71       | 0B  | 1 | 0    | 1 | 0      | 1    | 1 | 1.03       | 2B  |

| 0 | 0    | 1 | 1   | 0    | 0 | 0.72       | 0C  | 1 | 0    | 1 | 1      | 0    | 0 | 1.04       | 2C  |

| 0 | 0    | 1 | 1   | 0    | 1 | 0.73       | 0D  | 1 | 0    | 1 | 1      | 0    | 1 | 1.05       | 2D  |

| 0 | 0    | 1 | 1   | 1    | 0 | 0.74       | 0E  | 1 | 0    | 1 | 1      | 1    | 0 | 1.06       | 2E  |

| 0 | 0    | 1 | 1   | 1    | 1 | 0.75       | 0F  | 1 | 0    | 1 | 1      | 1    | 1 | 1.07       | 2F  |

| 0 | 1    | 0 | 0   | 0    | 0 | 0.76       | 10  | 1 | 1    | 0 | 0      | 0    | 0 | 1.08       | 30  |

| 0 | 1    | 0 | 0   | 0    | 1 | 0.77       | 11  | 1 | 1    | 0 | 0      | 0    | 1 | 1.09       | 31  |

| 0 | 1    | 0 | 0   | 1    | 0 | 0.78       | 12  | 1 | 1    | 0 | 0      | 1    | 0 | 1.1        | 32  |

| 0 | 1    | 0 | 0   | 1    | 1 | 0.79       | 13  | 1 | 1    | 0 | 0      | 1    | 1 | 1.11       | 33  |

| 0 | 1    | 0 | 1   | 0    | 0 | 0.8        | 14  | 1 | 1    | 0 | 1      | 0    | 0 | 1.12       | 34  |

| 0 | 1    | 0 | 1   | 0    | 1 | 0.81       | 15  | 1 | 1    | 0 | 1      | 0    | 1 | 1.13       | 35  |

| 0 | 1    | 0 | 1   | 1    | 0 | 0.82       | 16  | 1 | 1    | 0 | 1      | 1    | 0 | 1.14       | 36  |

| 0 | 1    | 0 | 1   | 1    | 1 | 0.83       | 17  | 1 | 1    | 0 | 1      | 1    | 1 | 1.15       | 37  |

| 0 | 1    | 1 | 0   | 0    | 0 | 0.84       | 18  | 1 | 1    | 1 | 0      | 0    | 0 | 1.16       | 38  |

| 0 | 1    | 1 | 0   | 0    | 1 | 0.85       | 19  | 1 | 1    | 1 | 0      | 0    | 1 | 1.17       | 39  |

| 0 | 1    | 1 | 0   | 1    | 0 | 0.86       | 1A  | 1 | 1    | 1 | 0      | 1    | 0 | 1.18       | ЗA  |

| 0 | 1    | 1 | 0   | 1    | 1 | 0.87       | 1B  | 1 | 1    | 1 | 0      | 1    | 1 | 1.19       | 3B  |

| 0 | 1    | 1 | 1   | 0    | 0 | 0.88       | 1C  | 1 | 1    | 1 | 1      | 0    | 0 | 1.2        | 3C  |

| 0 | 1    | 1 | 1   | 0    | 1 | 0.89       | 1D  | 1 | 1    | 1 | 1      | 0    | 1 | 1.21       | 3D  |

| 0 | 1    | 1 | 1   | 1    | 0 | 0.9        | 1E  | 1 | 1    | 1 | 1      | 1    | 0 | 1.22       | 3E  |

| 0 | 1    | 1 | 1   | 1    | 1 | 0.91       | 1F  | 1 | 1    | 1 | 1      | 1    | 1 | 1.23       | ЗF  |

# TABLE 6. VID CODES

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage (V) | HEX |

|------|------|------|------|------|------|------|------|-------------|-----|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | OFF         | 00  |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0.25000     | 01  |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0.25500     | 02  |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0.26000     | 03  |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0.26500     | 04  |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0.27000     | 05  |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0.27500     | 06  |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0.28000     | 07  |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0.28500     | 08  |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0.29000     | 09  |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0.29500     | 0A  |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0.30000     | 0B  |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0.30500     | 0C  |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0.31000     | 0D  |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0.31500     | 0E  |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0.32000     | 0F  |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0.32500     | 10  |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0.33000     | 11  |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0.33500     | 12  |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0.34000     | 13  |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0.34500     | 14  |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0.35000     | 15  |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0.35500     | 16  |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0.36000     | 17  |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0.36500     | 18  |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0.37000     | 19  |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0.37500     | 1A  |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0.38000     | 1B  |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0.38500     | 1C  |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0.39000     | 1D  |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0.39500     | 1E  |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0.40000     | 1F  |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0.40500     | 20  |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0.41000     | 21  |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage (V) | HEX |

|------|------|------|------|------|------|------|------|-------------|-----|

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0.41500     | 22  |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0.42000     | 23  |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0.42500     | 24  |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0.43000     | 25  |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0.43500     | 26  |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0.44000     | 27  |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0.44500     | 28  |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0.45000     | 29  |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0.45500     | 2A  |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0.46000     | 2B  |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0.46500     | 2C  |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0.47000     | 2D  |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0.47500     | 2E  |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0.48000     | 2F  |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0.48500     | 30  |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0.49000     | 31  |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0.49500     | 32  |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0.50000     | 33  |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0.50500     | 34  |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0.51000     | 35  |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0.51500     | 36  |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0.52000     | 37  |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0.52500     | 38  |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0.53000     | 39  |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0.53500     | ЗA  |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0.54000     | 3B  |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0.54500     | ЗC  |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0.55000     | 3D  |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0.55500     | 3E  |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0.56000     | 3F  |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0.56500     | 40  |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0.57000     | 41  |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 0.57500     | 42  |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 0.58000     | 43  |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage (V) | HEX |

|------|------|------|------|------|------|------|------|-------------|-----|

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0.58500     | 44  |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1    | 0.59000     | 45  |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 0.59500     | 46  |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 0.60000     | 47  |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0.60500     | 48  |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 0.61000     | 49  |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 0.61500     | 4A  |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1    | 0.62000     | 4B  |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0.62500     | 4C  |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1    | 0.63000     | 4D  |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0    | 0.63500     | 4E  |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 0.64000     | 4F  |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0.64500     | 50  |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0.65000     | 51  |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 0.65500     | 52  |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 0.66000     | 53  |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 0.66500     | 54  |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 0.67000     | 55  |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 0.67500     | 56  |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | 0.68000     | 57  |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0    | 0.68500     | 58  |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1    | 0.69000     | 59  |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | 0.69500     | 5A  |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | 0.70000     | 5B  |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0    | 0.70500     | 5C  |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1    | 0.71000     | 5D  |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0    | 0.71500     | 5E  |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 0.72000     | 5F  |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0.72500     | 60  |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 0.73000     | 61  |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | 0.73500     | 62  |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0.74000     | 63  |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0.74500     | 64  |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 0.75000     | 65  |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage (V) | HEX |

|------|------|------|------|------|------|------|------|-------------|-----|

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0.75500     | 66  |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 0.76000     | 67  |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 0.76500     | 68  |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 0.77000     | 69  |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 0.77500     | 6A  |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 0.78000     | 6B  |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0.78500     | 6C  |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1    | 0.79000     | 6D  |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0    | 0.79500     | 6E  |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 0.80000     | 6F  |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0.80500     | 70  |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1    | 0.81000     | 71  |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0    | 0.81500     | 72  |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 0.82000     | 73  |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 0.82500     | 74  |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 0.83000     | 75  |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 0.83500     | 76  |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 0.84000     | 77  |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0.84500     | 78  |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 0.85000     | 79  |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 0.85500     | 7A  |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0.86000     | 7B  |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0.86500     | 7C  |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0.87000     | 7D  |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0.87500     | 7E  |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0.88000     | 7F  |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0.88500     | 80  |

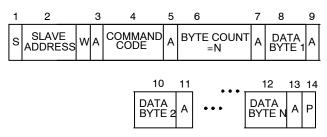

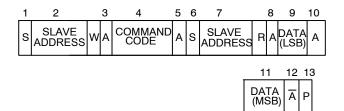

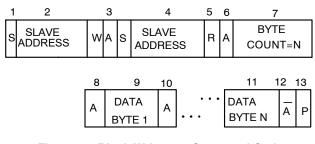

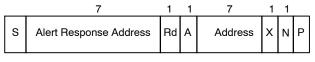

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0.89000     | 81  |