# Operational Amplifiers, High Slew Rate, Low Voltage, Rail-to-Rail Output

The NCS2003 family of op amps features high slew rate, low voltage operation with rail-to-rail output drive capability. The 1.8 V operation allows high performance operation in low voltage, low power applications. The fast slew rate and wide unity-gain bandwidth (5 MHz at 1.8 V) make these op amps suited for high speed applications. The low input offset voltage (4 mV max) allows the op amp to be used for current shunt monitoring. Additional features include no output phase reversal with overdriven inputs and ultra low input bias current of 1 pA.

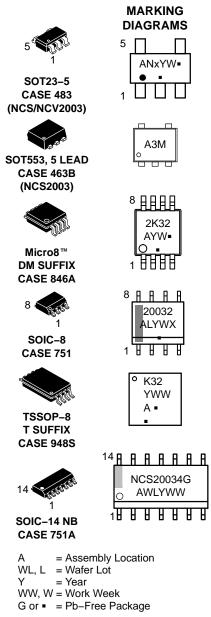

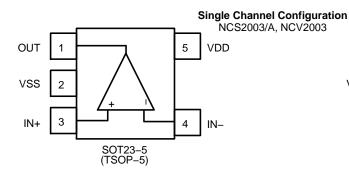

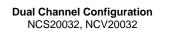

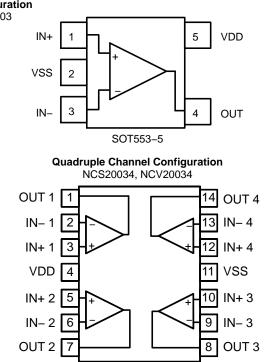

The NCS2003 family is the ideal solution for a wide range of applications and products. The single channel NCS2003, dual channel NCS20032, and quad channel NCS20034 are available in a variety of compact and space–saving packages. The NCV prefix denotes that the device is AEC–Q100 Qualified and PPAP Capable.

#### Features

- Unity Gain Bandwidth: 7 MHz at  $V_S = 5 V$

- Fast Slew Rate: 8 V/ $\mu$ s rising, 12.5 V/ $\mu$ s falling at V<sub>S</sub> = 5 V

- Rail-to-Rail Output

- No Output Phase Reversal for Over–Driven Input Signals

- Low Offset Voltage: 0.5 mV typical

- Low Input Bias Current: 1 pA typical

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP Capable

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### Applications

- Current Shunt Monitor

- Signal Conditioning

- Active Filter

- Sensor Buffer

#### **End Products**

- Motor Control Drives

- Hard Drives

- Medical Devices

- White Goods and Air Conditioners

# **ON Semiconductor®**

www.onsemi.com

(Note: Microdot may be in either location)

#### ORDERING INFORMATION

See detailed ordering, marking and shipping information on page 2 of this data sheet.

**Figure 1. Pin Connections**

### ORDERING INFORMATION

| Device          | Configuration | Automotive | Marking   | Package               | Shipping <sup>†</sup> |

|-----------------|---------------|------------|-----------|-----------------------|-----------------------|

| NCS2003SN2T1G   | Single        | No         | AN3       | SOT23–5<br>(Pb–Free)  | 3000 / Tape and Reel  |

| NCS2003ASN2T1G  |               | No         | AN4       | SOT23–5<br>(Pb–Free)  | 3000 / Tape and Reel  |

| NCS2003XV53T2G  |               | No         | A3        | SOT553–5<br>(Pb–Free) | 4000 /Tape and Reel   |

| NCV2003SN2T1G*  |               | Yes        | AN3       | SOT23–5<br>(Pb–Free)  | 3000 / Tape and Reel  |

| NCS20032DMR2G   | Dual          | No         | 2K32      | Micro8<br>(Pb–Free)   | 4000 / Tape and Reel  |

| NCS20032DR2G    |               |            | 20032     | SOIC-8<br>(Pb-Free)   | 2500 / Tape and Reel  |

| NCS20032DTBR2G  |               |            | K32       | TSSOP-8<br>(Pb-Free)  | 3000 / Tape and Reel  |

| NCV20032DMR2G*  |               | Yes        | 2K32      | Micro8<br>(Pb–Free)   | 4000 / Tape and Reel  |

| NCV20032DR2G*   |               |            | 20032     | SOIC-8<br>(Pb-Free)   | 2500 / Tape and Reel  |

| NCV20032DTBR2G* |               |            | K32       | TSSOP-8<br>(Pb-Free)  | 3000 / Tape and Reel  |

| NCS20034DR2G    | Quad          | No         | NCS20034G | SOIC-14<br>(Pb-Free)  | 2500 / Tape and Reel  |

| NCV20034DR2G*   |               | Yes        | NCS20034G | SOIC-14<br>(Pb-Free)  | 2500 / Tape and Reel  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP Capable.

#### ABSOLUTE MAXIMUM RATINGS

Over operating free-air temperature, unless otherwise stated

| Parameter                                           | Symbol           | Limit                 | Unit |

|-----------------------------------------------------|------------------|-----------------------|------|

| Supply Voltage (V <sub>DD</sub> – V <sub>SS</sub> ) | V <sub>S</sub>   | 7.0                   | V    |

| INPUT AND OUTPUT PINS                               | · · · ·          |                       |      |

| Input Voltage (Note 1)                              | V <sub>IN</sub>  | $V_{SS}$ – 0.3 to 7.0 | V    |

| Input Current                                       | I <sub>IN</sub>  | 10                    | mA   |

| Output Short Current (Note 2)                       | ۱ <sub>۵</sub>   | 100                   | mA   |

| TEMPERATURE                                         |                  |                       |      |

| Storage Temperature                                 | T <sub>STG</sub> | -65 to 150            | °C   |

| Junction Temperature                                | TJ               | 150                   | °C   |

| ESD RATINGS (Note 3)                                | · · ·            |                       |      |

| Human Body Model     | NCx2003, A<br>NCx20032<br>NCx20034 | НВМ | 3000<br>2000<br>3000 | V |

|----------------------|------------------------------------|-----|----------------------|---|

| Machine Model        | NCx2003, A<br>NCx20032<br>NCx20034 | MM  | 200<br>100<br>150    | V |

| Charged Device Model | NCx2003, A<br>NCx2003x             | CDM | 1000<br>2000         | V |

#### OTHER PARAMETERS

| Moisture Sensitivity Level (Note 5) | MSL             | Level 1 |    |

|-------------------------------------|-----------------|---------|----|

| Latch-up Current (Note 4)           | I <sub>LU</sub> | 100     | mA |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Neither input should exceed the range of V<sub>SS</sub> – 300 mV to 7.0 V. This device contains internal protection diodes between the input pins and V<sub>DD</sub>. When V<sub>IN</sub> exceeds V<sub>DD</sub>, the input current should be limited to the specified value.

2. Indefinite duration; however, maximum package power dissipation limits must be observed to ensure that the maximum junction temperature is not exceeded.

3. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 and JESD22-A114 ESD Machine Model tested per AEC-Q100-003 and JESD22-A115

ESD Machine Model tested per AEC-Q100-003 and JESD22-A115 ESD Charged Device Model tested per AEC-Q100-011 and ANSI/ESD S5.3.1-2009

4. Latch-up current tested per JEDEC Standard JESD78.

5. Moisture Sensitivity Level tested per IPC/JEDEC standard J-STD-020A.

#### THERMAL INFORMATION

| Thermal Metric      | Symbol        | Package        | Single Layer Board (Note 6) | Multi Layer Board (Note 7) | Unit  |

|---------------------|---------------|----------------|-----------------------------|----------------------------|-------|

|                     |               | SOT23-5/TSOP-5 | 408                         | 355                        |       |

|                     |               | SOT553-5       | 428                         | 406                        |       |

| Junction to Ambient | 0             | Micro8/MSOP8   | 235                         | 163                        | 00000 |

| Thermal Resistance  | $\theta_{JA}$ | SOIC-8         | 240                         | 179                        | °C/W  |

|                     |               | TSSOP-8        | 300                         | 238                        |       |

|                     |               | SOIC-14        | 167                         | 123                        |       |

6. Values based on a 1S standard PCB according to JEDEC51–3 with 1.0 oz copper and a 300 mm<sup>2</sup> copper area

7. Values based on a 1S2P standard PCB according to JEDEC51-7 with 1.0 oz copper and a 100 mm<sup>2</sup> copper area

#### RECOMMENDED OPERATING CONDITIONS

| Paramete                                                      | Parameter                                 |                 | Min             | Max                  | Unit |

|---------------------------------------------------------------|-------------------------------------------|-----------------|-----------------|----------------------|------|

| Operating Supply Voltage (V <sub>DD</sub> – V <sub>SS</sub> ) |                                           | V <sub>S</sub>  | 1.7             | 5.5                  | V    |

| Specified Operating Range                                     | NCS2003, A<br>NCV2003, NCx20032, NCx20034 | T <sub>A</sub>  | -40<br>-40      | +85<br>+125          | °C   |

| Input Common Mode Range                                       |                                           | V <sub>CM</sub> | V <sub>SS</sub> | V <sub>DD</sub> -0.6 | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### ELECTRICAL CHARACTERISTICS: V<sub>S</sub> = +1.8 V

At  $T_A = +25^{\circ}$ C,  $R_L = 10 \text{ k}\Omega$  connected to midsupply,  $V_{CM} = V_{OUT}$  = midsupply, unless otherwise noted. **Boldface** limits apply over the specified temperature range. Guaranteed by design and/or characterization.

| Parameter             | Symbol                     | Conditions                                                           | Min | Тур | Max | Unit  |

|-----------------------|----------------------------|----------------------------------------------------------------------|-----|-----|-----|-------|

| INPUT CHARACTERISTICS |                            |                                                                      | ·   |     |     |       |

| Input Offset Voltage  | V <sub>OS</sub>            | NCS2003A                                                             |     | 0.5 | 3.0 | mV    |

|                       |                            | NCx2003, NCx20032, NCx20034                                          |     | 0.5 | 4.0 | mV    |

|                       |                            |                                                                      |     |     | 5.0 | mV    |

| Offset Voltage Drift  | $\Delta V_{OS} / \Delta T$ |                                                                      |     | 2.0 |     | μV/°C |

|                       |                            | NCS2003A (Note 8)                                                    |     |     | 6.0 | μV/°C |

| Input Bias Current    | I <sub>IB</sub>            |                                                                      |     | 1   |     | pА    |

| Input Offset Current  | I <sub>OS</sub>            |                                                                      |     | 1   |     | pА    |

| Channel Separation    | XTLK                       | DC, NCx20032, NCx20034                                               |     | 100 |     | dB    |

| Input Resistance      | R <sub>IN</sub>            |                                                                      |     | 1   |     | TΩ    |

| Input Capacitance     | C <sub>IN</sub>            |                                                                      |     | 1.2 |     | pF    |

| Common Mode Rejection | CMRR                       | $V_{IN} = V_{SS}$ to $V_{DD} - 0.6$ V                                | 70  | 80  |     | dB    |

| Ratio                 |                            | $V_{\text{IN}}$ = $V_{\text{SS}}$ + 0.2 V to $V_{\text{DD}}$ – 0.6 V | 65  |     |     |       |

#### **OUTPUT CHARACTERISTICS**

| Open Loop Voltage Gain    | A <sub>VOL</sub> | $R_L = 10 \ k\Omega$   |            | 80   | 92    |     | dB |

|---------------------------|------------------|------------------------|------------|------|-------|-----|----|

|                           |                  |                        |            | 75   |       |     |    |

|                           |                  | $R_L = 2 k\Omega$      |            |      | 92    |     |    |

|                           |                  |                        |            | 70   |       |     |    |

| Output Current Capability | I <sub>SC</sub>  | Sourcing               |            | 5    | 8     |     | mA |

| (Note 8)                  |                  | Sinking                |            | 10   | 14    |     |    |

| Output Voltage High       | V <sub>OH</sub>  | R <sub>L</sub> = 10 kΩ |            | 1.75 | 1.798 |     | V  |

|                           |                  | $R_L = 2 k\Omega$      |            | 1.7  | 1.78  |     |    |

| Output Voltage Low        | Vol              | $R_L = 10 \ k\Omega$   | NCx2003, A |      | 7     | 50  | mV |

|                           |                  |                        | NCx2003x   |      | 7     | 100 |    |

|                           |                  | $R_L = 2 k\Omega$      | •          |      | 20    | 100 |    |

#### NOISE PERFORMANCE

| Voltage Noise Density | e <sub>N</sub> | f = 1 kHz | 20  | nV/√ <del>Hz</del> |

|-----------------------|----------------|-----------|-----|--------------------|

| Current Noise Density | i <sub>N</sub> | f = 1 kHz | 0.1 | pA√Hz              |

#### DYNAMIC PERORMANCE

| Gain Bandwidth Product  | GBWP           |                                                             |                                             |  | 5   | MHz  |

|-------------------------|----------------|-------------------------------------------------------------|---------------------------------------------|--|-----|------|

| Clow Data at Unity Cain | SR             | Rising Edge, R <sub>L</sub> = 2 I                           | Rising Edge, $R_L = 2 k\Omega$ , $A_V = +1$ |  | 6   | 1/// |

| Slew Rate at Unity Gain | SR             | Falling Edge, R <sub>L</sub> = 2 I                          | $\propto \Omega, A_V = +1$                  |  | 9   | V/μs |

| Phase Margin            | ψm             | $R_L = 10 \text{ k}\Omega, C_L = 5 \text{ pF}$              |                                             |  | 53  | ٥    |

| Gain Margin             | A <sub>m</sub> | $R_L = 10 \text{ k}\Omega, C_L = 5 \text{ pF}$              | NCx2003, A                                  |  | 12  | dB   |

|                         |                |                                                             | NCx2003x                                    |  | 8   |      |

| Settling Time           | ts             | V <sub>O</sub> = 1 Vpp,<br>Gain = 1, C <sub>L</sub> = 20 pF | Settling time to 0.1%                       |  | 1.8 | μS   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

8. Guaranteed by design and/or characterization.

#### ELECTRICAL CHARACTERISTICS: V<sub>S</sub> = +1.8 V

At  $T_A = +25^{\circ}C$ ,  $R_L = 10 \text{ k}\Omega$  connected to midsupply,  $V_{CM} = V_{OUT}$  = midsupply, unless otherwise noted. **Boldface** limits apply over the specified temperature range. Guaranteed by design and/or characterization.

| Parameter                             | Symbol | Conditions                                                               |  | Тур   | Max | Unit |

|---------------------------------------|--------|--------------------------------------------------------------------------|--|-------|-----|------|

| DYNAMIC PERORMANCE                    |        |                                                                          |  |       |     |      |

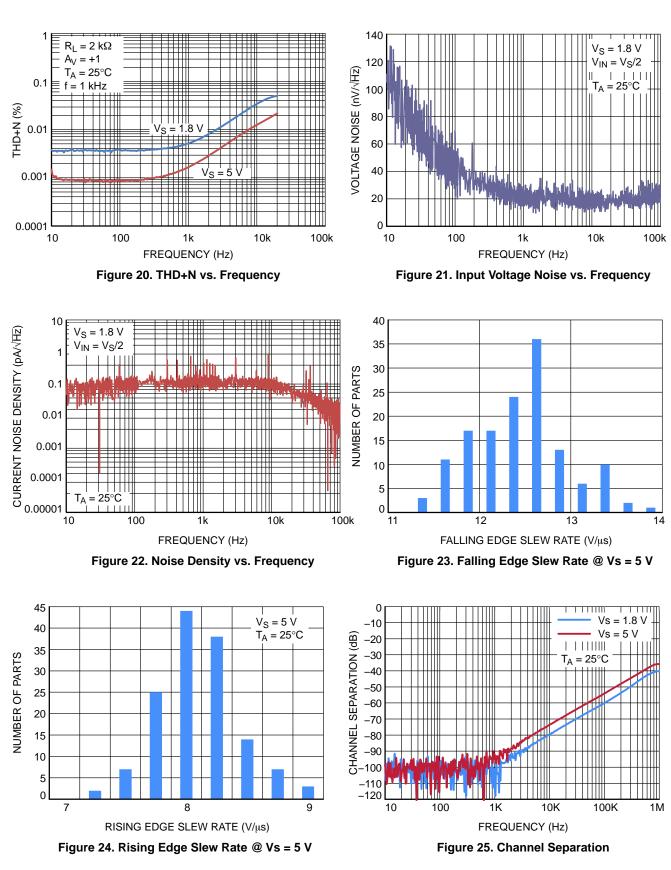

| Total Harmonics Distortion +<br>Noise | THD+N  | $V_{O}$ = 1 $V_{pp}$ , $R_{L}$ = 2 k $\Omega$ , $A_{V}$ = +1, f = 1 kHz  |  | 0.005 |     | %    |

| NOISE                                 |        | $V_{O}$ = 1 $V_{pp}$ , $R_{L}$ = 2 k $\Omega$ , $A_{V}$ = +1, f = 10 kHz |  | 0.025 |     |      |

#### POWER SUPPLY

| Power Supply Rejection Ratio | PSRR            | NCx2003              |                    | 72 | 80  |      | dB |

|------------------------------|-----------------|----------------------|--------------------|----|-----|------|----|

|                              |                 |                      |                    | 65 |     |      |    |

|                              |                 | NCx20032, NCx2       | NCx20032, NCx20034 |    | 100 |      |    |

| Quiescent Current            | I <sub>DD</sub> | No load, per channel | NCx2003, A         |    | 230 | 560  | μΑ |

|                              |                 |                      |                    |    |     | 1000 |    |

|                              |                 |                      | NCx20032,          |    | 275 | 375  |    |

|                              |                 |                      | NCx20034           |    |     | 575  |    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

8. Guaranteed by design and/or characterization.

#### ELECTRICAL CHARACTERISTICS: V<sub>S</sub> = +5.0 V

At  $T_A = +25^{\circ}$ C,  $R_L = 10 \text{ k}\Omega$  connected to midsupply,  $V_{CM} = V_{OUT}$  = midsupply, unless otherwise noted. **Boldface** limits apply over the specified temperature range. Guaranteed by design and/or characterization.

| Parameter             | Symbol                     | Conditions             |  | Тур | Max | Unit  |

|-----------------------|----------------------------|------------------------|--|-----|-----|-------|

| INPUT CHARACTERISTICS | 6                          |                        |  |     |     |       |

| Input Offset Voltage  | V <sub>OS</sub>            | NCS2003A               |  | 0.5 | 3.0 | mV    |

|                       |                            | NCx2003                |  | 0.5 | 4.0 | mV    |

|                       |                            | NCx20032, NCx20034     |  |     | 5.0 | mV    |

| Offset Voltage Drift  | $\Delta V_{OS} / \Delta T$ |                        |  | 2.0 |     | μV/°C |

|                       |                            | NCS2003A (Note 9)      |  |     | 6.0 | μV/°C |

| Input Bias Current    | I <sub>IB</sub>            |                        |  | 1   |     | pА    |

| Input Offset Current  | I <sub>OS</sub>            |                        |  | 1   |     | pА    |

| Channel Separation    | XTLK                       | DC, NCx20032, NCx20034 |  | 100 |     | dB    |

| Input Resistance      | R <sub>IN</sub>            |                        |  | 1   |     | TΩ    |

| Input Capacitance     | C <sub>IN</sub>            |                        |  | 1.2 |     | pF    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

9. Guaranteed by design and/or characterization.

## ELECTRICAL CHARACTERISTICS: V<sub>S</sub> = +5.0 V

At  $T_A = +25^{\circ}C$ ,  $R_L = 10 \text{ k}\Omega$  connected to midsupply,  $V_{CM} = V_{OUT}$  = midsupply, unless otherwise noted. Boldface limits apply over the specified temperature range. Guaranteed by design and/or characterization.

| Parameter                   | Symbol | Conditi            | ons                                              | Min | Тур | Max | Unit |

|-----------------------------|--------|--------------------|--------------------------------------------------|-----|-----|-----|------|

| INPUT CHARACTERISTICS       |        |                    |                                                  |     |     |     |      |

| Common Mode Rejection Ratio | CMRR   | NCx2003, A         | $V_{IN} = V_{SS}$ to $V_{DD} - 0.6$ V            | 65  | 90  |     | dB   |

|                             |        |                    | $V_{IN} = V_{SS} + 0.2 V$<br>to $V_{DD} - 0.6 V$ | 63  |     |     |      |

|                             |        | NCx20032, NCx20034 | $V_{IN} = V_{SS}$ to $V_{DD} - $<br>0.6 V        | 70  | 90  |     |      |

|                             |        |                    | $V_{IN} = V_{SS} + 0.2 V$<br>to $V_{DD} - 0.6 V$ | 65  |     |     |      |

#### **OUTPUT CHARACTERISTICS**

| Open Loop Voltage Gain    | A <sub>VOL</sub>       | $R_L = 10 k\Omega$ |            | 86   | 92   |     | dB |

|---------------------------|------------------------|--------------------|------------|------|------|-----|----|

|                           |                        |                    |            | 78   |      |     |    |

|                           |                        | L                  |            | 83   | 92   |     |    |

|                           |                        |                    |            | 78   |      |     |    |

| Output Current Capability | I <sub>SC</sub>        | Sourcing           |            | 40   | 76   |     | mA |

| (Note 9)                  |                        | Sinking            |            | 50   | 96   |     |    |

| Output Voltage High       | V <sub>OH</sub>        | R <sub>L</sub> = 2 | 10 kΩ      | 4.95 | 4.99 |     | V  |

|                           |                        | R <sub>L</sub> =   | 2 kΩ       | 4.9  | 4.97 |     |    |

| Output Voltage Low        | Output Voltage Low VoL |                    | NCx2003, A |      | 8    | 50  | mV |

|                           |                        |                    | NCx2003x   |      | 8    | 100 |    |

|                           |                        | R <sub>L</sub> = 2 | 2 kΩ       |      | 24   | 100 | 1  |

#### NOISE PERFORMANCE

| Voltage Noise Density | e <sub>N</sub> | f = 1 kHz | 20  | nV/√Hz            |

|-----------------------|----------------|-----------|-----|-------------------|

| Current Noise Density | i <sub>N</sub> | f = 1 kHz | 0.1 | pA√ <del>Hz</del> |

#### DYNAMIC PERORMANCE

| Gain Bandwidth Product       | GBWP           |                                                                          |                                            |   | 7     | MHz  |

|------------------------------|----------------|--------------------------------------------------------------------------|--------------------------------------------|---|-------|------|

| Slew Rate at Unity Gain      | SR             | Rising Edge, R <sub>L</sub> =                                            | Rising Edge, $R_L = 2 k\Omega$ , $AV = +1$ |   | 8     | V/μs |

|                              |                | Falling Edge, R <sub>L</sub> =                                           | 2 kΩ, AV = +1                              |   | 12.5  |      |

| Phase Margin                 | Ψm             | $R_L = 10 \text{ k}\Omega, C_L = 5 \text{ pF}$                           | NCx2003, A                                 |   | 64    | 0    |

|                              |                |                                                                          | NCx2003x                                   |   | 56    |      |

| Gain Margin                  | A <sub>m</sub> | R <sub>L</sub> = 10 kΩ, C                                                | C <sub>L</sub> = 5 pF                      |   | 9     | dB   |

| Settling Time                | t <sub>S</sub> | V <sub>O</sub> = 1 V <sub>pp</sub> ,<br>Gain = 1, C <sub>L</sub> = 20 pF | Settling time to 0.1%                      |   | 0.6   | μs   |

| Total Harmonics Distortion + | THD+N          | $V_{O} = 4 V_{pp}, R_{L} = 2 k\Omega,$                                   | A <sub>V</sub> = +1, f = 1 kHz             | C | 0.002 | %    |

| Noise                        |                | $V_{O} = 4 V_{pp}, R_{L} = 2 k\Omega, A$                                 | A <sub>V</sub> = +1, f = 10 kHz            | ( | 0.01  |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 9. Guaranteed by design and/or characterization.

## ELECTRICAL CHARACTERISTICS: $V_S = +5.0 V$

At  $T_A = +25^{\circ}$ C,  $R_L = 10 \text{ k}\Omega$  connected to midsupply,  $V_{CM} = V_{OUT}$  = midsupply, unless otherwise noted. **Boldface** limits apply over the specified temperature range. Guaranteed by design and/or characterization.

| Parameter                    | Symbol          | Conditions           |            | Min | Тур | Max  | Unit |

|------------------------------|-----------------|----------------------|------------|-----|-----|------|------|

| POWER SUPPLY                 |                 |                      |            |     |     |      |      |

| Power Supply Rejection Ratio | PSRR            | NCx2003, A<br>       |            | 72  | 80  |      | dB   |

|                              |                 |                      |            | 65  |     |      |      |

|                              |                 |                      |            | 80  | 100 |      |      |

| Quiescent Current            | I <sub>DD</sub> | No load, per channel | NCx2003, A |     | 300 | 660  | μΑ   |

|                              |                 | NCx20032,            |            |     |     | 1000 |      |

|                              |                 |                      |            |     | 325 | 450  |      |

|                              |                 |                      | NCx20034   |     |     | 675  | 1    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

9. Guaranteed by design and/or characterization.

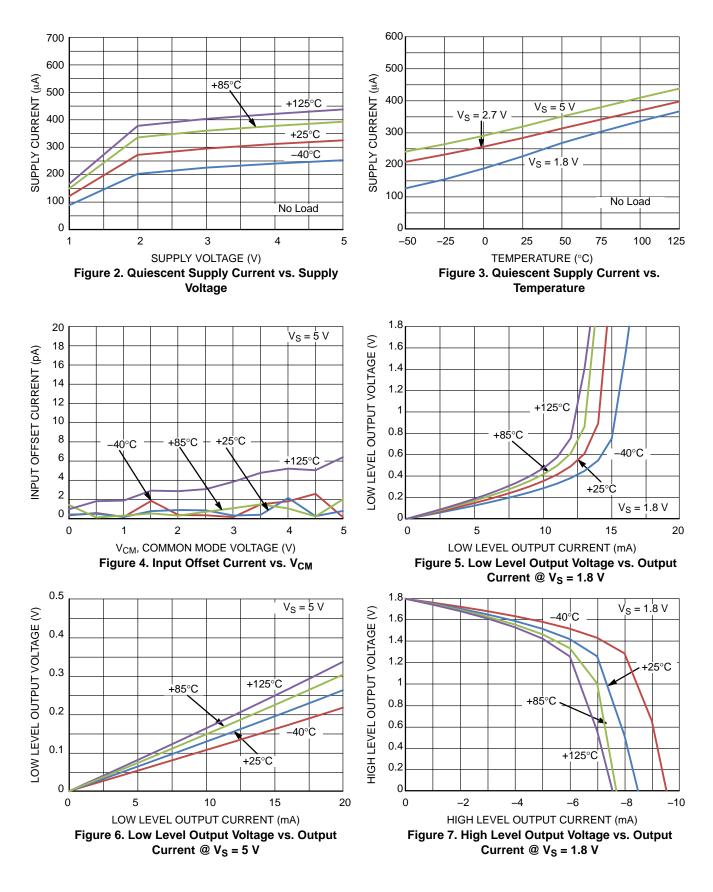

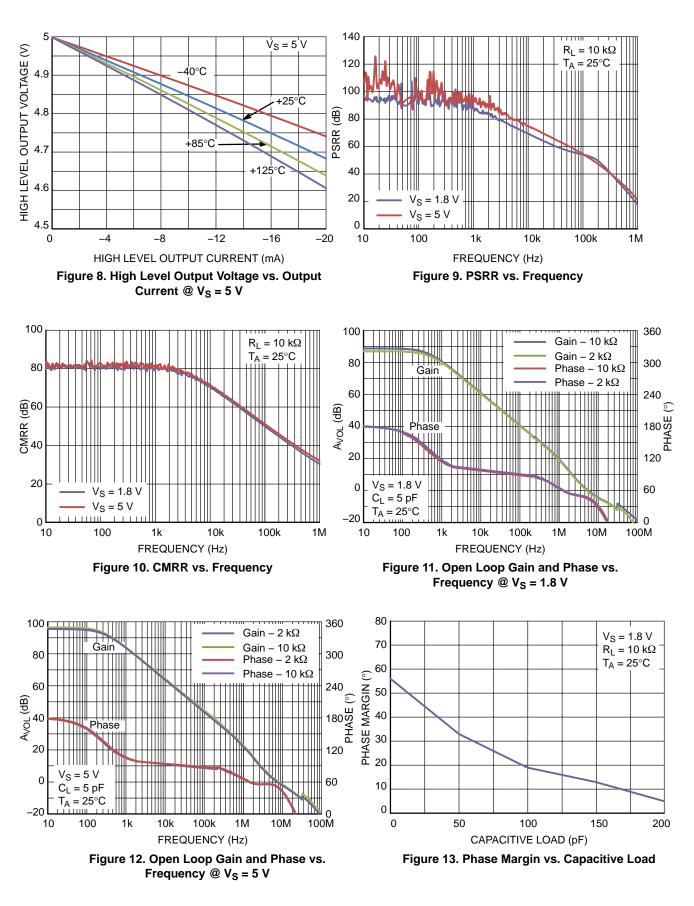

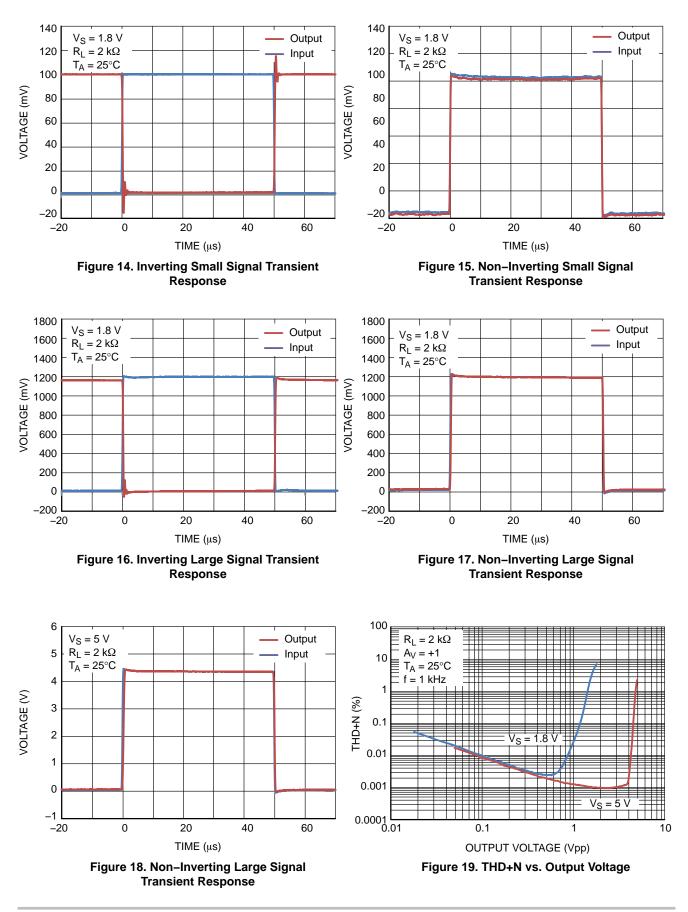

### **TYPICAL CHARACTERISTICS**

### **TYPICAL CHARACTERISTICS**

#### **TYPICAL CHARACTERISTICS**

www.onsemi.com

**TYPICAL CHARACTERISTICS**

Micro8 is a trademark of International Rectifier.

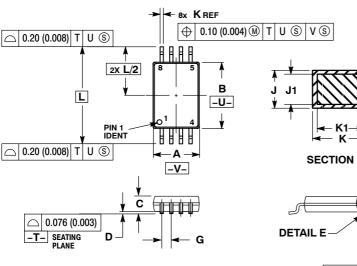

SCALE 4:1

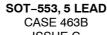

ISSUE C

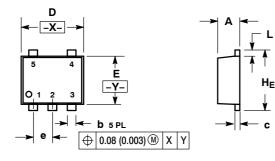

#### RECOMMENDED **SOLDERING FOOTPRINT\***

NOTES:

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETERS 3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.

|     | м    | ILLIMETE | RS   |       | INCHES    |       |

|-----|------|----------|------|-------|-----------|-------|

| DIM | MIN  | NOM      | MAX  | MIN   | NOM       | MAX   |

| Α   | 0.50 | 0.55     | 0.60 | 0.020 | 0.022     | 0.024 |

| b   | 0.17 | 0.22     | 0.27 | 0.007 | 0.009     | 0.011 |

| С   | 0.08 | 0.13     | 0.18 | 0.003 | 0.005     | 0.007 |

| D   | 1.55 | 1.60     | 1.65 | 0.061 | 0.063     | 0.065 |

| E   | 1.15 | 1.20     | 1.25 | 0.045 | 0.047     | 0.049 |

| е   |      | 0.50 BSC |      |       | 0.020 BSC | )     |

| L   | 0.10 | 0.20     | 0.30 | 0.004 | 0.008     | 0.012 |

| HE  | 1.55 | 1.60     | 1.65 | 0.061 | 0.063     | 0.065 |

# GENERIC **MARKING DIAGRAM\***

# XXM-

XX = Specific Device Code M = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| STYLE 1:              | STYLE 2:        | STYLE 3:       | STYLE 4:        | STYLE 5:     |

|-----------------------|-----------------|----------------|-----------------|--------------|

| PIN 1. BASE           | PIN 1. CATHODE  | PIN 1. ANODE 1 | PIN 1. SOURCE 1 | PIN 1. ANODE |

| 2. EMITTER            | 2. COMMON ANODE | 2. N/C         | 2. DRAIN 1/2    | 2. EMITTER   |

| 3. BASE               | 3. CATHODE 2    | 3. ANODE 2     | 3. SOURCE 1     | 3. BASE      |

| 4. COLLECTOR          | 4. CATHODE 3    | 4. CATHODE 2   | 4. GATE 1       | 4. COLLECTOR |

| 5. COLLECTOR          | 5. CATHODE 4    | 5. CATHODE 1   | 5. GATE 2       | 5. CATHODE   |

| STYLE 6:              | STYLE 7:        | STYLE 8:       | STYLE 9:        |              |

| PIN 1. EMITTER 2      | PIN 1. BASE     | PIN 1. CATHODE | PIN 1. ANODE    |              |

| 2. BASE 2             | 2. EMITTER      | 2. COLLECTOR   | 2. CATHODE      |              |

| 3. EMITTER 1          | 3. BASE         | 3. N/C         | 3. ANODE        |              |

| 4. COLLECTOR 1        | 4. COLLECTOR    | 4. BASE        | 4. ANODE        |              |

| 5. COLLECTOR 2/BASE 1 | 5. COLLECTOR    | 5. EMITTER     | 5. ANODE        |              |

| DOCUMENT NUMBER: | 98AON11127D               | Electronic versions are uncontrolle                                     |             |

|------------------|---------------------------|-------------------------------------------------------------------------|-------------|

| STATUS:          | ON SEMICONDUCTOR STANDARD | accessed directly from the Document<br>versions are uncontrolled except |             |

| NEW STANDARD:    |                           | "CONTROLLED COPY" in red.                                               |             |

| DESCRIPTION:     | SOT-553, 5 LEAD           |                                                                         | PAGE 1 OF 2 |

### DOCUMENT NUMBER: 98AON11127D

PAGE 2 OF 2

| ISSUE | REVISION                                                                    | DATE        |  |  |  |  |

|-------|-----------------------------------------------------------------------------|-------------|--|--|--|--|

| Α     | ADDED STYLES 3–9. REQ. BY D. BARLOW                                         | 11 NOV 2003 |  |  |  |  |

| В     | ADDED NOMINAL VALUES AND UPDATED GENERIC MARKING DIAGRAM. REQ. BY HONG XIAO | 27 MAY 2005 |  |  |  |  |

| С     | UPDATED DIMENSIONS D, E, AND HE. REQ. BY J. LETTERMAN.                      | 20 MAR 2013 |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

|       |                                                                             |             |  |  |  |  |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product culd create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

| DOCUMENT NUMBER:                                                                  | 98ARB18753C                                                                                 | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                           |                                                       |  |  |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

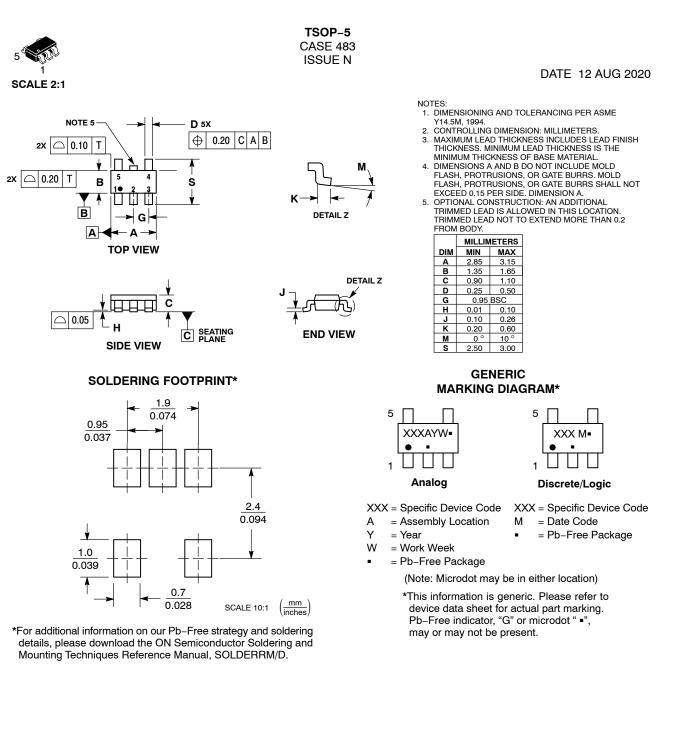

| DESCRIPTION:                                                                      | CRIPTION: TSOP-5 PAGE 1 OF                                                                  |                                                                                                                                                                                                                                                                                                               |                                                       |  |  |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product or<br>acidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>r circuit, and specifically |  |  |  |  |

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### STYLES ON PAGE 2

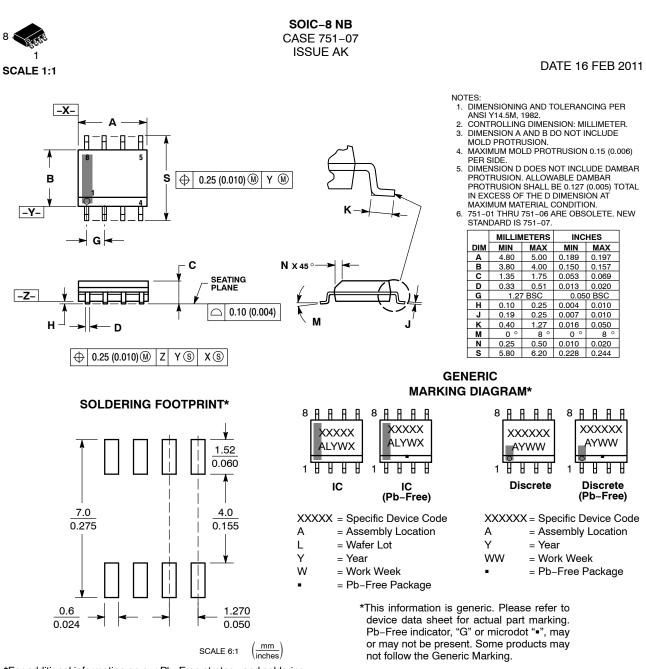

| DOCUMENT NUMBER:                                                                  | 98ASB42564B                                                                                 | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                            |                                                       |  |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| DESCRIPTION: SOIC-8 NB                                                            |                                                                                             |                                                                                                                                                                                                                                                                                                               |                                                       |  |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product on<br>acidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>r circuit, and specifically |  |  |  |

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR 3. 4. EMITTER EMITTER 5. BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: CATHODE 1 PIN 1. 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: PIN 1. GROUND BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE P-SOURCE 3 P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE 2. ANODE SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC COMMON CATHODE/VCC 3 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 COMMON ANODE/GND 8. STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. 4. DRAIN, #2 GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 DRAIN 1 7. 8. **MIRROR 1** STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. LINE 1 OUT 8. STYLE 27: PIN 1. ILIMIT 2 OVI 0 UVLO З. 4. INPUT+ 5. SOURCE SOURCE 6. SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: ANODE ANODE PIN 1. 2. ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE #2 3. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. 4. GATE 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE 2. EMITTER 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from<br>Printed versions are uncontrolled except when stamped "CONTROLLED 0 |             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SOIC-8 NB   |                                                                                                                                                | PAGE 2 OF 2 |

| ON Semiconductor and  Construction of the registrian of the semiconductor of the semiconductor or its subsidiaries in the United States and/or other countries.  ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding  the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically  disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |             |                                                                                                                                                |             |

SOURCE 1/DRAIN 2

7.

8. GATE 1

7.

8

rights of others

COLLECTOR, #1

COLLECTOR, #1

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### **STYLES ON PAGE 2**

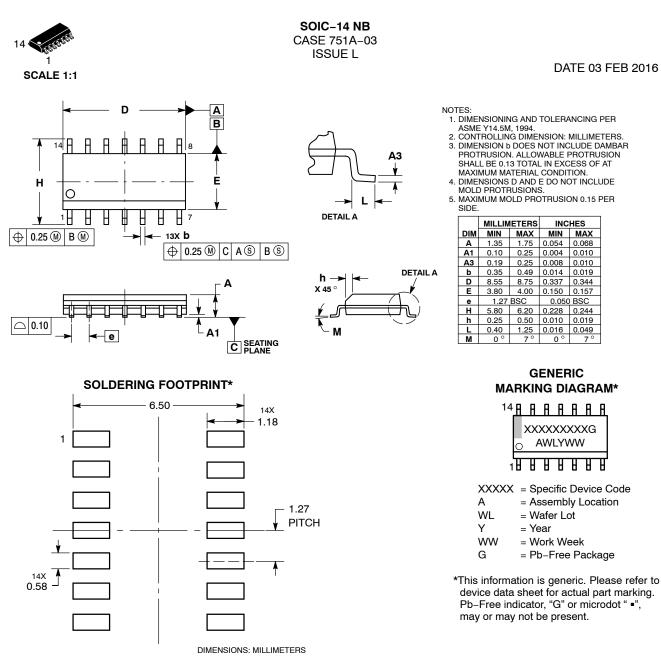

| DOCUMENT NUMBER:                                                                  | 98ASB42565B                                                                                 | Electronic versions are uncontrolled except when accessed directly from<br>Printed versions are uncontrolled except when stamped "CONTROLLED 0                                                                                                                                                                |                                                        |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| DESCRIPTION:                                                                      | SOIC-14 NB                                                                                  |                                                                                                                                                                                                                                                                                                               | PAGE 1 OF 2                                            |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product or<br>acidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>or circuit, and specifically |

#### SOIC-14 CASE 751A-03 ISSUE L

#### DATE 03 FEB 2016

| STYLE 1:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. NO CONNECTION<br>5. ANODE/CATHODE<br>6. NO CONNECTION<br>7. ANODE/CATHODE<br>8. ANODE/CATHODE<br>9. ANODE/CATHODE<br>10. NO CONNECTION<br>11. ANODE/CATHODE<br>12. ANODE/CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE | STYLE 2:<br>CANCELLED                                                                                                                                                                                   | STYLE 3:<br>PIN 1. NO CONNECTION<br>2. ANODE<br>3. ANODE<br>4. NO CONNECTION<br>5. ANODE<br>6. NO CONNECTION<br>7. ANODE<br>8. ANODE<br>9. ANODE<br>10. NO CONNECTION<br>11. ANODE<br>12. ANODE<br>13. NO CONNECTION<br>14. COMMON CATHODE                                            | STYLE 4:<br>PIN 1. NO CONNECTION<br>2. CATHODE<br>3. CATHODE<br>4. NO CONNECTION<br>5. CATHODE<br>6. NO CONNECTION<br>7. CATHODE<br>8. CATHODE<br>10. NO CONNECTION<br>11. CATHODE<br>12. CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. ANODE/CATHODE<br>5. ANODE/CATHODE<br>6. NO CONNECTION<br>7. COMMON ANODE<br>8. COMMON CATHODE<br>10. ANODE/CATHODE<br>11. ANODE/CATHODE<br>12. ANODE/CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE                     | STYLE 6:<br>PIN 1. CATHODE<br>2. CATHODE<br>3. CATHODE<br>4. CATHODE<br>5. CATHODE<br>6. CATHODE<br>7. CATHODE<br>8. ANODE<br>9. ANODE<br>10. ANODE<br>11. ANODE<br>12. ANODE<br>13. ANODE<br>14. ANODE | STYLE 7:<br>PIN 1. ANODE/CATHODE<br>2. COMMON ANODE<br>3. COMMON CATHODE<br>4. ANODE/CATHODE<br>5. ANODE/CATHODE<br>6. ANODE/CATHODE<br>8. ANODE/CATHODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. COMMON CATHODE<br>12. COMMON ANODE<br>13. ANODE/CATHODE<br>14. ANODE/CATHODE | STYLE 8:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. NO CONNECTION<br>5. ANODE/CATHODE<br>6. ANODE/CATHODE<br>7. COMMON ANODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. NO CONNECTION<br>12. ANODE/CATHODE<br>13. ANODE/CATHODE<br>14. COMMON CATHODE |

| DOCUMENT NUMBER:                                                                                                                                                      | 98ASB42565B Electronic versions are uncontrolled except when accessed directly from the Document Reposito<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| DESCRIPTION:                                                                                                                                                          | SOIC-14 NB                                                                                                                                                                                   |  | PAGE 2 OF 2 |

| ON Semiconductor and M are trademarks of Semiconductor Components Industries LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries |                                                                                                                                                                                              |  |             |

ON Semiconductor and united states and/or other countries. LC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

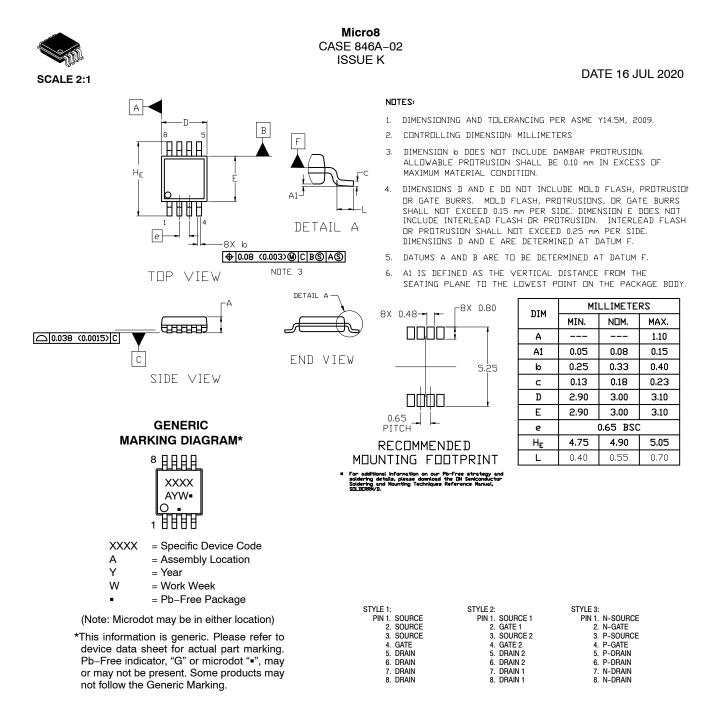

| DOCUMENT NUMBER:                                                                  | 98ASB14087C                                                                                 | Electronic versions are uncontrolled except when accessed directly from<br>Printed versions are uncontrolled except when stamped "CONTROLLED (                                                                                                                                                               |                                                       |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| DESCRIPTION:                                                                      | MICRO8                                                                                      |                                                                                                                                                                                                                                                                                                              | PAGE 1 OF 1                                           |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product o<br>acidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>r circuit, and specifically |

SCALE 2:1

**TSSOP-8** CASE 948S-01 ISSUE C

DATE 20 JUN 2008

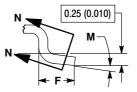

SECTION N-N

DETAIL E

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI

- VIMENSIONING AND TOLENANDING FER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A DOES NOT INCLUDE MOLD FLASH. PROTRUSIONS OR GATE BURRS. MOLD FLASH.

- PROTRUSION SHALL NOT EXCEED 0.15

(0.006) PER SIDE.

JIMENSION B DOES NOT INCLUDE INTERLEAD

FLASH OR PROTRUSION. INTERLEAD FLASH OR

PROTRUSION SHALL NOT EXCEED 0.25 (0.010)

DED SIDE. PER SIDE

- 5. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- 6. DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 2.90        | 3.10 | 0.114     | 0.122 |

| В   | 4.30        | 4.50 | 0.169     | 0.177 |

| С   |             | 1.10 |           | 0.043 |

| D   | 0.05        | 0.15 | 0.002     | 0.006 |

| F   | 0.50        | 0.70 | 0.020     | 0.028 |

| G   | 0.65 BSC    |      | 0.026 BSC |       |

| J   | 0.09        | 0.20 | 0.004     | 0.008 |

| J1  | 0.09        | 0.16 | 0.004     | 0.006 |

| K   | 0.19        | 0.30 | 0.007     | 0.012 |

| K1  | 0.19        | 0.25 | 0.007     | 0.010 |

| L   | 6.40 BSC    |      | 0.252     | BSC   |

| М   | 0°          | 8°   | 0°        | 8°    |

#### GENERIC **MARKING DIAGRAM\***

| S | XXX<br>YWW |  |

|---|------------|--|

|   | A •        |  |

|   | •          |  |

|   |            |  |

XXX = Specific Device Code А

- = Assembly Location

- = Year

Y

- WW = Work Week

- = Pb-Free Package -

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: | 98AON00697D               | Electronic versions are uncontrolled                                          |             |  |

|------------------|---------------------------|-------------------------------------------------------------------------------|-------------|--|

| STATUS:          | ON SEMICONDUCTOR STANDARD | accessed directly from the Document Re<br>versions are uncontrolled except wh |             |  |

| NEW STANDARD:    |                           | "CONTROLLED COPY" in red.                                                     |             |  |

| DESCRIPTION:     | TSSOP-8                   | F                                                                             | PAGE 1 OF 2 |  |

### DOCUMENT NUMBER: 98AON00697D

PAGE 2 OF 2

| 100115 |                                                                                                         | DATE        |

|--------|---------------------------------------------------------------------------------------------------------|-------------|

| ISSUE  | REVISION                                                                                                | DATE        |

| 0      | RELEASED FOR PRODUCTION.                                                                                | 18 APR 2000 |

| А      | ADDED MARKING DIAGRAM INFORMATION. REQ. BY V. BASS.                                                     | 13 JAN 2006 |

| В      | CORRECTED MARKING DIAGRAM PIN 1 LOCATION AND MARKING. REQ. BY C. REBELLO.                               | 13 MAR 2006 |

| С      | REMOVED EXPOSED PAD VIEW AND DIMENSIONS P AND P1. CORRECTED<br>MARKING INFORMATION. REQ. BY C. REBELLO. | 20 JUN 2008 |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

|        |                                                                                                         |             |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.