# **NGTD17T65F2**

## **IGBT** Die

Trench Field Stop II IGBT Die for motor drive and inverter applications.

#### Features

- Extremely Efficient Trench with Field Stop Technology

- Low V<sub>CE(sat)</sub> Loss Reduces System Power Dissipation

#### **Typical Applications**

- Industrial Motor Drives

- Solar Inverters

- UPS Systems

- Welding

#### MAXIMUM RATINGS

| Parameter                                                                          | Symbol                | Value       | Unit |

|------------------------------------------------------------------------------------|-----------------------|-------------|------|

| Collector–Emitter Voltage, $T_J = 25^{\circ}C$                                     | V <sub>CE</sub>       | 650         | V    |

| DC Collector Current, limited by $T_{J(\text{max})}$                               | Ι <sub>C</sub>        | (Note 1)    | A    |

| Pulsed Collector Current (Note 2)                                                  | I <sub>C, pulse</sub> | 160         | А    |

| Gate-Emitter Voltage                                                               | V <sub>GE</sub>       | ±20         | V    |

| Maximum Junction Temperature                                                       | ТJ                    | -55 to +175 | °C   |

| Short Circuit Withstand Time, $V_{GE}$ = 15 V, $V_{CE}$ = 500V, $T_J$ $\leq$ 150°C | T <sub>SC</sub>       | 5.0         | μs   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. Depending on thermal properties of assembly. 2.  $T_{pulse}$  limited by  $T_{jmax}$ , 10 µs pulse,  $V_{GE}$  = 15 V.

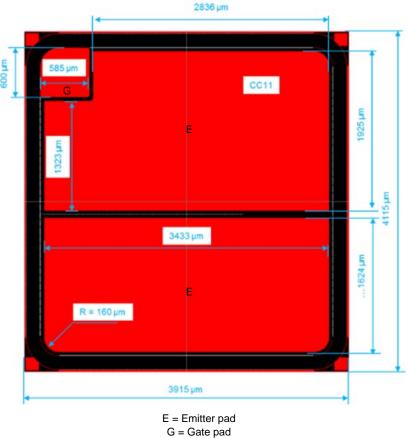

#### **MECHANICAL DATA**

| Parameter                                                                                                             | Value                                                      | Unit            |  |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|--|

| Die Size                                                                                                              | 3915 x 4115 μm <sup>2</sup>                                |                 |  |

| Emitter Pad Size                                                                                                      | See die layout µm <sup>2</sup>                             |                 |  |

| Gate Pad Size                                                                                                         | 585 x 600                                                  | μm <sup>2</sup> |  |

| Die Thickness                                                                                                         | 3                                                          | mils            |  |

| Wafer Size                                                                                                            | 150                                                        | mm              |  |

| Top Metal                                                                                                             | 4 μm AISI                                                  |                 |  |

| Back Metal                                                                                                            | 2 μm TiNiAg                                                |                 |  |

| Max possible chips per wafer                                                                                          | 778                                                        |                 |  |

| Passivation frontside                                                                                                 | Oxide-Nitride                                              |                 |  |

| Reject ink dot size                                                                                                   | 25 mils                                                    |                 |  |

| Recommended storage environment:<br>In original container, in dry nitrogen,<br>or temperature of 18–28°C,<br>30–65%RH | Type: Die on tape in ring–pack<br>Storage time: < 3 months |                 |  |

#### **ORDERING INFORMATION**

| Device         | Inking? | Shipping           |

|----------------|---------|--------------------|

| NGTD17T65F2WP  | Yes     | Bare Wafer on Tape |

| NGTD17T65F2SWK | Yes     | Sawn Wafer on Tape |

### **ON Semiconductor®**

www.onsemi.com

$V_{RCE} = 650 V$  $I_{C}$  = Limited by  $T_{J(max)}$

**DIE OUTLINE**

## NGTD17T65F2

#### ELECTRICAL CHARACTERISTICS (T<sub>J</sub> = 25°C, unless otherwise specified)

| Parameter                            | Test Conditions                                | Symbol               | Min | Тур  | Max | Units |

|--------------------------------------|------------------------------------------------|----------------------|-----|------|-----|-------|

| STATIC CHARACTERISTICS               |                                                |                      |     |      |     | •     |

| Collector-Emitter Breakdown Voltage  | $V_{GE}$ = 0 V, I <sub>C</sub> = 500 $\mu$ A   | V <sub>(BR)CES</sub> | 650 |      |     | V     |

| Collector-Emitter Saturation Voltage | V <sub>GE</sub> = 15 V, I <sub>C</sub> = 40 A  | V <sub>CE(sat)</sub> |     | 1.7  | 2.0 | V     |

| Gate-Emitter Threshold Voltage       | $V_{GE} = V_{CE}, I_C = 350 \ \mu A$           | V <sub>GE(TH)</sub>  | 4.5 | 5.5  | 6.5 | V     |

| Collector-Emitter Cutoff Current     | V <sub>GE</sub> = 0 V, V <sub>CE</sub> = 650 V | I <sub>CES</sub>     |     |      | 0.5 | mA    |

| Gate Leakage Current                 | $V_{GE}$ = 20 V, $V_{CE}$ = 0 V                | I <sub>GES</sub>     |     |      | 200 | nA    |

| DYNAMIC CHARACTERISTICS              |                                                |                      |     |      |     |       |

| lanut Canaditanaa                    |                                                | 0                    |     | 4000 |     |       |

| Input Capacitance            |                                                             | Cies             | 4060 | pF |

|------------------------------|-------------------------------------------------------------|------------------|------|----|

| Output Capacitance           | V <sub>CE</sub> = 20 V, V <sub>GE</sub> = 0 V, f = 1<br>MHz | C <sub>oes</sub> | 179  | pF |

| Reverse Transfer Capacitance |                                                             | C <sub>res</sub> | 115  | pF |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

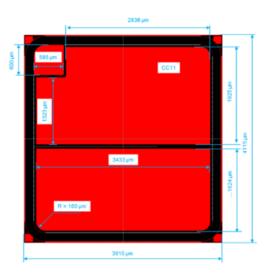

#### DIE LAYOUT

G = Gate padAll dimensions in  $\mu m$

#### **Further Electrical Characteristic**

Switching characteristics and thermal properties are depending strongly on module design and mounting technology and can therefore not be specified for a bare die.