**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# NGTD23T120F2

# **IGBT Die**

Trench Field Stop II IGBT Die for motor drive and inverter applications.

#### Features

- Extremely Efficient Trench with Field Stop Technology

- Low V<sub>CE(sat)</sub> Loss Reduces System Power Dissipation

#### **Typical Applications**

- Industrial Motor Drives

- Solar Inverters

- UPS Systems

- Welding

#### MAXIMUM RATINGS

| Parameter                                                                          | Symbol                | Value       | Unit |

|------------------------------------------------------------------------------------|-----------------------|-------------|------|

| Collector–Emitter Voltage, $T_J = 25^{\circ}C$                                     | V <sub>CE</sub>       | 1200        | V    |

| DC Collector Current, limited by $T_{J(\text{max})}$                               | Ι <sub>C</sub>        | (Note 1)    | A    |

| Pulsed Collector Current (Note 2)                                                  | I <sub>C, pulse</sub> | 120         | А    |

| Gate-Emitter Voltage                                                               | V <sub>GE</sub>       | ±20         | V    |

| Maximum Junction Temperature                                                       | TJ                    | -55 to +175 | °C   |

| Short Circuit Withstand Time, $V_{GE}$ = 15 V, $V_{CE}$ = 500V, $T_J$ $\leq$ 150°C | T <sub>SC</sub>       | 10          | μs   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Depending on thermal properties of assembly.

2.  $T_{pulse}$  limited by  $T_{jmax}$ , 10 µs pulse,  $V_{GE}$  = 15 V.

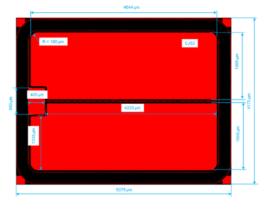

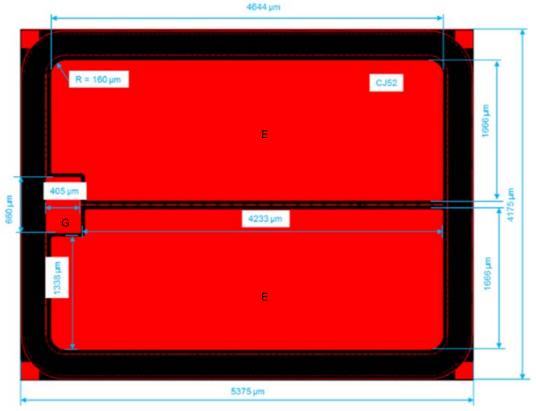

#### MECHANICAL DATA

| Parameter                                                                                                             | Value                                                      | Unit                                                                |  |  |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------|--|--|

| Die Size                                                                                                              | 5375 x 4175 μm <sup>2</sup>                                |                                                                     |  |  |

| Emitter Pad Size                                                                                                      | See die layout                                             | μm <sup>2</sup>                                                     |  |  |

| Gate Pad Size                                                                                                         | 405 x 660                                                  | μm <sup>2</sup>                                                     |  |  |

| Die Thickness                                                                                                         | 5                                                          | mils                                                                |  |  |

| Wafer Size                                                                                                            | 150                                                        | mm                                                                  |  |  |

| Top Metal                                                                                                             | 5 μm AlSi                                                  |                                                                     |  |  |

| Back Metal                                                                                                            | 2 μm TiNiAg                                                |                                                                     |  |  |

| Max possible chips per wafer                                                                                          | 546                                                        |                                                                     |  |  |

| Passivation frontside                                                                                                 | Oxide-Nitride                                              |                                                                     |  |  |

| Reject ink dot size                                                                                                   | 25 mils                                                    |                                                                     |  |  |

| Recommended storage environment:<br>In original container, in dry nitrogen,<br>or temperature of 18–28°C,<br>30–65%RH | Type: Bare<br>Wafer in Jar<br>Storage time:<br>< 36 months | Type: Die on<br>tape in<br>ring-pack<br>Storage time:<br>< 3 months |  |  |

#### **ORDERING INFORMATION**

| Device          | Inking? | Shipping           |

|-----------------|---------|--------------------|

| NGTD23T120F2WP  | Yes     | Bare Wafer in Jar  |

| NGTD23T120F2SWK | Yes     | Sawn Wafer on Tape |

## **ON Semiconductor®**

www.onsemi.com

V<sub>RCE</sub> = 1200 V I<sub>C</sub> = Limited by T<sub>J(max)</sub>

DIE OUTLINE

## NGTD23T120F2

#### **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = $25^{\circ}$ C, unless otherwise specified)

| Parameter                            | Test Conditions                                       | Symbol               | Min  | Тур  | Max | Units |

|--------------------------------------|-------------------------------------------------------|----------------------|------|------|-----|-------|

| STATIC CHARACTERISTICS               |                                                       |                      |      |      |     |       |

| Collector-Emitter Breakdown Voltage  | $V_{GE}$ = 0 V, I <sub>C</sub> = 500 $\mu$ A          | V <sub>(BR)CES</sub> | 1200 |      |     | V     |

| Collector-Emitter Saturation Voltage | $V_{GE}$ = 15 V, I <sub>C</sub> = 25 A                | V <sub>CE(sat)</sub> |      | 1.9  | 2.2 | V     |

| Gate-Emitter Threshold Voltage       | $V_{GE} = V_{CE}$ , $I_C = 400 \ \mu A$               | V <sub>GE(TH)</sub>  | 4.5  | 5.5  | 6.5 | V     |

| Collector-Emitter Cutoff Current     | $V_{GE} = 0 V, V_{CE} = 1200 V$                       | I <sub>CES</sub>     |      |      | 1.0 | mA    |

| Gate Leakage Current                 | $V_{GE} = 20 \text{ V}, \text{ V}_{CE} = 0 \text{ V}$ | I <sub>GES</sub>     |      |      | 200 | nA    |

| DYNAMIC CHARACTERISTICS              |                                                       |                      |      |      |     |       |

| land Oracitana                       |                                                       | 0                    |      | 5050 |     |       |

| Input Capacitance            |                                                             | Cies             | 5250 | pF |

|------------------------------|-------------------------------------------------------------|------------------|------|----|

| Output Capacitance           | V <sub>CE</sub> = 20 V, V <sub>GE</sub> = 0 V, f = 1<br>MHz | C <sub>oes</sub> | 170  | pF |

| Reverse Transfer Capacitance |                                                             | C <sub>res</sub> | 100  | pF |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

### DIE LAYOUT

$\begin{array}{l} \mathsf{E}=\mathsf{Emitter} \ \mathsf{pad} \\ \mathsf{G}=\mathsf{Gate} \ \mathsf{pad} \\ \mathsf{All} \ \mathsf{dimensions} \ \mathsf{in} \ \mathsf{\mu}\mathsf{m} \end{array}$