# Octal 3-State Inverting Buffer/Line Driver/Line Receiver

# High–Performance Silicon–Gate CMOS

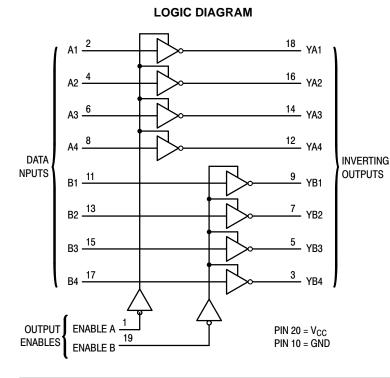

The MC74HC240A is identical in pinout to the LS240. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.

This octal noninverting buffer/line driver/line receiver is designed to be used with 3-state memory address drivers, clock drivers, and other sub-oriented systems. The device has inverting outputs and two active-low output enables.

The HC240A is similar in function to the HC244A.

#### Features

- Output Drive Capability: 15 LSTTL Loads

- Outputs Directly Interface to CMOS, NMOS, and TTL

- Operating Voltage Range: 2.0 to 6.0 V

- Low Input Current: 1 µA

- High Noise Immunity Characteristic of CMOS Devices

- In Compliance with the Requirements Defined by JEDEC Standard No. 7 A

- Chip Complexity: 120 FETs or 30 Equivalent Gates

- NLV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP Capable

- These Devices are Pb–Free, Halogen Free and are RoHS Compliant

## **ON Semiconductor®**

http://onsemi.com

### **PIN ASSIGNMENT**

| ۵ | 1● | :                                                    | 20                                                                                                                 | þ                                                                                                                                                                                                                       | V <sub>CC</sub>                                                                                                                                                                                                                                                                         |

|---|----|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ۵ | 2  |                                                      | 19                                                                                                                 | þ                                                                                                                                                                                                                       | ENABLE B                                                                                                                                                                                                                                                                                |

| Q | 3  |                                                      | 18                                                                                                                 | þ                                                                                                                                                                                                                       | YA1                                                                                                                                                                                                                                                                                     |

| q | 4  |                                                      | 17                                                                                                                 |                                                                                                                                                                                                                         | B4                                                                                                                                                                                                                                                                                      |

| Q | 5  |                                                      | 16                                                                                                                 |                                                                                                                                                                                                                         | YA2                                                                                                                                                                                                                                                                                     |

| C | 6  |                                                      | 15                                                                                                                 | þ                                                                                                                                                                                                                       | B3                                                                                                                                                                                                                                                                                      |

| C | 7  |                                                      | 14                                                                                                                 | þ                                                                                                                                                                                                                       | YA3                                                                                                                                                                                                                                                                                     |

| q | 8  |                                                      | 13                                                                                                                 |                                                                                                                                                                                                                         | B2                                                                                                                                                                                                                                                                                      |

| C | 9  |                                                      | 12                                                                                                                 | þ                                                                                                                                                                                                                       | YA4                                                                                                                                                                                                                                                                                     |

| ۵ | 10 |                                                      | 11                                                                                                                 | þ                                                                                                                                                                                                                       | B1                                                                                                                                                                                                                                                                                      |

|   | 0  | C 2<br>C 3<br>C 4<br>C 5<br>C 6<br>C 7<br>C 8<br>C 9 | <ul> <li>[ 2</li> <li>[ 3</li> <li>[ 4</li> <li>[ 5</li> <li>[ 6</li> <li>[ 7</li> <li>[ 8</li> <li>[ 9</li> </ul> | []       2       19         []       3       18         []       4       17         []       5       16         []       6       15         []       7       14         []       8       13         []       9       12 | []       2       19       ]         []       3       18       ]         []       4       17       ]         []       5       16       ]         []       6       15       ]         []       7       14       ]         []       8       13       ]         []       9       12       ] |

| FUNCTION TABLE        |        |        |  |  |  |

|-----------------------|--------|--------|--|--|--|

| Inpu                  | Inputs |        |  |  |  |

| Enable A,<br>Enable B | А, В   | YA, YB |  |  |  |

| L                     | L      | Н      |  |  |  |

| L                     | н      | L      |  |  |  |

| Н                     | Х      | Z      |  |  |  |

| 7 bish issued as a    |        |        |  |  |  |

Z = high impedance

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.

### MAXIMUM RATINGS

| Symbol           | Parameter                                                                  | Value                         | Unit |

|------------------|----------------------------------------------------------------------------|-------------------------------|------|

| V <sub>CC</sub>  | DC Supply Voltage (Referenced to GND)                                      | -0.5 to +7.0                  | V    |

| V <sub>in</sub>  | DC Input Voltage (Referenced to GND)                                       | –0.5 to V <sub>CC</sub> + 0.5 | V    |

| Vout             | DC Output Voltage (Referenced to GND)                                      | –0.5 to V <sub>CC</sub> + 0.5 | V    |

| l <sub>in</sub>  | DC Input Current, per Pin                                                  | ±20                           | mA   |

| l <sub>out</sub> | DC Output Current, per Pin                                                 | ±35                           | mA   |

| I <sub>CC</sub>  | DC Supply Current, $V_{CC}$ and GND Pins                                   | ±75                           | mA   |

| PD               | Power Dissipation in Still Air, SOIC Package†<br>TSSOP Package†            | 500<br>450                    | mW   |

| T <sub>stg</sub> | Storage Temperature                                                        | – 65 to + 150                 | °C   |

| TL               | Lead Temperature, 1 mm from Case for 10 Seconds<br>(SOIC or TSSOP Package) | 260                           | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range GND  $\leq$  ( $V_{in}$  or  $V_{out}$ )  $\leq$  V<sub>CC</sub>.

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or  $V_{CC}$ ). Unused outputs must be left open.

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

†Derating: SOIC Package: -7 mW/°C from 65° to 125°C

TSSOP Package: -6.1 mW/°C from 65° to 125°C

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                             | Parameter                                            |                                     | Min         | Max                | Unit |

|------------------------------------|------------------------------------------------------|-------------------------------------|-------------|--------------------|------|

| V <sub>CC</sub>                    | DC Supply Voltage (Referenced to GND)                |                                     | 2.0         | 6.0                | V    |

| V <sub>in</sub> , V <sub>out</sub> | DC Input Voltage, Output Voltage (Referenced to GND) |                                     | 0           | V <sub>CC</sub>    | V    |

| T <sub>A</sub>                     | Operating Temperature, All Package Types             |                                     | -55         | +125               | °C   |

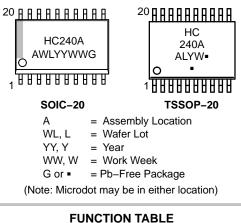

| t <sub>r</sub> , t <sub>f</sub>    | (Figure 1) V <sub>C0</sub>                           | c = 2.0 V<br>c = 4.5 V<br>c = 6.0 V | 0<br>0<br>0 | 1000<br>500<br>400 | ns   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

|                 |                                  |                                                  |                 | Guaranteed Limit |        | mit     |      |

|-----------------|----------------------------------|--------------------------------------------------|-----------------|------------------|--------|---------|------|

|                 |                                  |                                                  | V <sub>CC</sub> | -55 to           |        |         |      |

| Symbol          | Parameter                        | Test Conditions                                  | v               | 25°C             | ≤ 85°C | ≤ 125°C | Unit |

| VIH             | Minimum High-Level Input Voltage | $V_{out} = V_{CC} - 0.1 V$                       | 2.0             | 1.5              | 1.5    | 1.5     | V    |

|                 |                                  | $ I_{out}  \le 20 \ \mu A$                       | 3.0             | 2.1              | 2.1    | 2.1     |      |

|                 |                                  |                                                  | 4.5             | 3.15             | 3.15   | 3.15    |      |

|                 |                                  |                                                  | 6.0             | 4.2              | 4.2    | 4.2     |      |

| VIL             | Maximum Low–Level Input Voltage  | $V_{out} = 0.1 V$                                | 2.0             | 0.5              | 0.5    | 0.5     | V    |

|                 |                                  | $ I_{out}  \le 20 \ \mu A$                       | 3.0             | 0.9              | 0.9    | 0.9     |      |

|                 |                                  |                                                  | 4.5             | 1.35             | 1.35   | 1.35    |      |

|                 |                                  |                                                  | 6.0             | 1.8              | 1.8    | 1.8     |      |

| V <sub>OH</sub> | Minimum High–Level Output        | $V_{in} = V_{IH}$                                | 2.0             | 1.9              | 1.9    | 1.9     | V    |

|                 | Voltage                          | $ I_{out}  \le 20 \mu A$                         | 4.5             | 4.4              | 4.4    | 4.4     |      |

|                 |                                  |                                                  | 6.0             | 5.9              | 5.9    | 5.9     |      |

|                 |                                  | $V_{in} = V_{IH}$ $ I_{out}  \le 2.4 \text{ mA}$ | 3.0             | 2.48             | 2.34   | 2.2     |      |

|                 |                                  | $ I_{out}  \le 6.0 \text{ mA}$                   | 4.5             | 3.98             | 3.84   | 3.7     |      |

|                 |                                  | $ I_{out}  \le 7.8 \text{ mA}$                   | 6.0             | 5.48             | 5.34   | 5.2     |      |

| V <sub>OL</sub> | Maximum Low-Level Output         | $V_{in} = V_{IL}$                                | 2.0             | 0.1              | 0.1    | 0.1     | V    |

|                 | Voltage                          | $ I_{out}  \le 20 \mu A$                         | 4.5             | 0.1              | 0.1    | 0.1     |      |

|                 |                                  |                                                  | 6.0             | 0.1              | 0.1    | 0.1     |      |

|                 |                                  | $V_{in} = V_{IL}$ $ I_{out}  \le 2.4 \text{ mA}$ | 3.0             | 0.26             | 0.33   | 0.4     |      |

|                 |                                  | $ I_{out}  \le 6.0 \text{ mA}$                   | 4.5             | 0.26             | 0.33   | 0.4     |      |

|                 |                                  | $ I_{out}  \le 7.8 \text{ mA}$                   | 6.0             | 0.26             | 0.33   | 0.4     |      |

| l <sub>in</sub> | Maximum Input Leakage Current    | V <sub>in</sub> = V <sub>CC</sub> or GND         | 6.0             | ±0.1             | ±1.0   | ±1.0    | μΑ   |

| I <sub>OZ</sub> | Maximum Three-State Leakage      | Output in High-Impedance State                   | 6.0             | ± 0.5            | ± 5.0  | ± 10    | μA   |

|                 | Current                          | $V_{in} = V_{IL} \text{ or } V_{IH}$             |                 |                  |        |         |      |

|                 |                                  | $V_{out} = V_{CC}$ or GND                        |                 |                  |        |         |      |

| I <sub>CC</sub> | Maximum Quiescent Supply         | $V_{in} = V_{CC}$ or GND                         | 6.0             | 4.0              | 40     | 160     | μA   |

|                 | Current (per Package)            | $I_{out} = 0 \ \mu A$                            |                 |                  |        |         |      |

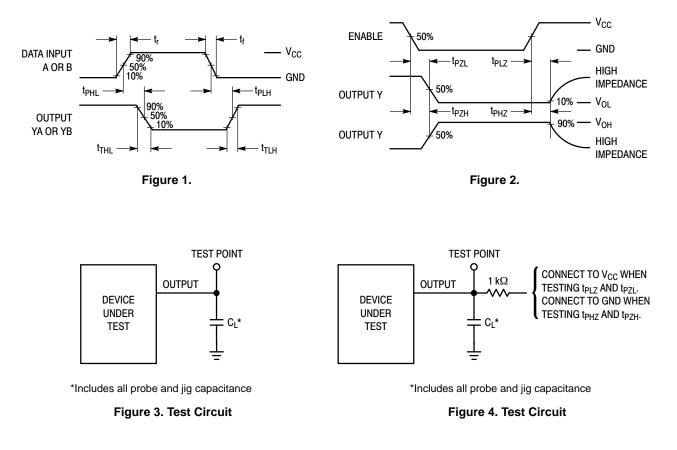

# AC ELECTRICAL CHARACTERISTICS (CL = 50 pF, Input $t_r = t_f = 6 \text{ ns}$ )

|                                        |                                                                            |                          | Gu                                      | Guaranteed Limit      |                       |      |

|----------------------------------------|----------------------------------------------------------------------------|--------------------------|-----------------------------------------|-----------------------|-----------------------|------|

| Symbol                                 | Parameter                                                                  | v <sub>cc</sub><br>v     | –55 to<br>25°C                          | ≤ 85°C                | ≤ 125°C               | Unit |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Maximum Propagation Delay, A to YA or B to YB<br>(Figures 1 and 3)         | 2.0<br>3.0<br>4.5<br>6.0 | 80<br>40<br>16<br>14                    | 100<br>50<br>20<br>17 | 120<br>60<br>24<br>20 | ns   |

| t <sub>PLZ</sub> ,<br>t <sub>PHZ</sub> | Maximum Propagation Delay, Output Enable to YA or YB (Figures 2 and 4)     | 2.0<br>3.0<br>4.5<br>6.0 | 110<br>60<br>22<br>19                   | 140<br>70<br>28<br>24 | 165<br>80<br>33<br>28 | ns   |

| t <sub>PZL</sub> ,<br>t <sub>PZH</sub> | Maximum Propagation Delay, Output Enable to YA or YB (Figures 2 and 4)     | 2.0<br>3.0<br>4.5<br>6.0 | 110<br>60<br>22<br>19                   | 140<br>70<br>28<br>24 | 165<br>80<br>33<br>28 | ns   |

| t <sub>TLH</sub> ,<br>t <sub>THL</sub> | Maximum Output Transition Time, Any Output<br>(Figures 1 and 3)            | 2.0<br>3.0<br>4.5<br>6.0 | 60<br>23<br>12<br>10                    | 75<br>27<br>15<br>13  | 90<br>32<br>18<br>15  | ns   |

| C <sub>in</sub>                        | Maximum Input Capacitance                                                  | -                        | 10                                      | 10                    | 10                    | pF   |

| C <sub>out</sub>                       | Maximum Three–State Output Capacitance<br>(Output in High–Impedance State) | -                        | 15                                      | 15                    | 15                    | pF   |

|                                        |                                                                            |                          | Typical @ 25°C, V <sub>CC</sub> = 5.0 V |                       |                       |      |

| C <sub>PD</sub>                        | Power Dissipation Capacitance (Per Transceiver Channel)*                   |                          |                                         | 32                    |                       | pF   |

|                 |                                                          | Typical @ 25°C, V <sub>CC</sub> = 5.0 V |    |

|-----------------|----------------------------------------------------------|-----------------------------------------|----|

| C <sub>PD</sub> | Power Dissipation Capacitance (Per Transceiver Channel)* | 32                                      | pF |

| *               | $d_{ata}$                                                |                                         |    |

\* Used to determine the no–load dynamic power consumption:  $P_D = C_{PD} V_{CC}^2 f + I_{CC} V_{CC}$ .

#### SWITCHING WAVEFORMS

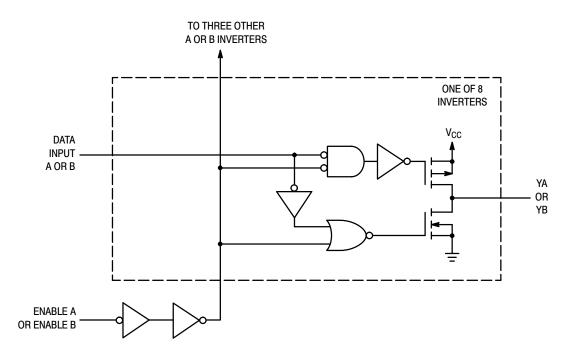

#### **PIN DESCRIPTIONS**

#### INPUTS

#### A1, A2, A3, A4, B1, B2, B3, B4 (Pins 2, 4, 6, 8, 11, 13, 15, 17)

Data input pins. Data on these pins appear in inverted form on the corresponding Y outputs, when the outputs are enabled.

#### CONTROLS

#### Enable A, Enable B (Pins 1, 19)

Output enables (active-low). When a low level is applied to these pins, the outputs are enabled and the devices

function as inverters. When a high level is applied, the outputs assume the high–impedance state.

#### OUTPUTS

#### YA1, YA2, YA3, YA4, YB1, YB2, YB3, YB4 (Pins 18, 16, 14, 12, 9, 7, 5, 3)

Device outputs. Depending upon the state of the output–enable pins, these outputs are either inverting outputs or high–impedance outputs.

#### LOGIC DETAIL

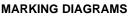

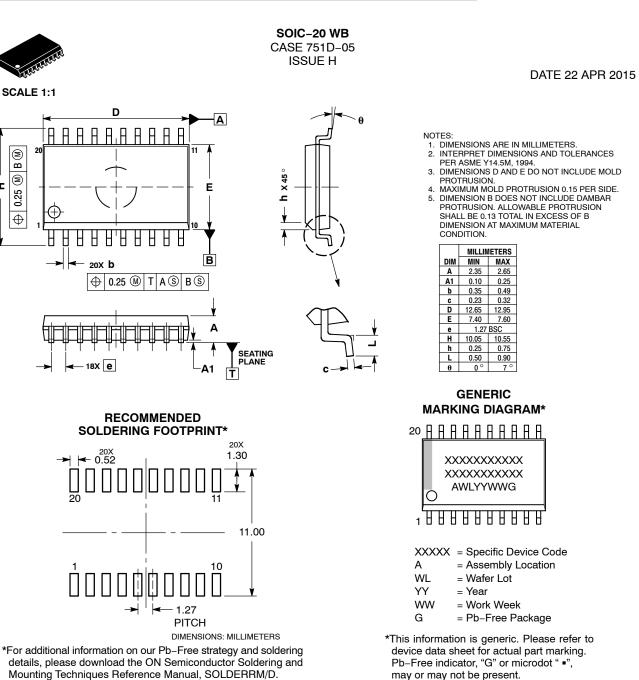

#### **ORDERING INFORMATION**

| Device            | Package                              | Shipping <sup>†</sup> |

|-------------------|--------------------------------------|-----------------------|

| MC74HC240ADWG     | SOIC-20 WIDE<br>(Pb-Free)            | 38 Units / Rail       |

| NVL74HC240ADWG*   | SOIC-20 WIDE 38 Units /<br>(Pb-Free) |                       |

| MC74HC240ADWR2G   | SOIC-20 WIDE<br>(Pb-Free)            | 1000 Tape & Reel      |

| NVL74HC240ADWR2G* | SOIC-20 WIDE<br>(Pb-Free)            | 1000 Tape & Reel      |

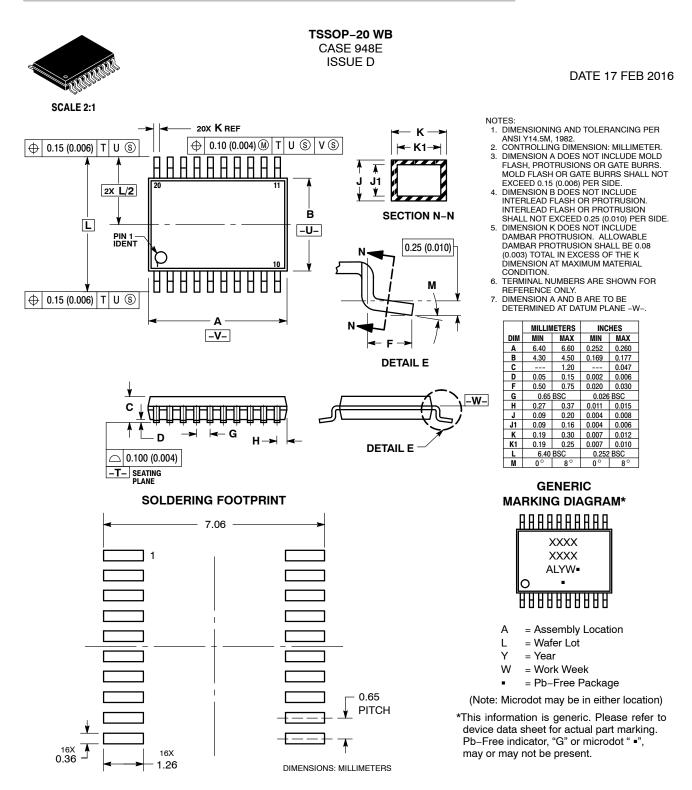

| MC74HC240ADTR2G   | TSSOP-20<br>(Pb-Free)                | 2500 Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*NLV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP

Capable

т

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 98ASB42343B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DESCRIPTION: SOIC-20 WB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             | PAGE 1 OF 1                                                                                                                                                                         |  |  |  |  |  |

| ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights nor the |             |                                                                                                                                                                                     |  |  |  |  |  |

| DOCUMENT NUMBER: | 98ASH70169A | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | TSSOP-20 WB |                                                                                                                                                                                   | PAGE 1 OF 1 |  |  |

|                  |             |                                                                                                                                                                                   |             |  |  |

ON Semiconductor and unarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights or the rights of others.