# **PCF8537**

# Industrial LCD driver for multiplex rates up to 1:8

Rev. 1 — 31 May 2012

**Product data sheet**

# 1. General description

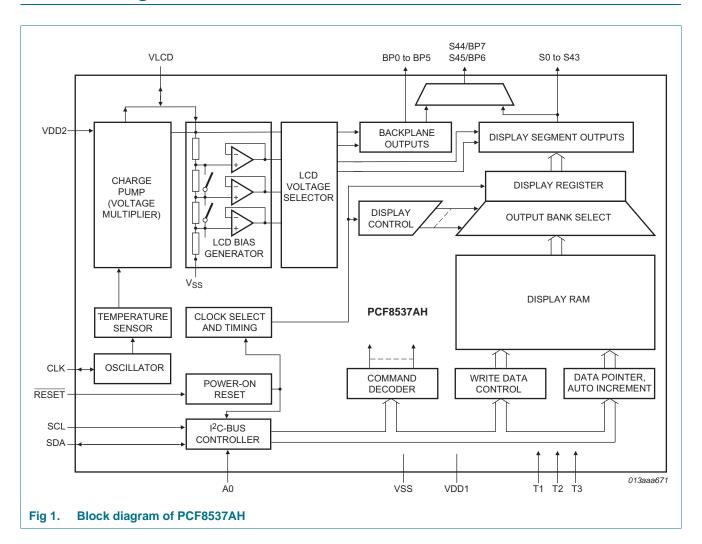

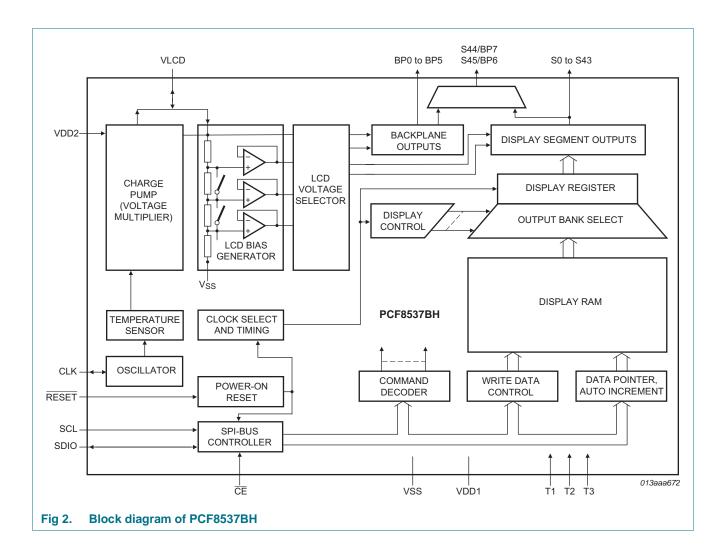

The PCF8537 is a fully featured Liquid Crystal Display (LCD)¹ driver, specifically designed for high-contrast Vertical Alignment (VA) LCD with multiplex rates up to 1:8. It generates the drive signals for any static or multiplexed LCD containing up to eight backplanes, 46 segments, and up to 352 elements. The PCF8537 features an internal charge pump with internal capacitors for on-chip generation of the LCD driving voltage. To ensure an optimal and stable contrast over the full temperature range, the PCF8537 offers a programmable temperature compensation of the LCD supply voltage. The PCF8537 can be easily connected to a microcontroller by either the two-line I²C-bus (PCF8537AH) or a three-line bidirectional SPI-bus (PCF8537BH).

# 2. Features and benefits

- Low-power single-chip LCD controller and driver

- 352 elements allowing to drive:

- up to 44 7-segment alphanumeric characters

- up to 22 14-segment alphanumeric characters

- Selectable backplane drive configuration: static, 2, 4, 6, or 8 backplane multiplexing

- Software programmable internal charge pump for on-chip LCD voltage generation up to 9 V with internal capacitors

- 400 kHz I<sup>2</sup>C-bus interface (PCF8537AH)

- 5 MHz SPI-bus interface (PCF8537BH)

- Programmable temperature compensation of V<sub>LCD</sub> in four regions

- Selectable display bias configuration

- Wide range for digital power supply: from 1.8 V to 5.5 V

- Wide LCD supply range: from 2.5 V for low threshold LCDs and up to 9.0 V for high threshold twisted nematic LCDs

- Display memory bank switching in static, duplex, and quadruplex drive modes

- 352-bit RAM for display data storage

- Programmable frame frequency in the range of 60 Hz to 300 Hz in steps of 10 Hz; factory calibrated

- Integrated temperature sensor with temperature readout

- On chip calibration of internal oscillator frequency and V<sub>LCD</sub>

- Manufactured in silicon gate CMOS process

<sup>1.</sup> The definition of the abbreviations and acronyms used in this data sheet can be found in Section 17.

# Industrial LCD driver for multiplex rates up to 1:8

# 3. Applications

- White goods

- Handheld electronics

- Battery operated equipment

- Machine control systems

- Measuring equipment

- Information boards

- Panels

- Consumer

- Industrial

- Medical and health care

# 4. Ordering information

#### Table 1. Ordering information

| Type number | Interface type       | Package |                                                                             |          |

|-------------|----------------------|---------|-----------------------------------------------------------------------------|----------|

|             |                      | Name    | Description                                                                 | Version  |

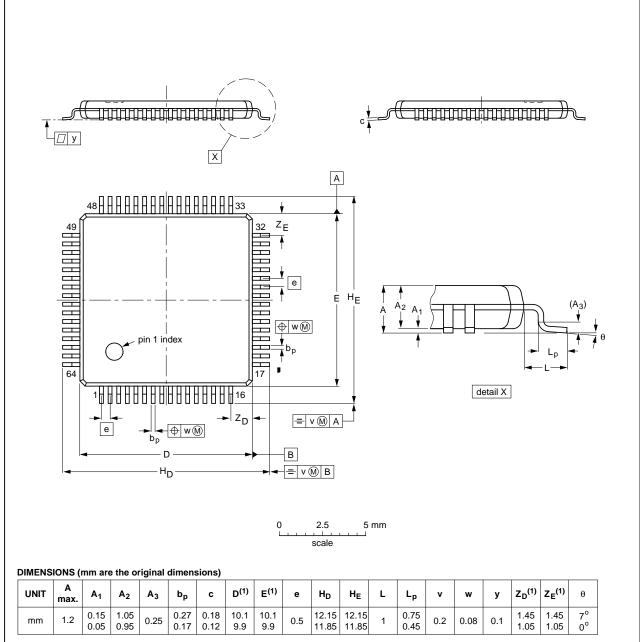

| PCF8537AH/1 | I <sup>2</sup> C-bus | TQFP64  | plastic thin quad flat package; 64 leads; body $10 \times 10 \times 1.0$ mm | SOT357-1 |

| PCF8537BH/1 | SPI-bus              | TQFP64  | plastic thin quad flat package; 64 leads; body $10 \times 10 \times 1.0$ mm | SOT357-1 |

# 5. Marking

Table 2. Marking codes

| Type number | Marking code |

|-------------|--------------|

| PCF8537AH/1 | PCF8537AH    |

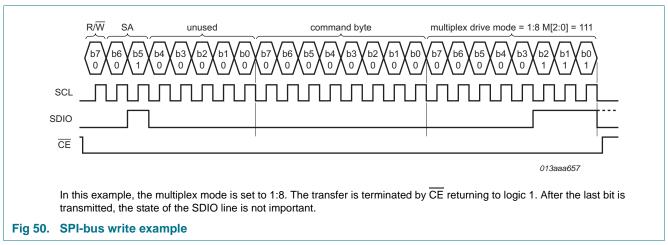

| PCF8537BH/1 | PCF8537BH    |

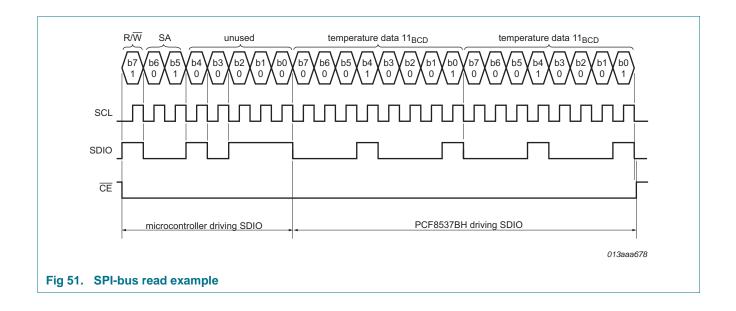

# Industrial LCD driver for multiplex rates up to 1:8

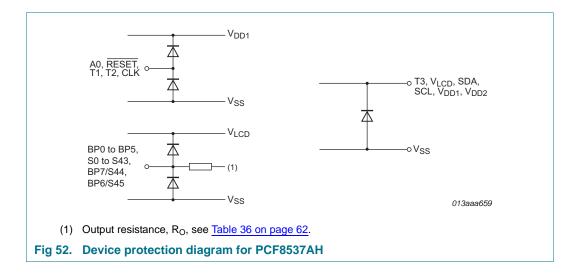

# 6. Block diagram

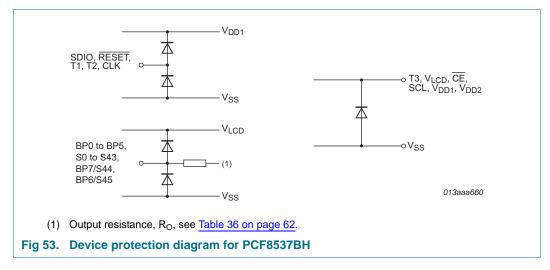

# Industrial LCD driver for multiplex rates up to 1:8

Industrial LCD driver for multiplex rates up to 1:8

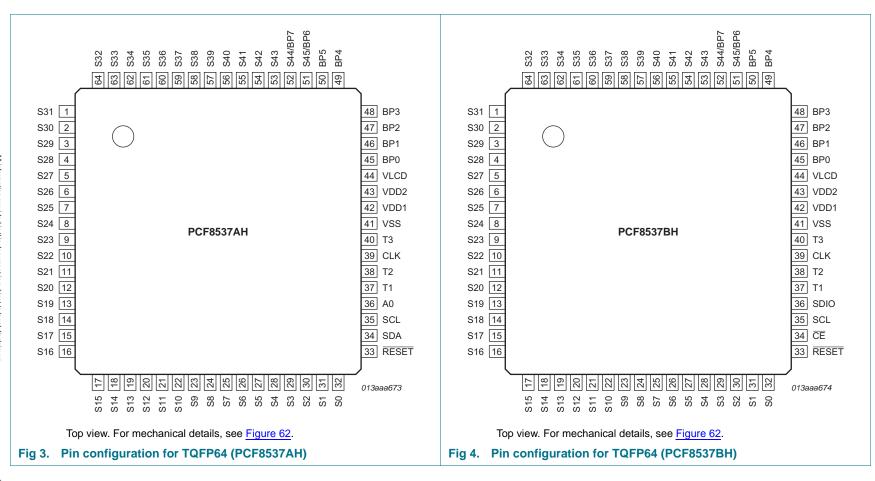

# 7.1 Pinning

31 May 2012

# Industrial LCD driver for multiplex rates up to 1:8

# 7.2 Pin description

Table 3. Pin description of PCF8537AH and PCF8537BH

| Pin           | Symbol     |           | Туре         | Description                                                |  |

|---------------|------------|-----------|--------------|------------------------------------------------------------|--|

|               | PCF8537AH  | PCF8537BH |              |                                                            |  |

| 1 to 32       | S31        | to S0     | output       | LCD segments                                               |  |

| 33            | RES        | SET       | input        | active low reset input                                     |  |

| 34            | SDA        |           | input/output | I <sup>2</sup> C-bus serial data                           |  |

|               |            | CE        | input        | SPI-bus chip enable - active LOW                           |  |

| 35            | SCL        |           | input        | I <sup>2</sup> C-bus serial clock                          |  |

|               |            | SCL       | input        | SPI-bus serial clock                                       |  |

| 36            | A0         |           | input        | I <sup>2</sup> C-bus slave address selection               |  |

|               |            | SDIO      | input/output | SPI-bus serial data                                        |  |

| 37, 38,<br>40 | T1 to T3   |           | input        | test pins; must be tied to V <sub>SS</sub> in applications |  |

| 39            | CLK        |           | input/output | internal oscillator output, external oscillator input      |  |

| 41            | VS         | SS        | supply       | ground supply                                              |  |

| 42            | VD         | D1        | supply       | supply voltage 1                                           |  |

| 43            | VD         | D2        | supply       | supply voltage 2                                           |  |

| 44            | VLCD[1]    |           | supply       | LCD supply[2]                                              |  |

| 45 to 50      | BP0 to BP5 |           | output       | LCD backplanes                                             |  |

| 51            | S45/BP6    |           | output       | LCD segments for 1:6 multiplex drive mode;                 |  |

| 52            | S44/BP7    |           | output       | LCD backplanes for 1:8 multiplex drive mode                |  |

| 53 to 64      | S43 t      | o S32     | output       | LCD segments                                               |  |

<sup>[1]</sup>  $V_{LCD}$  must be equal to or greater than  $V_{DD2}$ .

<sup>[2]</sup> When the internal V<sub>LCD</sub> generation is used, this pin drives the V<sub>LCD</sub> voltage. In this case pin VLCD is an output. When the external supply is requested, then pin VLCD is an input and V<sub>LCD</sub> can be supplied on it. In this case, the internal charge pump must be disabled (see <u>Table 8</u>).

# Industrial LCD driver for multiplex rates up to 1:8

# 8. Functional description

The PCF8537 is a versatile peripheral device designed to interface any microcontroller to a wide variety of LCDs. It can directly drive any static or multiplexed LCD containing up to 352 elements.

#### 8.1 Commands of PCF8537

The commands to control the PCF8537 are defined in <u>Table 4</u>. Any other combinations of operation code bits that are not mentioned in this document can lead to undesired operation modes of PCF8537.

**Table 4. Commands of PCF8537** The bit labeled with - is not implemented.

| Command name      | RS[1] | Bits  |    |       |       |        |        |        |     | Reference             |

|-------------------|-------|-------|----|-------|-------|--------|--------|--------|-----|-----------------------|

|                   |       | 7     | 6  | 5     | 4     | 3      | 2      | 1      | 0   |                       |

| Initialize        | 0     | 0     | 0  | 1     | 1     | 1      | 0      | 1      | 0   | Section 8.1.1         |

| OTP-refresh       | 0     | 1     | 1  | 0     | 1     | 0      | 0      | 0      | 0   | Section 8.1.2         |

| Oscillator-ctrl   | 0     | 1     | 1  | 0     | 0     | 1      | 1      | COE    | OSC | Section 8.1.3         |

| Charge-pump-ctrl  | 0     | 1     | 1  | 0     | 0     | 0      | 0      | CPE    | CPC | Section 8.1.4         |

| Temp-msr-ctrl     | 0     | 1     | 1  | 0     | 0     | 1      | 0      | TCE    | TME | Section 8.1.5         |

| Temp-comp         | 0     | 0     | 0  | 0     | 1     | 1      | SLA[2: | 0]     |     | Section 8.1.6         |

|                   | 0     | 0     | 0  | 1     | 0     | 0      | SLB[2: | 0]     |     |                       |

|                   | 0     | 0     | 0  | 1     | 0     | 1      | SLC[2: | 0]     |     |                       |

|                   | 0     | 0     | 0  | 1     | 1     | 0      | SLD[2: | 0]     |     |                       |

| Set-VPR           | 0     | 0     | 1  | 0     | 0     | VPR[7: | 4]     |        |     | Section 8.1.7         |

|                   | 0     | 0     | 1  | 0     | 1     | VPR[3: | 0]     |        |     |                       |

| Display-enable    | 0     | 0     | 0  | 1     | 1     | 1      | 0      | 0      | E   | Section 8.1.8         |

| Set-MUX-mode      | 0     | 0     | 0  | 0     | 0     | 0      | M[2:0] |        |     | Section 8.1.9         |

| Set-bias-mode     | 0     | 1     | 1  | 0     | 0     | 0      | 1      | B[1:0] |     | <u>Section 8.1.10</u> |

| Load-data-pointer | 0     | 1     | 0  | P[5:0 | ]     |        |        |        |     | <u>Section 8.1.11</u> |

| Frame-frequency   | 0     | 0     | 1  | 1     | F[4:0 | ]      |        |        |     | <u>Section 8.1.12</u> |

| Bank-select       | 0     | 0     | 0  | 0     | 0     | 1      | 0      | IBS    | OBS | <u>Section 8.1.13</u> |

| Write-RAM-data    | 1     | B[7:0 | ]  |       |       |        |        |        |     | <u>Section 8.1.14</u> |

| Temp-read         | -     | TD[7: | 0] |       |       |        |        |        |     | <u>Section 8.1.15</u> |

| Invmode_ctrl      | 0     | 1     | 1  | 0     | 1     | 0      | 1      | LF     | 0   | Section 8.1.16        |

| Temp-filter       | 0     | 1     | 1  | 0     | 1     | 0      | 0      | 1      | TFE | <u>Section 8.1.17</u> |

<sup>[1]</sup> For further information about the register selection bit, see  $\underline{\text{Table 30 on page 52}}$ .

#### Industrial LCD driver for multiplex rates up to 1:8

#### 8.1.1 Command: Initialize

This command generates a chip-wide reset which resets all command values to their default values. After this command is sent, it is possible to send additional commands without the need to re-initialize the interface. The reset takes 100 ns to complete.

**Table 5. Initialize - initialize command bit description** For further information, see Section 8.2 on page 17.

| Bit    | Symbol | Binary value | Description |

|--------|--------|--------------|-------------|

| 7 to 0 | -      | 00111010     | fixed value |

#### 8.1.2 Command: OTP-refresh

During production and testing of the device, each IC is calibrated to achieve the specified accuracy of  $V_{LCD}$ , the frame frequency, and the temperature measurement. This calibration is performed on EPROM cells called One Time Programmable (OTP) cells.

The device reads these cells every time at power-on, after a reset, and every time when the initialize command or the OTP-refresh command is sent.

Remark: It is recommended not to enter power-down mode during the OTP refresh cycle.

Table 6. OTP-refresh - OTP-refresh command bit description

| Bit    | Symbol | Binary value | Description |

|--------|--------|--------------|-------------|

| 7 to 0 | -      | 11010000     | fixed value |

# 8.1.3 Command: Oscillator-ctrl

The Oscillator-ctrl command switches between internal and external oscillator and enables or disables the pin CLK.

**Table 7.** Oscillator-ctrl - oscillator control command bit description For further information, see Section 8.1.3.1.

| Bit    | Symbol | Binary value | Description                                                                           |

|--------|--------|--------------|---------------------------------------------------------------------------------------|

| 7 to 2 | -      | 110011       | fixed value                                                                           |

| 1      | COE    |              | control pin CLK                                                                       |

|        |        | O <u>[1]</u> | clock signal not available on pin CLK; pin CLK is in 3-state and may be left floating |

|        |        | 1            | clock signal available on pin CLK                                                     |

| 0      | OSC    |              | oscillator source                                                                     |

|        |        | 0[1]         | internal oscillator used                                                              |

|        |        | 1            | external oscillator used;<br>pin CLK becomes an input                                 |

<sup>[1]</sup> Default value.

#### 8.1.3.1 Oscillator

The internal logic and LCD drive signals of the PCF8537 are timed either by the built-in oscillator or from an external clock.

#### Industrial LCD driver for multiplex rates up to 1:8

#### 8.1.3.2 Internal oscillator

When the internal oscillator is used, it is possible to make the clock signal available on pin CLK by using the Oscillator-ctrl command (see <u>Table 7</u>). If this is not intended, the pin CLK should be left open. At power-on the signal at pin CLK is disabled and pin CLK is in 3-state.

If the internal charge pump is enabled, then the internal oscillator starts and is used to run the charge pump. An external oscillator can still be applied for driving the display waveforms.

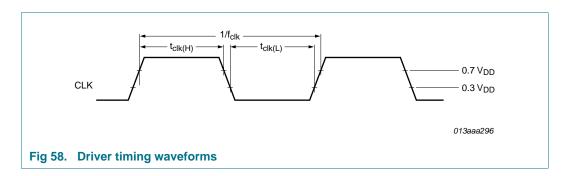

The duty cycle of the output clock provided on the CLK pin is not always 50 : 50. <u>Table 17</u> on page 13 shows the expected duty cycle for each of the chosen frame frequencies.

#### 8.1.3.3 External clock

In applications where an external clock must be applied to the PCF8537, bit OSC (see Table 7) must be set logic 1. In this case, pin CLK becomes an input.

The CLK signal is a signal that is fed into the  $V_{DD1}$  domain. Therefore it must have an amplitude equal to the  $V_{DD1}$  voltage supplied to the chip and be referenced to  $V_{SS}$ .

The clock frequency (f<sub>clk</sub>) determines the LCD frame frequency.

**Remark:** If an external clock is used then this clock signal must always be supplied to the device. Removing the clock can freeze the LCD in a DC state. Removal of the clock is possible when following the correct procedures (see <u>Figure 11 on page 21</u> and <u>Figure 12 on page 22</u>).

#### 8.1.4 Command: Charge-pump-ctrl

The Charge-pump-ctrl command enables or disables the internal  $V_{LCD}$  generation and controls the charge pump voltage multiplier setting.

Table 8. Charge-pump-ctrl - charge pump control command bit description For further information, see Table 11 on page 11 and Section 8.4.3 on page 26.

| Bit    | Symbol | Binary value | Description                                                                                        |

|--------|--------|--------------|----------------------------------------------------------------------------------------------------|

| 7 to 2 | -      | 110000       | fixed value                                                                                        |

| 1      | CPE    |              | charge pump switch                                                                                 |

|        |        | 0[1]         | charge pump disabled; no internal $V_{\text{LCD}}$ generation; external supply of $V_{\text{LCD}}$ |

|        |        | 1            | charge pump enabled                                                                                |

| 0      | CPC    |              | charge pump voltage multiplier setting                                                             |

|        |        | 0[1]         | $V_{LCD} = 2 \times V_{DD2}$                                                                       |

|        |        | 1            | $V_{LCD} = 3 \times V_{DD2}$                                                                       |

<sup>[1]</sup> Default value.

# Industrial LCD driver for multiplex rates up to 1:8

# 8.1.5 Command: Temp-msr-ctrl

The Temp-msr-ctrl command enables or disables the temperature measurement block and the temperature compensation of  $V_{\text{LCD}}$ .

Table 9. Temp-msr-ctrl - temperature measurement control command bit description For further information, see Section 8.4.4 on page 28.

| Bit    | Symbol | Binary value | Description                                              |

|--------|--------|--------------|----------------------------------------------------------|

| 7 to 2 | -      | 110010       | fixed value                                              |

| 1      | TCE    |              | temperature compensation switch                          |

|        |        | 0            | no temperature compensation of $V_{\text{LCD}}$ possible |

|        |        | 1[1]         | temperature compensation of $V_{\text{LCD}}$ possible    |

| 0      | TME    |              | temperature measurement switch                           |

|        |        | 0            | temperature measurement disabled:                        |

|        |        |              | no temperature readout possible                          |

|        |        | 1 <u>[1]</u> | temperature measurement enabled:                         |

|        |        |              | temperature readout possible                             |

<sup>[1]</sup> Default value.

#### 8.1.6 Command: Temp-comp

The Temp-comp command allows setting the temperature compensation coefficients for each of the temperature regions SFA to SFD. For further information, see <u>Section 8.4.4.2</u>.

**Table 10. Temp-comp - temperature compensation coefficients command** *For further information*, see <u>Section 8.4.4 on page 28</u>.

| Bit    | Symbol   | Binary value              | Description                                                              |

|--------|----------|---------------------------|--------------------------------------------------------------------------|

| SLA    |          |                           |                                                                          |

| 7 to 3 | -        | 00011                     | fixed value                                                              |

| 2 to 0 | SLA[2:0] | 000 <sup>[1]</sup> to 111 | temperature compensation coefficient SLA, see <u>Table 26 on page 30</u> |

| SLB    |          |                           |                                                                          |

| 7 to 3 | -        | 00100                     | fixed value                                                              |

| 2 to 0 | SLB[2:0] | 000 <sup>[1]</sup> to 111 | temperature compensation coefficient SLB, see Table 26 on page 30        |

| SLC    |          |                           |                                                                          |

| 7 to 3 | -        | 00101                     | fixed value                                                              |

| 2 to 0 | SLC[2:0] | 000 <sup>[1]</sup> to 111 | temperature compensation coefficient SLC, see <u>Table 26 on page 30</u> |

| SLD    |          |                           |                                                                          |

| 7 to 3 | -        | 00110                     | fixed value                                                              |

| 2 to 0 | SLD[2:0] | 000 <sup>[1]</sup> to 111 | temperature compensation coefficient SLD, see <u>Table 26 on page 30</u> |

<sup>[1]</sup> Default value.

# Industrial LCD driver for multiplex rates up to 1:8

#### 8.1.7 Command: Set-VPR

With these two instructions, it is possible to set the target  $V_{LCD}$  voltage for the internal charge pump.

Table 11. Set-VPR - set VPR command bit description

For further information, see Section 8.4.2 on page 25.

| Bit         Symbol         Binary value         Description           Set-VPR MSB         7 to 4 -         0100 fixed value           3 to 0 VPR[7:4]         0000[1] to 1111[2]         the four most significant bits of VPR[7:0]           Set-VPR LSB         7 to 4 -         0101 fixed value           3 to 0 VPR[3:0]         0000[1] to 1111[2]         the four least significant bits of VPR[7:0] |        |          |              |                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|--------------|---------------------------------------------|

| 7 to 4         -         0100         fixed value           3 to 0         VPR[7:4]         0000[1] to 1111[2]         the four most significant bits of VPR[7:0]           Set-VPR LSB           7 to 4         -         0101         fixed value           3 to 0         VPR[3:0]         0000[1] to         the four least significant bits of VPR[7:0]                                                 | Bit    | Symbol   | Binary value | Description                                 |

| 3 to 0       VPR[7:4]       0000[1] to 1111[2]       the four most significant bits of VPR[7:0]         Set-VPR LSB         7 to 4       -       0101       fixed value         3 to 0       VPR[3:0]       0000[1] to       the four least significant bits of VPR[7:0]                                                                                                                                     | Set-VP | R MSB    |              |                                             |

| 1111[2]         Set-VPR LSB         7 to 4 -       0101 fixed value         3 to 0 VPR[3:0]       0000[1] to the four least significant bits of VPR[7:0]                                                                                                                                                                                                                                                     | 7 to 4 | -        | 0100         | fixed value                                 |

| 7 to 4 - 0101 fixed value  3 to 0 VPR[3:0] 0000[1] to the four least significant bits of VPR[7:0]                                                                                                                                                                                                                                                                                                            | 3 to 0 | VPR[7:4] |              | the four most significant bits of VPR[7:0]  |

| 3 to 0 VPR[3:0] 0000[1] to the four least significant bits of VPR[7:0]                                                                                                                                                                                                                                                                                                                                       | Set-VP | PR LSB   |              |                                             |

| (e.e.)                                                                                                                                                                                                                                                                                                                                                                                                       | 7 to 4 | -        | 0101         | fixed value                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                              | 3 to 0 | VPR[3:0] |              | the four least significant bits of VPR[7:0] |

<sup>[1]</sup> Default value.

#### 8.1.8 Command: Display-enable

This command allows switching the display on and off. The possibility to disable and enable the display allows implementation of blinking the entire display under external control.

Table 12. Display-enable - display enable command bit description

| Bit    | Symbol | Binary value | Description                                                                                   |

|--------|--------|--------------|-----------------------------------------------------------------------------------------------|

| 7 to 1 | -      | 0011100      | fixed value                                                                                   |

| 0      | E      | 0[1]         | display disabled                                                                              |

|        |        |              | backplane and segment outputs are internally connected to $\ensuremath{\text{V}_{\text{SS}}}$ |

|        |        | 1            | display enabled                                                                               |

<sup>[1]</sup> Default value.

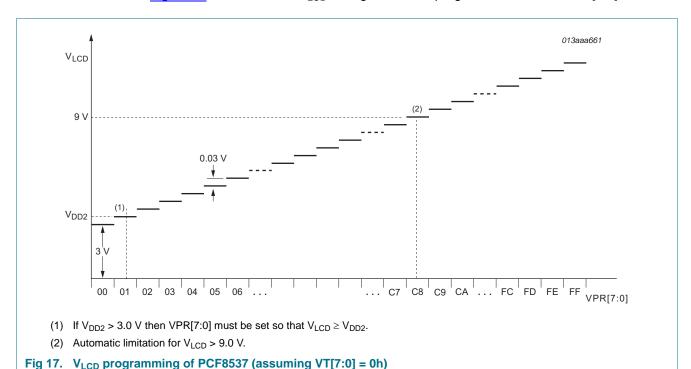

<sup>[2]</sup> VPR[7:0] = 0h results in  $V_{prog(LCD)} = 3 \text{ V}$ ; VPR[7:0] = C8h results in  $V_{prog(LCD)} = 9 \text{ V}$ .

#### Industrial LCD driver for multiplex rates up to 1:8

#### 8.1.9 Command: Set-MUX-mode

The multiplex drive mode is configured with the bits described in Table 13.

Table 13. Set-MUX-mode - set multiplex drive mode command bit description For further information, see Section 8.4.5 on page 31.

| Bit    | Symbol | Binary value                | Description                                           |

|--------|--------|-----------------------------|-------------------------------------------------------|

| 7 to 3 | -      | 00000                       | fixed value                                           |

| 2 to 0 | M[2:0] | 000[1]<br>011<br>101<br>111 | 1:8 multiplex drive mode 8 backplanes and 44 segments |

|        |        | 110                         | 1:6 multiplex drive mode 6 backplanes and 46 segments |

|        |        | 100                         | 1:4 multiplex drive mode 4 backplanes and 44 segments |

|        |        | 010                         | 1:2 multiplex drive mode 2 backplanes and 44 segments |

|        |        | 001                         | static drive mode 1 backplane and 44 segments         |

<sup>[1]</sup> Default value.

#### 8.1.10 Command: Set-bias-mode

The Set-bias-mode command allows setting the bias level.

Table 14. Set-bias-mode - set bias mode command bit description For further information, see Section 8.4.5 on page 31.

| Bit    | Symbol | Binary value            | Description               |

|--------|--------|-------------------------|---------------------------|

| 7 to 2 | -      | 110001                  | fixed value               |

| 1 to 0 | B[1:0] |                         | LCD bias configuration[1] |

|        |        | 00 <sup>[2]</sup><br>01 | 1⁄ <sub>4</sub> bias      |

|        |        | 11                      | 1/ <sub>3</sub> bias      |

|        |        | 10                      | $\frac{1}{2}$ bias        |

<sup>[1]</sup> Not applicable for static drive mode.

#### 8.1.11 Command: Load-data-pointer

The Load-data-pointer command defines the display RAM address where the following display data will be sent to.

Table 15. Load-data-pointer - load data pointer command bit description For further information, see <u>Section 8.8 on page 44</u>.

| Bit    | Symbol | Binary value | Description                   |

|--------|--------|--------------|-------------------------------|

| 7 to 6 | -      | 10           | fixed value                   |

| 5 to 0 | P[5:0] | 000000 to    | RAM address                   |

|        |        | 101101       | 6-bit binary value of 0 to 45 |

PCF8537

<sup>[2]</sup> Default value.

# Industrial LCD driver for multiplex rates up to 1:8

# 8.1.12 Command: Frame-frequency

With the Frame-frequency command, the frame frequency and the output clock frequency can be configured.

Table 16. Frame frequency - frame frequency and output clock frequency command bit description

| Bit    | Symbol | Binary value | Description                          |

|--------|--------|--------------|--------------------------------------|

| 7 to 5 | -      | 011          | fixed value                          |

| 4 to 0 | F[4:0] | see Table 17 | frame frequency values, see Table 17 |

Table 17. Frame frequency values

| F[4:0]         | Nominal frame<br>frequency f <sub>fr</sub> (Hz)[1] | Resultant output clock frequency, f <sub>clk(o)</sub> (Hz) | Duty cycle (%)[2] |

|----------------|----------------------------------------------------|------------------------------------------------------------|-------------------|

| 00000          | 60                                                 | 2880                                                       | 20 : 80           |

| 00001          | 70                                                 | 3360                                                       | 7:93              |

| 00010          | 80                                                 | 3840                                                       | 47 : 53           |

| 00011          | 91                                                 | 4368                                                       | 40 : 60           |

| 00100          | 100                                                | 4800                                                       | 33 : 67           |

| 00101          | 109                                                | 5232                                                       | 27 : 73           |

| 00110          | 120                                                | 5760                                                       | 20 : 80           |

| 00111          | 129.7                                              | 6226                                                       | 13 : 87           |

| 01000          | 141.2                                              | 6778                                                       | 5 : 95            |

| 01001          | 150                                                | 7200                                                       | 50 : 50           |

| 01010          | 160                                                | 7680                                                       | 47 : 53           |

| 01011          | 171.4                                              | 8227                                                       | 43 : 57           |

| 01100          | 177.8                                              | 8534                                                       | 41 : 59           |

| 01101          | 192                                                | 9216                                                       | 36 : 64           |

| 01110[3]       | 200                                                | 9600                                                       | 33 : 67           |

| 01111          | 208.7                                              | 10018                                                      | 30 : 70           |

| 10000          | 218.2                                              | 10474                                                      | 27 : 73           |

| 10001          | 228.6                                              | 10973                                                      | 23 : 77           |

| 10010          | 240                                                | 11 520                                                     | 20 : 80           |

| 10011          | 252.6                                              | 12125                                                      | 16 : 84           |

| 10100, 10101   | 266.7                                              | 12802                                                      | 10 : 90           |

| 10110, 10111   | 282.4                                              | 13555                                                      | 5 : 95            |

| 11000 to 11111 | 300                                                | 14400                                                      | 50 : 50           |

<sup>[1]</sup> Nominal frame frequency calculated for the default clock frequency of 9600 Hz.

<sup>[2]</sup> Duty cycle definition: % HIGH-level time : % LOW-level time.

<sup>[3]</sup> Default value.

#### Industrial LCD driver for multiplex rates up to 1:8

#### 8.1.12.1 Timing and frame frequency

The timing of the PCF8537 organizes the internal data flow of the device. This includes the transfer of display data from the display RAM to the display segment outputs. The timing also generates the LCD frame frequency. The frame frequency is a fixed division of the internal clock or of the frequency applied to pin CLK when an external clock is used.

When the internal clock is used, the clock frequency can be programmed by software such that the nominal frame frequency can be chosen in steps of 10 Hz in the range of 60 Hz to 300 Hz (see <u>Table 17</u>). Furthermore the nominal frame frequency is factory-calibrated with an accuracy of ±15 %.

When the internal clock is enabled at pin CLK by using bit COE, the duty ratio of the clock may change when choosing different values for the frame frequency prescaler. <u>Table 17</u> shows the different output duty ratios for each frame frequency prescaler setting.

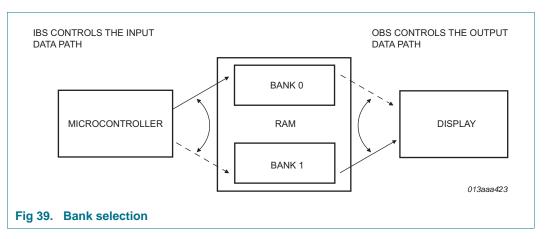

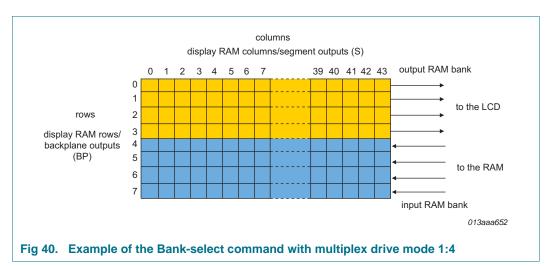

#### 8.1.13 Command: Bank-select

For the multiplex drive modes 1:4, 1:2, and the static drive mode, it is possible to write data to one area of the RAM while displaying from another. These areas are named RAM banks. There are two banks, 0 and 1. Figure 39 on page 50 and Figure 40 on page 50 show the concept. The Bank-select command controls where data is written to and where it is displayed from.

**Table 18.** Bank-select - bank select command bit description For further information, see Section 8.9 on page 50.

| Bit    | Symbol | Binary value | Description                              |

|--------|--------|--------------|------------------------------------------|

| 7 to 2 | -      | 000010       | fixed value                              |

| 1      | IBS    |              | selects RAM bank to write to             |

|        |        | 0[1]         | Bank 0                                   |

|        |        | 1            | Bank 1                                   |

| 0      | OBS    |              | selects RAM bank to read from to the LCD |

|        |        | 0[1]         | Bank 0                                   |

|        |        | 1            | Bank 1                                   |

<sup>[1]</sup> Default value.

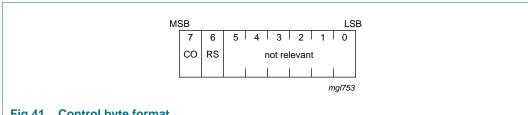

#### 8.1.14 Command: Write-RAM-data

By setting the RS bit of the control byte to logic 1, all data transferred is interpreted as RAM data and placed in the RAM in accordance with the current setting of the RAM address pointer (see Section 8.1.11 on page 12). Definition of the RS can be found in Table 30 on page 52.

**Remark:** After Power-On Reset (POR) the RAM content is random and should be brought to a defined status by clearing it (setting it to logic 0).

Table 19. Write-RAM-data - write RAM data command bit description For further information, see Section 8.8 on page 44.

| Bit    | Symbol | Binary value            | Description                       |

|--------|--------|-------------------------|-----------------------------------|

| 7 to 0 | B[7:0] | 00000000 to<br>11111111 | writing data byte-wise to the RAM |

#### Industrial LCD driver for multiplex rates up to 1:8

# 8.1.15 Command: Temp-read

The Temp-read command allows reading out the temperature values measured by the internal temperature sensor.

Table 20. Temp-read - temperature readout command bit description For further information, see Section 8.4.4 on page 28.

| Bit    | Symbol  | Binary value            | Description                   |

|--------|---------|-------------------------|-------------------------------|

| 7 to 0 | TD[7:0] | 00000000 to<br>11111111 | digital temperature values[1] |

<sup>[1]</sup> For this command, bit R/W of the I<sup>2</sup>C-bus slave address byte has to be set logic 1 (see Table 31).

#### 8.1.16 Command: Invmode ctrl

The Invmode\_ctrl command allows changing the drive scheme inversion mode.

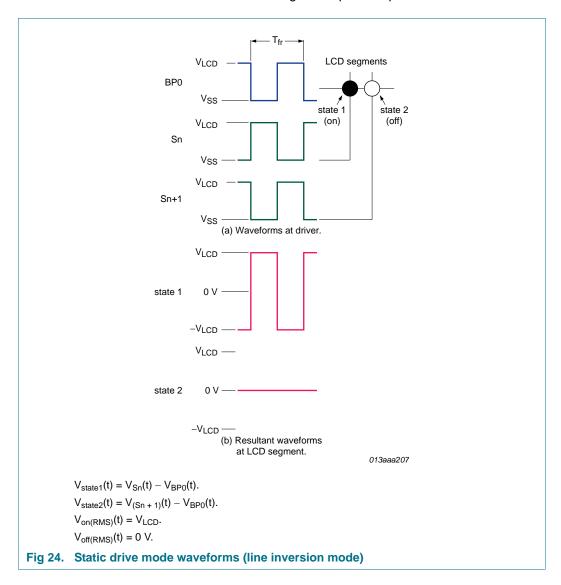

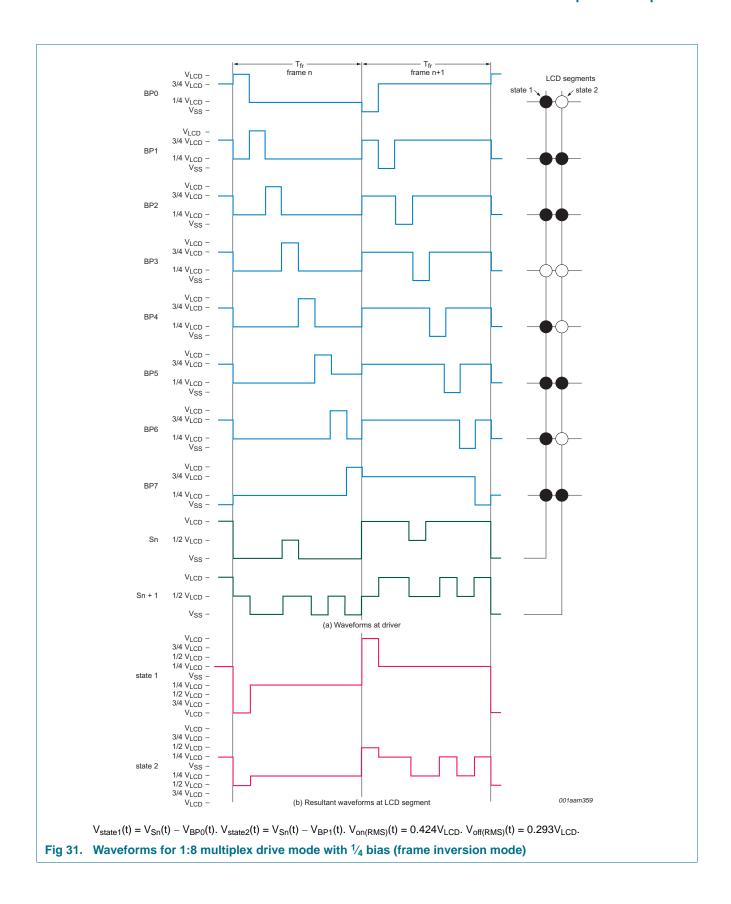

The waveforms used to drive LCD displays inherently produce a DC voltage across the display cell. The PCF8537 compensates for the DC voltage by inverting the waveforms on alternate frames or alternate lines. The choice of compensation method is determined with the LF bit.

Table 21. Invmode\_ctrl - drive scheme inversion command bit description For further information, see Section 8.4.6 on page 34.

| Bit    | Symbol | Binary value       | Description                            |  |  |

|--------|--------|--------------------|----------------------------------------|--|--|

| 7 to 2 | -      | 110101             | fixed value                            |  |  |

| 1      | LF     | set inversion mode |                                        |  |  |

|        |        | 0[1]               | driving scheme A: line inversion mode  |  |  |

|        |        | 1                  | driving scheme B: frame inversion mode |  |  |

| 0      | -      | 0                  | fixed value                            |  |  |

|        |        |                    |                                        |  |  |

<sup>[1]</sup> Default value.

In frame inversion mode, the DC value is compensated across two frames and not within one frame. Changing the inversion mode to frame inversion reduces the power consumption, therefore it is useful when power consumption is a key point in the application.

Frame inversion may not be suitable for all applications. The RMS voltage across a segment is better defined, however since the switching frequency is reduced there is possibility for flicker to occur.

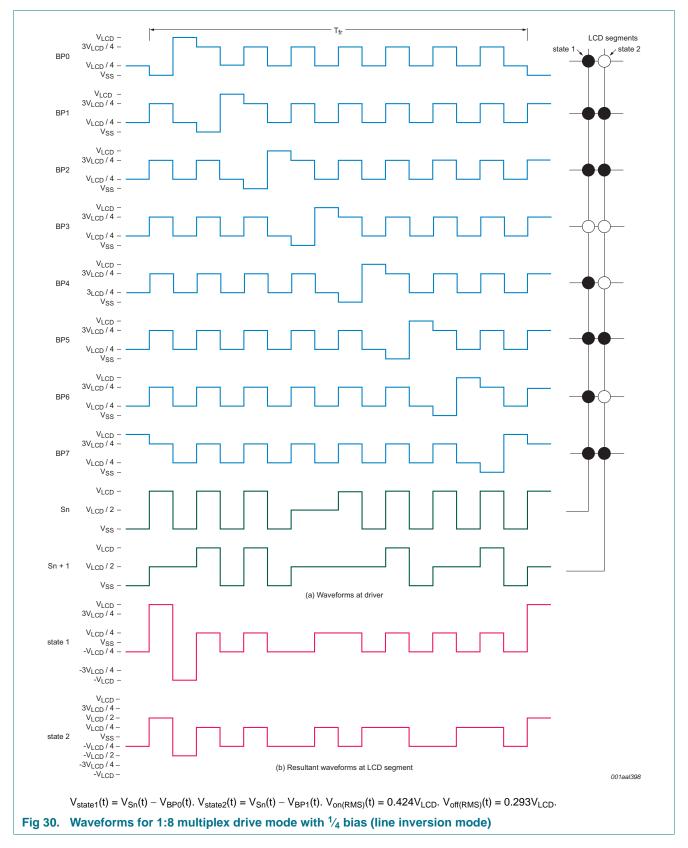

<u>Figure 24 on page 34</u> to <u>Figure 30 on page 40</u> are showing the waveforms in line inversion mode. <u>Figure 31 on page 41</u> shows an example of frame inversion.

# Industrial LCD driver for multiplex rates up to 1:8

# 8.1.17 Command: Temp-filter

Table 22. Temp-filter - digital temperature filter command bit description For further information, see <u>Section 8.4.4 on page 28</u>.

| Bit    | Symbol | Binary value | Description                                                                                                                                                                  |

|--------|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 1 | -      | 1101001      | fixed value                                                                                                                                                                  |

| 0      | TFE    |              | digital temperature filter switch                                                                                                                                            |

|        |        | 0[1]         | digital temperature filter disabled; the unfiltered digital value of TD[7:0] is immediately available for the readout and V <sub>LCD</sub> compensation, see Section 8.4.4.1 |

|        |        | 1            | digital temperature filter enabled                                                                                                                                           |

<sup>[1]</sup> Default value.

#### Industrial LCD driver for multiplex rates up to 1:8

# 8.2 Start-up and shut-down

#### 8.2.1 Power-On Reset (POR)

At power-on, the PCF8537 resets to starting conditions as follows:

- 1. All backplane and segment outputs are set to V<sub>SS</sub>.

- 2. Selected drive mode is: 1:8 with  $\frac{1}{4}$  bias.

- 3. Input and output bank selectors are reset.

- 4. The I<sup>2</sup>C-bus and SPI-bus interface are initialized.

- 5. The data pointer is cleared (set logic 0).

- 6. The internal oscillator is running; no clock signal is available on pin CLK; pin CLK is in 3-state.

- 7. Temperature measurement is enabled.

- 8. Temperature filter is disabled.

- 9. The internal V<sub>LCD</sub> voltage generation is disabled. The charge pump is switched off.

- 10. The V<sub>LCD</sub> temperature compensation is enabled.

- 11. The display is disabled.

The reset state is as shown in Table 23.

Table 23. Reset state

Reset state of configuration bits shown in the command table format for clarity. The bit labeled with - has an undefined reset state.

| Command name      | Bits |   |           |             | Bits    |            |                |         |  |  |  |  |  |

|-------------------|------|---|-----------|-------------|---------|------------|----------------|---------|--|--|--|--|--|

|                   | 7    | 6 | 5         | 4           | 3       | 2          | 1              | 0       |  |  |  |  |  |

| Oscillator-ctrl   | 1    | 1 | 0         | 0           | 1       | 1          | COE = 0        | OSC = 0 |  |  |  |  |  |

| Charge-pump-ctrl  | 1    | 1 | 0         | 0           | 0       | 0          | CPE = 0        | CPC = 0 |  |  |  |  |  |

| Temp-msr-ctrl     | 1    | 1 | 0         | 0           | 1       | 0          | TCE = 1        | TME = 1 |  |  |  |  |  |

| Temp-comp         | 0    | 0 | 0         | 1           | 1       | SLA[2:0    | 000 [          |         |  |  |  |  |  |

|                   | 0    | 0 | 1         | 0           | 0       | SLB[2:0    | 000 [          |         |  |  |  |  |  |

|                   | 0    | 0 | 1         | 0           | 1       | SLC[2:0    | SLC[2:0] = 000 |         |  |  |  |  |  |

|                   | 0    | 0 | 1         | 1           | 0       | SLD[2:0    | SLD[2:0] = 000 |         |  |  |  |  |  |

| Set-VPR           | 0    | 1 | 0         | 0           | VPR[7   | :4] = 0000 |                |         |  |  |  |  |  |

|                   | 0    | 1 | 0         | 1           | VPR[3   | :0] = 0000 |                |         |  |  |  |  |  |

| Display-enable    | 0    | 0 | 1         | 1           | 1       | 0          | 0              | E = 0   |  |  |  |  |  |

| Set-MUX-mode      | 0    | 0 | 0         | 0           | 0       | M[2:0] =   | = 000          |         |  |  |  |  |  |

| Set-bias-mode     | 1    | 1 | 0         | 0           | 0       | 1          | B[1:0] = 0     | 0       |  |  |  |  |  |

| Load-data-pointer | 1    | 0 | P[5:0] is | s undefined |         |            |                |         |  |  |  |  |  |

| Frame-frequency   | 0    | 1 | 1         | F[4:0] =    | = 01110 |            |                |         |  |  |  |  |  |

| Bank-select       | 0    | 0 | 0         | 0           | 1       | 0          | IBS = 0        | OBS = 0 |  |  |  |  |  |

| Invmode_ctrl      | 1    | 1 | 0         | 1           | 0       | 1          | LF = 0         | -       |  |  |  |  |  |

| Temp-filter       | 1    | 1 | 0         | 1           | 0       | 0          | 1              | TFE = 0 |  |  |  |  |  |

**Remark:** Do not transfer data on the I<sup>2</sup>C-bus or SPI-bus for at least 1 ms after a power-on reset to allow the reset action to complete.

PCF8537

#### Industrial LCD driver for multiplex rates up to 1:8

The first command sent to the device after the power-on event must be the Initialize command (see Section 8.1.1).

After POR and before enabling the display, the RAM content should be brought to a defined status

- by clearing it (setting it all to logic 0) or

- by writing meaningful content (for example, a graphic)

otherwise unwanted display artifacts may appear on the display.

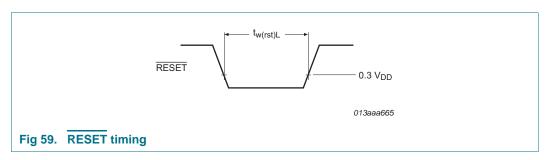

# 8.2.2 RESET pin function

The RESET pin of the PCF8537 resets all the registers to their default state. The reset state is given in Table 23. The RAM contents remain unchanged. After the reset signal is removed, the PCF8537 will behave in the same manner as after POR. See Section 8.2.1 for details.

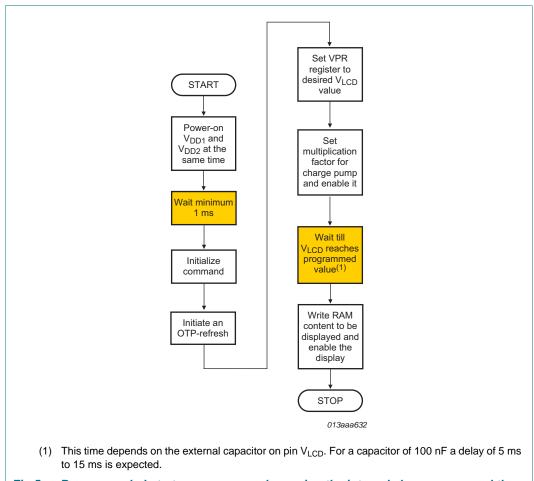

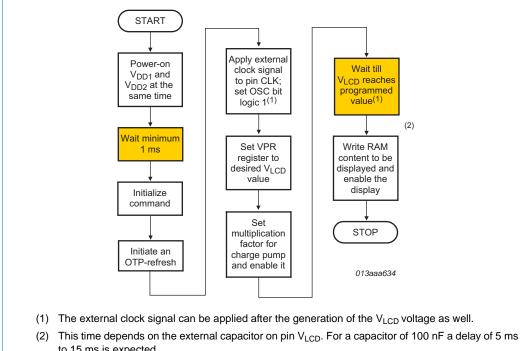

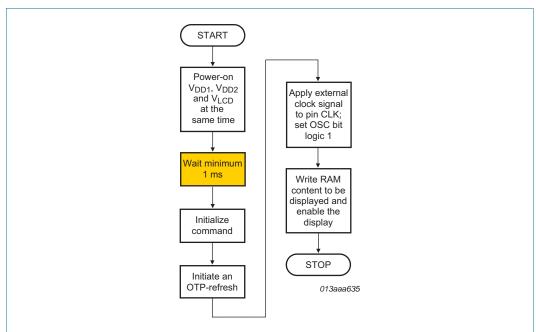

### 8.2.3 Recommended start-up sequences

This chapter describes how to proceed with the initialization of the chip in different application modes.

Fig 5. Recommended start-up sequence when using the internal charge pump and the internal clock signal

**NXP Semiconductors**

#### Industrial LCD driver for multiplex rates up to 1:8

If the display is enabled too soon after the charge pump is enabled, then the V<sub>LCD</sub> voltage may not have yet stabilized leading to an uneven display effect.

Fig 6. Recommended start-up sequence when using an external supplied V<sub>LCD</sub> and the internal clock signal

to 15 ms is expected.

Fig 7. Recommended start-up sequence when using the internal charge pump and an external clock signal

# Industrial LCD driver for multiplex rates up to 1:8

Fig 8. Recommended start-up sequence when using an external supplied  $V_{\text{LCD}}$  and an external clock signal

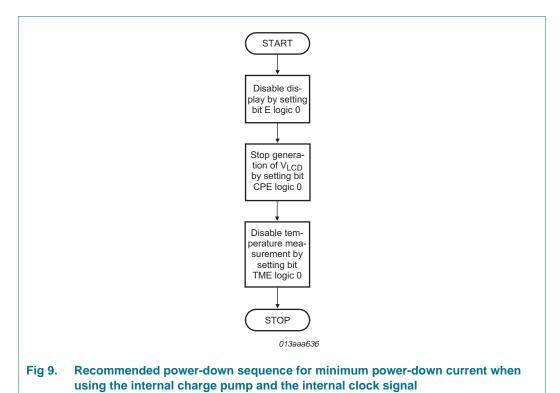

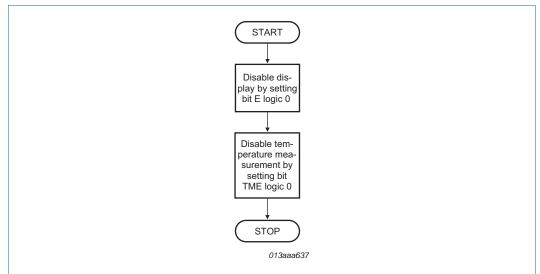

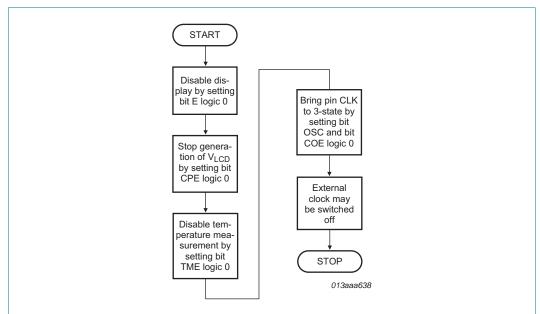

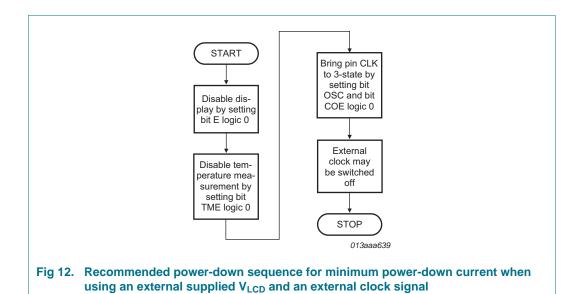

#### 8.2.4 Recommended sequences to enter power-down mode

With the following sequences, the PCF8537 can be set to a state of minimum power consumption, called power-down mode.

PCF8537

#### Industrial LCD driver for multiplex rates up to 1:8

Fig 10. Recommended power-down sequence when using an external supplied  $V_{LCD}$  and the internal clock signal

Fig 11. Recommended power-down sequence when using the internal charge pump and an external clock signal

#### Industrial LCD driver for multiplex rates up to 1:8

**Remark:** It is necessary to run the power-down sequence before removing the supplies. Depending on the application, care must be taken that no other signals are present at the chip input or output pins when removing the supplies (see <u>Section 10</u>). Otherwise this may cause unwanted display artifacts. In the case of uncontrolled removal of supply voltages the PCF8537 will not be damaged.

**Remark:** Static voltages across the liquid crystal display can build up when the external LCD supply voltage ( $V_{LCD}$ ) is on while the IC supply voltage ( $V_{DD1}$  or  $V_{DD2}$ ) is off, or the other way around. This may cause unwanted display artifacts. To avoid such artifacts,  $V_{LCD}$ ,  $V_{DD1}$ , and  $V_{DD2}$  must be applied or removed together.

**Remark:** A clock signal must always be supplied to the device when the display is active. Removing the clock may freeze the LCD in a DC state, which is not suitable for the liquid crystal. It is recommended to first disable the display and afterwards to remove the clock signal.

#### Industrial LCD driver for multiplex rates up to 1:8

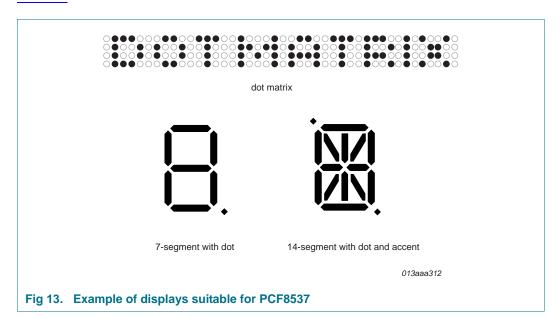

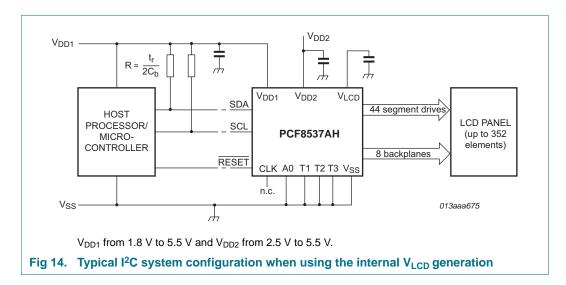

# 8.3 Possible display configurations

The PCF8537 is a versatile peripheral device designed to interface between any microcontroller to a wide variety of LCD segment or dot matrix displays (see <u>Figure 13</u>). It can directly drive any static or multiplexed LCD containing up to eight backplanes with 44 segments.

The display configurations possible with the PCF8537 depend on the number of active backplane outputs required. A selection of possible display configurations is given in Table 24.

Table 24. Selection of display configurations

| Number of  |          |       | Digits/Chara | Digits/Characters          |                   |  |

|------------|----------|-------|--------------|----------------------------|-------------------|--|

| Backplanes | Segments | Icons | 7 segment[1] | 7 segment[1] 14 segment[2] |                   |  |

| 8          | 44       | 352   | 44           | 22                         | 352 dots (8 × 44) |  |

| 6          | 46       | 276   | 34           | 17                         | 276 dots (6 × 46) |  |

| 4          | 44       | 176   | 22           | 11                         | 176 dots (4 × 44) |  |

| 2          | 44       | 88    | 11           | 5                          | 88 dots (2 × 44)  |  |

| 1          | 44       | 44    | 5            | 2                          | 44 dots (1 × 44)  |  |

<sup>[1] 7</sup> segment display has 8 elements including the decimal point.

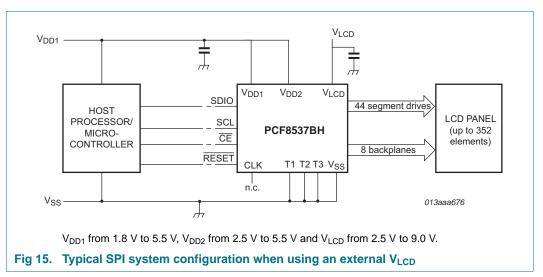

All of the display configurations in <u>Table 24</u> can be implemented in the typical systems shown in <u>Figure 14</u> (internal  $V_{LCD}$ ) and in <u>Figure 15</u> (external  $V_{LCD}$ ).

<sup>[2] 14</sup> segment display has 16 elements including decimal point and accent dot.

#### Industrial LCD driver for multiplex rates up to 1:8

The host microcontroller maintains the two-line  $I^2C$ -bus communication channel with the PCF8537AH or the three-line SPI-bus with the PCF8537BH. The appropriate biasing voltages for the multiplexed LCD waveforms are generated internally. The only other connections required to complete the system are the power supplies ( $V_{DD1}$ ,  $V_{DD2}$ ,  $V_{SS}$ ,  $V_{LCD}$ ), the external capacitors, and the LCD panel selected for the application.

The recommended values for external capacitors on  $V_{DD1}$ ,  $V_{DD2}$ , and  $V_{LCD}$  are of nominal 100 nF value. When using bigger capacitors, especially on the  $V_{LCD}$ , the generated ripple will be consequently smaller. However it will take longer for the internal charge pump to first reach the target  $V_{LCD}$  voltage.

If  $V_{DD1}$  and  $V_{DD2}$  are connected externally, the capacitors on  $V_{DD1}$  and  $V_{DD2}$  can be replaced by a single capacitor with a nominal value of 220 nF.

**Remark:** In case of insufficient decoupling, ripple on  $V_{DD1}$  and  $V_{DD2}$  will create additional  $V_{LCD}$  ripple. The ripple on the  $V_{LCD}$  can be reduced by making the  $V_{SS}$  connection as low-ohmic as possible. Excessive ripple on  $V_{LCD}$  may cause flicker on the display.

#### Industrial LCD driver for multiplex rates up to 1:8

### 8.4 LCD supply voltage

#### 8.4.1 External V<sub>LCD</sub> supply

$V_{LCD}$  can be directly supplied to the VLCD pin. In this case, the internal charge pump must not be enabled otherwise a high current may occur on pin VDD2 and pin VLCD. When  $V_{LCD}$  is supplied externally, no internal temperature compensation occurs on this voltage even if bit TCE is set logic 1 (see Section 8.4.4.2). The  $V_{LCD}$  voltage which is supplied externally will be available at the segments and backplanes of the device through the chosen bias system. Also programming VPR[7:0] will have no effect on the  $V_{LCD}$  which is externally supplied.

### 8.4.2 Internal V<sub>LCD</sub> generation

$V_{LCD}$  can be generated and controlled on the chip by using software commands. When the internal charge pump is used, the programmed  $V_{LCD}$  is available on pin VLCD. The charge pump generates a  $V_{LCD}$  of up to  $3 \times V_{DD2}$ . The charge pump can be enabled or disabled with the CPE bit (see <u>Table 8 on page 9</u>). With bit CPC, the charge pump multiplier setting can be configured.

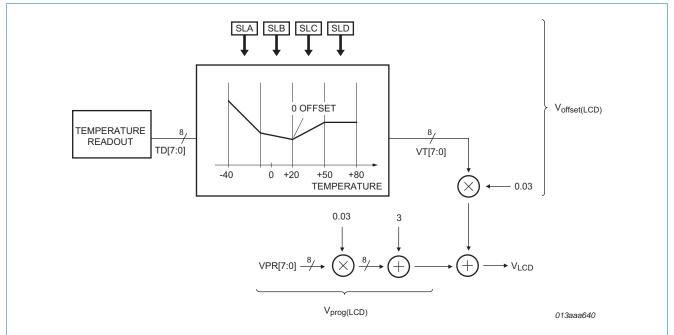

The final value of  $V_{LCD}$  is a combination of the programmed  $V_{prog(LCD)}$  value and the output of the temperature compensation block,  $V_{offset(LCD)}$ .

$$V_{LCD} = V_{prog(LCD)} + V_{offset(LCD)}$$

(1)

The system is shown in Figure 16.

VPR[7:0] is the binary value of the programmed voltage. VT[7:0] is the binary value of the temperature compensated voltage. Its values come from the temperature compensation block and is a two's complement which has the value 0h at 20 °C.

$$V_{prog(LCD)} = VPR[7:0] \times 0.03 + 3 \; . \label{eq:vprog(LCD)}$$

The equations for  $V_{offset(LCD)}$ , see <u>Table 27 on page 31</u>.

Fig 16. V<sub>LCD</sub> generation including temperature compensation

PCF8537

#### Industrial LCD driver for multiplex rates up to 1:8

Figure 17 illustrates how V<sub>LCD</sub> changes with the programmed value of VPR[7:0].

The programmable range of VPR[7:0] is from 0h to FFh. With the upper part of the programmable range, it is possible to achieve more than 9.0 V, but the PCF8537 has a built-in automatic limitation of  $V_{LCD}$  at 9.0 V. If  $V_{DD2}$  is higher than 3.0 V, then it is important that VPR[7:0] is set to a value such that the resultant  $V_{LCD}$  (including the temperature correction of VT[7:0]) is higher than  $V_{DD2}$ .

#### 8.4.3 Charge pump

#### 8.4.3.1 Charge pump configuration

To obtain the desired  $V_{LCD}$  values, the charge pump has to be configured properly. It has to be taken into account that the maximum theoretical values cannot be reached due to internal losses (see Section 8.4.3.2). So, for example, it is not possible to get a  $V_{LCD} = 6.0 \text{ V}$  with  $V_{DD2} = 3.0 \text{ V}$  and a charge pump configuration of 2 times  $V_{DD2}$ . In this case, a charge pump configuration of 3 times  $V_{DD2}$  is needed.

# 8.4.3.2 Charge pump driving capability

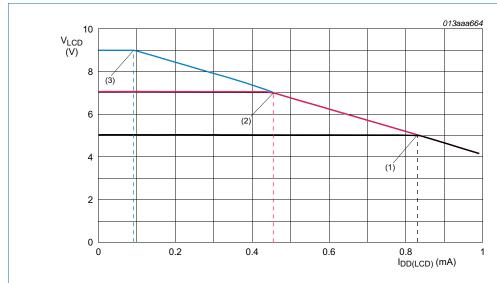

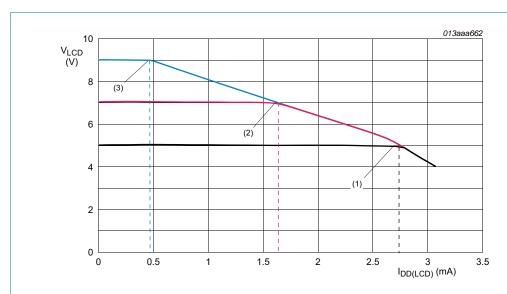

Figure 18 and Figure 19 are showing the charge pump driving capability with different settings of  $V_{DD2}$  and charge pump configurations.

# Industrial LCD driver for multiplex rates up to 1:8

- (1) VPR[7:0] = 42h.

- (2) VPR[7:0] = 85h.

- (3) VPR[7:0] = C6h.

$$T_{amb}$$

= 30 °C;  $V_{DD1}$  =  $V_{DD2}$  = 3.3 V.

**Remark:** For driving the charge pump safely the  $V_{LCD}$  and  $I_{DD(LCD)}$  values have to be kept below the flat part of the respective graph.

Charge pump configuration:  $V_{LCD} = 3 \times V_{DD2}$ .

Fig 18. Charge pump driving capability with  $V_{DD2} = 3.3 \text{ V}$

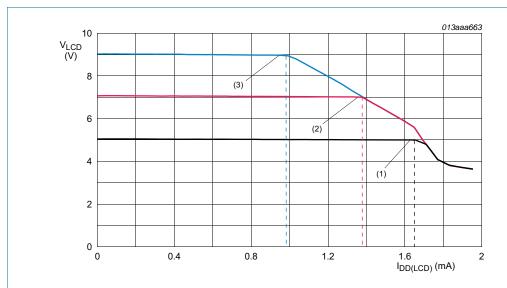

- (1) VPR[7:0] = 42h.

- (2) VPR[7:0] = 85h.

- (3) VPR[7:0] = C6h.

$T_{amb} = 30 \, ^{\circ}C; \, V_{DD1} = V_{DD2} = 5 \, V.$

**Remark:** For driving the charge pump safely the  $V_{LCD}$  and  $I_{DD(LCD)}$  values have to be kept below the flat part of the respective graph.

a. Charge pump configuration:  $V_{LCD} = 2 \times V_{DD2}$

#### Industrial LCD driver for multiplex rates up to 1:8

- (1) VPR[7:0] = 42h.

- (2) VPR[7:0] = 85h.

- (3) VPR[7:0] = C6h.

$$T_{amb} = 30 \, ^{\circ}C; \, V_{DD1} = V_{DD2} = 5 \, V.$$

**Remark:** For driving the charge pump safely the  $V_{LCD}$  and  $I_{DD(LCD)}$  values have to be kept below the flat part of the respective graph.

b. Charge pump configuration:  $V_{LCD} = 3 \times V_{DD2}$

Fig 19. Charge pump driving capability with  $V_{DD2} = 5.0 \text{ V}$

# 8.4.4 Temperature measurement and temperature compensation of V<sub>LCD</sub>

### 8.4.4.1 Temperature readout

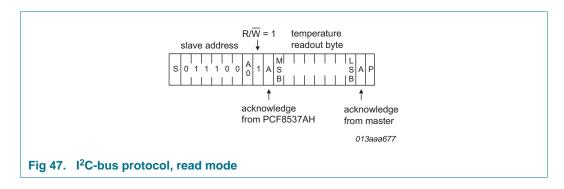

The PCF8537 has a built-in temperature sensor which provides an 8 bit digital value, TD[7:0], of the ambient temperature. This value can be read through the interface (see <u>Figure 47 on page 56</u> and <u>Figure 51 on page 59</u>). The actual temperature is determined from TD[7:0] using <u>Equation 2</u>:

$$T(^{\circ}C) = 0.9375 \times TD[7:0] - 40$$

(2)

The measurement needs about 5 ms to complete and is repeated periodically as soon as bit TME is set logic 1 (see <u>Table 9 on page 10</u>). The time between measurements is linked to the system clock and hence varies with changes in the chosen frame frequency, see <u>Table 25</u>.

Table 25. Temperature measurement update rate

| Selected frame frequency | Temperature measurement update rate |

|--------------------------|-------------------------------------|

| 60 Hz                    | 3.3 s                               |

| 200 Hz                   | 1 s                                 |

| 300 Hz                   | 0.67 s                              |

The temperature sensor can be thought of as analog to digital converter. Like all A/D converters, jitter will exist on the LSB of the output value. This is also true of the temperature sensor in the PCF8537. Jitter of the LSB of TD[7:0] may lead to contrast

PCF8537

#### Industrial LCD driver for multiplex rates up to 1:8

stepping of the display due to the  $V_{LCD}$  voltage is periodically changing between two different target voltages. For this reason, a filter has been implemented to ensure that LSB jitter does not affect the display performance.

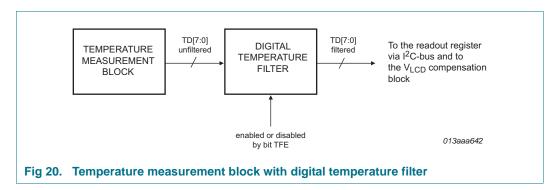

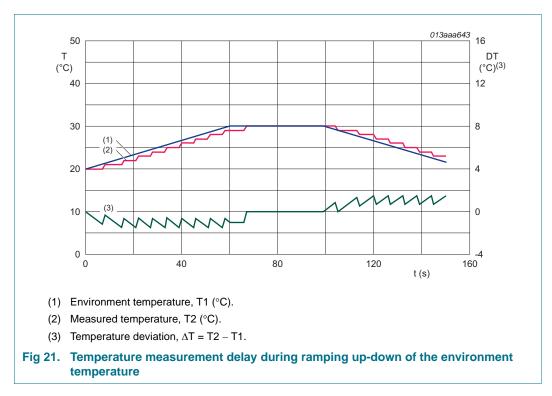

Like any other filtering, the digital temperature filter (see <u>Figure 20</u>) introduces a certain delay in the measurement of temperature. This behavior is illustrated in <u>Figure 21</u>.

This delay may cause undesired effects at start-up when the environment temperature may be different than the reset value of the PCF8537 which is 20 °C. In this case, it takes up to 30 s until the correct measured temperature value will be available. A control bit, TFE (see Table 22 on page 16), is implemented to enable or disable the digital temperature filter. This bit is set logic 0 by default, which means, that the filter is disabled and the unfiltered environment temperature value is available to calculate the desired  $V_{\rm LCD}$ .

#### Industrial LCD driver for multiplex rates up to 1:8

# 8.4.4.2 Temperature adjustment of the V<sub>LCD</sub>

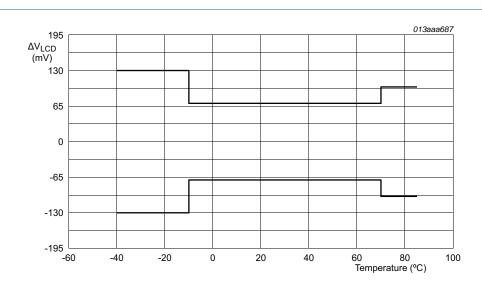

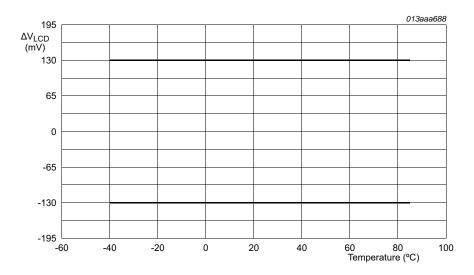

Due to the temperature dependency of the liquid crystal viscosity the LCD controlling voltage  $V_{LCD}$  might have to be adjusted at different temperatures to maintain optimal contrast. The temperature behavior of the liquid comes from the LCD manufacturer. The slope has to be set to compensate for the liquid behavior. Internal temperature compensation may be enabled via bit TCE (see <u>Table 9 on page 10</u>).

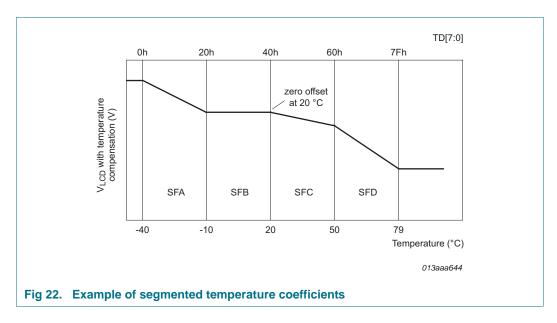

The ambient temperature range is split up into four equally sized regions and a different temperature coefficient can be applied to each. Each coefficient can be selected from a choice of eight different slopes. Each one of these coefficients may be independently selected (see Table 26).

Table 26. Temperature coefficients

| SLA to SLD register value | Corresponding slope factor, SFA to SFD (mV/°C) |

|---------------------------|------------------------------------------------|

| 000[1]                    | 0                                              |

| 001                       | -4                                             |

| 010                       | -8                                             |

| 011                       | -16                                            |

| 100                       | -40                                            |

| 101                       | +4                                             |

| 110                       | +8                                             |

| 111                       | +16                                            |

<sup>[1]</sup> Default value.

The slope factors imply a linear correction, however the implementation is in steps of 30 mV.

#### Industrial LCD driver for multiplex rates up to 1:8

The offset voltage is calculated according to Table 27.

Table 27. Calculation of the V<sub>LCD</sub> offset voltage

| Temperature range                       | V <sub>offset(LCD)</sub> voltage (mV)                    |

|-----------------------------------------|----------------------------------------------------------|

| $T \le -40$ °C                          | $V_{offset(LCD)} = 30 \times SFA + 30 \times SFB$        |

| $-40~^{\circ}C \le T \le -10~^{\circ}C$ | $V_{offset(LCD)} = (-10 - T) \times SFA + 30 \times SFB$ |

| -10 °C < T ≤ 20 °C                      | $V_{offset(LCD)} = (20 - T) \times SFB$                  |

| 20 °C < T ≤ 50 °C                       | $V_{offset(LCD)} = (T - 20) \times SFC$                  |

| 50 °C < T < 80 °C                       | $V_{offset(LCD)} = (T - 50) \times SFD + 30 \times SFC$  |

| 80 °C ≤ T[1]                            | $V_{offset(LCD)} = 30 \times SFD + 30 \times SFC$        |

<sup>[1]</sup> No temperature compensation is possible above 80 °C. Above this value, the system maintains the compensation value from 80 °C.

**Example**: Assumed that  $T_{amb} = -8 \,^{\circ}\text{C}$ ; SFB=  $-16 \,\text{mV/}^{\circ}\text{C}$ :

$$V_{offset(LCD)} = (20 - -8)x(-16) = 28 \times (-16) = -448mV$$

**Remark:** Care must be taken that the ranges of VPR[7:0] and VT[7:0] do not cause clipping and hence undesired results. The device will not permit overflow or underflow and will clamp results to either end of the range.

#### 8.4.5 LCD voltage selector

The LCD voltage selector co-ordinates the multiplexing of the LCD in accordance with the selected LCD drive configuration. The operation of the voltage selector is controlled by the Set-bias-mode command (see <u>Table 14 on page 12</u>) and the Set-MUX-mode command (see <u>Table 13 on page 12</u>).

Intermediate LCD biasing voltages are obtained from an internal voltage divider. The biasing configurations that apply to the preferred modes of operation, together with the biasing characteristics as functions of  $V_{LCD}$  and the resulting discrimination ratios (D), are given in <u>Table 28</u>.

Discrimination is a term which is defined as the ratio of the one and off RMS voltage across a segment. It can be thought of as a measurement of contrast.

#### Industrial LCD driver for multiplex rates up to 1:8

| LCD drive mode   | Number of: |             | LCD bias      | $V_{off(RMS)}$                 | $V_{on(RMS)}$                    | $D = \frac{V_{on(RMS)}}{[1]}$       | V <sub>LCD</sub> [2]       |

|------------------|------------|-------------|---------------|--------------------------------|----------------------------------|-------------------------------------|----------------------------|

|                  | Backplanes | Bias levels | configuration | $\frac{-g_{J}(tals)}{V_{LCD}}$ | $\frac{-\delta n(RMS)}{V_{LCD}}$ | $D = \frac{Von(RMS)}{V_{off(RMS)}}$ |                            |

| static           | 1          | 2           | static        | 0                              | 1                                | $\infty$                            | $V_{on(RMS)}$              |

| 1:2 multiplex    | 2          | 3           | 1/2           | 0.354                          | 0.791                            | 2.236                               | $2.828 V_{off(RMS)}$       |

| 1:2 multiplex    | 2          | 4           | 1/3           | 0.333                          | 0.745                            | 2.236                               | $3.0V_{\text{off}(RMS)}$   |

| 1:2 multiplex[3] | 2          | 5           | 1/4           | 0.395                          | 0.729                            | 1.845                               | 2.529V <sub>off(RMS)</sub> |

| 1:4 multiplex[3] | 4          | 3           | 1/2           | 0.433                          | 0.661                            | 1.527                               | 2.309V <sub>off(RMS)</sub> |

| 1:4 multiplex    | 4          | 4           | 1/3           | 0.333                          | 0.577                            | 1.732                               | 3.0V <sub>off(RMS)</sub>   |

| 1:4 multiplex[3] | 4          | 5           | 1/4           | 0.331                          | 0.545                            | 1.646                               | $3.024V_{off(RMS)}$        |

| 1:6 multiplex[3] | 6          | 3           | 1/2           | 0.456                          | 0.612                            | 1.341                               | 2.191V <sub>off(RMS)</sub> |

| 1:6 multiplex    | 6          | 4           | 1/3           | 0.333                          | 0.509                            | 1.527                               | 3.0V <sub>off(RMS)</sub>   |

| 1:6 multiplex    | 6          | 5           | 1/4           | 0.306                          | 0.467                            | 1.527                               | 3.266V <sub>off(RMS)</sub> |

| 1:8 multiplex[3] | 8          | 3           | 1/2           | 0.467                          | 0.586                            | 1.254                               | 2.138V <sub>off(RMS)</sub> |

| 1:8 multiplex[3] | 8          | 4           | 1/3           | 0.333                          | 0.471                            | 1.414                               | 3.0V <sub>off(RMS)</sub>   |

| 1:8 multiplex    | 8          | 5           | 1/4           | 0.293                          | 0.424                            | 1.447                               | 3.411V <sub>off(RMS)</sub> |

- [1] Determined from Equation 5.

- [2] Determined from Equation 4.

- [3] In these examples, the discrimination factor and hence the contrast ratios are smaller. The advantage of these LCD drive modes is a power saving from a reduction of the LCD voltage V<sub>LCD</sub>.

A practical value for  $V_{LCD}$  is determined by equating  $V_{off(RMS)}$  with a defined LCD threshold voltage ( $V_{th}$ ), typically when the LCD exhibits approximately 10 % contrast. In the static drive mode, a suitable choice is  $V_{LCD} > 3V_{th}$ .

Bias is calculated by  $\frac{1}{1+a}$ , where the values for a are

a = 1 for  $\frac{1}{2}$  bias

a = 2 for  $\frac{1}{3}$  bias

a = 3 for  $\frac{1}{4}$  bias

The RMS on-state voltage (Von(RMS)) for the LCD is calculated with Equation 3

$$V_{on(RMS)} = V_{LCD} \sqrt{\frac{a^2 + 2a + n}{n \times (1 + a)^2}}$$

(3)

where V<sub>LCD</sub> is the resultant voltage at the LCD segment and where the values for n are

n = 1 for static mode

n = 2 for 1:2 multiplex

n = 4 for 1:4 multiplex

n = 6 for 1:6 multiplex

n = 8 for 1:8 multiplex

The RMS off-state voltage (Voff(RMS)) for the LCD is calculated with Equation 4:

#### Industrial LCD driver for multiplex rates up to 1:8

$$V_{off(RMS)} = V_{LCD} \sqrt{\frac{a^2 - 2a + n}{n \times (1 + a)^2}}$$

(4)

Discrimination is the ratio of  $V_{on(RMS)}$  to  $V_{off(RMS)}$  and is determined from Equation 5:

$$\frac{V_{on(RMS)}}{V_{off(RMS)}} = \sqrt{\frac{(a+1)^2 + (n-1)}{(a-1)^2 + (n-1)}}$$

(5)

It should be noted that V<sub>LCD</sub> is sometimes referred as the LCD operating voltage.

#### 8.4.5.1 Electro-optical performance

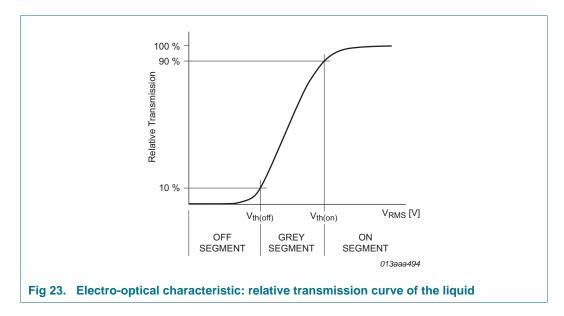

Suitable values for  $V_{\text{on(RMS)}}$  and  $V_{\text{off(RMS)}}$  are dependent on the LCD liquid used. The RMS voltage, at which a pixel will be switched on or off, determine the transmissibility of the pixel.

For any given liquid, there are two threshold values defined. One point is at 10 % relative transmission (at  $V_{th(off)}$ ) and the other at 90 % relative transmission (at  $V_{th(on)}$ ), see Figure 23. For a good contrast performance, the following rules should be followed:

$$V_{on(RMS)} \ge V_{th(on)} \tag{6}$$

$$V_{off(RMS)} \le V_{th(off)} \tag{7}$$

$V_{on(RMS)}$  and  $V_{off(RMS)}$  are properties of the display driver and are affected by the selection of a (see <u>Equation 3</u>), n (see <u>Equation 5</u>), and the  $V_{LCD}$  voltage.

$V_{th(off)}$  and  $V_{th(on)}$  are properties of the LCD liquid and can be provided by the module manufacturer.  $V_{th(off)}$  is sometimes just named  $V_{th}$ .  $V_{th(on)}$  is sometimes named saturation voltage  $V_{sat}$ .

It is important to match the module properties to those of the driver in order to achieve optimum performance.

# Industrial LCD driver for multiplex rates up to 1:8

#### 8.4.6 LCD drive mode waveforms

#### 8.4.6.1 Static drive mode

The static LCD drive mode is used when a single backplane is provided in the LCD.

# Industrial LCD driver for multiplex rates up to 1:8

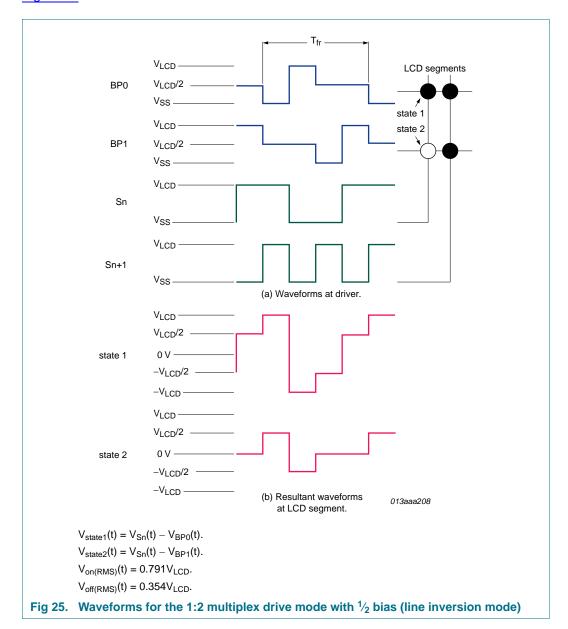

#### 8.4.6.2 1:2 multiplex drive mode

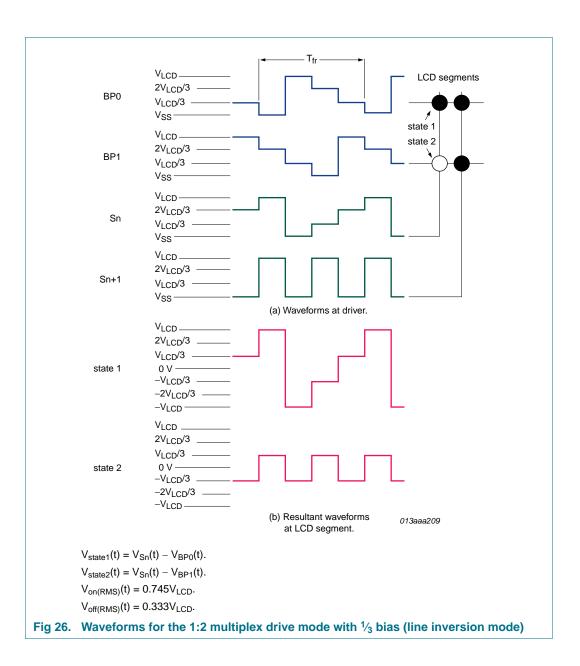

When two backplanes are provided in the LCD, the 1:2 multiplex mode applies. The PCF8537 allows the use of  $\frac{1}{2}$  bias or  $\frac{1}{3}$  bias in this mode as shown in Figure 25 and Figure 26.

# Industrial LCD driver for multiplex rates up to 1:8

# Industrial LCD driver for multiplex rates up to 1:8

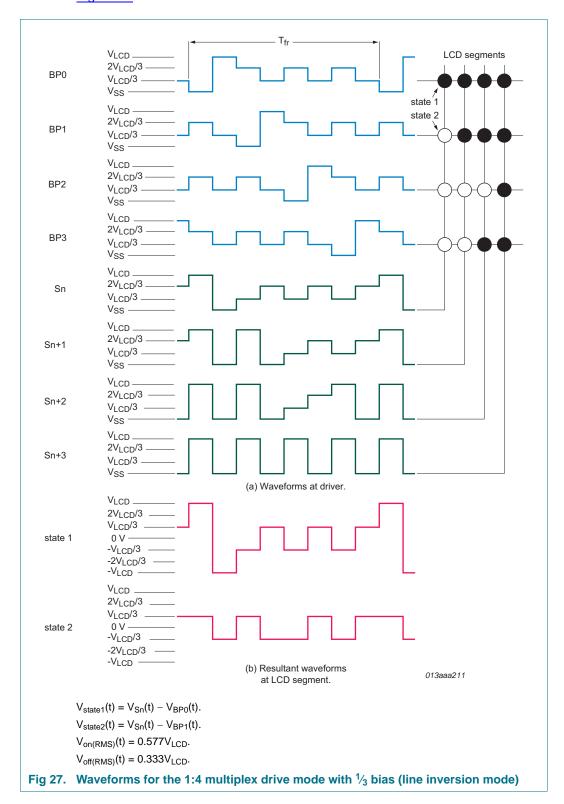

## 8.4.6.3 1:4 multiplex drive mode

When four backplanes are provided in the LCD, the 1:4 multiplex drive mode applies, as shown in Figure 27.

# Industrial LCD driver for multiplex rates up to 1:8

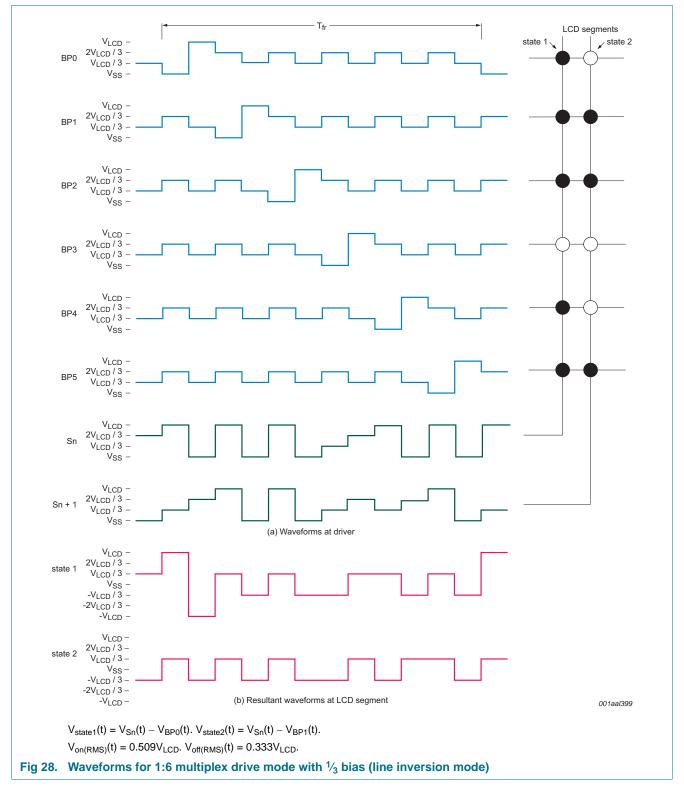

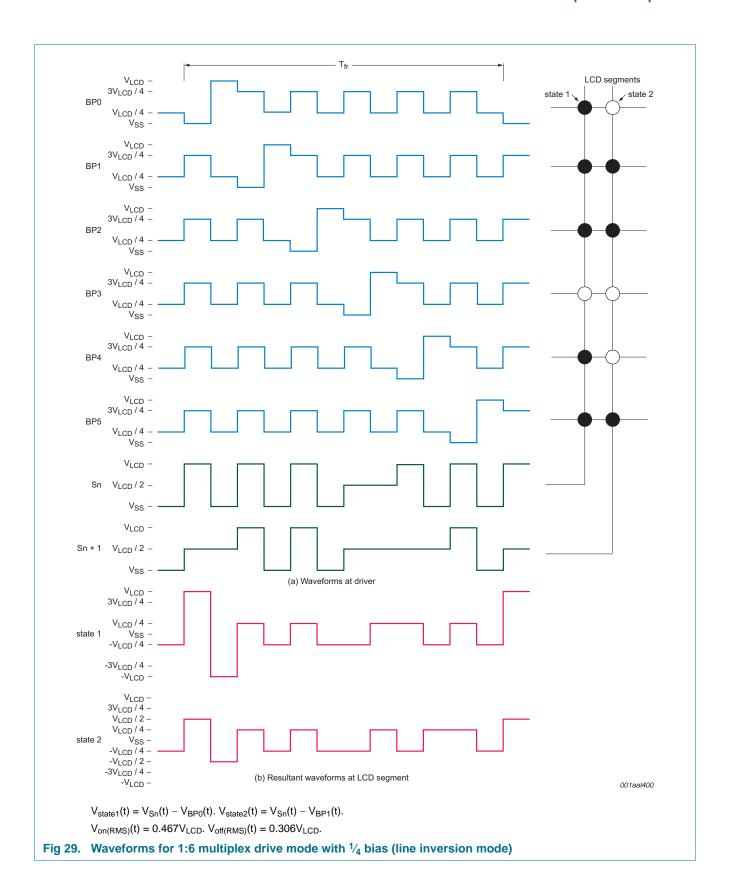

#### 8.4.6.4 1:6 multiplex drive mode

When six backplanes are provided in the LCD, the 1:6 multiplex drive mode applies. The PCF8537 allows the use of  $\frac{1}{3}$  bias or  $\frac{1}{4}$  bias in this mode as shown in Figure 28 and Figure 29.

PCF8537

## Industrial LCD driver for multiplex rates up to 1:8

## Industrial LCD driver for multiplex rates up to 1:8

## 8.4.6.5 1:8 multiplex drive mode

## Industrial LCD driver for multiplex rates up to 1:8

# Industrial LCD driver for multiplex rates up to 1:8

## 8.5 Backplane and segment outputs

#### 8.5.1 Backplane outputs

The LCD drive section includes eight backplane outputs: BP0 to BP7. The backplane output signals are generated based on the selected LCD multiplex drive mode.

Table 29 describes which outputs are active for each of the multiplex drive modes and what signal is generated.

Table 29. Mapping of output pins and corresponding signals with respect to driving mode

| MUX<br>mode | Output p | Output pin |        |                   |        |                   |         |                   |  |  |

|-------------|----------|------------|--------|-------------------|--------|-------------------|---------|-------------------|--|--|

|             | BP0      | BP1        | BP2    | BP3               | BP4    | BP5               | S45/BP6 | S44/BP7           |  |  |

|             | Signal   |            |        |                   |        |                   |         |                   |  |  |

| 1:8         | BP0      | BP1        | BP2    | BP3               | BP4    | BP5               | BP6     | BP7               |  |  |

| 1:6         | BP0      | BP1        | BP2    | BP3               | BP4    | BP5               | S45     | S44               |  |  |

| 1:4         | BP0      | BP1        | BP2    | BP3               | BP0[1] | BP1 <sup>11</sup> | BP2[1]  | BP3[1]            |  |  |

| 1:2         | BP0      | BP1        | BP0[1] | BP1 <sup>11</sup> | BP0[1] | BP1[1]            | BP0[1]  | BP1 <sup>11</sup> |  |  |

| static      | BP0      | BP0[1]     | BP0[1] | BP0[1]            | BP0[1] | BP0[1]            | BP0[1]  | BP0[1]            |  |  |

<sup>[1]</sup> These pins may optionally or alternatively be connected to the display to improve drive strength. Connect only with the corresponding output pin carrying the same signal. If not required, they can be left open circuit.

#### 8.5.1.1 1:8 multiplex drive mode

In 1:8 multiplex drive mode, BP0 to BP7 must be connected directly to the LCD.

# 8.5.1.2 1:6 multiplex drive mode

1:6 multiplex mode is a special case. In this mode BP0 to BP5 must be connected directly to the display as back plane signals and S44 and S45 must be connected to the display as segment signals.

#### 8.5.1.3 1:4 multiplex drive mode

In the 1:4 multiplex drive mode, BP0 to BP3 must be connected directly to the LCD.

The unused BPs may be left open-circuit. Optionally they may also be connected to the display to increase drive strength.

- BP0 is repeated on BP4

- BP1 is repeated on BP5

- BP2 is repeated on BP6

- BP3 is repeated on BP7

#### 8.5.1.4 1:2 multiplex drive mode

In the 1:2 multiplex drive mode, BP0 and BP1 must be connected directly to the LCD.

The unused BPs may be left open-circuit. Optionally they may also be connected to the display to increase drive strength.

- BP0 is repeated on BP2, BP4, and BP6

- BP1 is repeated on BP3, BP5, and BP7

PCF8537

# Industrial LCD driver for multiplex rates up to 1:8

#### 8.5.1.5 Static drive mode

In the static drive mode, BP0 must be connected directly to the LCD.

In the static drive mode, the same signal is carried by all eight backplane outputs and they can be connected in parallel for very high drive requirements.

• BP0 is repeated on BP1, BP2, BP3, BP4, BP5, BP6, and BP7

#### 8.5.2 Segment outputs

The LCD drive section includes up to 46 segment outputs. Segments S0 to S43 are always segment outputs. There are also two more segment outputs which become active in 1:6 multiplex mode. These are S45/BP6 and S44/BP7 and must also be connected directly to the display.

The segment output signals are generated based on the multiplexed backplane signals and with data resident in the display register. When less than 46 segment outputs are required, the unused segment outputs must be left open-circuit.

## 8.5.2.1 Static, 1:8, 1:4, 1:2 multiplex drive mode

In these drive modes, segments S0 to S43 must be connected to the display.

#### 8.5.2.2 1:6 multiplex drive mode

In this drive mode, segments S0 to S43, S44, and S45 must be connected to the display.

# Industrial LCD driver for multiplex rates up to 1:8

# 8.6 Display controller

The display controller executes the commands identified by the command decoder. It contains the status registers of the PCF8537 and co-ordinates their effects. The controller is also responsible for loading display data into the display RAM as required by the filling order.

# 8.7 Display register

The display register holds the display data while the corresponding multiplex signals are generated.

## 8.8 Display RAM

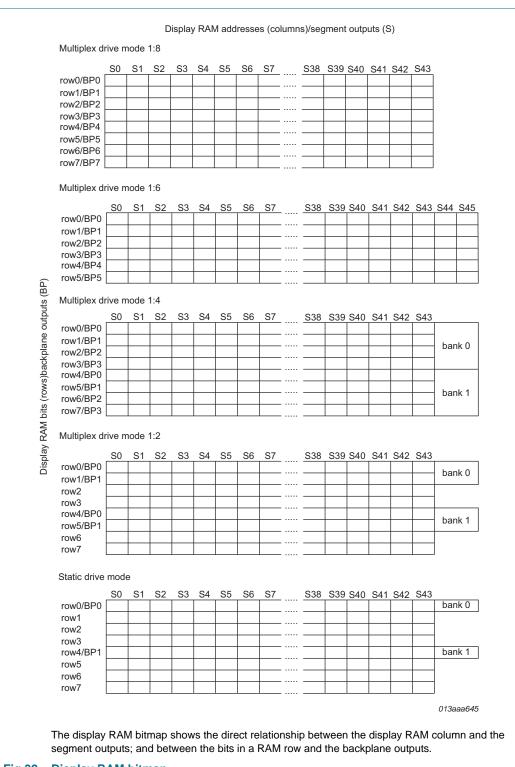

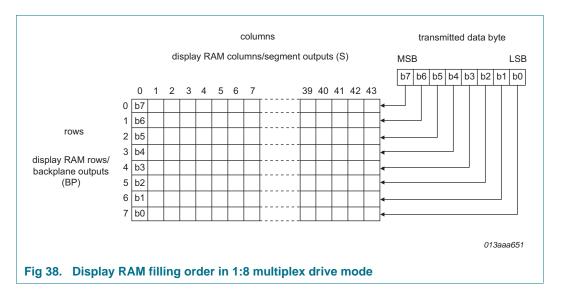

The display RAM stores LCD data. Depending on the multiplex drive mode, the arrangement of the RAM is changed.

- multiplex drive mode 1:8: RAM is 44 × 8 bit

- multiplex drive mode 1:6: RAM is 46 × 6 bit

- multiplex drive mode 1:4: RAM is 44 × 4 bit arranged in two banks

- multiplex drive mode 1:2: RAM is 44 × 2 bit arranged in two banks

- static drive mode: RAM is 44 x 1 bit arranged in two banks

A logic 1 in the RAM bit map indicates the on-state of the corresponding LCD element; similarly, a logic 0 indicates the off-state.

There is a one-to-one correspondence between

- the bits in the RAM bitmap and the LCD elements,

- the RAM columns and the segment outputs,

- the RAM rows and the backplane outputs.

# Industrial LCD driver for multiplex rates up to 1:8

Fig 32. Display RAM bitmap

#### Industrial LCD driver for multiplex rates up to 1:8

The display RAM bit map, <u>Figure 32</u>, shows row 0 to row 7 which correspond with the backplane outputs BP0 to BP7, and column 0 to column 45 which correspond with the segment outputs S0 to S45. In multiplexed LCD applications, the data of each row of the display RAM is time-multiplexed with the corresponding backplane (row 0 with BP0, row 1 with BP1, and so on).

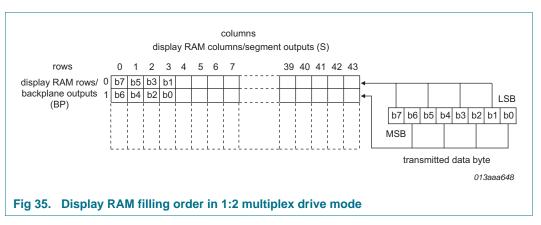

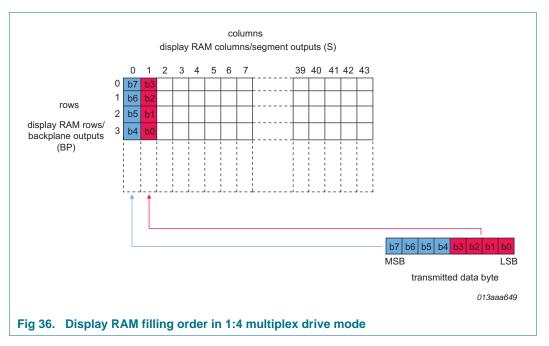

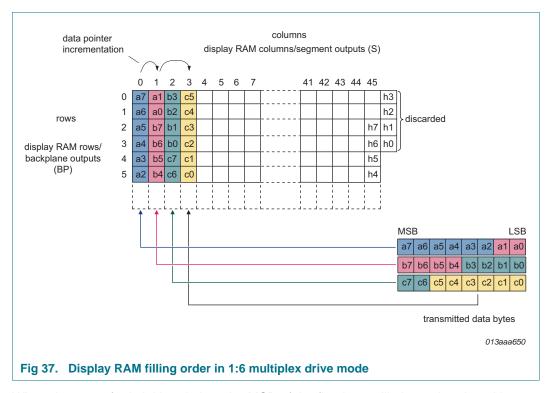

When display data is transmitted to the PCF8537, the display bytes received are stored in the display RAM in accordance with the selected LCD multiplex drive mode. The data is stored as it arrives. Depending on the current multiplex drive mode, data is stored singularly, in pairs, quadruples, sextuples or bytes.

#### 8.8.1 Data pointer

The addressing mechanism for the display RAM is realized using the data pointer. This allows the loading of an individual display data byte, or a series of display data bytes, into any location of the display RAM. The sequence commences with the initialization of the data pointer by the Load-data-pointer command (see Table 15 on page 12).

Following this command, an arriving data byte is stored starting at the display RAM address indicated by the data pointer.

After each byte stored, the data pointer is automatically incremented in accordance with the chosen LCD multiplex drive mode configuration:

- by eight (static drive mode)

- by four (1:2 multiplex drive mode)

- by two (1:4 multiplex drive mode)

- by one or two (1:6 multiplex drive mode), see Figure 37 on page 49

- by one (1:8 multiplex drive mode)

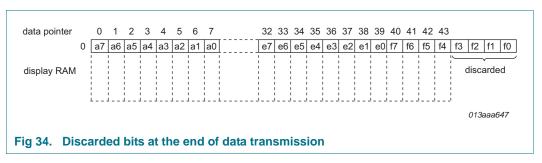

When the address counter reaches the end of the RAM row, it stops incrementing after the last byte is transmitted. Redundant bits of the last byte transmitted are discarded. Additional bytes, sent after the end of the RAM is reached, will be discarded too. The data pointer does not wrap around to the beginning. To send new RAM data, the data pointer must be reset.

If an I<sup>2</sup>C-bus or SPI-bus data access is terminated early, then the state of the data pointer is unknown. The data pointer must then be re-written before further RAM accesses.

#### Industrial LCD driver for multiplex rates up to 1:8

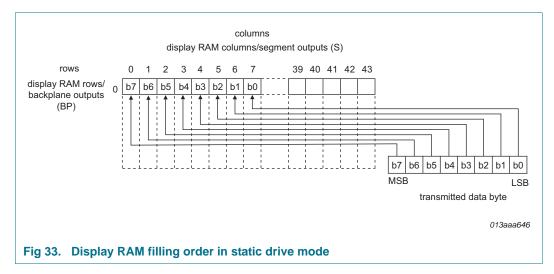

# 8.8.2 RAM filling in static drive mode

In the static drive mode the eight transmitted data bits are placed in eight successive display RAM columns in row 0 (see Figure 33).