Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriverRev. 3 — 28 September 2018Product data sheet

## **1** General description

PTN36502/PTN36502A is a Type-C USB 3.1 Gen 1/ DP1.2 combo redriver that is optimized for USB 3.1 Gen 1 and DisplayPort applications on either the Downstream Facing Port (DFP) or Upstream Facing Port (UFP) by following the four high-speed differential data flows to extend the signal reach.

PTN36502/PTN36502A addresses high-speed signal quality enhancement requirements for implementation of a USB Type-C interface in a platform that supports the VESA DisplayPort Alt Mode Standard v1.0a, includes a DisplayPort Branch or Sink function.

PTN36502/PTN36502A has three ternary (3-level) configuration pins (SCL/C1, SDA/ C2 and EN), and depending on the state of EN pin during Power-On Reset (POR), the device gets into GPIO mode or I<sup>2</sup>C mode. When EN is driven LOW during POR, PTN36502/PTN36502A operates under GPIO mode, and these three ternary pins are used to configure DFP/UFP configuration followed by mode setting (USB 3.1 Gen 1 and DisplayPort TX and RX function selection), as well as selecting receive equalization, transmit de-emphasis and output swing level. To support applications that require greater level of configurability, PTN36502/PTN36502A can operate in I<sup>2</sup>C mode when EN pin is left open (OPEN/NC) during POR.

For DisplayPort (DP) operation, PTN36502/PTN36502A has a built-in internal crossbar function that can swap AUXP and AUXN signals for supporting plug orientation. PTN36502/PTN36502A monitors the AUX transactions and adjusts the DisplayPort transmitter's output swing and emphasis setting during DP Link training accordingly.

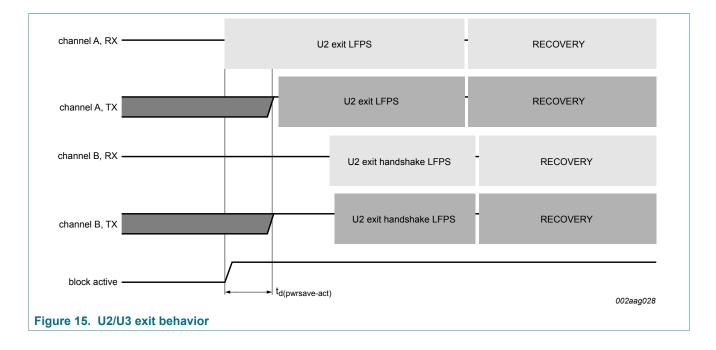

PTN36502/PTN36502A has built-in advanced power management capability that enables significant power saving under USB 3.1 Gen 1 Low power modes (U2/U3). It can detect LFPS signaling and link electrical conditions and can dynamically activate/deactivate internal circuitry and logic. The device performs these actions without host software intervention and conserves power. The host processor keeps PTN36502/PTN36502A in deep power saving or USB operation mode until DP Alt mode is entered.

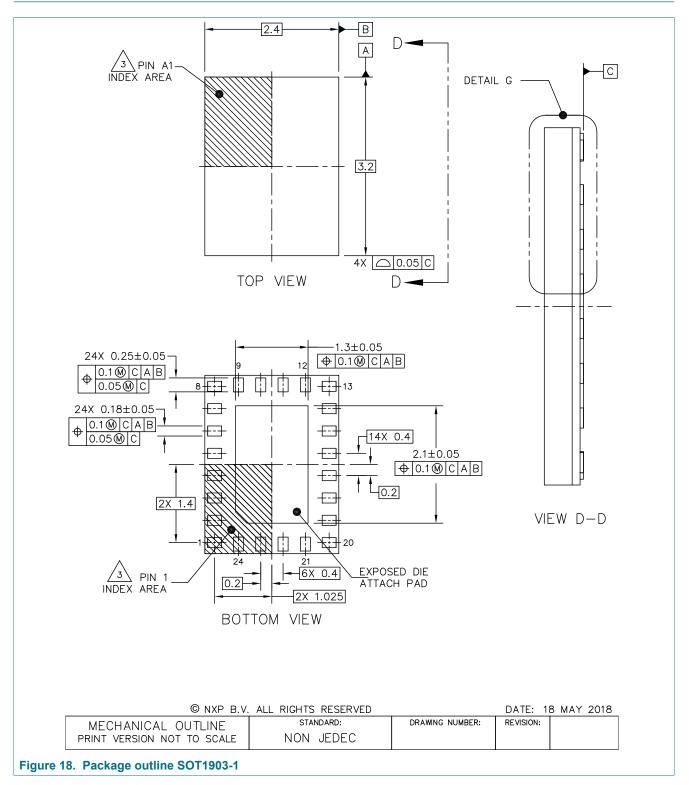

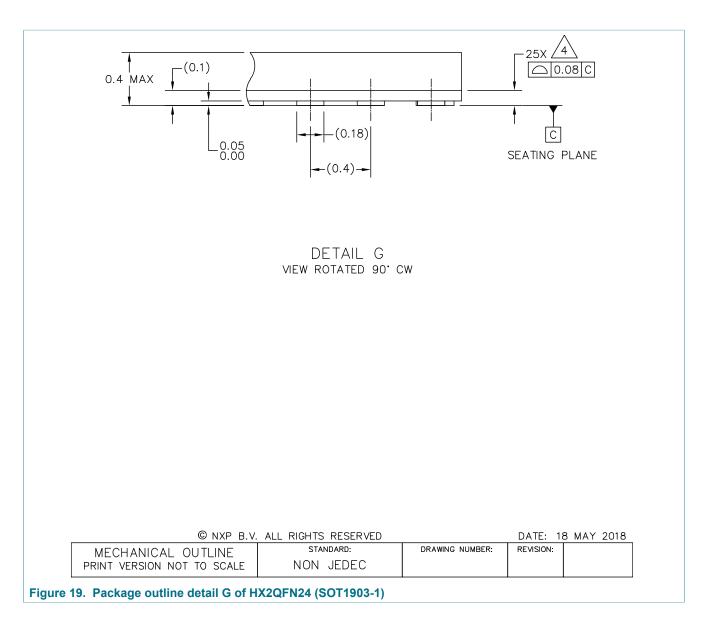

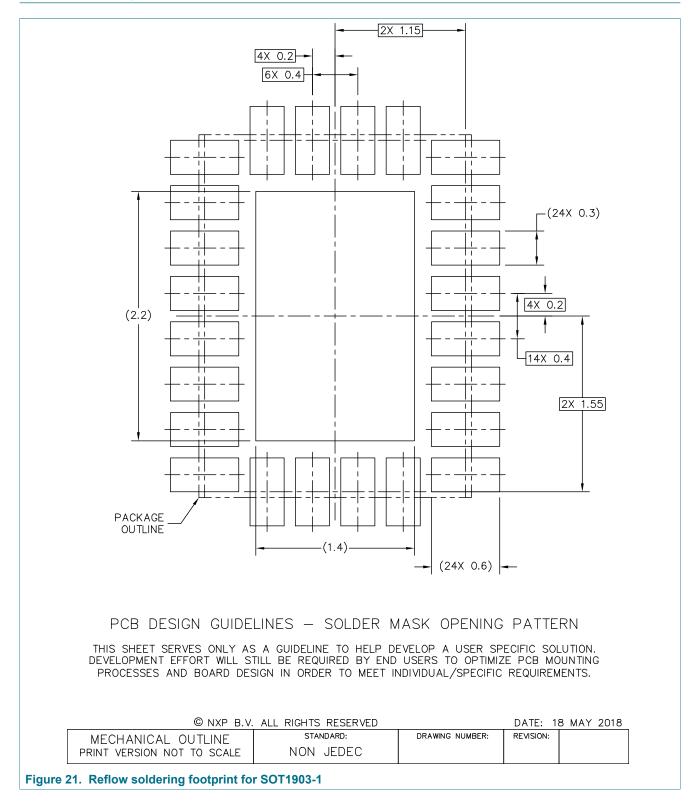

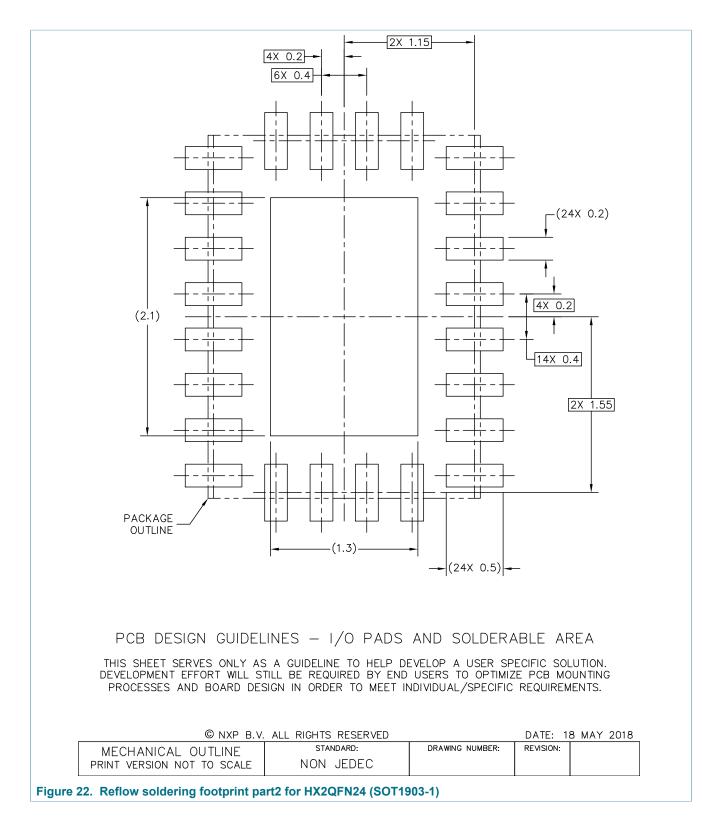

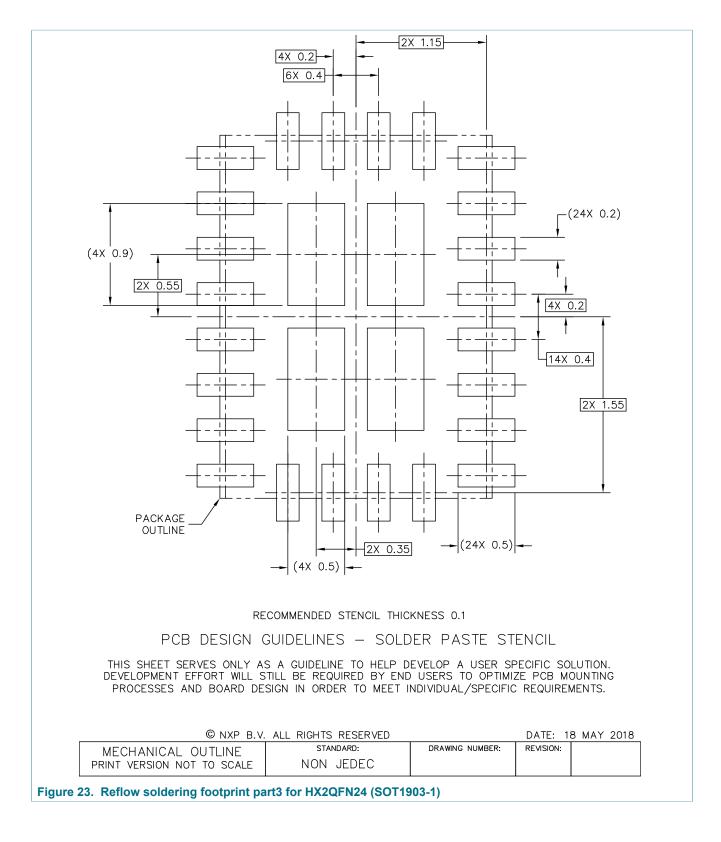

PTN36502/PTN36502A is powered from a 1.8 V supply and it is available in an extremely thin HX2QFN24 package with 2.4 mm x 3.2 mm x 0.35 mm and 0.4 mm pitch.

#### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

## 2 Features and benefits

- Flexible Type-C USB/DP combo redriver supports four signaling combinations specified in USB Type-C and VESA DisplayPort Alt Mode Standards through either I<sup>2</sup>C slave interface or ternary GPIO pins

- Mode 1: One USB 3.1 Gen 1 port only

- Mode 2: One USB 3.1 Gen 1 port + 2 lane DP + AUX channel

- Mode 3: 4 lane DP + AUX channel

- Supports USB 3.1 Gen 1 data rate of 5 Gbps, and DisplayPort data rates at 1.62 Gbps, 2.7 Gbps and 5.4 Gbps (HBR2), AUX at 1 Mbps

- · Compliant to SuperSpeed USB 3.1 Gen 1 standard

- Compliant to DisplayPort v1.2 standard for DFP applications

- · Compliant to VESA DisplayPort Alt mode on USB Type-C standard

- Implements USB Type-C Safe state conditions on all connector facing pins

- Configurable via ternary GPIO or I<sup>2</sup>C interface (operating up to 1 MHz)

- PTN36502 7-bit I<sup>2</sup>C address = 001 1010

- PTN36502A 7-bit I<sup>2</sup>C address = 001 0010

- Integrated termination resistors provide impedance matching on both transmit and receive sides

- RX equalizers on all inputs to compensate for high speed signal attenuation in PCB and cable channels

- Active TX De-emphasis and Output swing on all outputs to assure high frequency boost

- Automatic Receiver Termination Detection in USB 3.1 Gen 1 mode

- Supports auto power saving modes during USB 3.1 Gen 1 operation

- DP AUX sideband crossbar switch for Type-C plug orientation

- DP AUX monitoring during DP link training to control DP TX output driver adjustment

- Flow-through pinout to ease PCB layout and minimize crosstalk effects

- Low crosstalk: DDNEXT < -45 dB at 2.7 GHz

- Low active current consumption

- USB 3.1 Gen 1 only (Mode 1) active power: 115 mA (typ) for VOS = 1Vpp and DE=-3.5 dB

- 2-lane DP HBR2 level 0 (Mode 3): 75 mA (Level 0 : 400 mV with no Pre-emphasis)

- 1-lane DP HBR2 level 0 (Mode 3): 38 mA (Level 0 : 400 mV with no Pre-emphasis)

- 4-lane DP only HBR2 level 0 (Mode 3): 150 mA

- Power-saving states:

- USB 3.1 Gen 1 mode (mode 1):

- 1.16 mA (typ) when in USB 3.1 Gen 1 U2/U3 states

- 0.77 mA (typ) when no connection detected (USB Rx detection enabled) (when a USB Type-C to USB Type-A adapter is connected to a USB Type-C port, but no USB Type-A device is attached to the adapter)

- DP sleep D3 mode (Mode 2/3): 0.5 mA (typ)

- 3 µA (typ) when in deep power-saving state

- Excellent Differential and Common return loss performance

- Hot Plug capable

- Single Power Supply 1.8 V

- Extremely thin HX2QFN24 package

- 2.4 mm x 3.2 mm x 0.35 mm with 0.4 mm pitch

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

- ESD HBM 8 kV CDM 1 kV on high speed pins and HBM 4 kV CDM 500 V on control pins

- Supports IEC61000-4-5 8/20  $\mu s$  ±16 V Surge test performance with external 4.7  $\Omega$  series resistors on the DRX1P/N, DRX2P/N and DAUXP/N pins

- Operating temperature range -40 to +85 °C

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

## **3** Applications

- For USB Type-C Host/Source application

- Smartphones and Tablets

- Notebooks, AIO and Desktop Computers

- Hub or Dock Devices

- For USB Type-C Device/Sink application

- Docking Stations

- Display units

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

#### **Ordering information** 4

| Table 1. Ordering          | informati          | on       |                                                                                                                                    |           |  |  |

|----------------------------|--------------------|----------|------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

|                            | Topside<br>marking | Package  |                                                                                                                                    |           |  |  |

|                            |                    | Name     | Description                                                                                                                        | Version   |  |  |

| PTN36502HQ <sup>[1]</sup>  | 502                | HX2QFN24 | plastic, thermal enhanced super thin quad flat<br>package; no leads; 24 terminals; 0.4 mm pitch, 2.4<br>mm x 3.2 mm x 0.35 mm body | SOT1903-1 |  |  |

| PTN36502AHQ <sup>[2]</sup> | 52A                | HX2QFN24 | plastic, thermal enhanced super thin quad flat<br>package; no leads; 24 terminals; 0.4 mm pitch, 2.4<br>mm x 3.2 mm x 0.35 mm body | SOT1903-1 |  |  |

PTN36502 7-bit I<sup>2</sup>C address = 001 1010

PTN36502A 7-bit I<sup>2</sup>C address = 001 0010

### 4.1 Ordering options

#### Table 2. Ordering options

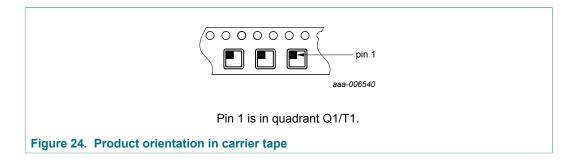

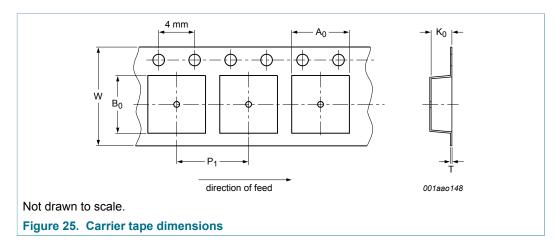

| Type number                | Orderable part number | Package  | Packing method                         | Minimum<br>order quantity | Temperature                        |  |  |

|----------------------------|-----------------------|----------|----------------------------------------|---------------------------|------------------------------------|--|--|

| PTN36502HQ <sup>[1]</sup>  | PTN36502HQX           | HX2QFN24 | REEL 7" Q1/T1<br>*STANDARD MARK<br>SMD | 3000                      | T <sub>amb</sub> = -40 °C to 85 °C |  |  |

| PTN36502AHQ <sup>[2]</sup> | PTN36502AHQX          | HX2QFN24 | REEL 7" Q1/T1<br>*STANDARD MARK<br>SMD | 3000                      | T <sub>amb</sub> = -40 °C to 85 °C |  |  |

PTN36502 7-bit I<sup>2</sup>C address = 001 1010

PTN36502A 7-bit I<sup>2</sup>C address = 001 0010

[2]

PTN36502\_PTN36502A **Product data sheet**

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

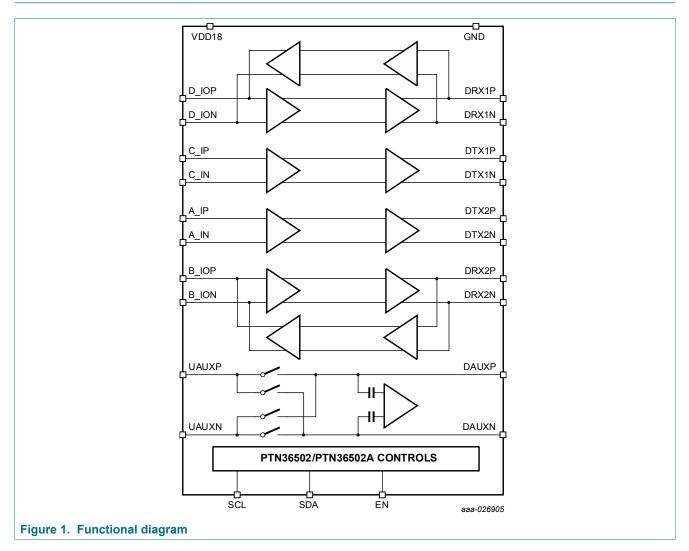

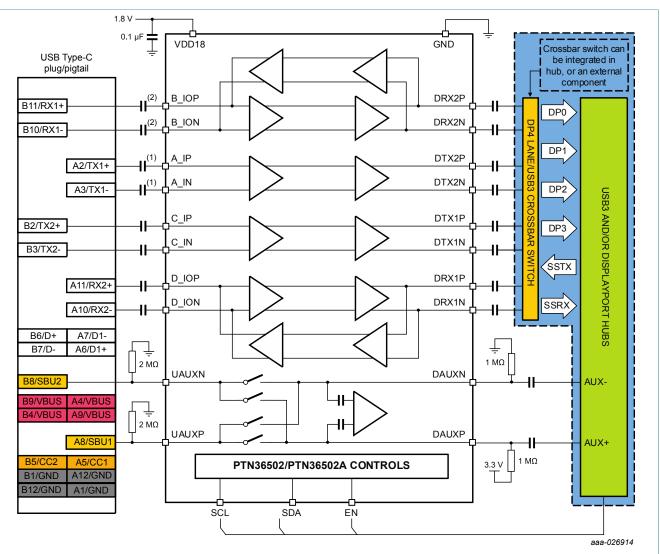

## 5 Functional diagram

## PTN36502/PTN36502A

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

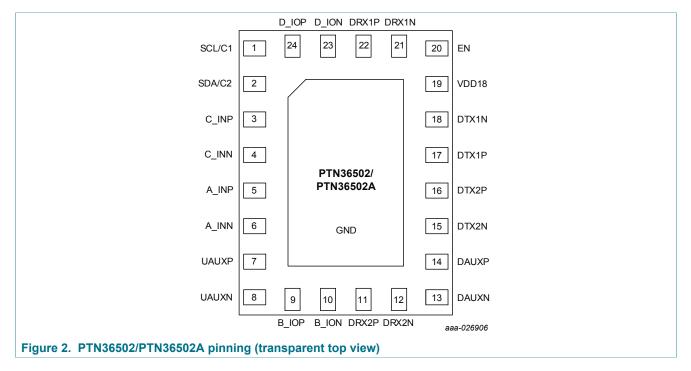

## 6 Pinning information

## 6.1 Pinning

## 6.2 Pin description

#### Table 3. Pin description

| Symbol         | Pin    | Туре                                | Description                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|----------------|--------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1              | SCL/C1 | Ternary open drain input/<br>output | When PTN36502/PTN36502A is operating in $I^2C$ mode, this pin is slave $I^2C$ clock pin, and external pull-up resistor to 1.8 V or 3.3 V is required.<br>When PTN36502/PTN36502A is operating in GPIO mode, this pin has multiple functions depending on EN pin state, and is 1.8 V tolerant. Refer to <u>Section 7.6</u> for more details.                    |  |  |  |

| 2              | SDA/C2 | Ternary open drain input/<br>output | When PTN36502/PTN36502A is operating in I <sup>2</sup> C mode, this pin is slave I <sup>2</sup> C data pin, and external pull-up resistor to 1.8 V or 3.3 V is required.<br>When PTN36502/PTN36502A is operating in GPIO mode, this pin has multiple functions depending on EN pin state, and is 1.8 V tolerant. Refer to <u>Section 7.6</u> for more details. |  |  |  |

| 3              | C_INP  | Self-biasing differential input     |                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 4              | C_INN  |                                     | differential pair with C_IN. The associated TX output pair is DTX1P and DTX1N                                                                                                                                                                                                                                                                                  |  |  |  |

| 5              | A_INP  | Self-biasing differential input     | Differential signal from high speed RX path. A_IP makes a                                                                                                                                                                                                                                                                                                      |  |  |  |

| 6              | A_INN  |                                     | differential pair with A_IN. The associated TX output pair is DTX2P and DTX2N                                                                                                                                                                                                                                                                                  |  |  |  |

| 7              | UAUXP  | I/O                                 | Upstream AUX Channel I/O. When PTN36502/PTN36502A is                                                                                                                                                                                                                                                                                                           |  |  |  |

| 8              | UAUXN  |                                     | placed in DFP application, these signals should be AC coupled a per DP spec                                                                                                                                                                                                                                                                                    |  |  |  |

| PTN36502_PTN36 | 502A   | All information provid              | ed in this document is subject to legal disclaimers. © NXP B.V. 2018. All rights reserv                                                                                                                                                                                                                                                                        |  |  |  |

## Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| Symbol        | Pin   | Туре                             | Description                                                                                                                                                                                                                           |  |  |  |

|---------------|-------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 9             | B_IOP | Self-biasing differential input/ | Differential signal high speed input/output. B_IOP makes a                                                                                                                                                                            |  |  |  |

| 10            | B_ION | output                           | differential pair with B_ION. The associated output/input pair is DRX2P and DRX2N. The I/O configuration is controlled by mode setting                                                                                                |  |  |  |

| 11            | DRX2P | Self-biasing differential input/ | Differential signal high speed input/output. DRX2P makes a                                                                                                                                                                            |  |  |  |

| 12            | DRX2N | output                           | differential pair with DRX2N. The associated output/input pair is B_<br>IOP and B_ION. The I/O configuration is controlled by mode setting                                                                                            |  |  |  |

| 13            | DAUXN | I/O                              | Downstream AUX Channel I/O. When PTN36502/PTN36502A is                                                                                                                                                                                |  |  |  |

| 14            | DAUXP |                                  | placed in UFP application, these signals should be AC coupled as per DP spec                                                                                                                                                          |  |  |  |

| 15            | DTX2N | Self-biasing differential        | Differential signal of high speed TX path. DTX2P makes a                                                                                                                                                                              |  |  |  |

| 16            | DTX2P | output                           | differential pair with DTX2N. The associated RX input pair is A_IP and A_IN                                                                                                                                                           |  |  |  |

| 17            | DTX1P | Self-biasing differential        | Differential signal of high speed TX path. DTX1P makes a                                                                                                                                                                              |  |  |  |

| 18            | DTX1N | output                           | differential pair with DTX1N. The associated RX input pair is C_IP and C_IN                                                                                                                                                           |  |  |  |

| 19            | VDD18 |                                  | 1.8 V Supply                                                                                                                                                                                                                          |  |  |  |

| 20            | EN    | Ternary input                    | <ul> <li>3 level mode configuration pin. When power is applied on VDD18 pin</li> <li>If EN = 0, PTN36502/PTN36502A is operating in GPIO mode</li> <li>If EN = OPEN, PTN36502/PTN36502A is operating in I<sup>2</sup>C mode</li> </ul> |  |  |  |

| 21            | DRX1N | Self-biasing differential input/ | Differential signal high speed input/output. DRX1P makes a                                                                                                                                                                            |  |  |  |

| 22            | DRX1P | output                           | differential pair with DRX1N. The associated output/input pair is D_IOP and D_ION. The I/O configuration is controlled by mode setting                                                                                                |  |  |  |

| 23            | D_ION | Self-biasing differential input/ | Differential signal high speed input/output. D_IOP makes a                                                                                                                                                                            |  |  |  |

| 24            | D_IOP | output                           | differential pair with D_ION. The associated output/input pair is DRX1P and DRX1N. The I/O configuration is controlled by mode setting                                                                                                |  |  |  |

| Center<br>pad | GND   |                                  | The center pad must be connected to GND plane for both electrical grounding and thermal relief                                                                                                                                        |  |  |  |

## 7 Functional description

### 7.1 USB 3.1 Gen 1 operation

PTN36502/PTN36502A supports USB redriver operation at 5 Gbps. The receive equalization, transmit output swing and de-emphasis settings are configured via GPIO or  $I^2C$  register settings.

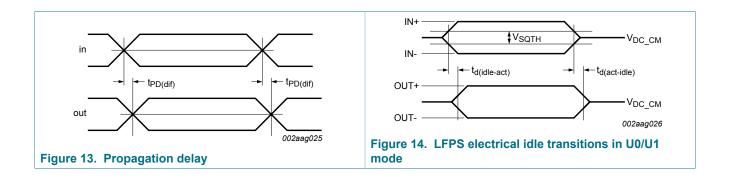

PTN36502/PTN36502A has implemented an advanced power management scheme that operates in tune with USB 3.1 Gen 1 Bus electrical condition. Though the device does not decode USB power management commands (related to USB 3.1 Gen 1 U1/U2/U3 transitions) exchanged between USB Host and Peripheral/Device, it relies on bus electrical conditions and control pins/register settings to decide to be in one of the following states:

- Active state wherein device is fully operational. In this state, USB connection exists and the Receive Termination remains active.

- Power-saving state wherein some portions of the TX and RX channels are kept enabled. In this state, squelching, LFPS detection and/or Receive termination detection circuitry are active. Based on USB connection, there are two possibilities:

- No USB connection (also called Rx-detect state)

- Receive Termination detection circuitry keeps polling periodically

- RX and TX signal paths (including squelch detector) are not enabled

- Receive Termination is not active

- DC Common mode voltage level is not maintained

- When USB connection exists and when the link is in USB U2/U3 mode,

- Receive Termination detection circuitry keeps polling periodically

- RX and TX signal paths are not enabled; squelch detector is enabled

- Receive Termination is active

- DC Common mode voltage level is maintained

### 7.2 DisplayPort v1.2 operation

PTN36502/PTN36502A supports DisplayPort redriver operation at 1.62 Gbps, 2.7 Gbps and 5.4 Gbps, with 2-tap pre-emphasis, pre-emphasis levels 0 to 3 and output swing levels 0 to 3.

The DisplayPort mode is selected only when DP Alternate mode has been entered by the host controller. Until then, PTN36502/PTN36502A stays in deep power saving or USB 3.1 Gen 1 only mode. The DisplayPort source can activate power down via AUX command.

The DisplayPort link rate, lane count, transmit output swing and pre-emphasis settings are configured autonomously during DisplayPort link training phase based on AUX communication exchanges between Source and Sink. In addition, the host can configure these settings via I<sup>2</sup>C interface.

<u>Table 4</u> illustrates the various combinations allowed and supported in DisplayPort modes. The host AP shall configure the settings only based on valid combinations listed in this table. Note PTN36502/PTN36502A does not check if combination is valid while being configured.

#### PTN36502\_PTN36502A Product data sheet

#### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| Output swing level | Pre-emphasis level |             |             |             |  |  |  |

|--------------------|--------------------|-------------|-------------|-------------|--|--|--|

|                    | 0 (0 dB)           | 1 (3.5 dB)  | 2 (6 dB)    | 3 (8.8 dB)  |  |  |  |

| 0 (400 mV)         | Supported          | Supported   | Supported   | Supported   |  |  |  |

| 1 (600 mV)         | Supported          | Supported   | Supported   | Not allowed |  |  |  |

| 2 (800 mV)         | Supported          | Supported   | Not allowed | Not allowed |  |  |  |

| 3 (1100 mV)        | Supported          | Not allowed | Not allowed | Not allowed |  |  |  |

#### Table 4. Allowed output swing and pre-emphasis combinations in DisplayPort mode

It is possible that only a subset of lanes gets selected during DP Link training and remaining lanes are not active. Depending on the number of lanes selected, PTN36502/PTN36502A is configured to operate with the selected lane count thereby saving power consumption on unused lanes.

#### 7.2.1 AUX crossbar switch

PTN36502/PTN36502A implements AUX crossbar switch with low insertion loss and  $R_{ON}$ . All AUX traffic is passively passed through from one side to another. The switch can be configured for 'pass through' mode or 'pass through with cross' mode. The host processor can configure the switch via GPIO or I<sup>2</sup>C-bus interface. By default, the switch is in Hi-Z state at power-on reset.

#### 7.2.2 AUX monitoring and configuration

PTN36502/PTN36502A monitors DP AUX communication exchanges that occur between DP source and DP sink and passes the AUX data in either direction (Source to sink and Sink to source). In particular, it detects for AUX communication involving DPCD register controls – Lane count, Link rate, Transmit output swing, Transmit pre-emphasis level, Sleep, Wake, etc. and configures its operation suitably. It also performs inversion as required for plug orientation in DFP configurations. At DP AUX PHY level, the required local biasing and AC coupling capacitance are implemented.

When PTN36502/PTN36502A is placed in DFP mode, the polarity of internal AUX monitoring signal follows the orientation of the cable connector plugged in. For example, if the orientation is reversed on the Type-C connector, signals presented on DAUXP and DAUXN pins will be interpreted as AUXN and AUXP signals internally.

When PTN36502/PTN36502A is placed in UFP mode, the polarity of internal AUX monitoring signal is fixed regardless of orientation of cable connector plugged in. Signals presented on DAUXP and DAUXN pins are interpreted as AUXP and AUXN signals internally.

The list of DPCD registers (with only the relevant bit fields) supported are as follows:

- LINK\_BW\_SET

- LANE\_COUNT\_SET

- TRAINING\_LANEx\_SET (x=0-3) (the DP source issues this command after sending the specific training pattern and so, the redriver must target very small delay)

- SET POWER

- Other DPCD registers and I<sup>2</sup>C over AUX transactions are not decoded

The applied values are expected to be within the capabilities of PTN36502/PTN36502A.

In case GPU sends out LANE\_COUNT\_SET =0 during AUX training, it is necessary to program  $I^2C$  register 0x06 to value of 0x06 after entering DP modes (either mode 2 or 3).

#### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

This will ensure the PTN36502/PTN36502A DisplayPort starts up properly. Please follow PTN36502/PTN36502A programming guide.

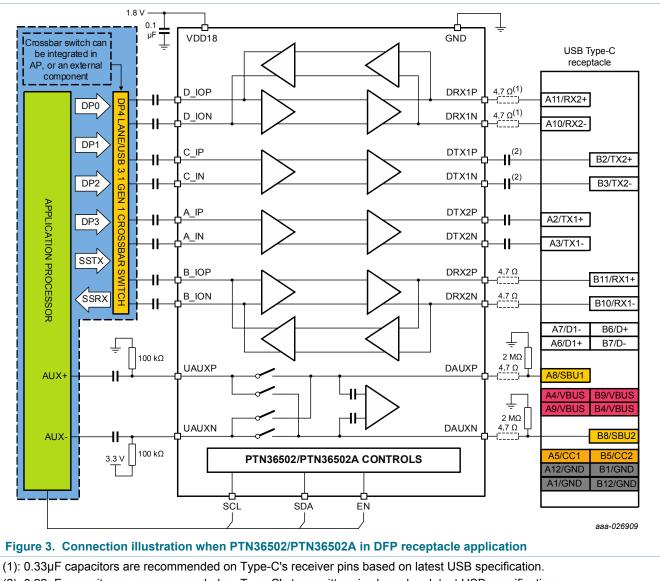

## 7.3 USB Type-C DFP receptacle application

(2): 0.22µF capacitors are recommended on Type-C's transmitter pins based on latest USB specification.

Refer to Figure 3 for using PTN36502/PTN36502A in USB Type-C DFP receptacle application. In this configuration, upstream (left) side of PTN36502/PTN36502A is connected to application processor with integrated or on-board crossbar switch function. and downstream (right) side is connected to Type-C receptacle.

Each pin on the downstream side of PTN36502/PTN36502A connecting to the Type-C connector has specific input/output configuration, and must match the signal assignments on the upstream side accordingly. Table 5 shows the downstream pin connection to Type-C receptacle.

PTN36502\_PTN36502A **Product data sheet**

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| PTN36502/PTN36502A pins |          | USB Type-C receptacle pins |          |  |

|-------------------------|----------|----------------------------|----------|--|

| Symbol                  | Pin name | Symbol                     | Pin name |  |

| 22                      | DRX1P    | A11                        | RX2+     |  |

| 21                      | DRX1N    | A10                        | RX2-     |  |

| 18                      | DTX1N    | В3                         | TX2-     |  |

| 17                      | DTX1P    | B2                         | TX2+     |  |

| 16                      | DTX2P    | A2                         | TX1+     |  |

| 15                      | DTX2N    | A3                         | TX1-     |  |

| 12                      | DRX2N    | B10                        | RX1-     |  |

| 11                      | DRX2P    | B11                        | RX1+     |  |

| 14                      | DAUXP    | A8                         | SBU1     |  |

| 13                      | DAUXN    | В8                         | SBU2     |  |

## Table 5. Downstream pin connection to Type-C receptacle in DFP application

The upstream pins of PTN36502/PTN36502A are connected to the application processor, with specific functions assigned to each differential signal. For each pin assignment configuration below, PTN36502/PTN36502A controls which transmitters or receivers to turn on or turn off, and operating in USB 3.1 Gen 1 mode, or DisplayPort mode according to the mode setting.

#### Table 6. Upstream pin connection to application processor in DFP receptacle application

| PTN36502/<br>PTN36502A<br>pins | Application | processor sig | ınal names    |        |                           |        |          |  |

|--------------------------------|-------------|---------------|---------------|--------|---------------------------|--------|----------|--|

| Symbol                         | Pin name    | USB 3.1 Ge    | USB 3.1 Gen 1 |        | USB 3.1 Gen 1 and DP2Lane |        | DP4Lane  |  |

|                                |             | Normal        | Reversed      | Normal | Reversed                  | Normal | Reversed |  |

| 23                             | D_ION       |               | SSRX-         | ML0-   | SSRX-                     | ML0-   | ML3-     |  |

| 24                             | D_IOP       |               | SSRX+         | ML0+   | SSRX+                     | ML0+   | ML3+     |  |

| 3                              | C_INP       |               | SSTX+         | ML1+   | SSTX+                     | ML1+   | ML2+     |  |

| 4                              | C_INN       |               | SSTX-         | ML1-   | SSTX-                     | ML1-   | ML2-     |  |

| 5                              | A_INP       | SSTX+         |               | SSTX+  | ML1+                      | ML2+   | ML1+     |  |

| 6                              | A_INN       | SSTX-         |               | SSTX-  | ML1-                      | ML2-   | ML1-     |  |

| 9                              | B_IOP       | SSRX+         |               | SSRX+  | ML0+                      | ML3+   | ML0+     |  |

| 10                             | B_ION       | SSRX-         |               | SSRX-  | ML0-                      | ML3-   | ML0-     |  |

| 7                              | UAUXP       |               |               | AUX+   | AUX+                      | AUX+   | AUX+     |  |

| 8                              | UAUXN       |               |               | AUX-   | AUX-                      | AUX-   | AUX-     |  |

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

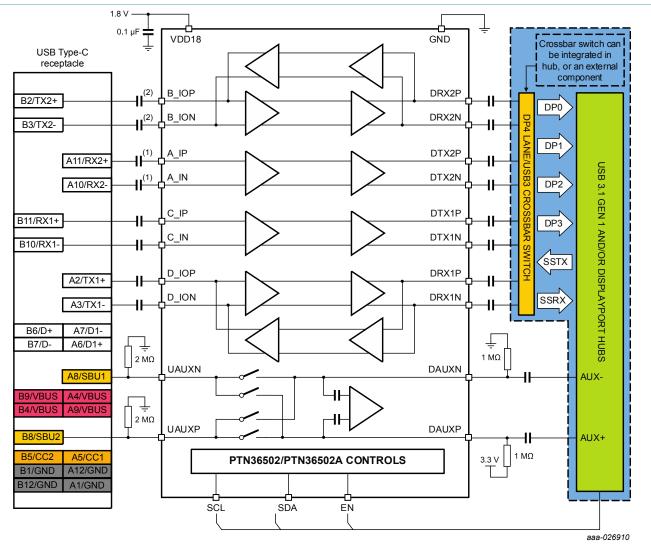

### 7.4 USB Type-C UFP receptacle application

Figure 4. Connection illustration when PTN36502/PTN36502A in UFP receptacle application

(1): 0.33µF capacitors are recommended on Type-C's receiver pins based on latest USB specification.

(2): 0.22µF capacitors are recommended on Type-C's transmitter pins based on latest USB specification.

Refer to Figure 4 for using PTN36502/PTN36502A in USB Type-C UFP receptacle application. In this configuration, downstream (right) side of PTN36502/PTN36502A is connected to USB 3.1 Gen 1 and/or DisplayPort hubs with integrated or on-board crossbar switch function, and upstream (left) side is connected to Type-C receptacle.

Each pin on the upstream side of PTN36502/PTN36502A connecting to the Type-C connector has specific input/output configuration, and must match the signal assignments on the downstream side accordingly. <u>Table 7</u> shows the upstream pin connection to Type-C receptacle.

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| PTN36502/PTN36502 | 2A pins  | USB Type-C recep | USB Type-C receptacle pins |  |  |

|-------------------|----------|------------------|----------------------------|--|--|

| Symbol            | Pin name | Symbol           | Pin name                   |  |  |

| 23                | D_ION    | A3               | TX1-                       |  |  |

| 24                | D_IOP    | A2               | TX1+                       |  |  |

| 3                 | C_INP    | B11              | RX1+                       |  |  |

| 4                 | C_INN    | B10              | RX1-                       |  |  |

| 5                 | A_INP    | A11              | RX2+                       |  |  |

| 6                 | A_INN    | A10              | RX2-                       |  |  |

| 9                 | B_IOP    | B2               | TX2+                       |  |  |

| 10                | B_ION    | B3               | TX2-                       |  |  |

| 7                 | UAUXP    | B8               | SBU2                       |  |  |

| 8                 | UAUXN    | A8               | SBU1                       |  |  |

## Table 7. Upstream pin connection to Type-C receptacle in UFP application

The downstream pins of PTN36502/PTN36502A are connected to the USB 3.1 Gen 1 and/or DisplayPort hubs, with specific functions assigned to each differential signal. For each pin assignment configuration below, PTN36502/PTN36502A controls which transmitters or receivers to turn on or turn off, and operating in USB 3.1 Gen 1 mode, or DisplayPort mode according to the mode setting.

## Table 8. Downstream pin connection to USB 3.1 Gen 1/DisplayPort hubs in UFP receptacle application

| PTN36502/PTN36502A<br>pins |          |         |          |                      |                           |        |          |  |

|----------------------------|----------|---------|----------|----------------------|---------------------------|--------|----------|--|

| Symbol                     | Pin name | USB 3.1 | Gen 1    | USB 3.1 G<br>DP2Lane | USB 3.1 Gen 1 and DP2Lane |        | DP4Lane  |  |

|                            |          | Normal  | Reversed | Normal               | Reversed                  | Normal | Reversed |  |

| 22                         | DRX1P    | SSTX+   |          | SSTX+                | ML0+                      | ML3+   | ML0+     |  |

| 21                         | DRX1N    | SSTX-   |          | SSTX-                | ML0-                      | ML3-   | ML0-     |  |

| 18                         | DTX1N    | SSRX-   |          | SSRX-                | ML1-                      | ML2-   | ML1-     |  |

| 17                         | DTX1P    | SSRX+   |          | SSRX+                | ML1+                      | ML2+   | ML1+     |  |

| 16                         | DTX2P    |         | SSRX+    | ML1+                 | SSRX+                     | ML1+   | ML2+     |  |

| 15                         | DTX2N    |         | SSRX-    | ML1-                 | SSRX-                     | ML1-   | ML2-     |  |

| 12                         | DRX2N    |         | SSTX-    | ML0-                 | SSTX-                     | ML0-   | ML3-     |  |

| 11                         | DRX2P    |         | SSTX+    | ML0+                 | SSTX+                     | ML0+   | ML3+     |  |

| 14                         | DAUXP    |         |          | AUX+                 | AUX+                      | AUX+   | AUX+     |  |

| 13                         | DAUXN    |         |          | AUX-                 | AUX-                      | AUX-   | AUX-     |  |

Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

### 7.5 USB Type-C UFP\_Dongle application

Figure 5. Connection illustration when PTN36502/PTN36502A in UFP\_Dongle application

(1): 0.33µF capacitors are recommended on Type-C's receiver pins based on latest USB specification.

(2): 0.22µF capacitors are recommended on Type-C's transmitter pins based on latest USB specification.

Refer to Figure 5 for using PTN36502/PTN36502A in USB Type-C UFP\_Dongle application. In this configuration, downstream (right) side of PTN36502/PTN36502A is connected to USB 3.1 Gen 1 and/or DisplayPort hubs with integrated or on-board crossbar switch function, and upstream (left) side is connected to Type-C plug.

Each pin on the upstream side of PTN36502/PTN36502A connecting to the Type-C connector has specific input/output configuration, and must match the signal assignments on the downstream side accordingly. <u>Table 9</u> shows the upstream pin connection to Type-C plug.

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| PTN36502/PTN3650 | 02A pins | USB Type-C recept | USB Type-C receptacle pins |  |  |

|------------------|----------|-------------------|----------------------------|--|--|

| Symbol           | Pin name | Symbol            | Pin name                   |  |  |

| 23               | D_ION    | A10               | RX2-                       |  |  |

| 24               | D_IOP    | A11               | RX2+                       |  |  |

| 3                | C_INP    | B2                | TX2+                       |  |  |

| 4                | C_INN    | В3                | TX2-                       |  |  |

| 5                | A_INP    | A2                | TX1+                       |  |  |

| 6                | A_INN    | A3                | TX1-                       |  |  |

| 9                | B_IOP    | B11               | RX1+                       |  |  |

| 10               | B_ION    | B10               | RX1-                       |  |  |

| 7                | UAUXP    | A8                | SBU1                       |  |  |

| 8                | UAUXN    | B8                | SBU2                       |  |  |

### Table 9. Upstream pin connection to Type-C plug UFP\_Dongle application

The downstream pins of PTN36502/PTN36502A are connected to the USB 3.1 Gen 1 and/or DisplayPort hubs, with specific functions assigned to each differential signal. For each pin assignment configuration below, PTN36502/PTN36502A controls which transmitters or receivers to turn on or turn off, and operating in USB 3.1 Gen 1 mode, or DisplayPort mode according to the mode setting.

A typical dongle has a fixed orientation design, usually the normal orientation. Therefore, only one CC line is connected on the USB Type-C plug, and the other CC line is being used for VCONN purpose. PTN36502/PTN36502A offers both normal and reversed orientation pin outs, and can be adapted to different layout requirements. However, in a typical dongle use case, only one orientation is necessary.

#### Table 10. Downstream pin connection to USB 3.1 Gen 1/DisplayPort hubs in UFP\_Dongle application

| PTN36502/<br>PTN36502A<br>pins | Hub signal names |            |               |        |                           |        |          |  |  |

|--------------------------------|------------------|------------|---------------|--------|---------------------------|--------|----------|--|--|

| Symbol                         | Pin name         | USB 3.1 Ge | USB 3.1 Gen 1 |        | USB 3.1 Gen 1 and DP2Lane |        | DP4Lane  |  |  |

|                                |                  | Normal     | Reversed      | Normal | Reversed                  | Normal | Reversed |  |  |

| 22                             | DRX1P            |            | SSTX+         | ML0+   | SSTX+                     | ML0+   | ML3+     |  |  |

| 21                             | DRX1N            |            | SSTX-         | ML0-   | SSTX-                     | ML0-   | ML3-     |  |  |

| 18                             | DTX1N            |            | SSRX-         | ML1-   | SSRX-                     | ML1-   | ML2-     |  |  |

| 17                             | DTX1P            |            | SSRX+         | ML1+   | SSRX+                     | ML1+   | ML2+     |  |  |

| 16                             | DTX2P            | SSRX+      |               | SSRX+  | ML1+                      | ML2+   | ML1+     |  |  |

| 15                             | DTX2N            | SSRX-      |               | SSRX-  | ML1-                      | ML2-   | ML1-     |  |  |

| 12                             | DRX2N            | SSTX-      |               | SSTX-  | ML0-                      | ML3-   | ML0-     |  |  |

| 11                             | DRX2P            | SSTX+      |               | SSTX+  | ML0+                      | ML3+   | ML0+     |  |  |

| 14                             | DAUXP            |            |               | AUX+   | AUX+                      | AUX+   | AUX+     |  |  |

| 13                             | DAUXN            |            |               | AUX-   | AUX-                      | AUX-   | AUX-     |  |  |

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

### 7.6 Control and programmability

PTN36502/PTN36502A implements ternary control IO logic on EN, C1/SCL, C2/SDA control pins to detect HIGH (connected to VDD), LOW (connected to GND) or left unconnected condition (OPEN/NC). These pins are 3.3 V tolerant in I<sup>2</sup>C mode, and 1.8 V tolerant in GPIO mode.

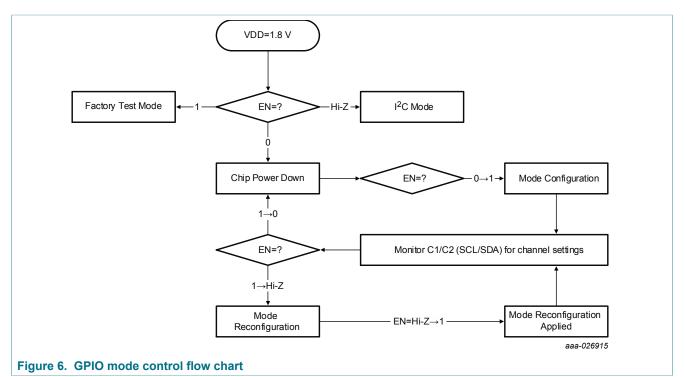

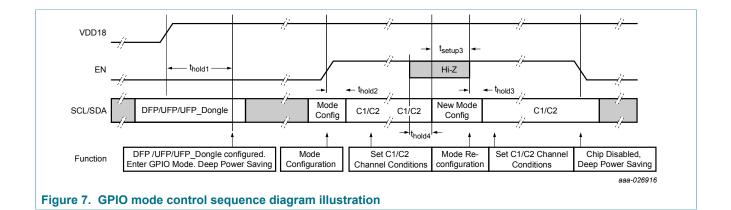

The following sections describe the individual block functions and capabilities of the device in more detail. In general, depending on the EN transition, there are specific functions for each transition state. Figure 6 and Figure 7 illustrate transitions described above. Hi-Z and OPEN/NC are used interchangeably in these figures.

PTN36502\_PTN36502A

Product data sheet

© NXP B.V. 2018. All rights reserved

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

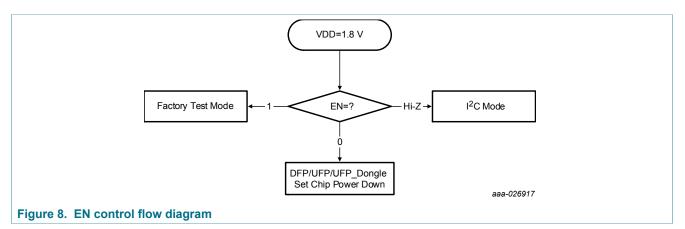

## 7.6.1 Operating mode selection (I<sup>2</sup>C mode or GPIO mode)

Upon POR, PTN36502/PTN36502A starts to detect the state of EN pin. If EN is not driven (or left OPEN) during POR, PTN36502/PTN36502A defaults to operate in I<sup>2</sup>C mode, and EN pin has no function after entering I<sup>2</sup>C mode. In I<sup>2</sup>C mode, PTN36502/PTN36502A is highly programmable. For more information, please reference <u>Section 7.6.6</u> for I<sup>2</sup>C register details.

If EN is driven LOW during POR (through a GPIO from host processor or external pull down resistor), the PTN36502/PTN36502A will be placed in GPIO mode. At the same time, PTN36502/PTN36502A is configured in DFP, UFP, or UFP\_Dongle modes depending on SCL/C1 and SDA/C2 pins' status (refer to <u>Table 11</u> below). By default, the chip is disabled in deep power saving mode after DFP/UFP/UFP\_Dongle configuration is detected. In the deep power saving mode, all PTN36502/PTN36502A line drivers and input receive paths are terminated to ground with hi-ohmic resistors and AUX switches are tri-stated, and mode configuration remains undetermined.

| Table 11  | EN control | forwariaua  | made esting  |  |

|-----------|------------|-------------|--------------|--|

| Table 11. | EN CONTO   | for various | mode setting |  |

| EN   | SCL/C1 | SDA/C2 | Mode                                                                                                                          |

|------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------|

| OPEN | х      | Х      | I <sup>2</sup> C Mode                                                                                                         |

| 0    | 0      | 0      | GPIO Mode – DFP Configuration, without external 4.7 $\Omega$ resistors on the DRXn pins.                                      |

|      | 0      | 1      | GPIO Mode – DFP Configuration, with external 4.7 $\Omega$ resistors added on the DRXn pins for higher level surge protection. |

|      | 1      | 0      | GPIO Mode – UFP Configuration.                                                                                                |

|      | 0      | 0      | GPIO Mode – UFP_Dongle Configuration.                                                                                         |

| 1    | x      | Х      | Reserved Operation Mode                                                                                                       |

### 7.6.2 Mode configuration through GPIO mode

Table 12, Table 13, and Table 14 show seven possible modes in which PTN36502/ PTN36502A can be configured while operating in DFP, UFP, or UFP plug modes respectively. Note that mode configuration setting is latched when EN transition from 0 to 1. When the mode needs to be reconfigured (for example, change from USB 3.1 Gen 1+DP2Lane mode to DP4Lane mode) after EN is 1, a GPIO controller can toggle EN pin to Hi-Z first and back to high again with new mode presented on SCL/C1 and SDA/

PTN36502\_PTN36502A Product data sheet

#### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

C2 pins. New mode value is latched when EN transition from Hi-Z to 1, and may take up to 0.2 milliseconds to take effect. When EN is toggled back to 0, mode configuration is cleared, and the PTN36502/PTN36502A is placed in deep power saving mode.

- C1/SCL indicates the orientation, 0 = normal orientation, 1 = reversed orientation

- C2/SDA indicates different mode configurations

- OPEN=USB 3.1 Gen 1 only, no AUX support

- 0 = USB 3.1 Gen 1 + DP 2Lane + AUX

- **–** 1 = DP 4Lane + AUX

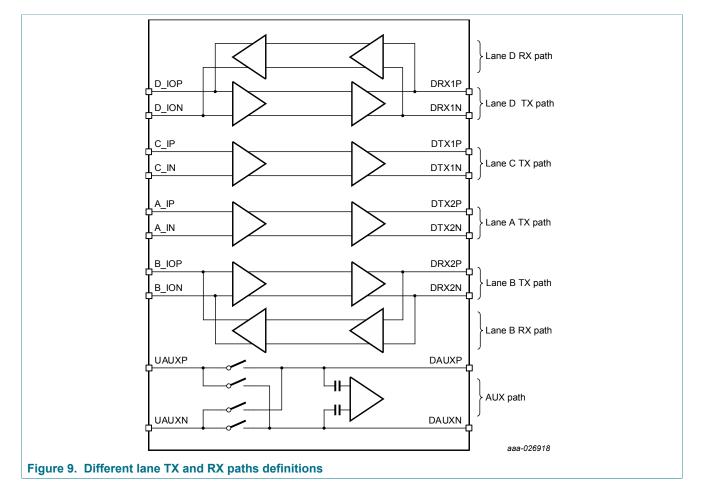

Definitions of different lane TX and RX paths in the tables are illustrated in Figure 9.

#### Table 12. PTN36502/PTN36502A DFP mode configuration

| EN                      | SCL/C1 | SDA/ C2 | Lane A<br>TX | Lane B<br>TX | Lane B<br>RX | Lane C<br>TX | Lane D<br>TX | Lane D<br>RX | AUX<br>Path | Mode            | Type-C<br>orientat<br>ion |

|-------------------------|--------|---------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-----------------|---------------------------|

| Transition<br>from 0 to | -      | OPEN    | SSTX         |              | SSRX         | [1]          |              | [1]          |             | USB<br>3.1 Gen  | Normal<br>(Or=0)          |

| 1                       | 1      | OPEN    | [1]          |              | [1]          | SSTX         |              | SSRX         |             | 1 Only<br>(M=1) | Reversed<br>(Or=1)        |

PTN36502\_PTN36502A

© NXP B.V. 2018. All rights reserved.

# PTN36502/PTN36502A

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| EN | SCL/C1 | SDA/ C2 | Lane A<br>TX | Lane B<br>TX | Lane B<br>RX | Lane C<br>TX | Lane D<br>TX | Lane D<br>RX | AUX<br>Path | Mode                   | Type-C<br>orientat<br>ion |

|----|--------|---------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|------------------------|---------------------------|

|    | 0      | 0       | SSTX         |              | SSRX         | ML1          | MLO          |              | Thru        | USB 3.1<br>Gen 1       | Normal<br>(Or=0)          |

|    | 1      | 0       | ML1          | ML0          |              | SSTX         |              | SSRX         | Cross       | & DP2<br>Lane<br>(M=2) | Reversed<br>(Or=1)        |

|    | 0      | 1       | ML2          | ML3          |              | ML1          | MLO          |              | Thru        | DP4<br>Lane            | Normal<br>(Or=0)          |

|    | 1      | 1       | ML1          | ML0          |              | ML2          | ML3          |              | Cross       | (M=3)                  | Reversed<br>(Or=1)        |

[1] Unused TX and RX pins are terminated to ground with hi-ohmic resistors

|                         |        |         |              |              | <b>J</b>     |              |              |              |             | 1                                          |                           |

|-------------------------|--------|---------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|--------------------------------------------|---------------------------|

| EN                      | SCL/C1 | SDA/ C2 | Lane A<br>TX | Lane B<br>TX | Lane B<br>RX | Lane C<br>TX | Lane D<br>TX | Lane D<br>RX | AUX<br>Path | Mode                                       | Type-C<br>orientat<br>ion |

| Transition<br>from 0 to | 0      | OPEN    | [1]          |              | [1]          | SSRX         |              | SSTX         |             | USB<br>3.1 Gen                             | Normal<br>(Or=0)          |

| 1                       | 1      | OPEN    | SSRX         |              | SSTX         | [1]          |              | [1]          |             | 1 Only<br>(M=1)                            | Reversed<br>(Or=1)        |

|                         | 0      | 0       | ML1          | ML0          |              | SSRX         |              | SSTX         | Thru        | USB 3.1<br>Gen 1<br>& DP2<br>Lane<br>(M=2) | Normal<br>(Or=0)          |

|                         | 1      | 0       | SSRX         |              | SSTX         | ML1          | ML0          |              | Cross       |                                            | Reversed<br>(Or=1)        |

|                         | 0      | 1       | ML1          | ML0          |              | ML2          | ML3          |              | Thru        | DP4Lane<br>(M=3)                           | Normal<br>(Or=0)          |

|                         | 1      | 1       | ML2          | ML3          |              | ML1          | ML0          |              | Cross       |                                            | Reversed<br>(Or=1)        |

#### Table 13. PTN36502/PTN36502A UFP mode configuration

[1] Unused TX and RX pins are terminated to ground with hi-ohmic resistors

#### Table 14. PTN36502/PTN36502A UFP\_Dongle mode configuration

| EN                      | SCL/C1 | SDA/ C2 | Lane A<br>TX | Lane B<br>TX | Lane B<br>RX | Lane C<br>TX | Lane D<br>TX | Lane D<br>RX | AUX<br>Path | Mode                   | Type-C<br>orientat<br>ion |

|-------------------------|--------|---------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|------------------------|---------------------------|

| Transition<br>from 0 to | 0      | OPEN    | SSRX         |              | SSTX         | [1]          |              | [1]          |             | USB<br>3.1 Gen         | Normal<br>(Or=0)          |

| 1                       | 1      | OPEN    | [1]          |              | [1]          | SSRX         |              | SSTX         |             | 1 Only<br>(M=1)        | Reversed<br>(Or=1)        |

|                         | 0      | 0       | SSRX         |              | SSTX         | ML1          | MLO          |              | Thru        | USB 3.1<br>Gen 1       | Normal<br>(Or=0)          |

|                         | 1      | 0       | ML1          | MLO          |              | SSRX         |              | SSTX         | Cross       | & DP2<br>Lane<br>(M=2) | Reversed<br>(Or=1)        |

## PTN36502/PTN36502A

#### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| EN | SCL/C1 | SDA/ C2 | Lane A<br>TX | Lane B<br>TX | Lane B<br>RX | Lane C<br>TX | Lane D<br>TX | Lane D<br>RX | AUX<br>Path | Mode        | Type-C<br>orientat<br>ion |

|----|--------|---------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|---------------------------|

|    | 0      | 1       | ML2          | ML3          |              | ML1          | MLO          |              | Thru        | DP4<br>Lane | Normal<br>(Or=0)          |

|    | 1      | 1       | ML1          | ML0          |              | ML2          | ML3          |              | Cross       | (M=3)       | Reversed<br>(Or=1)        |

[1] In USB 3.1 Gen 1 only mode, unused line drivers (TX) and input receivers (RX) are terminated to common mode (<2V) with hi-ohmic resistors

The AUX switch path remains enabled irrespective of DP lane sleep status as long as the mode is configured for DP support. The AUX switch path is disabled only during deep power saving state (when EN=0) or when mode is configured to USB 3.1 Gen 1 only mode (mode1).

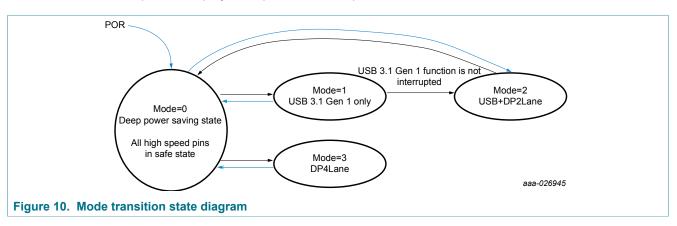

#### 7.6.3 Mode transitions

PTN36502/PTN36502A implements USB 3.1 Gen 1 (single port), and Combo (DP/USB) modes as per DP Alt mode specification. The mode transitions follow USB Safe state transition requirements of USB Type-C cable and Connection specification, USB Power Delivery and DisplayPort Alternate Mode specifications. <u>Figure 10</u> illustrates the various functional modes and deep power saving state transitions.

By default/POR, PTN36502/PTN36502A enters deep power saving mode state. In deep power saving mode, all high-speed pins are put in safe state by pulling these pins to ground with internal hi-ohmic resistors. The AUX switch path is disabled and AUX/SBU pins can be put in safe state by pulling these to ground by means of hi-ohmic resistors in the application. When a valid Type-C cable is connected, the host PD controller can first place PTN36502/PTN36502A in USB 3.1 Gen 1 mode (mode 1). If DP Alt mode is negotiated, PTN36502/PTN36502A adheres to the USB safe state requirements before making the mode transition. Except for transitions from Mode 1 to Mode 2, all other transitions need to happen via deep power saving state in order to meet USB Safe state requirements.

When transitioning from Mode 1 to Mode 2, the USB 3.1 Gen 1 connectivity is left undisturbed and 2-lane DP + AUX functionality is included. It is advised not to transition from Mode 2 back to Mode 1 directly; internal power management scheme automatically places DisplayPort operation in low power state.

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

#### 7.6.4 Channel settings for USB 3.1 Gen 1 mode

After EN pin is in steady state HIGH, C1/SCL and C2/SDA pins are used for upstream and downstream channel condition settings. PTN36502/PTN36502A samples these two pins every few milliseconds, and the configuration settings can be updated at any time, as long as EN is set to HIGH.

C1 controls signal traces on the upstream (left) side (as shown in Figure 3) of the redriver. It controls receive equalization, transmit de-emphasis and output swing interfacing pins with the host processor interface.

- When C1 = HIGH, the upstream (left) side of the redriver is optimized to drive long channel trace length

- When C1 = OPEN, the upstream (left) side of the redriver is optimized to drive medium channel trace length

- When C1 = LOW, the upstream (left) side of the redriver is optimized to drive short channel trace length

#### Table 15. Upstream channel configuration using C1 pin

| C1 state | Channel type | Upstream RX       | Upstream TX       |                   |

|----------|--------------|-------------------|-------------------|-------------------|

|          |              | EQ <sup>[1]</sup> | DE <sup>[2]</sup> | OS <sup>[3]</sup> |

| HIGH     | Long         | 9 dB              | -5.3 dB           | 1100 mV           |

| OPEN     | Medium       | 6 dB              | -3.1 dB           | 1000 mV           |

| LOW      | Short        | 3 dB              | 0 dB              | 900 mV            |

EQ is the input receiver equalization gain [1]

DE is the transmit output signal de-emphasis gain [2] [3]

OS is the transmit output differential voltage

C2 controls signal traces on the downstream (right) side with functionality similar to C1 (as shown in Figure 3). These pins are the Type-C connector in a DFP system.

#### Table 16. Downstream channel configuration using C2 pin

| C2 state | Channel type | Downstream RX     | Downstream TX     |                   |

|----------|--------------|-------------------|-------------------|-------------------|

|          |              | EQ <sup>[1]</sup> | DE <sup>[2]</sup> | OS <sup>[3]</sup> |

| HIGH     | Long         | 9 dB              | -5.3 dB           | 1100 mV           |

| OPEN     | Medium       | 6 dB              | -3.1 dB           | 1000 mV           |

| LOW      | Short        | 3 dB              | 0 dB              | 900 mV            |

EQ is the input receiver equalization gain

DE is the transmit output signal de-emphasis gain [2]

[3] OS is the transmit output differential voltage

### 7.6.5 Channel settings for DisplayPort mode

In GPIO mode, lane count, link rate, transmit output and pre-emphasis settings are determined by AUX DPCD commands. Only the input receive equalization is determined by C1 value. C2 is not used.

PTN36502\_PTN36502A **Product data sheet**

#### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| C1 state | Channel type | Upstream RX eq | Upstream RX equalization |          |  |  |  |  |

|----------|--------------|----------------|--------------------------|----------|--|--|--|--|

|          |              | 1.62 Gbps      | 2.7 Gbps                 | 5.4 Gbps |  |  |  |  |

| HIGH     | Long         | 4.5 dB         | 6 dB                     | 9 dB     |  |  |  |  |

| OPEN     | Medium       | 1.5 dB         | 3 dB                     | 6 dB     |  |  |  |  |

| LOW      | Short        | 0 dB           | 1.5 dB                   | 3 dB     |  |  |  |  |

#### Table 17. DisplayPort channel equalization settings

All lanes of DP redriver use the same setting in GPIO mode whereas they can be configured separately on a per lane basis. The transmit line driver output swing and preemphasis control settings are set based on AUX transactions during DP Link training and these can also be configured via  $l^2$ C-bus interface.

In I<sup>2</sup>C mode, AUX monitor training can be disabled with full control of output swing, preemphasis and RX equalization through I<sup>2</sup>C registers. If AUX monitor bit (in Register 0xoD) is enabled, the default value of output swing, pre-emphasis and RX equalization values will be based on the values in the I<sup>2</sup>C registers. After AUX monitor training, output swing and pre-emphasis will be adjusted; the RX equalization value is not modified.

### 7.6.6 I<sup>2</sup>C configurability

PTN36502/PTN36502A has an I<sup>2</sup>C register interface that enables system integrator to program register settings suitable as per application needs. <u>Table 18</u> describes possible settings for different functions of the device. Though the device can be pin configured through board-strapping or it also allows the system integrator to override those settings by programming the registers through I<sup>2</sup>C.

After power-on, the device samples EN pin and if it is OPEN, the device defaults to operate in  $I^2C$  mode. The system integrator must program the registers of the device for proper operation. Further, it is expected that the system integrator performs  $I^2C$  configuration after power-on and before data transport is initiated over the link. If such an operation is attempted during normal operation, the device may not behave as specified.

Note that registers 0x06, 0x07, 0x08, 0x09 and 0x0A hold DP link settings can be modified by AUX monitor; therefore, these registers do not necessarily hold the latest settings that are applied to the DP channel training through AUX.

| Register offset    | Register name            | Bits | POR default value | Description                                                                                                                                                     |

|--------------------|--------------------------|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00<br>Read Only  | Chip ID                  | 7:0  | b'0000 0010       | Chip ID Number                                                                                                                                                  |

| 0x01               | Chip Revision            | 7:4  | b`0001            | Chip base layer version                                                                                                                                         |

| Read Only          |                          | 3:0  | b`0010            | Chip metal layer version                                                                                                                                        |

| 0x02-0x03          | Reserved                 | 7:0  | Don't care        |                                                                                                                                                                 |

| 0x04<br>Read/Write | USB_US_TX/RX_<br>Control | 7:6  | b`01              | USB mode upstream (left) side link<br>de-emphasis level<br>• 0: de-emphasis = 0 dB<br>• 1: de-emphasis = -3.1 dB<br>• 2: de-emphasis = -5.3 dB<br>• 3: Reserved |

### Table 18. I<sup>2</sup>C registers and description

# PTN36502/PTN36502A

## Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| Register offset    | Register name            | Bits | POR default value | Description                                                                                                                                                                                                                            |

|--------------------|--------------------------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |                          | 5:4  | p.00              | <ul> <li>USB mode upstream (left) side link<br/>output signal swing</li> <li>0: output swing level = 900mVppd</li> <li>1: output swing level = 1000mVppd</li> <li>2: output swing level = 1100mVppd</li> <li>3: reserved</li> </ul>    |

|                    |                          | 3:0  | b`0010            | USB mode upstream (left) side link<br>Rx Equalization gain<br>• 0: 0 dB<br>• 1: 3 dB<br>• 2: 6 dB<br>• 3: 9 dB<br>• 4: 12 dB<br>• 5-15: reserved                                                                                       |

| 0x05<br>Read/Write | USB_DS_TX/RX_<br>Control | 7:6  | b`01              | USB mode downstream (right) side<br>link de-emphasis level<br>• 0: de-emphasis = 0 dB<br>• 1: de-emphasis = -3.1dB<br>• 2: de-emphasis = -5.1 dB<br>• 3: Reserved                                                                      |

|                    |                          | 5:4  | p.00              | <ul> <li>USB mode downstream (right) side<br/>link output signal swing</li> <li>0: output swing level = 900mVppd</li> <li>1: output swing level = 1000mVppd</li> <li>2: output swing level = 1100mVppd</li> <li>3: reserved</li> </ul> |

|                    |                          | 3:0  | b`0010            | USB mode downstream (right) side<br>link Rx Equalization gain<br>• 0: 0 dB<br>• 1: 3 dB<br>• 2: 6 dB<br>• 3: 9 dB<br>• 4: 12 dB<br>• 5-15: reserved                                                                                    |

| 0x06               | DP link control          | 7:5  | p,000             | Reserved                                                                                                                                                                                                                               |

| Read/Write         |                          | 4    | p.0               | DisplayPort Power saving mode<br>selection on all DP lanes.<br>• 0: Normal/Active mode<br>• 1: D3 Power saving mode                                                                                                                    |

|                    |                          | 3:2  | p.00              | <ul> <li>DisplayPort operating lane count.</li> <li>0: 0 DP Lane (i.e. USB 3.1 Gen 1<br/>Only)</li> <li>1: 1 DP Lane</li> <li>2: 2 DP lanes</li> <li>3: 4 DP lanes</li> </ul>                                                          |

# PTN36502/PTN36502A

## Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| Register offset | Register name    | Bits | POR default value | Description                                                                                                                                                      |

|-----------------|------------------|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                  | 1:0  | p.00              | DP Link rate<br>• 0: 1.62 Gbps (RBR)<br>• 1: 2.7 Gbps (HBR)<br>• 2: 5.4 Gbps (HBR2)<br>• 3: Reserved.                                                            |

| 0x07            | DP Lane 0 TX/RX  | 7    | b`0               | Reserved                                                                                                                                                         |

| Read/Write      | Control Register | 6:4  | p.000             | DP Lane 0 Rx equalization gain<br>control<br>• 0: 0 dB<br>• 1: 1.5 dB<br>• 2: 3 dB<br>• 3: 4.5 dB<br>• 4: 6 dB<br>• 5: 9 dB<br>• 6: 12dB<br>• 7: Reserved        |

|                 |                  | 3:2  | p.00              | DP Lane 0 TX output swing control<br>(When AUX monitor bit in 0x0D byte<br>is disabled)<br>• 0: 400 mVppd<br>• 1: 600 mVppd<br>• 2: 800 mVppd<br>• 3: 1100mVppd  |

|                 |                  | 1:0  | b`00              | DP Lane 0 pre-emphasis control<br>(When AUX monitor bit in 0x0D byte<br>is disabled)<br>• 0: 0 dB<br>• 1: 3.5 dB<br>• 2: 6 dB<br>• 3: 8.8 dB                     |

| 0x08            | DP Lane 1 TX/RX  | 7    | b`0               | Reserved                                                                                                                                                         |

| Read/Write      | Control Register | 6:4  | p.000             | DP Lane 1 Rx equalization gain<br>control<br>• 0: 0 dB<br>• 1: 1.5 dB<br>• 2: 3 dB<br>• 3: 4.5 dB<br>• 4: 6 dB<br>• 5: 9 dB<br>• 6: 12dB<br>• 7: Reserved        |

|                 |                  | 3:2  | p.00              | DP Lane 1 TX output swing control<br>(When AUX monitor bit in 0x0D byte<br>is disabled)<br>• 0: 400 mVppd<br>• 1: 600 mVppd<br>• 2: 800 mVppd<br>• 3: 1100 mVppd |

PTN36502\_PTN36502A

© NXP B.V. 2018. All rights reserved.

# PTN36502/PTN36502A

## Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| Register offset | Register name    | Bits | POR default value | Description                                                                                                                                                      |

|-----------------|------------------|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                  | 1:0  | p.00              | DP Lane 1 pre-emphasis control<br>(When AUX monitor bit in 0x0D byte<br>is disabled)<br>• 0: 0 dB<br>• 1: 3.5 dB<br>• 2: 6 dB<br>• 3: 8.8 dB                     |

| 0x09            | DP Lane 2 TX/RX  | 7    | b`0               | Reserved                                                                                                                                                         |

| Read/Write      | Control Register | 6:4  | p.000             | DP Lane 2 Rx equalization gain<br>control<br>• 0: 0 dB<br>• 1: 1.5 dB<br>• 2: 3 dB<br>• 3: 4.5 dB<br>• 4: 6 dB<br>• 5: 9 dB<br>• 6: 12dB<br>• 7: Reserved        |

|                 |                  | 3:2  | p.00              | DP Lane 2 TX output swing control<br>(When AUX monitor bit in 0x0D byte<br>is disabled)<br>• 0: 400 mVppd<br>• 1: 600 mVppd<br>• 2: 800 mVppd<br>• 3: 1100 mVppd |

|                 |                  | 1:0  | p.00              | DP Lane 2 pre-emphasis control<br>(When AUX monitor bit in 0x0D byte<br>is disabled)<br>• 0: 0 dB<br>• 1: 3.5 dB<br>• 2: 6 dB<br>• 3: 8.8 dB                     |

| 0x0A            | DP Lane 3 TX/RX  | 7    | b`0               | Reserved                                                                                                                                                         |

| Read/Write      | Control Register | 6:4  | p.000             | DP Lane 3 Rx equalization gain<br>control<br>• 0: 0 dB<br>• 1: 1.5 dB<br>• 2: 3 dB<br>• 3: 4.5 dB<br>• 4: 6 dB<br>• 5: 9 dB<br>• 6: 12 dB<br>• 7: Reserved       |

# PTN36502/PTN36502A

## Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| Register offset    | Register name  | Bits | POR default value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|----------------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |                | 3:2  | p.00              | DP Lane 3 TX output swing control<br>(When AUX monitor bit in 0x0D byte<br>is disabled)<br>• 0: 400 mVppd<br>• 1: 600 mVppd<br>• 2: 800 mVppd<br>• 3: 1100 mVppd                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    |                | 1:0  | p.00              | DP Lane 3 pre-emphasis control<br>(When AUX monitor bit in 0x0D byte<br>is disabled)<br>• 0: 0 dB<br>• 1: 3.5 dB<br>• 2: 6 dB<br>• 3: 8.8 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x0B<br>Read/Write | Mode control 1 | 7:6  | p.00              | <ul> <li>DFP or /UFP application mode</li> <li>0: DFP configuration, without external 4.7Ω resistors on the DRXn pins. This setting also applies to UFP_Dongle configuration.</li> <li>1: DFP configuration, with external 4.7Ω resistors on the DRXn pins for higher level surge protection</li> <li>2: UFP configuration.</li> <li>3: Reserved (DFP/UFP application mode must be set once before taking PTN36502/PTN36502A out of deep power saving state. Changing these bits after the operational mode of the device is set to a mode other than deep power saving state is not allowed)</li> </ul> |

|                    |                | 5    | p.0               | <ul> <li>Plug orientation control. This orientation condition applies to both high speed TX/RX configuration and AUX crossbar switch.</li> <li>0: normal plug orientation of Type-C connection</li> <li>1: reverse plug orientation of Type-C connection</li> </ul>                                                                                                                                                                                                                                                                                                                                      |

|                    |                | 4    | p.0               | <ul> <li>AUX monitor polarity control.</li> <li>0: Polarity automatically controlled<br/>by plug orientation configuration</li> <li>1: reverse polarity with respect to<br/>automatically controlled polarity.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                |

|                    |                | 3    | p.0               | <ul> <li>AUX crossbar switch control</li> <li>0: AUX switch path disabled.<br/>(AUX switch is in high-Z state; but<br/>AUX monitor is still connected to<br/>DAUXP/N pins)</li> <li>1: AUX switch path enabled in DP<br/>mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 |

**Product data sheet**

27 / 58

# PTN36502/PTN36502A

### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver

| Register offset    | Register name     | Bits | POR default value | Description                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|-------------------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |                   | 2:0  | p,000             | <ul> <li>Operational mode of the device.</li> <li>Refer to 7.6.3 for mode transition requirement.</li> <li>0: Deep power saving state</li> <li>1: USB 3.1 Gen 1 only</li> <li>2: USB 3.1 Gen 1 and 2-lane DP</li> <li>3: 4-lane DP</li> <li>4-7: Reserved</li> </ul>                                                                                                             |

| 0X0C<br>Read/Write | Squelch threshold | 7:4  | b'0001            | Upstream side (left) squelch threshold<br>setting<br>• 0: 75mVpp<br>• 1: 80mVpp<br>• 2: 90mVpp<br>• 3: 100mVpp<br>• Other values are reserved                                                                                                                                                                                                                                    |

|                    |                   | 3:0  | b'0001            | Downstream side (right) squelch<br>threshold setting<br>• 0: 75mVpp<br>• 1: 80mVpp<br>• 2: 90mVpp<br>• 3: 100mVpp<br>• Other values are reserved                                                                                                                                                                                                                                 |

| 0x0D<br>Read/Write | Device control    | 7    | b`1               | <ul> <li>AUX monitoring function</li> <li>0: Disabled. DisplayPort OS/DE settings are adjusted through GPIO/ I<sup>2</sup>C registers.</li> <li>1: Enabled. DisplayPort OS/DE settings are adjusted autonomously by monitoring AUX channel traffic.</li> </ul>                                                                                                                   |

|                    |                   | 6:1  | b`000000          | Reserved                                                                                                                                                                                                                                                                                                                                                                         |

|                    |                   | 0    | p.0               | <ul> <li>Device Reset bit. This is a self-clearing bit, and reading this register will always return 0.</li> <li>Writing a '1' to this register will soft reset the device including I<sup>2</sup>C register contents and internal digital logics, while the chip continuing to operating under I<sup>2</sup>C mode.</li> <li>Writing a '0' does not have any effect.</li> </ul> |

| 0x0E-0x1F          | Reserved          |      |                   | Reserved for NXP Internal use only;<br>Do not write to these registers                                                                                                                                                                                                                                                                                                           |

| 0x20-0xFF          | Reserved          |      |                   | Reserved for NXP Internal use only;<br>Do not write to these registers                                                                                                                                                                                                                                                                                                           |

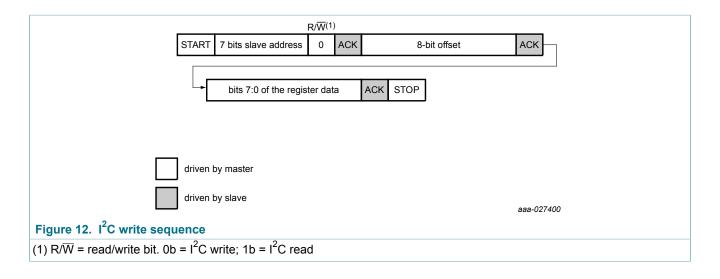

## 7.6.7 I<sup>2</sup>C read/write operations

PTN36502/PTN36502A has an  $I^2C$  register interface that enables system integrator to program register settings suitable as per application needs. <u>Table 18</u> describes possible

#### Type-C USB 3.1 Gen 1 and DisplayPort v1.2 combo redriver