# **PTN3816**

# DisplayPort 20Gbps 4-lane linear redriver

Rev. 1.0 — 7 June 2021

Product data sheet

## 1 General description

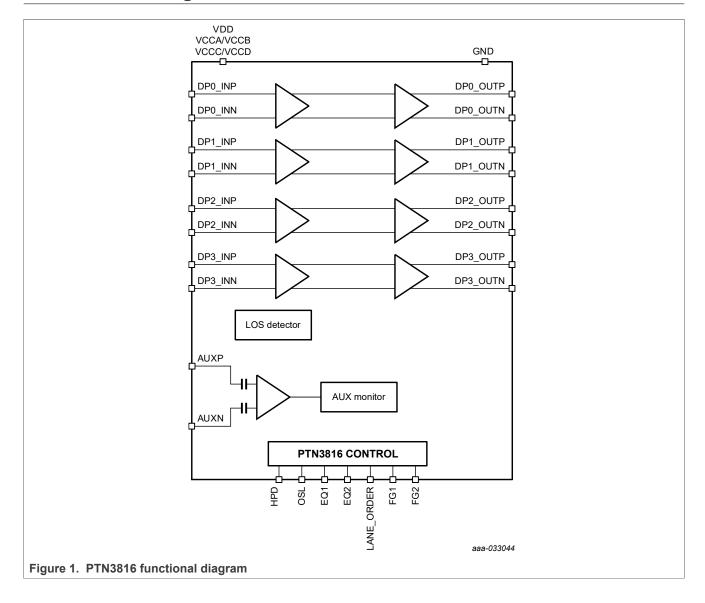

PTN3816 is a high performance 20 Gbps per lane, 4-lane DisplayPort linear redriver for DisplayPort upstream (DP source side) and downstream (DP Sink side) applications. It is used to improve high speed signal quality in DisplayPort interfaces in various platforms and applications.

The device provides pin programmable receive equalization, output linearity control to improve signal integrity and enable channel extension by reducing Inter-Symbol Interference (ISI). This IC also implements AUX snooping to monitor the AUX signals to optimally configure the link and achieve power saving and SI performance.

PTN3816 has control pins for application specific configurability. These pins can either be strapped appropriately on the PCB or connected to a microcontroller's GPIO pins. PTN3816 does not require any I2C software configuration.

PTN3816 is powered from 1.8 V supply. It is available in a small high performance HWFLGA36 package with 2.1 mm x 6.0 mm x 0.6 mm size and 0.4 mm pitch.

### 2 Features and benefits

- Implements DisplayPort linear redriver that can operate for various link rates -1.62 Gbps (RBR), 2.7 Gbps (HBR), 5.4 Gbps (HBR2) 8.1 Gbps (HBR3), 10, 13.5 and 20 Gbps

- Supports configurable number of lanes: 1, 2 and 4

- DP AUX monitoring for link configuration and power management

- Implements HPD for deep power saving

- Configurable Rx Equalizer gain

- Configurable output swing linearity control

- High Speed redriver path supports DP++ mode that targets DP to HDMI interface use

- Supports maximum voltage limit (V<sub>voltage\_jump</sub>) to align to the latest system platform capabilities

- Integrated termination resistors provide impedance matching on transmit and receive sides

- Good linearity over the frequency band (50 MHz to 10.3 GHz) and voltage dynamic range

- Excellent Differential return loss performance: < -16 dB up to 10.3 GHz

- Flow-through pin-out to ease PCB layout and minimize crosstalk effects

- Low active current consumption for output linearity control setting of 950 mVppd

1-lane DP: 62 mA (typ)2-lane DP: 125 mA (typ)4-lane DP: 250 mA (typ)

## DisplayPort 20Gbps 4-lane linear redriver

- · Power-saving state:

- DisplayPort sleep D3 mode: 3.2 mA (typ)

- 10 μA (typ) when in deep power-saving state (when HPD is LOW)

- · Configurable via GPIO control pins

- Power Supply 1.7 V to 1.9 V

- Small high performance HWFLGA36 package

- 2.1 mm x 6.0 mm x 0.6 mm with 0.4 mm pitch

- ESD HBM 1.5 kV CDM 1 kV

- Operating temperature range -20 °C to +85 °C

# 3 Applications

- DisplayPort source applications

- Smartphones and tablets

- Notebooks, AIO and desktop computers

- Hub or dock devices

- · DisplayPort sink applications

- Docking stations

- Display units

# 4 Ordering information

### Table 1. Ordering information

| Type number | Topside marking | Package |                                                                                |           |  |  |

|-------------|-----------------|---------|--------------------------------------------------------------------------------|-----------|--|--|

|             |                 | Name    | Description                                                                    | Version   |  |  |

| PTN3816EW   | 16              |         | plastic thermal enhanced very very thin fine-<br>pitch land grid array package | SOT1948-1 |  |  |

## 4.1 Ordering options

### Table 2. Ordering options

| Type number | Orderable part number | Package  | Packing method                | Minimum order quantity | Temperature                        |

|-------------|-----------------------|----------|-------------------------------|------------------------|------------------------------------|

| PTN3816EW   | PTN3816EWY            | HWFLGA36 | reel dry pack, SMD,<br>13" Q1 | 7000                   | T <sub>amb</sub> = -20 °C to 85 °C |

DisplayPort 20Gbps 4-lane linear redriver

# 5 Functional diagram

DisplayPort 20Gbps 4-lane linear redriver

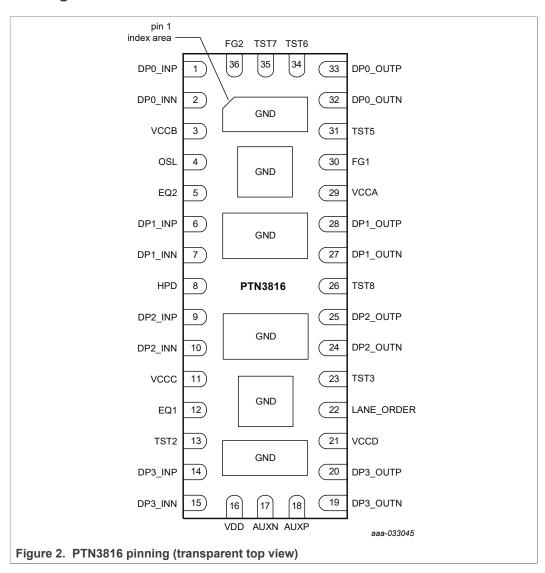

# 6 Pinning information

## 6.1 Pinning

## 6.2 Pin description

Table 3. Pin description

| Symbol | Pin     | Туре         | Description                                                                                     |

|--------|---------|--------------|-------------------------------------------------------------------------------------------------|

| 1      | DP0_INP | Self-biasing | Differential signal high-speed Rx input. DP0_                                                   |

| 2      | DP0_INN | •            | INP makes a differential pair with DP0_INN. The associated output pair is DP0_OUTP and DP0_OUTN |

## DisplayPort 20Gbps 4-lane linear redriver

Table 3. Pin description...continued

| Symbol | Pin        | Туре                          | Description                                                                                                                                       |  |  |

|--------|------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 29     | VCCA       | Power pins for high-          | These dedicated power pins for high-speed                                                                                                         |  |  |

| 3      | VCCB       | speed paths                   | differential pairs provide good signal integrity and noise isolation.                                                                             |  |  |

| 11     | VCCC       |                               |                                                                                                                                                   |  |  |

| 21     | VCCD       |                               |                                                                                                                                                   |  |  |

| 4      | OSL        | Ternary control input         | Ternary input for controlling output swing linearity (-1 dB compression point) of the line driver. Please refer to Section 7.3 for details.       |  |  |

| 12     | EQ1        | Ternary control inputs        | EQ1 and EQ2 are Receive equalization peaking                                                                                                      |  |  |

| 5      | EQ2        |                               | gain setting pins of the chip. Please refer to Section 7.3 for details.                                                                           |  |  |

| 6      | DP1_INP    | Self-biasing                  | Differential signal from high-speed RX path. DP1_                                                                                                 |  |  |

| 7      | DP1_INN    | differential input            | INP makes a differential pair with DP1_INN. The associated TX output pair is DP1_OUTP and DP1_OUTN                                                |  |  |

| 8      | HPD        | CMOS control input            | This pin is connected to Hot Plug Detect signal of DisplayPort interface and it controls whether the IC is in Deep power saving mode or otherwise |  |  |

| 9      | DP2_INP    | Self-biasing                  | Differential signal from high-speed RX path. DP                                                                                                   |  |  |

| 10     | DP2_INN    | differential input            | INP makes a differential pair with DP2_INN. The associated output pair is DP2_OUTP and DP2_OUTN                                                   |  |  |

| 13     | TST2       | Reserved Test pin             | This pin is connected to GND in the application                                                                                                   |  |  |

| 14     | DP3_INP    | Self-biasing                  | Differential signal high-speed Rx input. DP3_                                                                                                     |  |  |

| 15     | DP3_INN    | differential input/<br>output | INP makes a differential pair with DP3_INN. The associated output pair is DP3_OUTP and DP3_OUTN                                                   |  |  |

| 16     | VDD        | Power                         | 1.8 V Supply for AUX snooping and digital blocks                                                                                                  |  |  |

| 17     | AUXN       | Input                         | AUX channel snooping input                                                                                                                        |  |  |

| 18     | AUXP       |                               |                                                                                                                                                   |  |  |

| 19     | DP3_OUTN   | Self-biasing                  | Differential signal high-speed Rx input. DP3_OUTP                                                                                                 |  |  |

| 20     | DP3_OUTP   | differential input/<br>output | makes a differential pair with DP3_OUTN. The associated output pair is DP3_INP and DP3_INN                                                        |  |  |

| 22     | LANE_ORDER | CMOS control Input            | This pin is used to control DP lane order control – DP0/1/2/3 or DP3/2/1/0. Refer to <u>Table 7</u> for more details                              |  |  |

| 23     | TST3       | Reserved Test pin             | This pin is connected to GND in the application                                                                                                   |  |  |

| 24     | DP2_OUTN   | Self-biasing                  | Differential signal high-speed output. DP2_OUTP                                                                                                   |  |  |

| 25     | DP2_OUTP   | differential output           | makes a differential pair with DP2_OUTN. The associated input pair is DP2_INP and DP2_INN.                                                        |  |  |

| 26     | TST8       | Reserved Test pin             | Reserved for test purpose only. Must be connected to GND in the system application                                                                |  |  |

| 27     | DP1_OUTN   | Self-biasing                  | Differential signal high-speed output. DP1_OUTP makes a differential pair with DP1_OUTN. The associated input pair is DP1_INP and DP1_INN.        |  |  |

| 28     | DP1_OUTP   | differential output           |                                                                                                                                                   |  |  |

DisplayPort 20Gbps 4-lane linear redriver

Table 3. Pin description...continued

| Symbol      | Pin      | Туре                  | Description                                                                                                    |  |  |

|-------------|----------|-----------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| 30          | FG1      | Ternary control input | Ternary input for controlling flat gain setting of the output driver. Please refer to Section 7.3 for details. |  |  |

| 31          | TST5     | Reserved Test pin     | Reserved for test purpose only. Must be connected to GND in the system application                             |  |  |

| 32          | DP0_OUTN | Self-biasing          | Differential signal high-speed output. DP0_OUTP                                                                |  |  |

| 33          | DP0_OUTP | differential output   | makes a differential pair with DP0_OUTN. The associated input pair is DP0_INP and DP0_INN.                     |  |  |

| 34          | TST6     | Reserved Test pins    | This pin is connected to GND in the application                                                                |  |  |

| 35          | TST7     |                       |                                                                                                                |  |  |

| 36          | FG2      | Ternary control input | Ternary input for controlling flat gain setting of the output driver. Please refer to Section 7.3 for details. |  |  |

| Center pads | GND      |                       | These six center pads must be connected to GND plane for both electrical grounding and thermal relief          |  |  |

## 7 Functional description

## 7.1 DisplayPort operation

PTN3816 implements signal equalization to compensate for channel ISI loss and it supports DP operation at 1.62 Gbps, 2.7 Gbps, 5.4 Gbps, 8.1 Gbps, 10 Gbps, 13.5 Gbps and 20 Gbps. It provides configurability for receive equalization and output swing linearity control (EQ1, EQ2, OSL, FG1, FG2). It also performs AUX monitoring and decodes select AUX commands. It detects HPD level and determine whether to enter or exit Deep power saving state.

The DP lane count is configured during link training phase based on AUX communication exchanges between DP source and DP sink. PTN3816 uses lane count for configuring its high-speed lanes. It is possible that only a subset of lanes gets selected during DP Link training and the remaining lanes are not active. Depending on the number of lanes selected, PTN3816 is configured to operate with the selected lane count thereby saving power consumption on unused lanes.

The DP source can activate power down via AUX command. DP spec supports two modes – D0 or D3/Low power mode. In D0 mode, the linear redriver data path is active depending on the state of the DP link. In D3 mode, the AUX snooping logic is active while high-speed path is disabled resulting in lower current consumption.

### 7.2 AUX monitoring and configuration

PTN3816 monitors DP AUX communication exchanges that occur between DP source and DP sink. It detects AUX communication involving DPCD register controls – count, sleep, wake and configures its operation suitably.

The list of DPCD registers (with only the relevant bit fields) supported are as follows:

- LANE COUNT SET

- SET POWER

- Other DPCD registers and I<sup>2</sup>C over AUX transactions are not decoded

PTN3816

DisplayPort 20Gbps 4-lane linear redriver

When the Lane count is being initialized via AUX command, the acceptable values are 1, 2, and 4. If AUX command tries to set it to 0, PTN3816 ignores it, and continues with the last known legal value.

### 7.3 Redriver control and programmability

PTN3816 allows for programming of linear redriver functions – receive equalizer and output swing linearity as shown in <u>Table 4</u>, <u>Table 5</u> and <u>Table 6</u> below. In addition, LANE\_ORDER is used to inform the PTN3816 to consider specific lane ordering on its high-speed input and output. It is necessary for the redriver to know the lane ordering given that AUX monitor configures the lanes based on lane-count selection. <u>Table 7</u> and <u>Table 8</u> capture HPD control and Lane ordering scheme implemented in PTN3816.

Table 4. EQ[2:1] configuration: Flat gain 0.7 dB

Peaking Gain is the equalization gain at specific frequency relative to gain at 100 MHz and for typical Flat Gain (FG) value of 0.7 dB

| EQ2  | EQ1  | Unit | Gain at<br>100 MHz | 0.81 GHz | 1.35 GHz | 2.7 GHz | 4.05 GHz | 6.75 GHz | 8 GHz | 10 GHz |

|------|------|------|--------------------|----------|----------|---------|----------|----------|-------|--------|

| LOW  | OPEN | dB   | 0.5                | -0.2     | -0.4     | -0.1    | 0.1      | 1.0      | 1.6   | 2.0    |

| OPEN | LOW  | dB   | 0.5                | -0.1     | -0.3     | 0.1     | 0.4      | 1.5      | 2.3   | 2.8    |

| HIGH | HIGH | dB   | 0.5                | 0.1      | 0.0      | 0.7     | 1.3      | 3.0      | 4.1   | 5.4    |

| HIGH | OPEN | dB   | 0.5                | 0.6      | 0.5      | 1.6     | 2.6      | 5.1      | 6.6   | 8.4    |

| HIGH | LOW  | dB   | 0.6                | 1.1      | 1.3      | 2.8     | 4.2      | 7.5      | 9.3   | 11.6   |

| OPEN | HIGH | dB   | 0.6                | 1.7      | 2.0      | 4.0     | 5.7      | 9.7      | 11.7  | 14.2   |

| LOW  | HIGH | dB   | 0.6                | 2.4      | 2.8      | 5.3     | 7.4      | 11.9     | 14.2  | 16.8   |

| OPEN | OPEN | dB   | 0.7                | 2.9      | 3.7      | 6.2     | 8.6      | 13.6     | 15.9  | 18.4   |

| LOW  | LOW  | dB   | 0.7                | 2.9      | 3.7      | 6.2     | 8.6      | 13.6     | 16.0  | 18.4   |

Table 5. EQ[2:1] configuration: Flat gain -0.7 dB

Peaking Gain is the equalization gain at specific frequency relative to gain at 100 MHz and for typical Flat Gain (FG) value of -0.7 dB

| EQ2  | EQ1  | Unit | Gain at<br>100 MHz | 0.81 GHz | 1.35 GHz | 2.7 GHz | 4.05 GHz | 6.75 GHz | 8 GHz | 10 GHz |

|------|------|------|--------------------|----------|----------|---------|----------|----------|-------|--------|

| LOW  | OPEN | dB   | -1.1               | -0.1     | -0.2     | 0.6     | 1.3      | 2.6      | 3.4   | 3.8    |

| OPEN | LOW  | dB   | -1.1               | 0.0      | -0.1     | 0.8     | 1.6      | 3.1      | 4.0   | 4.6    |

| HIGH | HIGH | dB   | -1.1               | 0.3      | 0.2      | 1.6     | 2.6      | 4.7      | 5.9   | 7.2    |

| HIGH | OPEN | dB   | -1.1               | 0.9      | 1.0      | 2.7     | 4.0      | 6.9      | 8.4   | 10.2   |

| HIGH | LOW  | dB   | -1.0               | 1.6      | 2.0      | 4.0     | 5.8      | 9.3      | 11.1  | 13.3   |

| OPEN | HIGH | dB   | -1.0               | 2.3      | 2.8      | 5.3     | 7.4      | 11.4     | 13.4  | 15.9   |

| LOW  | HIGH | dB   | -1.0               | 3.1      | 3.8      | 6.7     | 9.1      | 13.6     | 15.8  | 18.4   |

| OPEN | OPEN | dB   | -0.9               | 3.7      | 4.7      | 7.7     | 10.2     | 15.2     | 17.5  | 20     |

| LOW  | LOW  | dB   | -0.9               | 3.7      | 4.7      | 7.7     | 10.2     | 15.2     | 17.6  | 20     |

## DisplayPort 20Gbps 4-lane linear redriver

Table 6. OSL configuration

| · · · · · · · · · · · · · · · · · · · |                                                                            |  |  |  |  |

|---------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| OSL                                   | Line driver output swing linearity (OSL) governing -1 dB compression level |  |  |  |  |

| OPEN                                  | 650 mVppd                                                                  |  |  |  |  |

| LOW                                   | 800 mVppd                                                                  |  |  |  |  |

| HIGH                                  | 950 mVppd                                                                  |  |  |  |  |

Table 7. Lane ordering configuration

| LANE_ORDER | PTN3816 High speed<br>Input pins                       | PTN3816 High speed output pins                    |

|------------|--------------------------------------------------------|---------------------------------------------------|

|            | Source Lane0(p) → DP0_INP<br>Source Lane0(n) → DP0_INN | DP0_OUTP → Sink Lane0(p) DP0_OUTN → Sink Lane0(n) |

|            | Source Lane1(p) → DP1_INP<br>Source Lane1(n) → DP1_INN | DP1_OUTP → Sink Lane1(p) DP1_OUTN → Sink Lane1(n) |

|            | Source Lane2(p) → DP2_INP<br>Source Lane2(n) → DP2_INN | DP2_OUTP → Sink Lane2(p) DP2_OUTN → Sink Lane2(n) |

| LOW        | Source Lane3(p) → DP3_INP<br>Source Lane3(n) → DP3_INN | DP3_OUTP → Sink Lane3(p) DP3_OUTN → Sink Lane3(n) |

|            | Source Lane3(p) → DP0_INP<br>Source Lane3(n) → DP0_INN | DP0_OUTP → Sink Lane3(p) DP0_OUTN → Sink Lane3(n) |

|            | Source Lane2(p) → DP1_INP<br>Source Lane2(n) → DP1_INN | DP1_OUTP → Sink Lane2(p) DP1_OUTN → Sink Lane2(n) |

|            | Source Lane1(p) → DP2_INP<br>Source Lane1(n) → DP2_INN | DP2_OUTP → Sink Lane1(p) DP2_OUTN → Sink Lane1(n) |

| HIGH       | Source Lane0(p) → DP3_INP<br>Source Lane0(n) → DP3_INN | DP3_OUTP → Sink Lane0(p) DP3_OUTN → Sink Lane0(n) |

Table 8. HPD configuration

| HPD  | PTN3816 device state                                                            |

|------|---------------------------------------------------------------------------------|

| LOW  | Deep power saving state                                                         |

| HIGH | Operational mode (D3 or D0 mode depending on AUX command or high-speed traffic) |

Table 9. Flat gain configuration

| FG2  | FG1  | Flat gain (dB) of individual DP lanes |        |        |        |  |  |

|------|------|---------------------------------------|--------|--------|--------|--|--|

|      |      | Lane 3                                | Lane 2 | Lane 1 | Lane 0 |  |  |

| LOW  | LOW  | 0.7                                   | 0.7    | 0.7    | 0.7    |  |  |

| LOW  | OPEN | 0.7                                   | 0.7    | 0.7    | -0.7   |  |  |

| LOW  | HIGH | 0.7                                   | 0.7    | -0.7   | 0.7    |  |  |

| OPEN | LOW  | 0.7                                   | 0.7    | -0.7   | -0.7   |  |  |

| OPEN | OPEN | 0.7                                   | -0.7   | 0.7    | 0.7    |  |  |

PTN3816 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2021. All rights reserved.

DisplayPort 20Gbps 4-lane linear redriver

Table 9. Flat gain configuration...continued

| FG2  | FG1  | Flat gain (dB) of individual DP lanes |        |        |        |  |  |

|------|------|---------------------------------------|--------|--------|--------|--|--|

|      |      | Lane 3                                | Lane 2 | Lane 1 | Lane 0 |  |  |

| OPEN | HIGH | 0.7                                   | -0.7   | -0.7   | 0.7    |  |  |

| HIGH | LOW  | -0.7                                  | 0.7    | 0.7    | 0.7    |  |  |

| HIGH | OPEN | -0.7                                  | -0.7   | 0.7    | 0.7    |  |  |

| HIGH | HIGH | -0.7                                  | -0.7   | -0.7   | -0.7   |  |  |

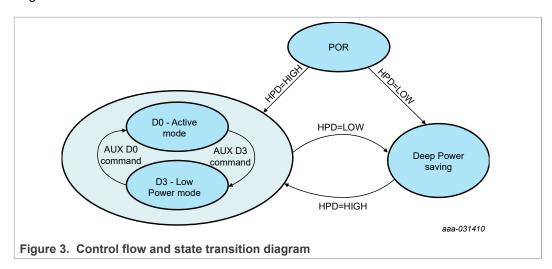

### 7.4 Control flow

The HPD pin of PTN3816 overrides all other control inputs/signals. This input pin can be changed dynamically at any time based on Source-sink connectivity status. After POR, PTN3816 checks the HPD pin. If it is LOW, PTN3816 defaults to Deep power saving state and if it is HIGH, the device goes into normal operating mode (and held in D3 mode) waiting for AUX communication or DP high speed traffic. The signal detector at high speed input determines whether the DP signal crosses the LoS threshold level. The AUX communication exchanged between DP source and sink is monitored by PTN3816 and the mode change (D3←→D0) is affected accordingly.

The configuration pins – EQ1, EQ2, FG1, FG2 and OSL can be changed dynamically at any time.

In deep power saving state, PTN3816 line drivers and input receive paths are terminated to ground with hi-ohmic resistors.

The HPD signal is debounced for 100 ms (min) for HIGH to LOW transitions. With this, when HPD goes LOW due to display sink disconnect will trigger PTN3816 to transition to Deep power saving state. The IRQ\_HPD event (≤2 ms duration) does not impact the operational state of PTN3816.

### 7.5 Signal detectors

PTN3816 implements Loss of (High-speed) Signal detector aka LOS detector (LoS threshold of 45 mVppd typ) – this function is meant to detect the presence of high-speed signaling at the high-speed input pins. Based on LOS detector output, PTN3816

DisplayPort 20Gbps 4-lane linear redriver

implements power management to optimizes current consumption under DP (D0 vs D3) mode and especially under electrical Idle conditions.

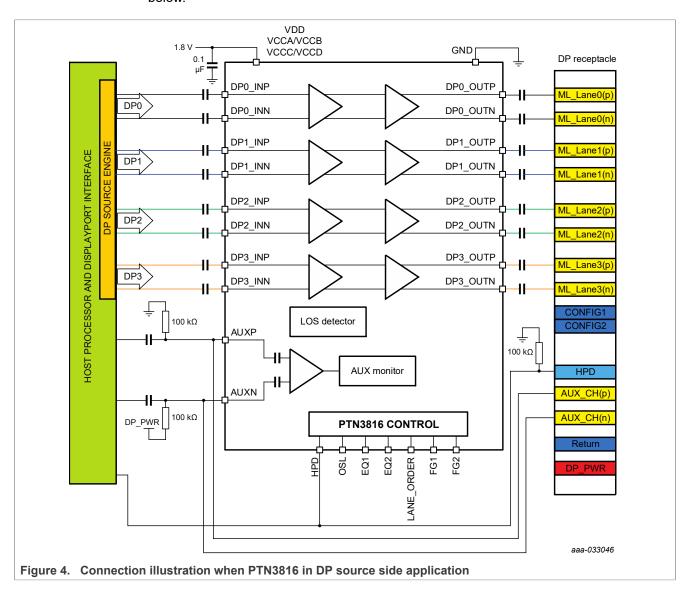

## 7.6 Application scenarios

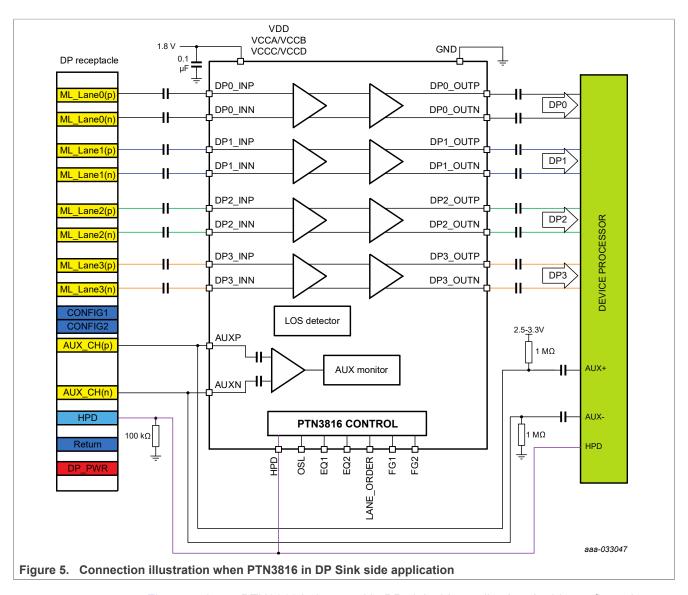

PTN3816 can be used in different system applications – source side DP redriver, sink side DP redriver or as a DP redriver in a dongle/dock as shown in <u>Figure 4</u> and <u>Figure 5</u> below.

<u>Figure 4</u> shows PTN3816 usage in DP source side application. In this configuration, upstream side of PTN3816 is connected to host processor and downstream side is connected to DP receptacle.

PTN3816 controls can be configured in the platform to suit the application needs.

## DisplayPort 20Gbps 4-lane linear redriver

<u>Figure 5</u> shows PTN3816 being used in DP sink side application. In this configuration, downstream side of PTN3816 is connected to device processor while the upstream side is connected to DP receptacle.

DisplayPort 20Gbps 4-lane linear redriver

# 8 Limiting values

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Table 10. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                           | Parameter                                               | Conditions                                                                                      | Min  | Тур  | Max  | Unit | Unique Identifier |

|----------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|-------------------|

| V <sub>DD</sub> <sup>[1]</sup>   | Supply voltage                                          | 1.8 V digital supply voltage                                                                    | -0.5 | -    | +2.2 | V    | LTC-VOL-PRIO1-001 |

| V <sub>CCXX</sub> <sup>[1]</sup> | Supply voltage for high-speed channels                  | VCCA, VCCB, VCCC,<br>VCCD                                                                       | -0.5 | -    | +2.2 | V    | LTC-VOL-PRIO1-002 |

| V <sub>I</sub> <sup>[1]</sup>    | Input voltage                                           | EQ1, EQ2, FG1, FG2,<br>OSL, HPD, LANE_<br>ORDER, AUXP/N pins                                    | -0.5 | -    | +3.6 | V    | LTC-VOL-PRIO1-005 |

|                                  |                                                         | High-speed pins                                                                                 | -0.5 | -    | +2.5 | V    | LTC-VOL-PRIO1-006 |

| T <sub>stg</sub>                 | Storage<br>temperature                                  |                                                                                                 | -65  | -    | 150  | °C   | LTC-TMP-PRIO1-007 |

| V <sub>esd</sub>                 | Electro Static<br>Discharge                             | HBM <sup>[2]</sup> for High-speed and AUX pins                                                  | 1500 | -    |      | V    | LTC-VOL-PRIO1-008 |

|                                  |                                                         | HBM for other control pins                                                                      | 1500 | -    |      | V    | LTC-VOL-PRIO1-009 |

|                                  |                                                         | CDM <sup>[3]</sup> for High-speed and AUX pins                                                  | 1000 | -    |      | V    | LTC-VOL-PRIO1-010 |

|                                  |                                                         | CDM for other control pins                                                                      | 1000 | -    |      | V    | LTC-VOL-PRIO1-011 |

| R <sub>th(j-a)</sub>             | Thermal resistance from junction to ambient environment | JEDEC still air test environment                                                                | -    | 40.6 | -    | °C/W | LTC-RES-PRIO2-012 |

| R <sub>th(j-c)</sub>             | Thermal resistance from junction to case                |                                                                                                 | -    | 16.8 | -    | °C/W | LTC-RES-PRIO2-013 |

| R <sub>th(j-b)</sub>             | Thermal resistance from junction to board               | FR4 PCB material<br>and with center<br>pad soldered with<br>recommended solder<br>pad structure | -    | 19.7 | -    | °C/W | LTC-RES-PRIO2-014 |

<sup>[1]</sup> All voltage values, except differential voltages, are with respect to network ground terminal.

PTN3816

<sup>[2]</sup> Human Body Model: ANSI/EOS/ESD-S5.1-1994, standard for ESD sensitivity testing, Human Body Model – Component level; Electrostatic Discharge Association, Rome, NY, USA.

<sup>[3]</sup> Charged Device Model: ANSI/EOS/ESD-S5.3-1-1999, standard for ESD sensitivity testing, Charged Device Model – Component level; Electrostatic Discharge Association, Rome, NY, USA

DisplayPort 20Gbps 4-lane linear redriver

# 9 Recommended operating conditions

Over operating free-air temperature range (unless otherwise noted). Typical values are specified for 1.8 V and 25 °C operating temperature.

Table 11. Operating conditions

| Symbol           | Parameter                            | Conditions                                                         | Min  | Тур | Max                  | Unit | Unique Identifier |

|------------------|--------------------------------------|--------------------------------------------------------------------|------|-----|----------------------|------|-------------------|

| $V_{DD}$         | Supply voltage for digital circuitry | VDD pin                                                            | 1.7  | 1.8 | 1.9                  | V    | ROC-VOL-PRIO1-001 |

| V <sub>CC</sub>  | Supply voltage for high-speed lanes  | VCCA, VCCB, VCCC and VCCD pins                                     | 1.7  | 1.8 | 1.9                  | V    | ROC-VOL-PRIO1-002 |

| V <sub>I</sub>   | Input voltage                        | EQ1, EQ2, OSL,<br>AUXP/N, LANE_<br>ORDER, HPD, FG1<br>and FG2 pins | -0.3 |     | 3.6                  | V    | ROC-VOL-PRIO1-003 |

|                  |                                      | High-speed Data pins                                               | -0.3 |     | V <sub>CC</sub> +0.3 | V    | ROC-VOL-PRIO1-005 |

| T <sub>amb</sub> | Ambient temperature                  | Operating in free air                                              | -20  | -   | 85                   | °C   | ROC-TMP-PRIO1-008 |

DisplayPort 20Gbps 4-lane linear redriver

## 10 Characteristics

## 10.1 Device characteristics

Table 12. Device characteristics

| Symbol                        | Parameter                                                                                                        | Conditions                                                                                                                                                                                         | Min | Тур | Max | Unit | Unique Identifier |

|-------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|-------------------|

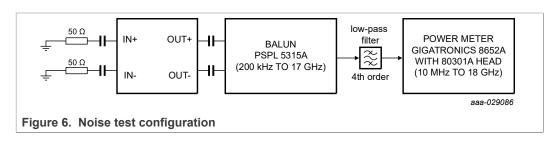

| V <sub>GND_VCC</sub><br>noise | Noise voltage from DUT<br>(50 Hz to 1 MHz)<br>GND noise/bounce with<br>V <sub>CC</sub> as the reference<br>point | DUT only and No<br>bypass cap during<br>testing<br>Test recommendations:<br>Battery powered DUT                                                                                                    |     | 18  |     | mVpp | DEV-VOL-PRIO2-001 |

|                               | Noise voltage<br>(1 MHz to 10 MHz)                                                                               | with V <sub>CCx</sub> pin as the reference power plan and measure the GND                                                                                                                          |     | 18  |     | mVpp | DEV-VOL-PRIO2-002 |

|                               | Noise voltage<br>(10 MHz to 5 GHz)                                                                               | pin ground bounce;<br>measured by power rail<br>probe                                                                                                                                              |     |     | 10  | mVpp | DEV-VOL-PRIO1-003 |

| CMRR                          | Common Mode<br>Rejection Ratio<br>Δ(Vcm,rx)/Δ(Vout_diff)                                                         | 10 MHz to 1 GHz                                                                                                                                                                                    |     | 30  |     | dB   | DEV-DB-PRIO2-004  |

| PSRR                          | Power Supply Rejection Ratio<br>Δ(VCC)/Δ(Vout_diff)                                                              | 10 MHz to 200 MHz                                                                                                                                                                                  |     | 41  |     | dB   | DEV-DB-PRIO2-005  |

| t <sub>Startup</sub>          | Start-up time                                                                                                    | Between supply voltage<br>exceeding 1.4 V and<br>sampling of EQ1/EQ2/<br>OSL/FG1/FG2 pin                                                                                                           |     |     | 3   | ms   | DEV-TIM-PRIO1-006 |

| t <sub>rcfg</sub>             | Reconfiguration time                                                                                             | Any channel configuration pin change (from one setting to another setting) to specified operating characteristics. Device is supplied with valid supply voltage. This includes control pin changes | -   | -   | 50  | μs   | DEV-TIM-PRIO1-009 |

| t <sub>hold-port</sub>        | Hold time for data on<br>the control pins after<br>VDD ramps up                                                  | hold time for determining channel control changes                                                                                                                                                  | 2.5 | 3   |     | ms   | DEV-TIM-PRIO1-015 |

| t <sub>HPD(EN-</sub><br>DIS)  | Disable time to turn<br>off high speed data<br>channels when HPD<br>goes LOW                                     | Applicable when HPD is getting deasserted (HIGH to LOW transition).                                                                                                                                | 95  | 100 | 105 | ms   | DEV-TIM-PRIO1-066 |

| t <sub>HPD(DIS</sub> -<br>EN) | Enable time to turn on<br>the high speed data<br>channels when HPD<br>goes HIGH                                  | Applicable when HPD is getting asserted (LOW to HIGH transition).                                                                                                                                  | 8   | 10  | 25  | μs   | DEV-TIM-PRIO1-067 |

| t <sub>PD</sub>               | Differential Propagation<br>Delay                                                                                | Differential propagation<br>delay between 50 %<br>level at input and output<br>of High-speed pins                                                                                                  |     | 70  | 90  | ps   | DEV-TIM-PRIO1-011 |

PTN3816

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

## DisplayPort 20Gbps 4-lane linear redriver

Table 12. Device characteristics...continued

| Symbol                 | Parameter                                                                                                                               | Conditions                                                                      | Min  | Тур  | Max  | Unit              | Unique Identifier |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|------|------|-------------------|-------------------|

| Gp                     | Peaking gain                                                                                                                            | 10 GHz                                                                          |      | 20   |      | dB                | DEV-DB-PRIO2-016  |

|                        | (compensation at 10 GHz, 5 GHz and                                                                                                      | 5 GHz                                                                           |      | 12.1 |      | dB                | DEV-DB-PRIO1-017  |

|                        | 4.05 GHz, relative<br>to gain at 100 MHz;<br>sinusoidal input of<br>100 mVppd);<br>EQ2 = No connect,<br>EQ1 = No connect,<br>FGx = HIGH | 4.05 GHz                                                                        |      | 10.2 |      | dB                | DEV-DB-PRIO1-018  |

| Gp,var                 | Peaking gain variation over Gp at 10 GHz                                                                                                |                                                                                 | -2.3 |      | +2.3 | dB                | DEV-DB-PRIO2-019  |

| OSL <sub>100M</sub>    | -1 dB compression                                                                                                                       | OSL = No connect                                                                |      | 650  |      | mVppd             | DEV-VOL-PRIO2-024 |

|                        | point of output swing at 100 MHz                                                                                                        | OSL = LOW                                                                       |      | 800  |      | mVppd             | DEV-VOL-PRIO2-025 |

|                        | 100 111112                                                                                                                              | OSL = HIGH                                                                      |      | 950  |      | mVppd             | DEV-VOL-PRIO2-026 |

| OSL <sub>4G</sub>      | -1 dB compression                                                                                                                       | OSL = No connect                                                                |      | 650  |      | mVppd             | DEV-VOL-PRIO2-070 |

|                        | point of output swing at 4.05 GHz                                                                                                       | OSL = LOW                                                                       |      | 800  |      | mVppd             | DEV-VOL-PRIO2-071 |

|                        | 1.00 01.12                                                                                                                              | OSL = HIGH                                                                      |      | 950  |      | mVppd             | DEV-VOL-PRIO2-072 |

| OSL <sub>10G</sub>     | -1 dB compression                                                                                                                       | OSL = No connect                                                                |      | 650  |      | mVppd             | DEV-VOL-PRIO2-032 |

|                        | point of output swing at 10 GHz                                                                                                         | OSL = LOW                                                                       |      | 800  |      | mVppd             | DEV-VOL-PRIO2-033 |

|                        |                                                                                                                                         | OSL = HIGH                                                                      |      | 950  |      | mVppd             | DEV-VOL-PRIO2-034 |

| V <sub>noise_in</sub>  | Input referred noise                                                                                                                    | 100 MHz to 15 GHz;<br>Peaking gain of 10.2 dB<br>at 10 GHz and OSL<br>950 mVppd |      | 0.8  |      | mV <sub>rms</sub> | DEV-VOL-PRIO2-035 |

|                        |                                                                                                                                         | 100 MHz to 15 GHz;<br>Peaking gain of 17.3 dB<br>at 10 GHz and OSL<br>950 mVppd |      | 1    |      | mV <sub>rms</sub> | DEV-VOL-PRIO2-036 |

| V <sub>noise_out</sub> | Output referred noise                                                                                                                   | 100 MHz to 15 GHz;<br>Peaking gain of 10.2 dB<br>at 10 GHz and OSL<br>950 mVppd |      | 2.0  |      | mV <sub>rms</sub> | DEV-VOL-PRIO2-037 |

|                        |                                                                                                                                         | 100 MHz to 15 GHz;<br>Peaking gain of 17.3 dB<br>at 10 GHz and OSL<br>950 mVppd |      | 2.0  |      | mV <sub>rms</sub> | DEV-VOL-PRIO2-038 |

| $V_{LOS}$              | Loss of Signal detector threshold level                                                                                                 | Applicable to high speed lanes                                                  |      | 45   |      | mVppd             | DEV-VOL-PRIO2-042 |

| I <sub>DD</sub>        | Supply current All 4 DP lanes are active                                                                                                | -1 dB compression point at 950 mVppd                                            |      | 250  | 270  | mA                | DEV-CUR-PRIO1-044 |

|                        |                                                                                                                                         | -1 dB compression point at 800 mVppd                                            |      | 225  | 260  | mA                | DEV-CUR-PRIO1-045 |

|                        |                                                                                                                                         | -1 dB compression point at 650 mVppd                                            |      | 200  | 240  | mA                | DEV-CUR-PRIO1-046 |

## DisplayPort 20Gbps 4-lane linear redriver

Table 12. Device characteristics...continued

| Symbol             | Parameter                                                                               | Conditions                           | Min | Тур | Max | Unit              | Unique Identifier |

|--------------------|-----------------------------------------------------------------------------------------|--------------------------------------|-----|-----|-----|-------------------|-------------------|

|                    | Supply current 2 DP lanes are active                                                    | -1 dB compression point at 950 mVppd |     | 125 | 140 | mA                | DEV-CUR-PRIO1-048 |

|                    |                                                                                         | -1 dB compression point at 800 mVppd |     | 110 | 130 | mA                | DEV-CUR-PRIO1-049 |

|                    |                                                                                         | -1 dB compression point at 650 mVppd |     | 115 | 120 | mA                | DEV-CUR-PRIO1-050 |

|                    | Supply current 1 DP lane is active                                                      | -1 dB compression point at 950 mVppd |     | 62  | 75  | mA                | DEV-CUR-PRIO1-052 |

|                    |                                                                                         | -1 dB compression point at 800 mVppd |     | 57  | 70  | mA                | DEV-CUR-PRIO1-053 |

|                    |                                                                                         | -1 dB compression point at 650 mVppd |     | 52  | 65  | mA                | DEV-CUR-PRIO1-054 |

|                    | Supply current                                                                          | Power saving mode (DP D3 mode)       |     | 3.2 |     | mA                | DEV-CUR-PRIO2-059 |

|                    | Deep Power-saving state (HPD = LOW)                                                     |                                      | 10  |     | μΑ  | DEV-CUR-PRIO2-060 |                   |

| Xtak <sub>oo</sub> | Far end crosstalk<br>between two output<br>drivers (between any<br>two DP lane outputs) | Applies at 10 GHz                    |     | -34 |     | dB                | DEV-DB-PRIO2-065  |

## Note: For DisplayPort interface, One lane means one differential pair/channel

DisplayPort 20Gbps 4-lane linear redriver

# 10.2 Input AC/DC characteristics

Table 13. Input AC/DC characteristics

| Symbol                                           | Parameter                                                                     | Conditions                                                                                     | Min  | Тур | Max  | Unit  | Unique Identifier |

|--------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|-----|------|-------|-------------------|

| C <sub>ac_coupling</sub>                         | AC coupling capacitance                                                       | Applicable for high speed input pins                                                           | 75   |     | 265  | nF    | INC-CAP-PRIO1-001 |

| T <sub>Discharge</sub>                           | Discharge time                                                                |                                                                                                |      |     | 250  | ms    | INC-TIM-PRIO1-003 |

| R <sub>in-DC</sub>                               | Input DC common mode impedance                                                |                                                                                                | 21   |     | 34   | Ω     | INC-RES-PRIO1-004 |

| V <sub>RX-CM-AC-</sub> RX AC common mode voltage |                                                                               | A single tone injection at 120 MHz is a stress test                                            |      |     | 300  | mVpp  | INC-VOL-PRIO1-005 |

|                                                  | tolerance A single at 400 M stress te                                         |                                                                                                |      |     | 100  | mVpp  | INC-VOL-PRIO1-006 |

| R <sub>IN-DIFF-DC</sub>                          | DC Differential<br>Impedance                                                  |                                                                                                | 90   |     | 131  | Ω     | INC-RES-PRIO1-007 |

| V <sub>IP-DC-CM</sub>                            | DC biasing/common mode voltage                                                | Biasing on high speed input pins                                                               |      | 1.8 |      | V     | INC-VOL-PRIO2-008 |

| V <sub>RX-DIFF-PP</sub>                          | DisplayPort Input<br>voltage (peak to<br>peak differential<br>signal)         | At high speed input pins                                                                       | 45   |     | 1400 | mVppd | INC-VOL-PRIO1-013 |

| V <sub>voltage</sub> _<br>jump                   | Maximum voltage jump on input pin side measured before AC coupling capacitors | Applicable during power-on/power-off, transition from low power to active state and vice versa | -0.3 | -   | 1    | V     | INC-VOL-PRIO1-009 |

| RL <sub>DD11, IN</sub>                           | Input differential mode Return Loss                                           | 100 MHz to 10.3 GHz                                                                            |      | 15  |      | dB    | INC-DB-PRIO2-014  |

| RL <sub>CC11, IN</sub>                           | Input common mode Return Loss                                                 | 100 MHz to 10.3 GHz                                                                            |      | 12  |      | dB    | INC-DB-PRIO2-015  |

DisplayPort 20Gbps 4-lane linear redriver

# 10.3 Output AC/DC characteristics

Table 14. Output AC/DC characteristics

| Symbol                              | Parameter                                                                     | Conditions                                                                                     | Min  | Тур | Max | Unit  | Unique Identifier |

|-------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|-----|-----|-------|-------------------|

| C <sub>ac_coupling</sub>            | AC coupling capacitance                                                       | Applicable on high speed output                                                                | 75   |     | 265 | nF    | OUC-CAP-PRIO1-013 |

| R <sub>OP-DC</sub>                  | Output DC common mode Impedance                                               |                                                                                                | 21   |     | 34  | Ω     | OUC-RES-PRIO1-001 |

| R <sub>OP-DIFF-DC</sub>             | Output Differential Impedance                                                 |                                                                                                | 89   |     | 131 | Ω     | OUC-RES-PRIO1-002 |

| V <sub>OP-DC-CM</sub>               | DC biasing/common mode voltage on                                             | -1 dB Compression point at 950 mVppd                                                           |      | 1.2 |     | V     | OUC-VOL-PRIO2-003 |

|                                     | high speed pins                                                               | -1 dB Compression point at 800 mVppd                                                           |      | 1.3 |     | V     | OUC-VOL-PRIO2-004 |

|                                     |                                                                               | -1 dB Compression point at 650 mVppd                                                           |      | 1.4 |     | V     | OUC-VOL-PRIO2-005 |

| V <sub>TX-CM-AC-</sub><br>PP_ACTIVE | Output AC Common mode output voltage in active state                          | •                                                                                              |      |     | 20  | mVpp  | OUC-VOL-PRIO1-007 |

| V <sub>TX-IDLE-</sub><br>DIFF-AC-pp | Output AC<br>differential output<br>voltage                                   | When link is in electrical idle                                                                |      |     | 10  | mVppd | OUC-VOL-PRIO1-008 |

| V <sub>voltage</sub> _<br>jump      | Maximum voltage jump on output pin side measured after AC coupling capacitors | Applicable during power-on/power-off, transition from low power to active state and vice versa | -0.3 | -   | 1   | V     | OUC-VOL-PRIO1-009 |

| RL <sub>DD11, OP</sub>              | Output differential mode Return Loss                                          | 100 MHz to 10.3 GHz                                                                            |      | 18  |     | dB    | OUC-DB-PRIO2-011  |

| RL <sub>CC11, OP</sub>              | Output common mode Return Loss                                                | 100 MHz to 10.3 GHz                                                                            |      | 12  |     | dB    | OUC-DB-PRIO2-012  |

DisplayPort 20Gbps 4-lane linear redriver

## 10.4 AUX monitor characteristics

Table 15. AUX monitor characteristics

| Symbol                          | Parameter                                                  | Conditions                                          | Min  | Тур | Max  | Unit | Unique Identifier |

|---------------------------------|------------------------------------------------------------|-----------------------------------------------------|------|-----|------|------|-------------------|

| V <sub>I</sub>                  | Bias Voltage at the pin                                    | AUXP/AUXN pins                                      | 0    |     | 3.6  | V    | AUX-VOL-PRIO1-001 |

| r <sub>AUX</sub>                | AUX bit rate                                               |                                                     |      | 1   |      | Mbps | AUX-FRQ-PRIO2-002 |

| V <sub>AUX-AC-</sub><br>DIFF-pp | AUX AC<br>differential<br>peak-to-peak                     | AUXP/AUXN pins                                      | 0.27 |     | 1.38 | Vppd | AUX-VOL-PRIO1-003 |

| I <sub>IL</sub>                 | Leakage<br>current at the<br>pin                           | Pin voltage 3.6 V                                   |      |     | 19   | μΑ   | AUX-CUR-PRIO1-004 |

| I <sub>bck</sub>                | Back current<br>sunk from pin<br>to powered<br>down supply | V <sub>DD</sub> = 0 V, Pin voltage<br>= 3.6 V       |      |     | 27   | μА   | AUX-CUR-PRIO1-005 |

| Z <sub>in</sub>                 | AUX monitor<br>differential<br>input<br>impedance          | Over frequency range<br>of interest DC to<br>50 MHz |      | 1   |      | ΜΩ   | AUX-RES-PRIO2-006 |

| C <sub>Aux</sub>                | AUX AC coupling capacitance                                |                                                     | 75   |     | 200  | nF   | AUX-CAP-PRIO1-007 |

All S-parameter measurements are with respect to 100  $\Omega$  differential impedance reference and 50  $\Omega$  single-ended impedance reference.

DisplayPort 20Gbps 4-lane linear redriver

# 10.5 Input characteristics of binary configuration pin – HPD, LANE\_ORDER

Table 16. Binary control input characteristics

| Symbol                | Parameter                                                  | Conditions                          | Min                 | Тур | Max                  | Unit | Unique Identifier |

|-----------------------|------------------------------------------------------------|-------------------------------------|---------------------|-----|----------------------|------|-------------------|

| V <sub>IH</sub>       | High level voltage                                         | LANE_ORDER pin                      | 0.7*V <sub>DD</sub> | -   | V <sub>DD</sub> +0.3 | V    | BIN-VOL-PRIO1-001 |

| V <sub>IL</sub>       | Low level voltage                                          | LANE_ORDER pin                      | -                   | -   | 0.25*V <sub>DD</sub> | V    | BIN-VOL-PRIO1-002 |

| V <sub>Lo to Hi</sub> | HPD plug<br>detection<br>threshold                         | HPD pin                             | 2                   | -   | 3.6                  | V    | BIN-VOL-PRIO1-007 |

| V <sub>Hi to Lo</sub> | HPD unplug detection threshold                             | HPD pin                             | -                   | -   | 0.8                  | V    | BIN-VOL-PRIO1-008 |

| I <sub>IL</sub>       | Leakage<br>current at the                                  | VDD = 1.8 V, Pin<br>voltage = 3.6 V |                     |     | 14                   | μΑ   | BIN-CUR-PRIO1-003 |

|                       | pin                                                        | VDD = 1.8 V, Pin<br>voltage = 1.8 V |                     |     | 1.5                  | μΑ   | BIN-CUR-PRIO1-004 |

| I <sub>bck</sub>      | Back current<br>sunk from pin<br>to powered<br>down supply | VDD = 0, Pin voltage = 3.6 V        |                     |     | 24                   | μΑ   | BIN-CUR-PRIO1-005 |

| C <sub>pin</sub>      | Maximum<br>allowed<br>capacitance at<br>the pin            |                                     |                     |     | 10                   | pF   | BIN-CAP-PRIO1-006 |

DisplayPort 20Gbps 4-lane linear redriver

# 10.6 Input characteristics of ternary configuration pins - EQ1, EQ2, OSL, FG1 and FG2

Table 17. Ternary control input characteristics (external system voltage  $V_{SYS}$ = 1.7 V to 3.6 V)

| Symbol           | Parameter                                                  | Conditions                                                                | Min                  | Тур | Max                  | Unit | Unique Identifier |

|------------------|------------------------------------------------------------|---------------------------------------------------------------------------|----------------------|-----|----------------------|------|-------------------|

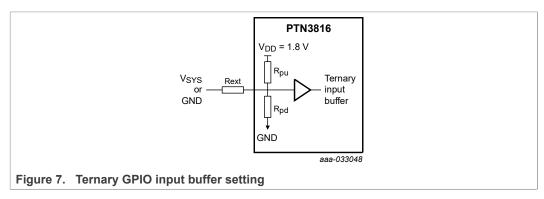

| V <sub>IH</sub>  | High level voltage                                         | External pull-up 1 k $\Omega$ resistor to $V_{SYS}$                       | 0.8*V <sub>DD</sub>  |     | V <sub>SYS</sub>     | V    | TER-VOL-PRIO1-001 |

| V <sub>IM</sub>  | Unconnected or open condition                              |                                                                           | 0.35*V <sub>DD</sub> |     | 0.45*V <sub>DD</sub> | V    | TER-VOL-PRIO1-002 |

| V <sub>IL</sub>  | Low level voltage                                          | External pull-down 1 kΩ resistor to GND                                   |                      |     | 0.15*V <sub>DD</sub> | V    | TER-VOL-PRIO1-003 |

| I <sub>IL</sub>  | Leakage<br>current when<br>pin is not<br>active            | VDD = 1.8 V, Pull-up resistor connected to V <sub>SYS</sub> = 3.6 V       |                      |     | 15                   | μΑ   | TER-CUR-PRIO1-004 |

|                  |                                                            | VDD = 1.8 V, Pull-up<br>resistor connected to<br>V <sub>SYS</sub> = 1.8 V |                      |     | 1                    | μА   | TER-CUR-PRIO1-005 |

|                  | Leakage<br>current when<br>pin is active                   | VDD = 1.8 V, Pull-up resistor connected to V <sub>SYS</sub> = 3.6 V       |                      |     | 80                   | μА   | TER-CUR-PRIO1-006 |

|                  |                                                            | VDD = 1.8 V, Pull-up resistor connected to V <sub>SYS</sub> = 1.8 V       | -25                  |     | 35                   | μА   | TER-CUR-PRIO1-007 |

| I <sub>bck</sub> | Back current<br>sunk from pin<br>to powered<br>down supply | VDD = 0, Pin voltage = 3.6 V                                              |                      |     | 20                   | μΑ   | TER-CUR-PRIO1-008 |

| R <sub>pu</sub>  | Internal pull-<br>up resistance                            |                                                                           |                      | 120 |                      | kΩ   | TER-RES-PRIO2-009 |

| R <sub>pd</sub>  | Internal<br>pull-down<br>resistance                        |                                                                           |                      | 80  |                      | kΩ   | TER-RES-PRIO2-010 |

| C <sub>pin</sub> | Maximum<br>allowed<br>capacitance at<br>the pin            |                                                                           |                      |     | 10                   | pF   | TER-CAP-PRIO1-011 |

PTN3816

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

## DisplayPort 20Gbps 4-lane linear redriver

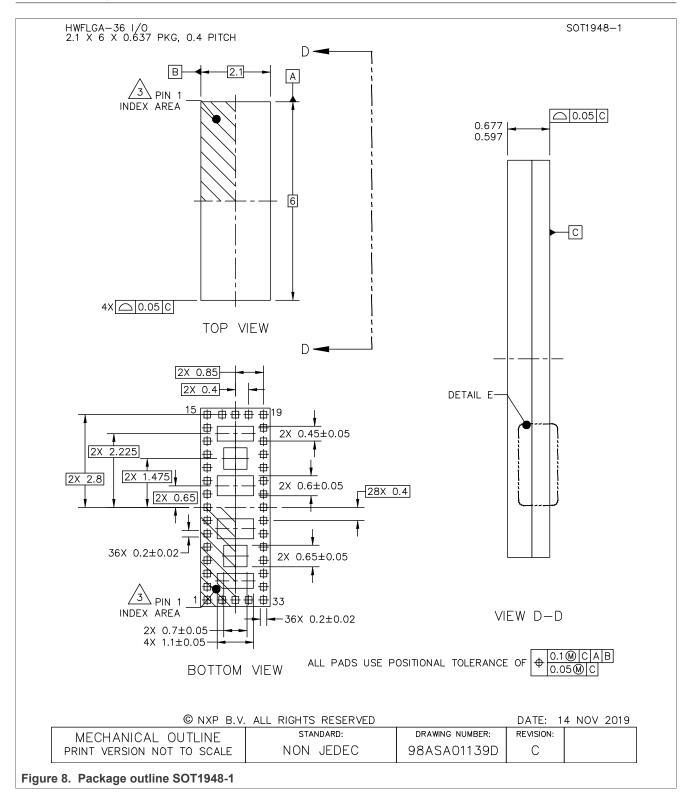

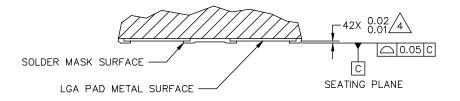

# 11 Package outline

## DisplayPort 20Gbps 4-lane linear redriver

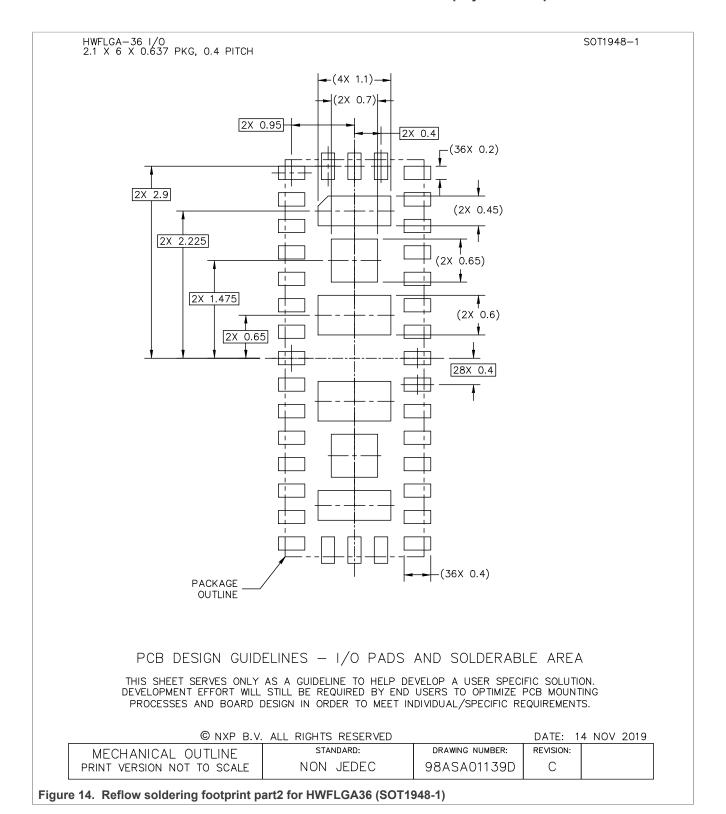

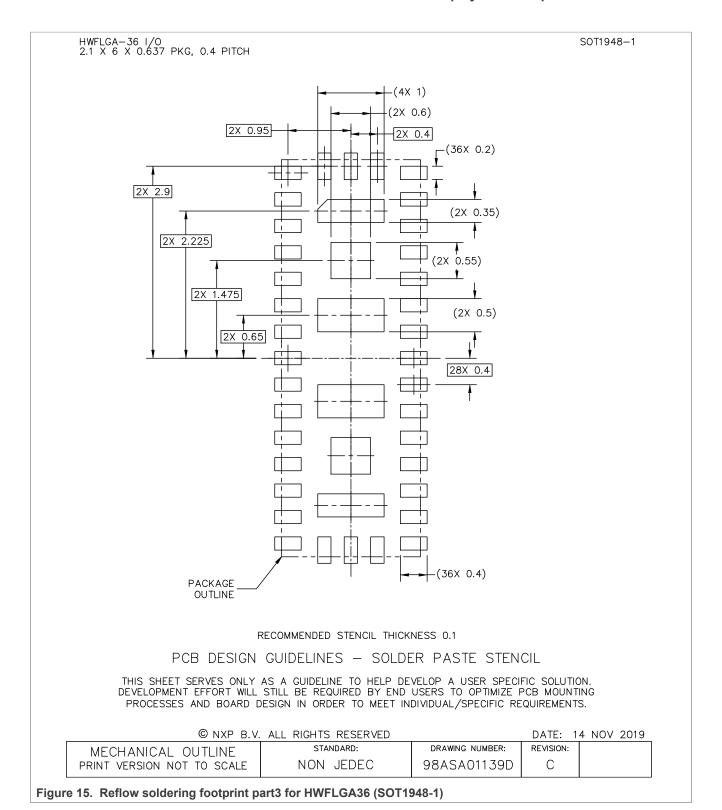

HWFLGA-36 I/O 2.1 X 6 X 0.637 PKG, 0.4 PITCH SOT1948-1

DETAIL E

© NXP B.V. ALL RIGHTS RESERVED

DATE: 14 NOV 2019

| MECHANICAL OUTLINE         | STANDARD: | DRAWING NUMBER: | REVISION: |  |

|----------------------------|-----------|-----------------|-----------|--|

| PRINT VERSION NOT TO SCALE | NON JEDEC | 98ASA01139D     | С         |  |

Figure 9. Package outline HWFLGA36 (SOT1948-1)

## DisplayPort 20Gbps 4-lane linear redriver

HWFLGA-36 I/O 2.1 X 6 X 0.637 PKG, 0.4 PITCH

SOT1948-1

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

3. PIN 1 CONFIGURATION MAY VARY.

4. DIMENSION APPLIES TO ALL LEADS.

© NXP B.V. ALL RIGHTS RESERVED

DATE: 14 NOV 2019

| MECHANICAL OUTLINE         | STANDARD: | DRAWING NUMBER: | REVISION: |  |

|----------------------------|-----------|-----------------|-----------|--|

| PRINT VERSION NOT TO SCALE | NON JEDEC | 98ASA01139D     | С         |  |

Figure 10. Package outline note HWFLGA36 (SOT1948-1)

DisplayPort 20Gbps 4-lane linear redriver

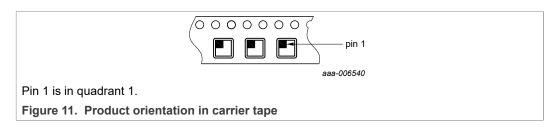

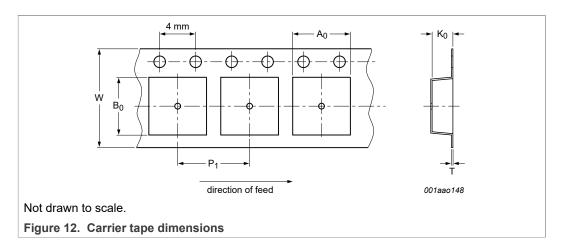

# 12 Packing information

# 12.1 SOT1948-1; HWFLGA36; reel dry pack, SMD, 13" Q1 standard product orientation ordering code (12NC) ending 019

### 12.1.1 Dimensions and quantities

Table 18. Dimensions and quantities

| Reel dimensions<br>d × w (mm) <sup>[1]</sup> | SPQ/PQ (pcs) <sup>[2]</sup> | Reels<br>per box |

|----------------------------------------------|-----------------------------|------------------|

| 330 × 12                                     | 7000                        | 1                |

<sup>[1]</sup> d = reel diameter; w = tape width.

### 12.1.2 Product orientation

### 12.1.3 Carrier tape dimensions

Table 19. Carrier tape dimensions

In accordance with IEC 60286-3/EIA-481.

| A <sub>0</sub> (mm) | B <sub>0</sub> (mm) | K <sub>0</sub> (mm) | T (mm)      | P <sub>1</sub> (mm) | W (mm)       |

|---------------------|---------------------|---------------------|-------------|---------------------|--------------|

| 2.30 ± 0.05         | 6.30 ± 0.05         | 0.85 +.1/05         | 0.30 ± 0.05 | 8 ± 0.1             | 12 +0.3/-0.1 |

PTN3816

<sup>[2]</sup> Packing quantity dependent on specific product type. View ordering and availability details at NXP order portal, or contact your local NXP representative.

## DisplayPort 20Gbps 4-lane linear redriver

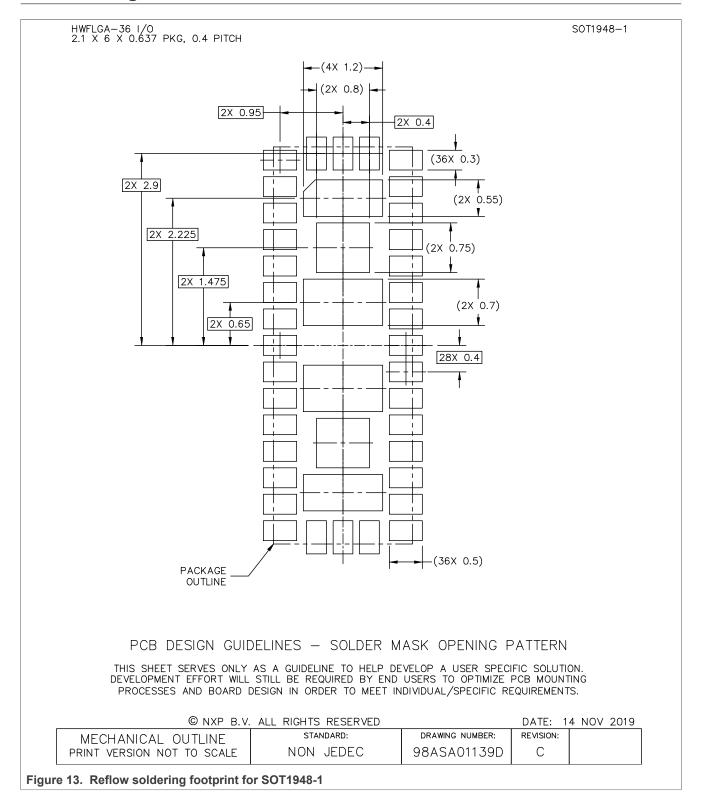

# 13 Soldering

## DisplayPort 20Gbps 4-lane linear redriver

PTN3816

### DisplayPort 20Gbps 4-lane linear redriver

PTN3816

DisplayPort 20Gbps 4-lane linear redriver

## 14 Abbreviations

### Table 20. Abbreviations

| Acronym | Description                                       |

|---------|---------------------------------------------------|

| AUX     | Auxiliary channel of DisplayPort standard         |

| CDM     | Charged Device Model                              |

| DFP     | Downstream Facing Port                            |

| DP      | DisplayPort                                       |

| Gbps    | Giga bits per second                              |

| НВМ     | Human Body Model                                  |

| HPD     | Hot Plug Detect signaling of DisplayPort standard |

| NC      | No Connect                                        |

| os      | Output Swing                                      |

| OSL     | Output Swing Linearity level                      |

| Rx      | Receiver                                          |

| SI      | Signal Integrity                                  |

| TX      | Transmitter                                       |

| UFP     | Upstream Facing Port                              |

# 15 Revision history

## Table 21. Revision history

| Document ID  | Release date | Data sheet status  | Change notice | Supersedes |

|--------------|--------------|--------------------|---------------|------------|

| PTN3816 v1.0 | 20210607     | Product data sheet | -             | -          |

### DisplayPort 20Gbps 4-lane linear redriver

# 16 Legal information

### 16.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

### 16.2 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

### 16.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

$\ensuremath{\mathbf{Applications}}$  — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

PTN3816

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved

### DisplayPort 20Gbps 4-lane linear redriver

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications. In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

#### 16.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

## DisplayPort 20Gbps 4-lane linear redriver

## **Tables**

| Tab. 1.  | Ordering information2                      | Tab. 13. | Input AC/DC characteristics              | 17 |

|----------|--------------------------------------------|----------|------------------------------------------|----|

| Tab. 2.  | Ordering options2                          | Tab. 14. | Output AC/DC characteristics             | 18 |

| Tab. 3.  | Pin description4                           | Tab. 15. | AUX monitor characteristics              | 19 |

| Tab. 4.  | EQ[2:1] configuration: Flat gain 0.7 dB 7  | Tab. 16. | Binary control input characteristics     | 20 |

| Tab. 5.  | EQ[2:1] configuration: Flat gain -0.7 dB7  | Tab. 17. | Ternary control input characteristics    |    |

| Tab. 6.  | OSL configuration 8                        |          | (external system voltage VSYS = 1.7 V to |    |

| Tab. 7.  | Lane ordering configuration 8              |          | 3.6 V)                                   | 21 |

| Tab. 8.  | HPD configuration8                         | Tab. 18. | Dimensions and quantities                |    |

| Tab. 9.  | Flat gain configuration8                   | Tab. 19. | Carrier tape dimensions                  | 25 |

| Tab. 10. | Limiting values12                          | Tab. 20. | Abbreviations                            | 29 |

| Tab. 11. | Operating conditions13                     | Tab. 21. | Revision history                         | 29 |

| Tab. 12. | Device characteristics                     |          |                                          |    |