# **UM11816**

## RD33774ADSTEVB user manual

Rev. 1 — 16 June 2023

**User manual**

#### **Document information**

| Information | Content                                                                   |

|-------------|---------------------------------------------------------------------------|

| Keywords    | Battery-cell controller, battery emulator, battery management systems     |

| Abstract    | This user manual describes how to use the RD33774ADSTEVB evaluation board |

#### RD33774ADSTEVB user manual

#### **Revision history**

| Rev | Date     | Description     |

|-----|----------|-----------------|

| v.1 | 20230616 | Initial version |

#### **RD33774ADSTEVB user manual**

#### **IMPORTANT NOTICE**

#### For engineering development or evaluation purposes only

NXP provides the product under the following conditions:

This evaluation kit is for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY. It is provided as a sample IC pre-soldered to a printed-circuit board to make it easier to access inputs, outputs and supply terminals. This evaluation board may be used with any development system or other source of I/O signals by connecting it to the host MCU computer board via off-the-shelf cables. This evaluation board is not a Reference Design and is not intended to represent a final design recommendation for any particular application. Final device in an application heavily depends on proper printed-circuit board layout and heat sinking design as well as attention to supply filtering, transient suppression, and I/O signal quality.

The product provided may not be complete in terms of required design, marketing, and or manufacturing related protective considerations, including product safety measures typically found in the end device incorporating the product. Due to the open construction of the product, it is the responsibility of the user to take all appropriate precautions for electric discharge. In order to minimize risks associated with the customers' applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. For any safety concerns, contact NXP sales and technical support services.

**RD33774ADSTEVB** user manual

### 1 Introduction

This user manual describes the RD33774ADSTEVB. The RD33774ADSTEVB features one MC33774A battery-cell controller integrated circuit (IC).

The NXP analog product development board provides a platform for evaluating NXP products.

These development boards support a range of analog, mixed-signal, and power solutions. These boards incorporate monolithic ICs and system-in-package devices that use high-volume technology. NXP products offer long battery life, a small form factor, reduced component counts, lower cost, and improved performance in powering state-of-the-art systems.

**RD33774ADSTEVB** user manual

## 2 Finding kit resources and information on the NXP web site

NXP Semiconductors provides online resources for this evaluation board and its supported device(s) on <a href="http://www.nxp.com">http://www.nxp.com</a>. The information page for the RD33774ADSTEVB evaluation board is at <a href="http://www.nxp.com/RD33774ADSTEVB">http://www.nxp.com/RD33774ADSTEVB</a>. The information page provides overview information, documentation, software and tools, parametrics, ordering information and a Getting Started tab. The Getting Started tab provides quick-reference information applicable to using the RD33774ADSTEVB evaluation board, including the downloadable assets referenced in this document.

**RD33774ADSTEVB** user manual

## 3 Getting ready

#### 3.1 Kit contents

- · Assembled and tested evaluation board/module in anti-static bag

- One 32-pin battery cell cable

- One two-pin TPL cable

#### 3.2 Required equipment

To use this kit, the following equipment is required:

- A 4-cell to 18-cell battery pack or a battery pack emulator, such as BATT-18CEMULATOR

- FRDMDUALK3664EVB (EVB for MC33664A) in combination with the S32K3X4EVB-T172 (S32K3X4 EVB) to interface with a PC. For the evaluation setup, a graphical user interface, EvalGUI 7, is available in Secure Files on <a href="http://www.nxp.com">http://www.nxp.com</a>.

RD33774ADSTEVB user manual

## 4 Getting to know the hardware

#### 4.1 Kit overview

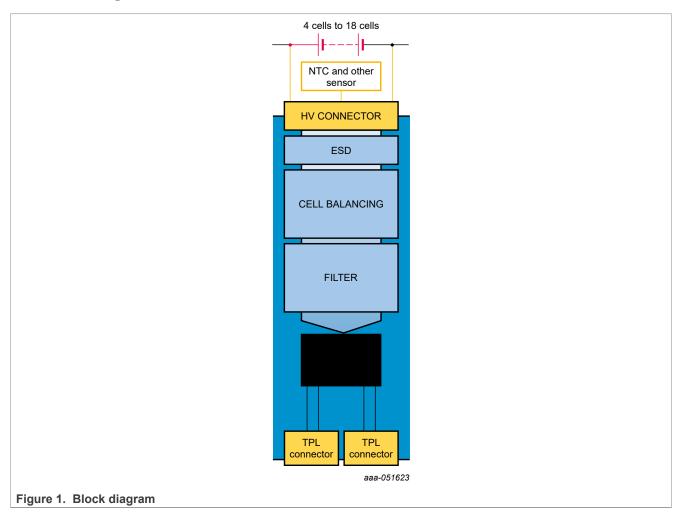

The RD33774ADSTEVB serves as a hardware evaluation tool in support of NXP's MC33774A device. The MC33774A is a battery-cell controller that monitors up to 18 lithium-ion battery cells. RD33774ADSTEVB is designed for use in automotive and industrial applications. The device performs analog-to-digital conversion on the differential cell voltages and currents. It is also capable of battery-charge coulomb counting and battery temperature measurements. The RD33774ADSTEVB can be used for rapid prototyping of MC33774A-based applications that involve voltage and temperature sensing.

The information is digitally transmitted to a microcontroller for processing. The evaluation board can be used with a physical layer transformer transceiver driver (MC33664) to convert MCU SPI data bits to pulse bit information for the MC33774A and vice versa.

#### 4.2 Board features

The main features of the RD33774ADSTEVB are:

- · Daisy-chain device connection

- · LED indicator for operation mode

- Cell-balancing resistors (22 Ω per individual cell)

- · Cell-sense input with RC filter

- GPIO: Digital I/O, wake-up inputs, convert trigger inputs, ratiometric analog inputs, analog inputs with absolute measurements

- EEPROM (connected to the IC with I<sup>2</sup>C interface) to store user-defined calibration parameters

RD33774ADSTEVB user manual

#### 4.3 Block diagram

#### 4.4 MC33774A features and benefits

The MC33774A is a battery-cell controller IC designed to monitor battery characteristics, such as voltage, current, and temperature. The MC33774A contains all of the circuit blocks necessary to perform battery-cell voltage measurement, cell temperature measurement, and integrated cell balancing. The MC33774A supports the following functions:

- AEC-Q100 grade 1 qualified: -40 °C to +125 °C ambient temperature range

- ISO 26262 ASIL D support for cell voltage and cell temperature measurements from the host microcontroller unit (MCU) to the cell

- · Cell-voltage measurement

- 4 cells to 18 cells per device

- Supports bus bars voltage measurement with +5/-3 V input voltage

- 16-bit resolution and ±1 mV typical measurement accuracy with ultra-low long-term drift

- 136 µs synchronicity of cell-voltage measurements

- Integrated configurable digital filter

- · External temperature and auxiliary voltage measurements

- One analog input for absolute measurement, 5 V input range

- Eight analog inputs configurable as absolute or ratiometric, 5 V input range

JM11816

All information provided in this document is subject to legal disclaimers.

© 2023 NXP B.V. All rights reserved

#### **RD33774ADSTEVB user manual**

- 16 bit resolution and ±5 mV typical measurement accuracy

- Integrated configurable digital filter

- · Internal measurement

- Two redundant internal temperature sensors

- Supply voltages

- External transistor current

- · Cell voltage balancing

- 18 internal balancing field effect transistors (FET), up to 150 mA average with 0.5 Ω R<sub>DSon</sub> per channel (typ.)

- Support for simultaneous passive balancing of all channels with automatic odd/even sequence

- Global balancing timeout timer

- Timer-controlled balancing with individual timers with 10 s resolution and up to 45 hours duration

- Voltage-controlled balancing with global and individual undervoltage thresholds

- Temperature-controlled balancing; if balancing resistors are in overtemperature, balancing is interrupted

- Configurable pulse width modulation (PWM) duty cycle balancing

- Automatic pausing of balancing during measurement with configurable filter settling time

- Configurable delay of the start of balancing after transition to sleep

- Automatic discharge of the battery pack (emergency discharge)

- Constant current cell balancing to compensate the balancing current variation because of cell voltage variation

- 1<sup>2</sup>C-bus master interface to control external devices, for example, EEPROMs and security ICs

- · Configurable alarm output

- Cyclic wake-up to monitor the pack and the balancing function during sleep.

- · Capability to wake up the host MCU via daisy chain in case of a fault event.

- · Host interface supporting SPI or isolated daisy chain communication (TPL3)

- 2 Mbit/s data rate for TPL interface

- 4 Mbit/s data rate for SPI interface

- TPL3 daisy chain communication supports

- Two wire daisy chain with capacitive or inductive isolation

- Protocol supporting up to six daisy chains and 62 nodes per chain

- · Unique device ID with dynamic adressing

- Operation modes

- Active mode (12 mA typ.)

- Sleep mode (60 µA typ.)

- Deep Sleep mode (15 µA typ.)

RD33774ADSTEVB user manual

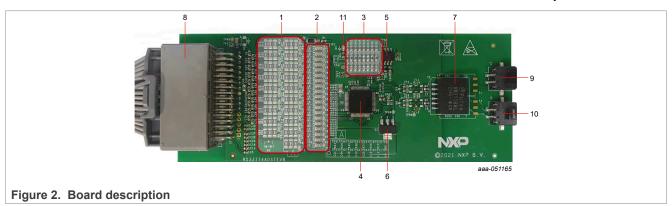

## 4.5 Board description

The RD33774ADSTEVB allows the user to exercise all the functions of the MC33774A battery controller cell.

Table 1. Board description

| Number | Name                                            | Description                                                                     |

|--------|-------------------------------------------------|---------------------------------------------------------------------------------|

| 1      | Cell balancing resistors                        | 3 x 33 ohms in parallel on each Cx pin: 200 mA of cell-balancing current @4.5 V |

| 2      | Cell terminal low-pass filters                  | LPF: 10 KΩ resistor/0.047 μF capacitor to GND                                   |

| 3      | GPIO low-pass filters                           | For NTC connections and temperature measurement                                 |

| 4      | MC33774A (U2)                                   | 18-cell battery-cell controller IC                                              |

| 5      | NV24C64DWVLT3G (U1)                             | High-speed 64 Kb I <sup>2</sup> C EEPROM                                        |

| 6      | NSS1C201MZ4T1G (Q1)                             | NPN supply bipolar transistor                                                   |

| 7      | HM2118NL or HM2168NL(T2) or capacitive coupling | Default BOM: High-voltage dual-channel transformer                              |

| 8      | JAE-MX34032NF2 (J1)                             | 32-pin connector for cell connections and NTC connections                       |

| 9      | MOLEX-43650-0213 (J2)                           | TPL connector to higher node                                                    |

| 10     | MOLEX-43650-0213 (J3)                           | TPL connector to lower node                                                     |

| 11     | LED                                             | VAUX status                                                                     |

**RD33774ADSTEVB** user manual

#### 4.5.1 Connectors

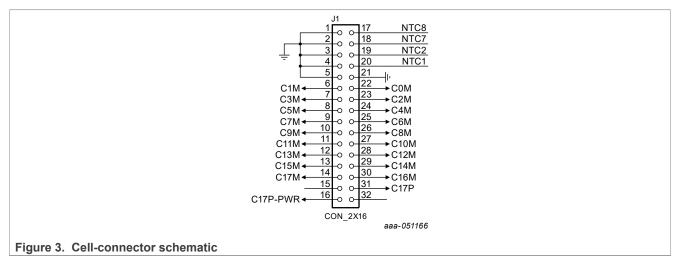

#### 4.5.1.1 Battery pack connector J1

The cells and NTCs connections are available on J1. See Figure 3

Cell0 is connected between C0M(cell0M) and C1M(cell0P); Cell1 is connected between C1M(cell1M) and C2M(cell1P), etc... Cell17 is connected between C17M (cell17M) and C17P (cell17P)

C17P-PWR and GND (pin21) are used to supply the RD33774ADSTEVB and are separated from C17P and C0M respectively to avoid any voltage drop because of the EVB current consumption.

Optional external 10 KΩ NTCs can be connected between each NTCx terminal and one GND terminal.

Board connector reference: MX34032NF2 (32 pins/right angle version) - Manufacturer : JAE

Corresponding mate connector reference: MX34032SF1

Crimp reference for the mate connector: M34S75C4F1 (applicable cable 0.22 mm<sup>2</sup> to 0.35 mm<sup>2</sup>)

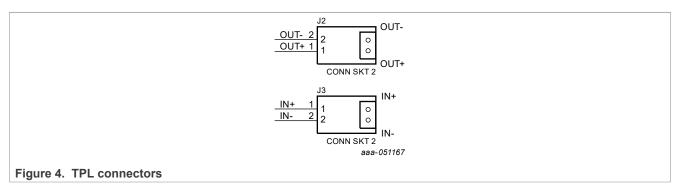

#### 4.5.1.2 TPL connectors

Isolated connections to upper and lower nodes can be done through J2 and J3, respectively. As the TPL communications are bidirectional, the connections can be reversed.

Board connector reference: Micro-fit 3.0 43650-0213 (two pins/right angle version) - Manufacturer: Molex

Corresponding mate connector reference: 0436450200 Crimp reference for the mate connector: 0436450201

UM11816

All information provided in this document is subject to legal disclaimers.

© 2023 NXP B.V. All rights reserved.

RD33774ADSTEVB user manual

Twisted cable: 64920108 - Manufacturer: Kromberg & Schubert

#### 4.5.1.2.1 TPL configuration

The RD33774ADSTEVB can be configured for capacitive TPL communications instead of the default BOM with inductive TPL communication (transformer). See <u>Table 2</u> for configuration instructions.

Table 2. Configuration

| Name                 | Value           | Inductive isolation | Capacitive isolation |

|----------------------|-----------------|---------------------|----------------------|

| T2                   | 1:1 transformer | Place               | Remove               |

| C21, C23, C28, C30   | 10 nF/10 ohms   | Remove              | Place                |

| R25, R28, R102, R103 | TBD             | Remove              | Place                |

RD33774ADSTEVB user manual

## 4.6 Test points

Test points are provided to access various signals on the board. Main test points are detailed in Table 3.

Table 3. Test points

| Label                           | Signal name | Description                 |

|---------------------------------|-------------|-----------------------------|

| TP1                             | C17P-VPWR   | Battery stack HV+           |

| TP2                             | VBAT        | MC33774A VBAT supply        |

| TP3 – TP6                       | RXTX        | MC33774A TPL lines          |

| TP51, 44, 38, 31, 23, 18, 10, 8 | NTCx        | NTC1 to 8                   |

| TP53, 45, 39, 32, 24, 19, 11, 7 | GPIO        | MC33774 GPIO0 to GPIO7 pins |

| TP61                            | ALARM_OUT   | MC33774 AINA_ALARM_OUT pin  |

| TP57                            | VDDA        | MC33774 VDDA pin            |

| TP58                            | VAUX        | MC33774 VAUX pin            |

| TP66                            | DRIVE_VDDC  | MC33774 DRIVE_VDDC pin      |

| TP67                            | IMON_VDDC   | MC33774 IMON_VDCC pin       |

| TP68                            | VDDC, VDDIO | MC33774 VDDC pin            |

| TP86, 87, 88, 89                | GND         | Battery stack HV-           |

**RD33774ADSTEVB** user manual

### 4.7 GPIO configurations

The MC33774A has nine GPIO pins (GPIO0 to GPIO7 and AINA) available for temperature measurements (excepted AINA), absolute analog measurements, and other functions.

The RD33774ADSTEVB makes available the GPIO measurements and functions as described in Table 4.

Table 4. GPIO connections

| Connection                         | Board label | Description - BCC connection                                                                                                              |

|------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| J1-20                              | NTC1        | GPIO0/AIN0 pin through low-pass filter for NTC acquisition - to be connected to an external 10 KΩ NTC (that is, NCP15 XV103J03RC)         |

| J1-19                              | NTC2        | GPIO1/AIN1 pin through low-pass filter for NTC acquisition - to be connected to an external 10 K $\Omega$ NTC (that is, NCP15 XV103J03RC) |

| J1-18                              | NTC7        | GPIO6/AIN6 pin through low-pass filter for NTC acquisition - to be connected to an external 10 KΩ NTC (that is, NCP15 XV103J03RC)         |

| J1-17                              | NTC8        | GPIO7/AIN7 pin through low-pass filter for NTC acquisition - to be connected to an external 10 KΩ NTC (that is, NCP15 XV103J03RC)         |

| Onboard NTC NCP15XV103J03RC - TP38 | NTC3        | GPIO2/AIN2 pin through low-pass filter for NTC acquisition                                                                                |

| Not connected - TP31               | NTC4        | GPIO3/AIN3 pin through low-pass filter for NTC acquisition                                                                                |

| Onboard I2Ceeprom - SCL            | GPIO4       | GPIO4 pin                                                                                                                                 |

| Onboard I2Ceeprom - SDA            | GPIO5       | GPIO5 pin                                                                                                                                 |

| Not connected - TP61               | AINA        | AINA pin                                                                                                                                  |

RD33774ADSTEVB user manual

## 5 Configuring the hardware

The RD33774ADSTEVB kit is designed for use with the FRDMDUALK3664EVB in high-voltage isolated applications that provide an SPI-to-high-speed isolated communication interface. The FRDMDUALK3664EVB includes two MC33664 isolated-network high-speed transceivers allowing loopback connection. MCU SPI data bits are directly converted to pulse bit information.

Figure 5. FRDMDUALK3664EVB transceiver board

#### 5.1 Battery emulator connection

The RD33774ADSTEVB supports the use of a battery-cell emulator, such as the BATT-18EMULATOR board.

The BATT-18EMULATOR is an 18-cell battery-emulator board that provides an intuitive way to change the voltage across any of the 18 cells and four voltage outputs in order to emulate four external NTCs. The emulator board can be connected to the RD33774ADSTEVB J1 connector using the provided cell connection cable.

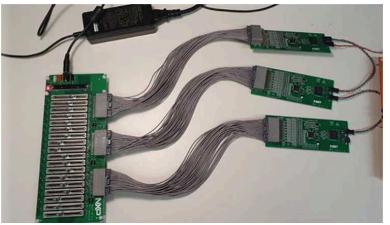

Up to three RD33774ADSTEVB can be connected to one BATT-18EMULATOR. See Figure 6

aaa-051169

Figure 6. RD33774ADSTEVBs connection to a BATT-18EMULATOR

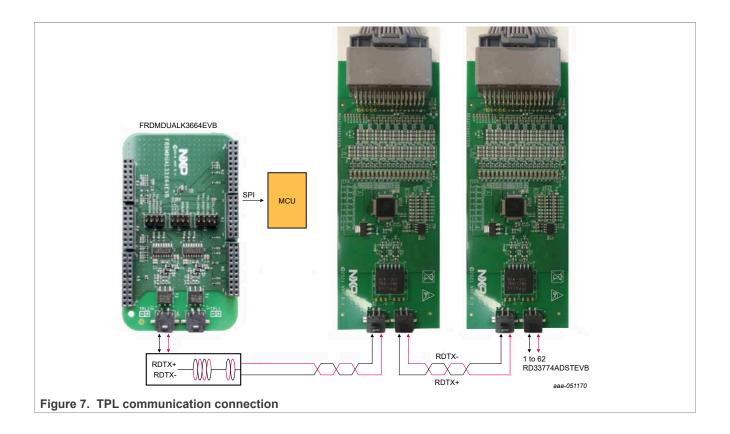

#### 5.2 TPL communication connection

In a high-voltage isolated application with a daisy-chain configuration, up to 62 RD33774ADSTEVB boards may be connected.

The TPL connections use the connectors J2 and J3.

#### **RD33774ADSTEVB** user manual

#### **RD33774ADSTEVB** user manual

## 6 Legal information

#### 6.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### 6.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Suitability for use in automotive applications — This NXP product has been qualified for use in automotive applications. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

#### 6.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

$\ensuremath{\mathsf{NXP}}$  — wordmark and logo are trademarks of NXP B.V.

UM11816

All information provided in this document is subject to legal disclaimers.

© 2023 NXP B.V. All rights reserved.

#### RD33774ADSTEVB user manual

## **Tables**

| Tab. 1. | Board description10 | Tab. 3. | Test points1       |

|---------|---------------------|---------|--------------------|

| Tab. 2. | Configuration12     | Tab. 4. | GPIO connections14 |

## RD33774ADSTEVB user manual

## **Figures**

|         | <b>5</b> 1 1 11            |         |                                    |    |

|---------|----------------------------|---------|------------------------------------|----|

| Fig. 1. | Block diagram 8            | ⊦ıg. 5. | FRDMDUALK3664EVB transceiver board | 15 |

| Fig. 2. | Board description10        | Fig. 6. | RD33774ADSTEVBs connection to a    |    |

| Fig. 3. | Cell-connector schematic11 |         | BATT-18EMULATOR                    | 15 |

| Fig. 4. | TPL connectors11           | Fig. 7. | TPL communication connection       | 16 |