# STDP4320 DisplayPort 1.2a Splitter

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time

### **Features**

- DisplayPort<sup>™</sup> dual mode receiver

- DP 1.2a compliant

- Link rate HBR2/HBR/RBR

- SST or MST (up to eight streams)

- 1, 2, or 4 lanes

- AUX CH 1 Mbps

- HPD out

- HDMI/DVI operation (3.2 Gbps link rate)

- Functions as eDP and MyDP receiver

- DisplayPort dual mode transmitters

- Two transmitter ports

- DP 1.2a compliant

- Link rate HBR2/HBR/RBR

- SST or MST (up to eight streams)

- 1, 2, or 4 lanes

- AUX CH 1 Mbps

- HPD in

- HDMI/DVI operation (3.2 Gbps link rate) with external level translator

- Functions as eDP transmitter

- SPDIF audio output

- Two SPDIF port pins

- 192 kHz/24 bits

- Compressed/LPCM

- Conversion from DP SST to TMDS format and vice versa

- HDCP repeater with embedded keys

- AUX to I2C bridge for EDID/MCCS pass through

- Maps on DDC ports

- Device configuration options

- SPI Flash

- I2C host interface

- Deep color support

- RGB/YCC (4:4:4) 16-bit color

- YCC (4:2:2) 16-bit color

- Spread spectrum on DisplayPort interface for EMI reduction

- Bandwidth

- Video resolution up to 4K2K @ 60 Hz

- Audio 7.1 Ch up to 192 kHz sample rate

- Low power operation

- Standby 30 mW

- Package

- 172 LFBGA (12 x 12 mm)

- Power supply voltages

- 3.3 V I/O; 1.2 V core

### **Applications**

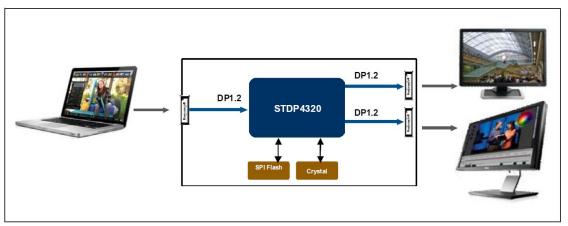

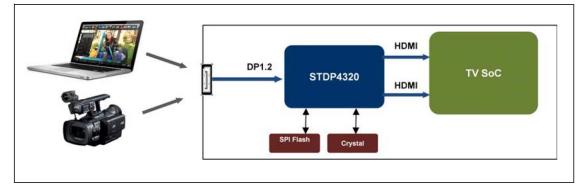

• Audio-video router for PC/notebooks, docking stations, hub, 4K2K TVs, daisy chain monitors, digital signage

## Contents

| 1. | Desc                         | ription                              | 7                                                   |    |  |  |  |

|----|------------------------------|--------------------------------------|-----------------------------------------------------|----|--|--|--|

| 2. | Appli                        | ication o                            | cation overview                                     |    |  |  |  |

| 3. | Feat                         | ure attrik                           | butes                                               | 10 |  |  |  |

|    | 3.1                          | Input ir                             | nterface                                            | 10 |  |  |  |

|    | 3.2                          | Output                               | 11                                                  |    |  |  |  |

|    | 3.3                          | Supported video timings              |                                                     |    |  |  |  |

|    | 3.4                          | Suppor                               | rted audio timings                                  | 11 |  |  |  |

|    | 3.5                          | Contro                               | I channel interfaces                                | 11 |  |  |  |

|    | 3.6                          | HDCP                                 | 1.3 support                                         | 12 |  |  |  |

|    | 3.7                          | Packag                               | ge                                                  | 12 |  |  |  |

|    | 3.8                          |                                      | supply voltages                                     |    |  |  |  |

|    | 3.9                          |                                      |                                                     |    |  |  |  |

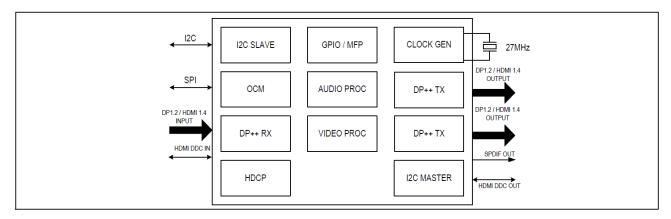

| 4. | Functional block description |                                      |                                                     |    |  |  |  |

|    | 4.1                          |                                      |                                                     |    |  |  |  |

|    | 4.2                          | Block diagram<br>Power sequence      |                                                     |    |  |  |  |

|    | 4.3                          |                                      |                                                     |    |  |  |  |

|    | 4.4                          |                                      |                                                     |    |  |  |  |

|    |                              | 4.4.1                                | generation<br>Internal crystal oscillator operation |    |  |  |  |

|    |                              | 4.4.2                                | Recommendations for crystal specifications          |    |  |  |  |

|    | 4.5                          | I2C inte                             | erface                                              |    |  |  |  |

|    | -                            | 4.5.1                                | I2C slave interface                                 |    |  |  |  |

|    |                              | 4.5.2                                | HDMI Rx DDC interface                               |    |  |  |  |

|    |                              | 4.5.3                                | HDMI Tx DDC interface                               |    |  |  |  |

|    |                              | 4.5.4                                | I2C over AUX interface                              |    |  |  |  |

|    |                              | 4.5.5                                | I2C transactions                                    |    |  |  |  |

|    | 4.6                          | DP, HD                               | 24                                                  |    |  |  |  |

|    | 4.7                          | HDMI formatter and controller        |                                                     |    |  |  |  |

|    | 4.8                          | DisplayPort formatter and controller |                                                     |    |  |  |  |

|    | 4.9                          | 3D forr                              | mats                                                | 27 |  |  |  |

|    | 4.10                         | Display                              | yPort++ transmitter                                 | 27 |  |  |  |

|    | 4.11                         |                                      | ·                                                   |    |  |  |  |

## STDP4320

|    | 4.12                   | SPDIF audio transmitter                                  |    |  |  |  |  |

|----|------------------------|----------------------------------------------------------|----|--|--|--|--|

|    |                        | 4.12.1 SPDIF audio output signal conditioning            |    |  |  |  |  |

|    | 4.13                   | Input-output maximum video timing support matrix         |    |  |  |  |  |

|    |                        | 4.13.1 HDMI output mode maximum video timing             |    |  |  |  |  |

|    | 4.14                   | DisplayPort output maximum video timings                 |    |  |  |  |  |

|    | 4.15                   | On-chip microcontroller (OCM)                            |    |  |  |  |  |

|    | 4.16                   | Serial peripheral interface for SPI Flash ROM            |    |  |  |  |  |

|    | 4.17                   | Test, debug, and development                             |    |  |  |  |  |

|    |                        | 4.17.1 UART interface                                    |    |  |  |  |  |

|    |                        | 4.17.2 In-system-programming (ISP) of external Flash ROM |    |  |  |  |  |

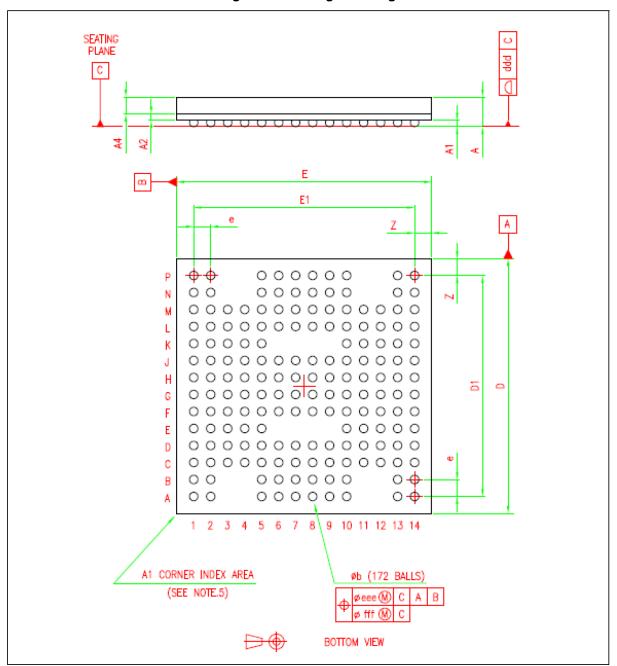

| 5. | BGA                    | footprint and pin lists                                  |    |  |  |  |  |

|    | 5.1                    | Ball grid array diagram                                  |    |  |  |  |  |

|    | 5.2                    | Full pin list sorted by pin number                       | 34 |  |  |  |  |

| 6. | Conr                   | nections                                                 |    |  |  |  |  |

|    | 6.1                    | Pin list                                                 |    |  |  |  |  |

|    | 6.2                    | Bootstrap configuration                                  | 44 |  |  |  |  |

| 7. | Package specifications |                                                          |    |  |  |  |  |

|    | 7.1                    | Package drawing                                          |    |  |  |  |  |

|    | 7.2                    | Package dimensions4                                      |    |  |  |  |  |

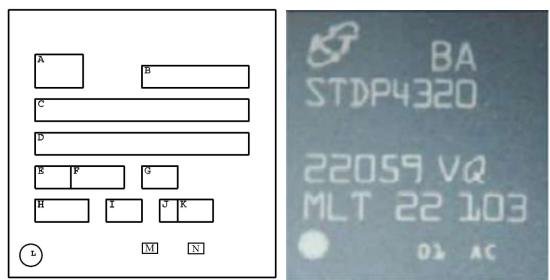

|    | 7.3                    | Marking field template and descriptors                   |    |  |  |  |  |

|    | 7.4                    | Classification reflow profile                            |    |  |  |  |  |

| 8. | Elect                  | trical specifications                                    |    |  |  |  |  |

|    | 8.1                    | Preliminary DC characteristics: absolute maximum ratings |    |  |  |  |  |

|    | 8.2                    | DC characteristics                                       |    |  |  |  |  |

|    | 8.3                    | AC characteristics                                       |    |  |  |  |  |

|    |                        | 8.3.1 DisplayPort receiver                               |    |  |  |  |  |

|    |                        | 8.3.2 DisplayPort transmitter                            | 51 |  |  |  |  |

|    |                        | 8.3.3 HDMI receiver                                      |    |  |  |  |  |

|    |                        | 8.3.4 HDMI transmitter                                   |    |  |  |  |  |

|    |                        | 8.3.5 Crystal specification                              | 54 |  |  |  |  |

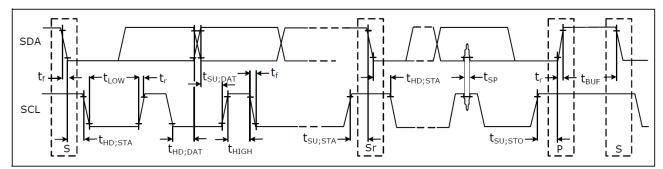

|    |                        | 8.3.6 I2C interface timing                               | 55 |  |  |  |  |

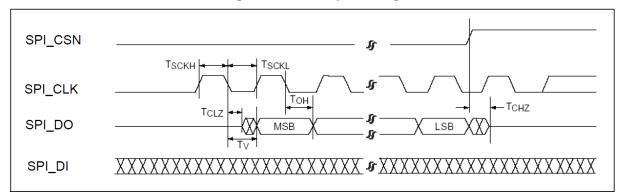

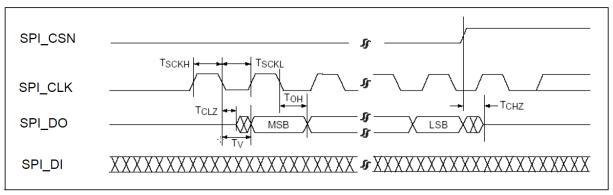

|    |                        | 8.3.7 SPI interface timing                               | 56 |  |  |  |  |

| 9. | Orde                   | ering information                                        | 57 |  |  |  |  |

kinetic

technologies

## **List of Tables**

| Table 1.  | Power sequencing requirements                 | 14 |

|-----------|-----------------------------------------------|----|

| Table 2.  | Power-on reset characteristics                | 15 |

| Table 3.  | Reset glitch specifications                   | 16 |

| Table 4.  | Recommended crystal specifications            | 19 |

| Table 5.  | I2C device-pin map                            | 20 |

| Table 6.  | I2C device address selection                  |    |

| Table 7.  | 3D format mapping from DP 1.2a to HDMI 1.4    | 27 |

| Table 8.  | SPDIF sample rates and line bit rates         | 29 |

| Table 9.  | HDMI output mode maximum video timings        | 30 |

| Table 10. | DisplayPort output mode maximum video timings | 31 |

| Table 11. | Pin list                                      |    |

| Table 12. | DisplayPort receiver pins                     | 38 |

| Table 13. | System function pins                          | 39 |

| Table 14. | Multi-function pins                           | 39 |

| Table 15. | Transmitter pins                              |    |

| Table 16. | System power and ground                       | 43 |

| Table 17. | Reserved pins                                 |    |

| Table 18. | Bootstrap configuration                       |    |

| Table 19. | Field descriptors                             | 47 |

| Table 20. | Absolute maximum ratings                      | 48 |

| Table 21. | DC characteristics                            |    |

| Table 22. | Maximum speed of operation                    |    |

| Table 23. | DisplayPort receiver electrical parameters    |    |

| Table 24. | DisplayPort transmitter electrical parameters | 51 |

| Table 25. | HDMI receiver DC characteristics              | 53 |

| Table 26. | HDMI receiver AC characteristics              | 53 |

| Table 27. | HDMI transmitter (DP++) DC characteristics    |    |

| Table 28. | HDMI transmitter AC characteristics           | 54 |

| Table 29. | Crystal specifications                        | 54 |

| Table 30. | I2C interface timing                          |    |

| Table 31. | SPI interface timing, VDD = 3.3 V             | 56 |

| Table 32. | Order codes                                   | 57 |

|           |                                               |    |

## List of Figures

| Figure 1.  | STDP4320 in video hub application9                             |   |

|------------|----------------------------------------------------------------|---|

| Figure 2.  | STDP4320 in 4K2K TV application9                               |   |

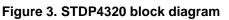

| Figure 3.  | STDP4320 block diagram13                                       | 3 |

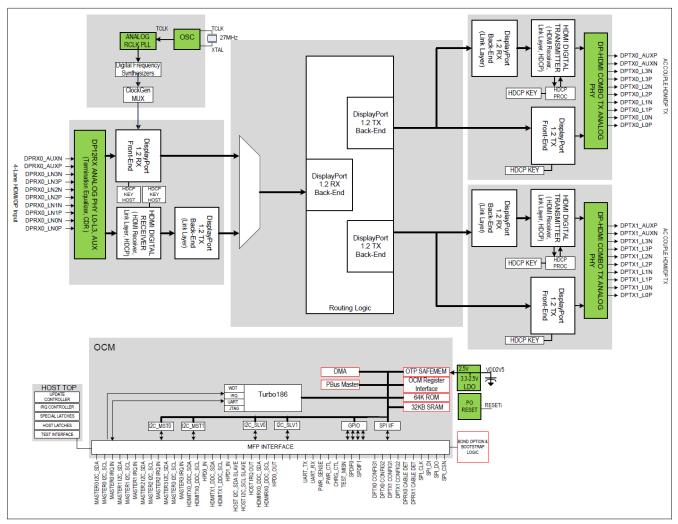

| Figure 4.  | Correct power sequencing14                                     | 1 |

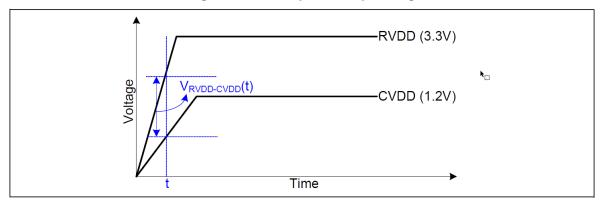

| Figure 5.  | Power-on reset timings                                         | 5 |

| Figure 6.  | RVDD_3V3 glitch                                                | 5 |

| Figure 7.  | Internal crystal oscillator operation16                        | 3 |

| Figure 8.  | Internal crystal oscillator circuit with an external crystal17 | 7 |

| Figure 9.  | Internal oscillator output                                     | 7 |

| Figure 10. | Parasitic capacitance sources                                  | 3 |

| Figure 11. | I2C devices                                                    | 9 |

| Figure 12. | Data transfer in I2C bus                                       | ١ |

| Figure 13. | SPDIF format                                                   | 3 |

| Figure 14. | SPDIF output circuit                                           | 9 |

| Figure 15. | STDP4320 BGA diagram                                           | 3 |

| Figure 16. | Package drawing48                                              | 5 |

| Figure 17. | Package dimensions                                             | 3 |

| Figure 18. | Marking template4                                              | 7 |

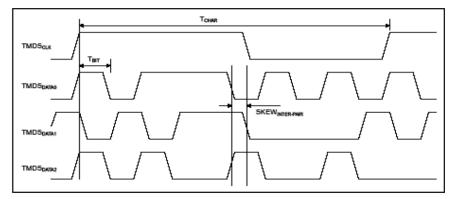

| Figure 19. | HDMI and DVI receiver AC characteristics                       | 3 |

| Figure 20. | I2C timing                                                     | 5 |

| Figure 21. | SPI input timing                                               | 3 |

| Figure 22. | SPI output timing                                              | 3 |

### 1. Description

The STDP4320 is a high-speed DisplayPort dual mode splitter IC targeted for audio-video demultiplexing and routing in applications such as notebooks, docking stations, video hub, 4K2K TVs, daisy chainable monitors, digital signage, etc. It consists of one dual mode input port and two dual mode output ports configurable as either DisplayPort or HDMI/DVI. STDP4320 is a VESA DP Standard Ver. 1.2a compliant device that supports advanced features such as MST, HBR2, 3D formats and GTC assist. Designs based on STDP4320 have the flexibility to offer either DP or HDMI/DVI connectors on its end product to interface with legacy and new generation video sources and sinks. In addition, STDP4320based products with a DisplayPort output connector are DP++ compliant and work with any HDMI or single link DVI sink through a passive level translator (dongle).

The STDP4320 uses Kinetic's latest generation DisplayPort dual mode receiver and transmitter technology that supports both DisplayPort and TMDS signal formats. This device receives MST format up to eight audio-video streams, which can be further routed on either of the two outputs in any combination of eight streams depending on the capability of downstream sinks. This device can also replicate the incoming video streams on both output ports simultaneously, thus allowing cloning on two downstream sinks. For example, a 4K2K 60 Hz video input is replicated on two output ports simultaneously. The DisplayPort receiver and transmitters support HBR2 speed, a data rate of 5.4 Gbps per lane with a total bandwidth of 21.6 Gbps link rate. In HDMI mode, this device supports link rates up to 3.2 Gbps corresponding to a pixel rate of 300 MHz, adequate for supporting video resolution up to FHD 120 Hz with all 3D formats. The device is also capable of delivering deep color video up to 16-bits per color. The STDP4320 allows audio transport from the source to the desired audio rendering devices over the video output port or through an SPDIF port.

The STDP4320 supports RGB and YCbCr colorimetric formats with color depth of 16, 12, 10, and 8 bits. The STDP4320 features the HDCP 1.3 content protection scheme with embedded keys for secure transmission of protected audio-video content. It also operates as an HDCP repeater for the downstream sinks.

The DDC ports in the STDP4320 allow the upstream source to access EDID and transfer MCCS commands to downstream sinks when the physical ports are either HDMI or DVI type. If both the upstream source and downstream sinks are DP type, I2C transactions take place over the AUX CH. If one of them is a DP type and the other is either a HDMI or DVI type, STDP4320 converts the I2C over AUX message protocol to I2C commands and sends it on the DDC port.

The device has an on-chip microcontroller with SPI, UART, and I2C interface. The STDP4320 uses an external SPI Flash ROM for storing device configuration firmware. It has an I2C slave port for external host communication. Other system interface signals include general-purpose IO for source, sink communication, detection, monitoring, etc. When the downstream sink is disconnected, STDP4320 automatically turns off the inactive port for power saving purposes.

## 2. Application overview

Figure 1. STDP4320 in video hub application

#### Figure 2. STDP4320 in 4K2K TV application

### 3. Feature attributes

### 3.1 Input interface

- Single DP++ interface featuring

- DisplayPort Ver. 1.2a compliant receiver; supports eDP and MyDP

- HDMI 1.4 compliant receiver

- Main link configuration

- SST or MST (up to eight streams)

- HBR2/HBR/RBR link rate

- 1, 2, or 4 lanes

- AUX CH: 1 Mbps Manchester transaction format

- HPD: IRQ\_HPD assertion

- Video: EDID 1.4 and CEA861 video timing and formats from 24 to 48 bits/pixel in RGB, YCC422, or YCC444 colorimetry

- Audio: DisplayPort 1.2a standard info frame packets and IEC60958/61937 type audio stream packets ranging from 16 to 24 bits/sample, 32 to 192 kHz sample rates

- HDMI link rate: 3.2 Gbps/data pair max

### 3.2 Output interface

- Two DP++ interfaces featuring

- AC coupled DisplayPort Ver. 1.2a compliant transmitter: supports eDP

- AC coupled HDMI 1.4 transmitter

- DP main link configuration

- SST or MST (up to eight streams)

- HBR2/HBR/RBR link rate

- 1, 2, or 4 lanes

- AUX CH: Manchester transaction format

- HPD: IRQ\_HPD assertion

- Video: EDID 1.4 and CEA861 video timing and formats from 24 to 48 bits/pixel in RGB, YCC422, or YCC444 colorimetry

- Audio: DisplayPort 1.2a standard info frame packets and IEC60958/61937 type audio stream packets ranging from 16 to 24 bits/sample, 32 to 192 kHz sample rates

- HDMI link rate: 3.2 Gbps/data pair max

### 3.3 Supported video timings

- 4K2K 60 Hz: 24 bits/pixel in DP 1.2a configuration

- 1920 x 1080 (FHD) 240 Hz, 24 bits/pixel

- All 3D formats defined in DP 1.2a and HDMI 1.4 standards

- All standard CEA861 timing formats

### 3.4 Supported audio timings

- All audio formats as specified in DP 1.2a and HDMI 1.4 standards

- SPDIF; 2-Ch LPCM, AC3, DTS, bit depth up to 24 bits, sample rate up to 192 kHz (applicable in DP SST/HDMI output use case)

### 3.5 Control channel interfaces

• AUX CH, DDC, I2C host interface, and UART (UART for test/debug purposes only)

### 3.6 HDCP 1.3 support

- Key sets for DP/HDMI RX and DP/HDMI TX integrated in one-time programmable ROM (OTP)

- Standalone HDCP repeater capability

### 3.7 Package

• 172 LFBGA (12 x 12 mm), 0.8 ball pitch

### 3.8 Power supply voltages

• 3.3 V I/O; 1.2 V core

### 3.9 ESD

• 2 kV HBM, 450 V CDM

### 4. Functional block description

### 4.1 Block diagram

### 4.2 Power sequence

When using linear regulators for the 3.3 V and 1.2 V supplies, precautions must be taken in designing the power supply system to meet the following requirements.

At any time during the power-up sequence, the actual voltage of the 3.3 V ring VDD (RVDD) power supply should always be equal to or higher than the actual voltage of the 1.2 V core VDD (CVDD). In mathematical terms, VRVDD >= VCVDD at all times.

Table 1. Power sequencing requirements

| Parameter                 | Min | Тур    | Мах |

|---------------------------|-----|--------|-----|

| VRVDD-VCVDD (for all t>0) | 0 V | 1.50 V |     |

Figure 4. Correct power sequencing

### 4.3 Power-on reset

The STDP4320 device has an integrated reset pulse generator. The internal reset pulse generator performs hardware reset under the following conditions:

- During system power-up, after the RVDD\_3V3 voltage has reached reset threshold voltage VT

- In the event RVDD\_3V3 voltage drops below threshold VT for more than approximately 150 ns

- Manually holding the RESETn pin low for a minimum of 1 ms

The active-low reset pulse on the RESETn pin generated by the internal reset pulse generator is described in the table below. During the reset period, all internal circuits and logic are reset to the default power-on state. To ensure proper chip operation, TCLK (generated by crystal oscillator or from the external clock source) must be applied during and after the reset.

The following figure shows the relationship between RVDD\_3V3 and RESETn during system power-up.

Figure 5. Power-on reset timings

#### Table 2. Power-on reset characteristics

| Description                      | Symbol         | Min    | Тур    | Мах    |

|----------------------------------|----------------|--------|--------|--------|

| Power-on reset threshold voltage | V <sub>T</sub> | 2.60 V | 2.70 V | 2.80 V |

| Reset pulse duration             | T <sub>R</sub> | 80 ms  | 100 ms | 150 ms |

| Push-button hold time            | T <sub>P</sub> | 1 ms   | -      | -      |

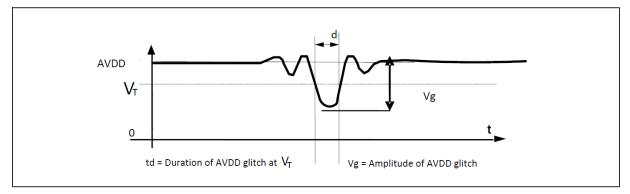

The glitch filter inside the internal reset pulse generator ignores the RVDD\_3V3 power line glitch if the duration of the glitch is shorter than approximately 150 ns. However, if RVDD\_3V3 voltage drops below the threshold  $V_T$  for more than 150 ns in duration, reset will be asserted and RESETn signal will go low. The following figure illustrates the RVDD\_3V3 glitch.

| Description               | Symbol | Min    | Тур | Мах   |

|---------------------------|--------|--------|-----|-------|

| RVDD_3V3 glitch duration  | tg     | 150 ns |     |       |

| RVDD_3V3 glitch amplitude | Vg     | 0.9 V  |     | 1.2 V |

Table 3. Reset glitch specifications

The RESETn pin requires a connection to ground with a 4.7 nF capacitor and a pull-up resistor of 1.2 K to RVDD\_3V3 to avoid spurious reset conditions caused by board noise.

### 4.4 Clock generation

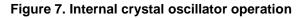

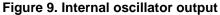

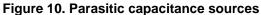

TCLK is the main timing clock for this device. All other internal clocks are generated from the TCLK. The TCLK oscillator circuitry is a custom designed circuit to support the use of an external oscillator (27 MHz) or a crystal resonator (27 MHz) to generate a reference frequency source, as shown in the figure below.

The recommended operation uses an external crystal, which in turn, uses an internal oscillator circuit to generate the main chip clock. The internal oscillator provides a low jitter and low harmonic clock to the internal circuitry. The internal oscillator circuit also minimizes the overdrive of the crystal, which reduces the aging of the crystal.

#### 4.4.1 Internal crystal oscillator operation

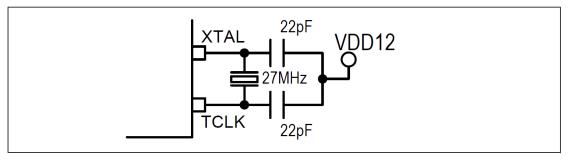

A crystal resonator is connected between the XTAL pin and the TCLK pin with the appropriately sized loading capacitors CEX1 and CEX2. The logic level on the SPDIF pin is latched during the de-asserting edge of the RESETn signal and provides the XTAL\_OSC\_SEL bootstrap signal. A '1' latched on this pin enables the crystal oscillator. The SPDIF pad has an internal pullup and should not be driven low during RESETn going high edge. Note that a '0' latched turns off the oscillator and the availability of an external oscillator on the TCLK pin is assumed.

Note: The size of CL1 and CL2 are determined from the crystal manufacturer's specification and by compensating for the parasitic capacitance of the device and the printed circuit board traces. The loading capacitors are terminated to the RPLL\_VDDA\_1V2 power supply. This connection increases the power supply rejection ratio when compared to terminating the loading capacitors to ground.

Figure 8. Internal crystal oscillator circuit with an external crystal

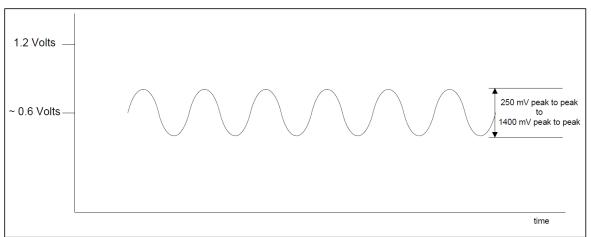

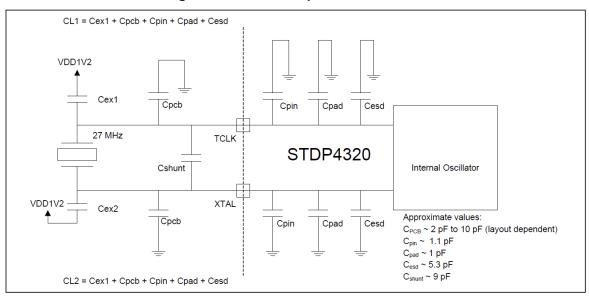

The internal oscillator circuit is a Pierce Oscillator circuit and a simplified schematic is shown in the figure above. The peak-to-peak voltage of the output can range from 250 mV to 1400 mV, depending on the specific characteristics of the crystal and variation in the oscillator characteristics. The output of the oscillator feeds to a comparator that converts the sine wave to a square wave. The comparator requires a minimum signal level of about 50 mV peak-to-peak to function correctly. The buffered output signal of the comparator distributes to the rest of the STDP4320 circuits.

One of the design parameters that must be given some consideration is the value of the loading capacitors used with the crystal, as shown below. The loading capacitance ( $C_{load}$ ) on the crystal is the combination of CL1 and CL2 and is calculated by  $C_{load} = ((CL1 * CL2)/(CL1 + CL2)) + C_{shunt}$ . The shunt capacitance  $C_{shunt}$  is the effective capacitance between the XTAL and TCLK pins. For STDP4320, this is

approximately 9 pF. CL1 and CL2 are a parallel combination of the external loading capacitors (Cex), the PCB board capacitance ( $C_{pcb}$ ), the pin capacitance ( $C_{pin}$ ), the pad capacitance ( $C_{pad}$ ), and the ESD protection capacitance ( $C_{esd}$ ). The capacitances are symmetrical so that CL1 = CL2 =  $C_{ex} + C_{PCB} + C_{pin} + C_{pad} + C_{ESD}$ . The correct value of Cex must be calculated based on the values of the load capacitances.

Some attention must be given to the details of the oscillator circuit when used with a crystal resonator. The PCB traces should be as short as possible. The value of  $C_{load}$  that is specified by the manufacturer should not be exceeded to avoid potential start-up problems with the oscillator. Additionally, the crystal should be a parallel resonate-cut and the value of the equivalent series resistance must be less than 90  $\Omega$ .

It is recommended to utilize a minimum 50 ppm crystal oscillator for all applications. This will ensure optimum performance.

#### 4.4.2 Recommendations for crystal specifications

While the selection of a crystal mainly depends on the specific PCB layout and the crystal manufacturer's

specifications, the following are general recommendations.

| Parameters                                  | Specifications              |

|---------------------------------------------|-----------------------------|

| Frequency                                   | 27.000 MHz                  |

| Operation mode                              | Fundamental                 |

| Operating temperature                       | -10°C to +70°C              |

| Frequency tolerance @25°C                   | +/- 50 ppm max              |

| Frequency stability over temperature        | +/- 100 ppm max             |

| Load capacitance CL<br>Shunt capacitance C0 | 8pF to 18pF<br>0.5pF to 7pF |

| Equivalent series resistance                | < 80 ohms                   |

#### Table 4. Recommended crystal specifications

### 4.5 I2C interface

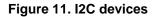

The STDP4320 implements I2C master and slave ports for inter-device communication purposes. The I2C interface pins for host and slave device access are shown below.

There are two I2C Masters and two I2C Slaves inside STDP4320. The I2C Masters can communicate with an external slave device in the system through any of the six I2C master ports. The two I2C Slaves have dedicated port pins; one is used for host interface from an external system master in case STDP4320 is used as a slave device, and the second I2C Slave is used for HDMI RX DDC interface. In addition, the I2C over AUX communication from the upstream DP source can be sent out on any of the Master I2C ports or over the downstream AUX Channel. The following table provides a summary of all port pin pairs through which I2C Slaves, Masters, and AUX20CM are accessible.

| I2C Master0                             | I2C Master1                             | I2C over AUX                                           | I2C Slave0     | I2C Slave1                 | Port pins                          |

|-----------------------------------------|-----------------------------------------|--------------------------------------------------------|----------------|----------------------------|------------------------------------|

| From OCM to external slave device       | From OCM to<br>external slave<br>device | From upstream DP<br>source to external<br>slave device | x              | x                          | MASTER0 I2C_SDA<br>MASTER0 I2C_SCL |

| From OCM to<br>external slave<br>device | From OCM to<br>external slave<br>device | From upstream DP<br>source to external<br>slave device | x              | х                          | MASTER1 I2C_SDA<br>MASTER1 I2C_SCL |

| From OCM to<br>external slave<br>device | From OCM to<br>external slave<br>device | From upstream DP<br>source to external<br>slave device | x              | х                          | MASTER2 I2C_SDA<br>MASTER2 I2C_SCL |

| From OCM to<br>external slave<br>device | From OCM to<br>external slave<br>device | From upstream DP<br>source to external<br>slave device | x              | х                          | MASTER3 I2C_SDA<br>MASTER3 I2C_SCL |

| From OCM to<br>downstream<br>HDMI sink  | From OCM to<br>downstream<br>HDMI sink  | From upstream DP<br>source to downstream<br>HDMI sink  | x              | х                          | HDMITX0_DDC_SDA<br>HDMITX0_DDC_SCL |

| From OCM to<br>downstream<br>HDMI sink  | From OCM to<br>downstream<br>HDMI sink  | From upstream DP<br>source to downstream<br>HDMI sink  | x              | x                          | HDMITX1_DDC_SDA<br>HDMITX1_DDC_SCL |

| x                                       | x                                       | From upstream DP<br>source to downstream<br>DP sink    | x              | x                          | TX0_AUX_P<br>TX0_AUX_N             |

| x                                       | x                                       | From upstream DP<br>source to downstream<br>DP sink    | x              | x                          | TX1_AUX_P<br>TX1_AUX_N             |

| x                                       | x                                       | x                                                      | Host interface | x                          | HOST I2C_SDA<br>HOST I2C_SCL       |

| x                                       | x                                       | x                                                      | x              | To upstream<br>HDMI source | HDMIRX0_DDC_SDA<br>HDMIRX0_DDC_SCL |

#### Table 5. I2C device-pin map

HDMI\_DDC\_SDA/HDMI\_DDC\_SCL signal pairs are also used for HDCP transactions between STDP4320 and connected HDMI source or sink.

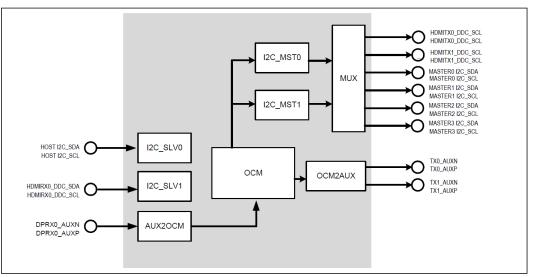

Access communication protocol over all of the above I2C ports is identical. Every byte on the SDA line must be 8-bits long and the number of bytes in each transfer is unrestricted. Data transferred is with MSB first. If a slave cannot send or receive a complete transfer until it has performed some other function, such as servicing an internal interrupt, it can hold the clock line SCL Low to force the master into wait state. Data transfer can resume when the slave is ready for another byte of data after it releases the clock line SCL.

#### 4.5.1 I2C slave interface

The I2C slave0 is intended for host communication purposes. In a typical application, the host controller (external I2C master) communicates with STDP4320 through this interface. STDP4320 contains a set of host interface registers that are directly read and written by the host controller. Whenever the host controller intends to configure or change the behavior of STDP4320, it writes into the corresponding host register. The STDP4320 responds to this instruction by executing the intended function and updating the status flag or result register. The host then reads the status or result registers. The host controller must provide the clocks on SCL for both read and write transactions. The port pins used for the host interface are HOST I2C\_SDA and HOST I2C\_SCL. When the chip power is turned off, these lines are tri-stated allowing other I2C devices to continue communication over common I2C bus. The host controller can access STDP4320 OCM registers with the device ID E0h/E2h/E4h/E6h and the core registers using configurable I2C device ID. The I2C device address selection is based on the settings of Bootstrap\_6 and Bootstrap\_7 as follows. Refer to Section 6.2: Bootstrap configuration for bootstrap pin descriptions.

| Bootstrap_7 | Bootstrap_6 | 12C device address |

|-------------|-------------|--------------------|

| Low         | Low         | E2h                |

| Low         | High        | E0h                |

| High        | Low         | E4h                |

| High        | High        | E6h                |

| Table (  | 6. I2C | device | address | selection  |

|----------|--------|--------|---------|------------|

| 1 4 5 10 |        | 401100 | 4441000 | 0010011011 |

#### 4.5.2 HDMI Rx DDC interface

The HDMIRX DDC interface is a 3.3 V tolerant open-drain I2C slave interface. A 5 V to 3.3 V external level shifter is recommended for these signal pairs to connect with the HDMI source. This interface handles the EDID, MCCS, or HDCP protocols with the upstream source.

#### 4.5.3 HDMI Tx DDC interface

The HDMITX DDC interface is a 3.3 V tolerant open-drain I2C master interface. A 3.3 V to 5 V external level shifter is recommended for these signal pairs to connect with the HDMI sinks. This interface handles the EDID, MCCS, or HDCP protocols with the downstream sinks.

#### 4.5.4 I2C over AUX interface

The I2C over AUX communication between STDP4320 and the upstream DisplayPort source is handled by the On-Chip Micro (OCM). The AUX2OCM block bridges between the upstream DP AUX channel and OCM for I2C message transaction. These I2C commands are further routed out either through one of the I2C masters or through the OCM2AUX Bridge for the downstream DP sinks. The selection of the output port pins are software configurable depending on the application. For ex: If the downstream sinks are HDMI, the I2C commands are sent out on HDMI DDC port pins. Similarly, if the downstream is DP sinks, the I2C commands are sent out on the downstream AUX channel. The EDID access and MCCS command exchange between DisplayPort source and the downstream sinks take place through this interface.

Note: The base firmware handles all AUX transactions through the AUX2OCM and OCM2AUX interface.

#### 4.5.5 I2C transactions

The basic I2C transactions are shown below. Commands in parenthesis are sent by I2C master.

#### Read sequence:

(SLAVE ADDRESS+R), ACK, DATA, (ACK), DATA, (ACK), DATA,..... (NACK), (Stop)

#### Write sequence:

(SLAVE ADDRESS+#W), ACK, (DATA), ACK,..... (DATA), ACK (Stop)

#### **Device addressing**

| S | DevID with R/W | Address |

|---|----------------|---------|

| 3 |                | Address |

#### Word write

The slave sends an ACK after every byte. S is *start* condition. P is *stop* condition.

| S | DevID with R/W = 0 | Address | Data (L) | Data (H) | Ρ |  |

|---|--------------------|---------|----------|----------|---|--|

|---|--------------------|---------|----------|----------|---|--|

#### Page write

The slave sends an ACK after every byte. The address is auto-incremented for every word received.

| S | DevID with<br>R/W = 0 | Address | Data0 (L) | Data0 (H) | Data1 (L) | Data1 (H) |  | DataN-1 (L) | DataN-1 (H) | Ρ |  |

|---|-----------------------|---------|-----------|-----------|-----------|-----------|--|-------------|-------------|---|--|

|---|-----------------------|---------|-----------|-----------|-----------|-----------|--|-------------|-------------|---|--|

#### Word read

The master writes the register address. The slave sends an ACK after every byte received.

| S | DevID with R/W = 0 | Address | Р |

|---|--------------------|---------|---|

|---|--------------------|---------|---|

The data is sent out in the second transaction. The master provides the clocks and sends an ACK after every byte, except the last one. The stop condition marks the end of the transaction.

| S         DevID with R/W = 1         Data (L)         Data (H) | Р |  |

|----------------------------------------------------------------|---|--|

|----------------------------------------------------------------|---|--|

#### Sequential read

The master writes the address of the first register to be read. The slave sends an ACK after every byte received.

| S DevID with R/W = 0 | Address | Р |

|----------------------|---------|---|

|----------------------|---------|---|

The data is sent out in the second transaction. The master provides the clock and sends an ACK after every byte, except the last one. The address is auto-incremented after every word sent out on the bus. The stop condition marks the end of the transaction.

#### Short read

This is similar to the sequential read, except the first write transaction with the address is omitted. The data is read from the current address in the address register. The master provides the clock and sends an ACK after every byte, except the last one. The address is auto-incremented after every word sent out on the bus. The stop condition marks the end of the transaction.

| s | DevID with R/W = 1 | Data0 (L) | Data0 (H) | Data1 (L) | Data1 (H) | <br>DataN-1 (L) | DataN-1 (H) | Р |

|---|--------------------|-----------|-----------|-----------|-----------|-----------------|-------------|---|

|   |                    | ( )       |           |           |           |                 |             |   |

### 4.6 DP, HDMI dual mode receiver

The STDP4320 has a high speed dual mode digital receiver that can be configured for DisplayPort, HDMI, or DVI operation. This receiver features four high speed differential input channels with a maximum link speed of 5.4 Gbps and a differential AUX Channel with a data rate of 1Mbps. The FastAUX feature is not supported. The Phy is configurable for DisplayPort mode or for HDMI/ DVI mode. The receiver has an internal differential termination of 100 ohms (50 ohms on each line to AVDD33). This can be either calibrated to 1/5th the external resistor value or manually programmable using register bits.

Inputs are AC-coupled in DisplayPort mode and DC-Coupled in HDMI / DVI modes. The dual mode receiver characteristics meet HBR2 operation in accordance with DisplayPort-1.2a specification. The Phy is also configurable for HDMI-1.4 operations up to 3.2 Gbps. The lane ordering of the receiver is programmable to optimize the board layout for each of the interface standards.

*Note:* The HDMI1.4 LAN and the audio back channel features are not supported. In case of DisplayPort input, the data first goes through de-serialization and clock recovery, followed by 10b-8b conversion, symbol recovery, lane-de-skew, and HDCP decryption. The receiver back-end block receives the input packets and converts into video raster and audio samples. The video de-packetizer generates a raster video stream of up to 16 bits/color at up to 300 MHz video clock rate from 1, 2, or 4 lanes of DisplayPort traffic. The data may be in RGB 444 or 422 formats. 422 is only supported for YUV. 3D-formatted packets and VSC packets conveying in-band 3D signals can also be received. The secondary packets received may be CEA861E info frames or audio stream packets, recovered into buffers or audio-FIFOs.

The received audio packet may be a 2-channel layout or an 8-channel layout. Coding types can be either IEC61937 or IEC60958 style encoded data for 1 to 8 channels of LPCM, AC3, and DTS audio streams. Other formats including HBR audio (based on audio InfoFrame support definition of the sink device DDC) are also supported. Audio copy management is supported.

The DisplayPort Aux channel is a bidirectional, AC-coupled, doubly terminated differential signal pair. It is capable of transmitting and receiving data at 1 Mbps. The Aux channel is for link management and device control purposes. The Aux channel in the STDP4320 handles the following functions:

- Link training/Link management

- Native AUX and I2C-over-AUX communication

The HPD output signal serves as a cable-plug event indicator, as well as an interrupt request to the source device. The HPD output signal is in low state as long as the receiver is inactive. Once the sink device is ready to receive data, it sets the HPD signal to an active high state. This indicates to the source device that the sink is ready to receive data over the DisplayPort interface. When the receiver needs to interrupt the source, it shortly brings the HPD signal to low state. Refer to HPD-IRQ event described in the DisplayPort 1.2a specification.

In the case of HDMI mode, the receiver supports a max link rate of 3.2Gbps of operation with all possible video timing up to 4K2K 30Hz and color depths up to 48 bpp depending on available bandwidth. All 3D TV formats and color formats are supported including RGB/YUV444/YUV422 and xvYCC. The receiver supports automatic video and audio mute based on link conditions. The data island packet processor handles GCP packets, ACR packets, and AVI info packets. The HDMI receiver supports an HPD out signal. HEAC is not supported.

The received signal first goes through de-serialization and clock recovery. The receiver block then recovers sync presence, monitors and measures link clock, and detects symbol boundaries, lane alignment, and detects HDMI/DVI protocol and decodes the signal into video and data island streams. The video format is also detected. The signals then go through HDCP decryption. Video and audio streams are recovered from HDMI decoding.

### 4.7 HDMI formatter and controller

This block formats and encodes the video (TMDS), audio (TERC4), and auxiliary information as per the HDMI 1.4 specifications, including the BCH error encoding. The input video data to the formatter can be up to 16bits/color and is to be accompanied by EIA/CEA 861 standard Hsync/Vsync and video clock up to 300 MHz. Input data can be either 444 RGB or YCbCr or 422 YCbCr. Pixel repeat of 1 to 4 is supported. Various 3D video formats can be transmitted. The 3D video format is indicated in the VIC Code in the AVI InfoFrame in conjunction with the 3D\_Structure values defined in Table H-2 of the HDMI

1.4 spec in the HDMI Vendor Specific InfoFrame. In addition, STDP4320 contains logic to map DisplayPort 3D structures to HDMI 3D structure.

The HDMI formatter also takes in 8-channel, IEC60958, and IEC61937 formatted audio data up to 192 kHz. This includes two-channel or multi-channel PCM, LBR compressed, and HBR audio. The HDMI does not compress or decompress audio, but simply inserts the received audio into appropriate fields of the selected audio packets type in the HDMI frame. The HDMI frame formatter interfaces to the transmitter serializer on three 10-bit parallel buses, which are synchronous with the TMDS clock.

The encoded 30-bit stream can be sent to DisplayPort++ compliant transmitter for serialization and transmission.

### 4.8 DisplayPort formatter and controller

The DisplayPort formatter encodes 24-bit audio and 48-bit video signals into 1/2/4 lanes of DisplayPort singlestream packets. The encoded data is sent to the DisplayPort++ transmitter for serialization and transmission. All link rates from 1.62 Gbps (RBR), 2.7 Gbps (HBR), and 5.4 Gbps (HBR2) are supported.

The video formatter inputs a raster video stream of up to 16 bits per color at up to 300 MHz video clock rate. The data is converted to primary stream packets and can be mapped in 1, 2, or 4 lane formats as defined by DP 1.2a specifications. Input data may be in RGB or YUV 444 or 422 formats. Transfer units are formed with appropriate symbol stuffing as defined in the DisplayPort 1.2a specifications. MSA for all DP 1.2a color encoding formats up to 16-bits per color are supported. VSC packets can be used to send 3D in-band signals.

Secondary packets may be CEA861E Info Frames or audio stream packets. These are inserted into the main stream along with bit stuffing and MSA data stuffing. Inter-lane skewing is performed as defined by DP 1.2a specifications.

Audio stream data is formatted into secondary packets. The packet may be a 2-channel layout or an 8channel layout. Coding types can be either IEC61937 or IEC60958 style encoded data for 1 to 8 channels of LPCM, AC2, and DTS audio streams. Other formats (based on audio InfoFrame support definition of the sink device DDC) and also audio copy management are supported.

The DPTX front-end block then performs data scrambling, 8b-10 encoding and DisplayPort specific formatting of the input data and generates one to four 20-bit parallel streams for each DP++ transmitter to serialize and output. An Aux channel controller handles link initiation, HDCP authentication communications, and DPCD messaging with the sink device. Side-band messages as defined in the DP 1.2a specification are also supported.

The AUX channel is used for link management and device control and handles the following functions:

- Link training

- Exchanging DPCD AUX and I2C communication

The HPD line is used to detect the presence of the sink device and to receive the interrupt requests from a DisplayPort sink device. The transmitter monitors the activity on the HPD line and responds to the receiver's interrupt request by initiating the Aux channel transaction. The HPD line remains low when the sink device is not present and high when the sink device is ready to receive DisplayPort signals. An active low short pulse on the HPD line indicates an interrupt request from the sink device for an AUX transaction.

### 4.9 3D formats

The DisplayPort receiver and DisplayPort ++ transmitter supports all compatible 3D formats defined the DP1.2a and HDMI1.4 specifications. Following table lists the mapping of various 3D formats when converting DisplayPort input to HDMI output:

| From DP 1.2a format                                    | To HDMI 1.4b format       |

|--------------------------------------------------------|---------------------------|

| Frame/field sequential (VSC=0x01, 0x11, 0x21)          | Frame packing (0x00)      |

| Stacked frame (VSC=0x02)                               | Frame packing (0x00)      |

| Frame/Field Sequential (VSC=0x01, 0x11, 0x21)          | Frame Packing (0x00)      |

| Stacked Frame (VSC=0x02)                               | Frame Packing (0x00)      |

| Pixel Interleaved Right on Even Line (VSC=0x03)        | Line Alternative(0x02)    |

| Pixel Interleaved Right on Odd Line (VSC=0x013)        | Line Alternative(0x02)    |

| Pixel Interleaved Checker Board (VSC=0x23)             | -                         |

| Pixel Interleaved Left First Vertical Line (VSC=0x33)  | -                         |

| Pixel Interleaved Right First Vertical Line (VSC=0x43) | -                         |

| Side-by-Side Left View on Left Side (VSC=0x04)         | Side-by-Side (Full, 0x03) |

| Side-by-Side Left View on Left Side (VSC=0x14)         | Side-by-Side (Full, 0x03) |

| Table 7. 3D format mapping from DP 1.2a to HDMI 1.4 |

|-----------------------------------------------------|

|-----------------------------------------------------|

### 4.10 DisplayPort++ transmitter

The DisplayPort++ transmitter can receive lane signals from either the HDMI formatter or the DisplayPort formatter blocks. The main lanes are unidirectional, AC-coupled, doubly terminated differential pairs, to transport the audio-video streams. The serializer and PLL can operate in HDMI or DisplayPort modes. In HDMI mode, an external level translator is needed to make the output levels HDMI compliant. In DP++ modes, the AUX+/- can be shorted with HDMI\_DDC\_SDA/SCL. Configuration pins on the TX connector can be used to identify the presence of a passive dongle so the transmitters can be reconfigured as appropriate.

The transmitter supports all bit rates, 5.4 Gbps per lane (HBR2), 2.7 Gbps (HBR), and 1.62 Gbps (RBR). The transmitter locks to one of the bit rates after negotiating with the receiver (sink device). The transmitter supports down-spreading of link frequency.

The DisplayPort Aux channel is a half-duplex bidirectional, AC-coupled, doubly terminated differential pair. It is capable of transmitting and receiving bits at 1 Mbps.

### 4.11 HDCP

The HDCP block in STDP4320 establishes a secure channel for the transmission of high-definition multimedia data from an upstream source device to downstream receiving device(s). The HDCP cipher is used to provide key and messaging information to authenticate the transmission. Signals from the input video source device instruct the HDCP engine when to generate encryption keys, which are used by the transmitter to encrypt outgoing video data. An encrypted input stream from the DisplayPort or HDMI receiver will be re-transmitted as an encrypted stream with an HDCP repeater implementation. A driver controls HDCP authentication and synchronization of the HDCP receiver to allow encrypted data and identification of the receiver capabilities via AUX Channel or DDC. STDP4320 stores two separate sets of HDCP transmitter keys and one set of receiver keys within the OTP memory space.

### 4.12 SPDIF audio transmitter

STDP4320 includes two IEC60958 compliant SPDIF transmitters. Audio signals received over the DisplayPort or HDMI input can be transmitted on the SPDIF output port pins to either drive external audio DAC/amplifiers or an external audio processor. The SPDIF audio output is available as optional, besides the audio being transmitted over the DP or HDMI output. The feature is available in DP SST and/or HDMI output use cases. It is not available in DP MST output use cases. Audio outputs from DP or HDMI transmitter and SPDIF transmitter can be enabled simultaneously. Any two channels from an 8-channel DP or HDMI LPCM audio stream can be transmitter also supports multi-channel compressed audio formats such as AC3 and DTS. There is no internal processing done on the audio stream. The output signal however, can be auto-muted based on receiver line conditions to avoid output of transient audio glitches during signal transition conditions.

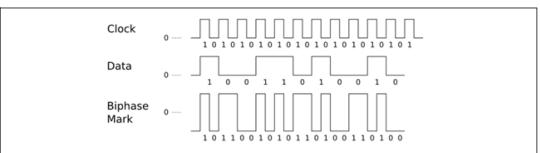

The coding format used is BiPhase Mark Code (BMC) shown below.

#### Figure 13. SPDIF format

For each sample, two 32 bit words are sent out resulting in the following bit rates. The sample size can be 16, 20, or 24 bits. The data may be PCM or Compressed Audio.

|   | Sample rate | Bit rate    |

|---|-------------|-------------|

| 1 | 44.1 kHz    | 2.822 Mbps  |

| 2 | 48.0 kHz    | 3.072 Mbps  |

| 3 | 88.2 kHz    | 5.645 Mbps  |

| 4 | 96.0 kHz    | 6.144 Mbps  |

| 5 | 192.0 kHz   | 12.288 Mbps |

#### Table 8. SPDIF sample rates and line bit rates

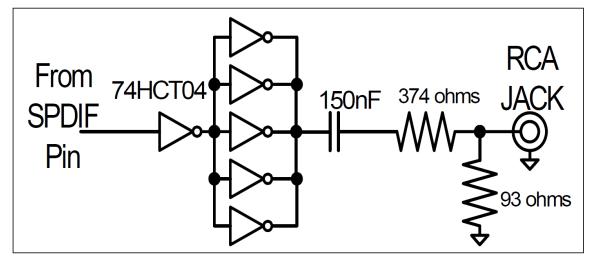

#### 4.12.1 SPDIF audio output signal conditioning

SPDIF output needs to have a circuit to make the voltage-down shift of the LVTTL signal to specific SPDIF signal. An example of such a conversion circuit is shown below.

### 4.13 Input-output maximum video timing support matrix

Maximum input-to-output timings are provided in the tables below. Note that the data path has a limit of 300 MHz on the HDMI output, thus maximum video timing with HDMI input or output configuration is limited to 4k2k 30Hz. Higher video timings up to 4k2k 60Hz is supported with the DisplayPort input, output configuration.

### 4.13.1 HDMI output mode maximum video timing

|   | Input video<br>DP or HDMI<br>mode | Video resolution                          | Color<br>depth | Video clock | HDMI output video timing                 |

|---|-----------------------------------|-------------------------------------------|----------------|-------------|------------------------------------------|

| 1 | 1L 5.4 GHz<br>Or<br>2L 2.7 GHz    | 1920 x 1080p 60 Hz,<br>reduced blanking   | 10 bits        | 148.5 MHz   | 1920 x 1080p 60 Hz, 10 bit, 185.6<br>MHz |

| 2 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz    | 1920 x 1080p 60 Hz,<br>standard blanking  | 16 bits        | 148.5 MHz   | 1920 x 1080p 60 Hz, 16 bit, 297.0<br>MHz |

| 3 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz    | 2560 x 1440 60 Hz,<br>reduced blanking    | 10 bits        | 241.5 MHz   | 2560 x 1440 60 Hz, 10 bit 301.88<br>MHz  |

| 4 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz    | 2560 x 1600 60 Hz,<br>reduced blanking    | 8 bits         | 268.50 MHz  | 2560 x 1600 60 Hz, 8 bit, 268.5<br>MHz   |

| 5 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz    | 1920 x 1080p 120 Hz,<br>standard blanking | 8 bits         | 297.0 MHz   | 1920 x 1080p 120 Hz, 8 bit 297.0<br>MHz  |

| 6 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz    | 4K x 2K, 24 Hz, reduced blanking          | 12 bits        | 211.5 MHz   | 4K x 2K 240 Hz, 12 bit, 317.0 MHz        |

| 7 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz    | 4K x 2K, 30 Hz, reduced blanking          | 8 bits         | 265.0 MHz   | 4K x 2K 30 Hz, 8 bit, 265.0 MHz          |

| 8 | HDMI1.4                           | 4K x 2K, 24 Hz, standard<br>blanking      | 12 bits        | 211.5 MHz   | 4K x 2K 30 Hz, 12 bit, 317.0 MHz         |

| 9 | HDMI1.4                           | 4K x 2K, 30 Hz, reduced blanking          | 8 bits         | 265.0 MHz   | 4K x 2K 30 Hz, 8 bit, 265.0 MHz          |

### 4.14 DisplayPort output maximum video timings

|   | Input DP                       | Video resolution                                 | Output<br>color<br>depth | Video clock | DisplayPort output video timing |            |             |  |

|---|--------------------------------|--------------------------------------------------|--------------------------|-------------|---------------------------------|------------|-------------|--|

| 1 | 1L 5.4 GHz<br>Or<br>2L 2.7 GHz | 1920 x 1080p 60 Hz,<br>reduced blanking          | 10 bits                  | 148.5 MHz   | 2L 5.4 GHz                      | 4L 2.7 GHz | 4L 1.62 GHz |  |

| 2 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz | 1920 x 1080p 60 Hz,<br>16b, standard<br>blanking | 16 bits                  | 148.5 MHz   | 2L 5.4 GHz                      | 4L 2.7 GHz | -           |  |

| 3 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz | 2560 x 1440 60 Hz,<br>reduced blanking           | 10 bits                  | 241.5 MHz   | 2L 5.4 GHz                      | 4L 2.7 GHz | -           |  |

| 4 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz | 2560 x 1600 60 Hz,<br>reduced blanking           | 8 bits                   | 268.50 MHz  | 2L 5.4 GHz                      | 4L 2.7 GHz | -           |  |

| 5 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz | 1920 x 1080p 120 Hz,<br>standard blanking        | 8 bits                   | 97.0 MHz    | 2L 5.4 GHz                      | 4L 2.7 GHz | -           |  |

| 6 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz | 4K x 2K, 24 Hz,<br>reduced blanking              | 12 bits                  | 211.5 MHz   | 2L 5.4 GHz                      | 4L 2.7 GHz | -           |  |

| 7 | 2L 5.4 GHz<br>Or<br>4L 2.7 GHz | 4K x 2K, 30 Hz,<br>reduced blanking              | 8 bits                   | 265.0 MHz   | 2L 5.4 GHz                      | 4L 2.7 GHz | -           |  |

| 8 | HDMI1.4                        | 4K x 2K, 24 Hz,<br>standard blanking             | 12 bits                  | 211.5 MHz   | 2L 5.4 GHz                      | 4L 2.7 GHz | -           |  |

| 9 | HDMI1.4                        | 4K x 2K, 30 Hz,<br>reduced blanking              | 8 bits                   | 265.0 MHz   | 2L 5.4 GHz                      | 4L 2.7 GHz | -           |  |

|   | 42L 5.4 GHz                    | 4K x 2K, 60 Hz,<br>reduced blanking              | 10 bits                  | 538.5 MHz   | 4L 5.4 GHz                      | -          | -           |  |

#### Table 10. DisplayPort output mode maximum video timings

### 4.15 On-chip microcontroller (OCM)

The STDP4320 features a 16-bit on-chip microcontroller. On Power-on Reset, the OCM executes code from internal ROM. Following initial chip configuration, the execution can transfer to external Flash memory. The OCM is used to initialize various modules and provide firmware drivers for the receivers and transmitters, as well as execute customer-specific application code involved in the chip deployment. The OCM can execute at 150 MHz clock and can be tuned to optimize power consumption and processing requirements. Among the various peripheral controllers that are part of OCM are timers, interrupt controller, I2C master and slave controllers, UART, and general-purpose input-output pins. The GPIO pins are used to monitor and control external TTL outputs. Some of the monitoring functions include cable detection, host power detection etc. External power supply units can be controlled by programmable outputs to control the way the system is powered.

The chip supports a SPI interface to connect a commercial serial Flash ROM device. The chip supports

SPI Flash ROMs of sizes up to 4 MBits. Contact Kinetic for the list of SPI Flash devices supported in the ISP driver tool.

### 4.16 Serial peripheral interface for SPI Flash ROM

The SPI interface between STDP4320 and a serial Flash ROM is as follows:

- SPI\_CSn <-> CE# of SPI memory

- SPI\_CLK <-> SCK of SPI memory

- SPI\_DO <-> SI of SPI memory

- SPI\_DI <-> SO of SPI memory

As an option, the SPI Flash can be partitioned to hold two executable images; only one of them is valid for execution at a time. A Flash image can be updated through In-System Programming (ISP). Once the update is successful, the old image is invalidated. During the next boot-up, the new Flash image will be executed. It is possible to connect GPIO pins to control other pins the Flash memory might need to interface to. Pins of WP# and HOLD# of SPI memory are options for controlling the SPI device. WP#, if pulled low, disables writing to the memory. HOLD# is used when multiple devices are used in daisy-chain configuration. They can be pulled-high at all times to disable their functions or they can be controlled with GPIOs for more flexibility. The SPI pins must not be driven during RESETn low, as this can cause potential lock-ups due to boot-failure. The levels on these pins during reset are used for bootstrap configuration and this could change the way the chip boots.

### 4.17 Test, debug, and development

The following sections are useful for chip test, debug, and development purposes.

#### 4.17.1 UART interface

The OCM has an integrated Universal Asynchronous Receiver and Transmitter (UART) port that can be used as a factory debug port. The UART interface is optional and described only to give information for developmental/debug purposes. In particular, the UART can be used to 1) read/write chip registers; 2) In-System-Programming of the SPI Flash. The UART\_RX and UART\_TX pins also share functionality with GPIO. When unused, these pins are available as GPIO pins. The UART baud rate is set to 115200 baud.

#### 4.17.2 In-system-programming (ISP) of external Flash ROM

It is possible to program the serial ROM devices via the standard UART or I2C or through DisplayPort AUX channel or HDMI DDC interface. The embedded boot firmware performs the programming of external Flash ROM. However, ISP requires an external hardware and software tool (GProbe). Contact Kinetic for the ISP tool and procedure.

### 5. BGA footprint and pin lists

### 5.1 Ball grid array diagram

The ball grid array (BGA) diagrams give the allocation of pins to the package, shown from the top looking down using the PCB footprint.

The STDP4320 is available in a 172-pin LFBGA package.

White = no ball at this location

n/c = no connect: ball present, but must not be connected

|   | 1                  | 2                  | 3          | 4                  | 5          | 6               | 7         | 8         | 9          | 10         | 11                   | 12                   | 13                   | 14                   |   |

|---|--------------------|--------------------|------------|--------------------|------------|-----------------|-----------|-----------|------------|------------|----------------------|----------------------|----------------------|----------------------|---|

| А | VSS                | RX0_LN2_N          |            |                    | RX0_LN0_P  | RX0_AUX_P       | RX0_AUX_N | n/c       | n/c        | n/c        |                      |                      | n/c                  | VSS                  | А |

| в | RX0_LN3_P          | RX0_LN2_P          |            |                    | RX0_LN0_N  | VSS             | VSS       | VSS       | VSS        | n/c        |                      |                      | n/c                  | n/c                  | в |

| с | RX0_LN3_N          | AVDD33_RX          | RX0_LN1_N  | RX0_LN1_P          | AVDD12_RX  | AVDD12_RX       | AVDD33_RX | AVDD33_RX | AVDD12_RX  | AVDD12_RX  | n/c                  | n/c                  | AVDD33_RX            | n/c                  | с |

| D | TX1_HPD            | TEST               | VSS        | VSS                | VSS        | RX0_REXT        | VSS       | VSS       | n/c        | VSS        | VSS                  | VSS                  | HDMI_TX0_D<br>DC_SCL | HDMI_TX0_D<br>DC_SDA | D |

| E | n/c                | SPDIF_OUT0         | HDMI_CEC   | TX0_HPD            | DVDD12     |                 |           |           |            | DVDD12     | HDMI_TX1_D<br>DC_SDA | GPIO8                | GPIO6                | HDMI_TX1_D<br>DC_SCL | E |

| F | MASTER1_IR<br>Q_IN | GPO                | SPDIF_OUT1 | RX0_HPD            | DVDD12     | VSS             | VSS       | VSS       | VSS        | DVDD12     | GPIO9                | GPIO10               | GPIO11               | GPIO7                | F |

| G | MASTER2_IR<br>Q_IN | MASTER3_IR<br>Q_IN | GPIO13     | MASTERO_IR<br>Q_IN | DVDD12     | VSS             | VSS       | VSS       | VSS        | DVDD12     | MASTER2_I2<br>C_SDA  | MASTER2_I2<br>C_SCL  | MASTER0_12<br>C_SDA  | MASTER0_12<br>C_SCL  | G |

| н | GPIO12             | HOST_IRQ_O<br>UT   | SPI_CLK    | UART_TX            | DVDD12     | VSS             | VSS       | VSS       | VSS        | DVDD12     | HDMI_RX0_D<br>DC_SCL | RESET_N              | MASTER1_I2<br>C_SDA  | MASTER1_I2<br>C_SCL  | н |

| J | SPI_DI             | UART_RX            | SPI_CSN    | GPIO2              | DVDD33     | VSS             | VSS       | VSS       | VSS        | DVDD33     | n/c                  | HOST_I2C_S<br>CL     | MASTER3_12<br>C_SCL  | MASTER3_12<br>C_SDA  | J |

| к | TCLK_3V3_O<br>UT   | SPI_DO             | GPIO0      | GPIO1              | DVDD25_SM  |                 |           |           |            | GPIO5      | n/c                  | HDMI_RX0_D<br>DC_SDA | AVDD12_PLL           | HOST_I2C_S<br>DA     | к |

| L | TCLK_1V2_0<br>UT   | TX0_REXT           | VSS        | VSS                | GPIO3      | VSS             | VSS       | VSS       | VSS        | GPIO4      | VSS                  | VSS                  | AVDD12_OS<br>C1      | AVDD33_RC<br>OSC     | L |

| м | TX0_AUX_N          | AVDD12_TX0         | TX0_LN2_N  | TX0_LN2_P          | AVDD12_TX0 | AVDD12_OS<br>C0 | VSS       | VSS       | TX1_REXT   | AVDD12_TX1 | TX1_LN2_N            | TX1_LN2_P            | AVDD33_TX1           | TX1_LN0_P            | м |

| N | TX0_AUX_P          | TX0_LN3_P          |            |                    | TX0_LN1_N  | AVDD33_TX0      | TCLK      | XTAL      | AVDD12_TX1 | TX1_LN3_P  |                      |                      | TX1_LN1_N            | TX1_LN0_N            | N |

| Р | VSS                | TX0_LN3_N          |            |                    | TX0_LN1_P  | TX0_LN0_N       | TX0_LN0_P | TX1_AUX_N | TX1_AUX_P  | TX1_LN3_N  |                      |                      | TX1_LN1_P            | VSS                  | Р |

|   | 1                  | 2                  | 3          | 4                  | 5          | 6               | 7         | 8         | 9          | 10         | 11                   | 12                   | 13                   | 14                   |   |

#### Figure 15. STDP4320 BGA diagram

Full pin list sorted by pin number Table 11. Pin list 5.2

| Pin number       | Net name         |

|------------------|------------------|

| A1               | VSS              |

| A2               | RX0_LN2_N        |

| A5               | RX0_LN0_P        |

| A6               | RX0_AUX_P        |

| A7               | RX0_AUX_N        |

| A8, A9, A10, A13 | n/c              |

| A14              | VSS              |

| B1               | RX0_LN3_P        |

| B2               | RX0_LN2_P        |

| B5               | RX0_LN0_N        |

| B6, B7, B8, B9   | VSS              |

| B10, B13, B14    | n/c              |

| C1               | RX0_LN3_N        |

| C2               | AVDD33_RX        |

| C3               | RX0_LN1_N        |

| C4               | RX0_LN1_P        |

| C5, C6           | AVDD12_RX        |

| C7, C8           | AVDD33_RX        |

| C9, C10          | AVDD12_RX        |

| C11, C12         | n/c              |

| C13              | AVDD33_RX        |

| C14              | n/c              |

| D1               | TX1_HPD          |

| D2               | TEST             |

| D3, D4, D5       | VSS              |

| D6               | RX0_REXT         |

| D7, D8           | VSS              |

| D9               | n/c              |

| D10, D11, D12    | VSS              |

| D13              | HDMI_TX0_DDC_SCL |

| D14              | HDMI_TX0_DDC_SDA |

| E1               | n/c              |

| E2               | SPDIF_OUT0       |

### Table 11. Pin list (continued)

| Pin number     | Net name           |

|----------------|--------------------|

| E3             | HDMI_CEC           |

| E4             | TX0_HPD            |

| E5             | DVDD12             |

| E10            | DVDD12             |

| E11            | HDMI_TX1_DDC_SDA   |

| E12            | GPIO8              |

| E13            | GPIO6              |

| E14            | HDMI_TX1_DDC_SCL   |

| F1             | MASTER1_IRQ_IN     |

| F2             | GPO                |

| F3             | SPDIF_OUT1         |

| F4             | RX0_HPD            |

| F5             | DVDD12             |

| F6, F7, F8, F9 | VSS                |

| F10            | DVDD12             |

| F11            | GPIO9              |

| F12            | GPIO10             |

| F13            | GPIO11             |

| F14            | GPIO7              |

| G1             | MASTER2_IRQ_IN     |

| G2             | MASTER3_IRQ_IN     |

| G3             | GPIO13/TX1_CONFIG2 |

| G4             | MASTER0_IRQ_IN     |

| G5             | DVDD12             |

| G6, G7, G8, G9 | VSS                |

| G10            | DVDD12             |

| G11            | MASTER2_I2C_SDA    |

| G12            | MASTER2_I2C_SCL    |

| G13            | MASTER0_I2C_SDA    |

| G14            | MASTER0_I2C_SCL    |

| H1             | GPIO12/TX1_CONFIG1 |

| H2             | HOST_IRQ_OUT       |

| H3             | SPI_CLK            |

| H4             | UART_TX            |

| H5             | DVDD12             |

### Table 11. Pin list (continued)

| Pin number     | Net name             |

|----------------|----------------------|

| H6, H7, H8, H9 | VSS                  |

| H10            | DVDD12               |

| H11            | HDMI_RX0_DDC_SCL     |

| H12            | RESETn               |

| H13            | MASTER1_I2C_SDA      |

| H14            | MASTER1_I2C_SCL      |

| J1             | SPI_DI               |

| J2             | UART_RX              |

| J3             | SPI_CSN              |

| J4             | GPIO2                |

| J5             | DVDD33               |

| J6, J7, J8, J9 | VSS                  |

| J10            | DVDD33               |

| J11            | n/c                  |

| J12            | HOST_I2C_SCL         |

| J13            | MASTER3_I2C_SCL      |

| J14            | MASTER3_I2C_SDA      |

| K1             | TCLK_3V3_OUT         |

| K2             | SPI_DO               |

| K3             | GPIO0/TX0_CONFIG1    |

| K4             | GPIO1/TX0_CONFIG2    |

| K5             | DVDD25_SM            |

| K10            | GPIO5                |

| K11            | n/c                  |

| K12            | HDMI_RX0_DDC_SDA     |

| K13            | AVDD12_PLL           |

| K14            | HOST_I2C_SDA         |

| L1             | TCLK_1V2_OUT         |

| L2             | TX0_REXT             |

| L3, L4         | VSS                  |

| L5             | GPIO3/RX0_CABLE_DET0 |

| L6, L7, L8, L9 | VSS                  |

| L10            | GPIO4/RX0_CABLE_DET1 |

| L11, L12       | VSS                  |

| L13            | AVDD12_OSC1          |

## Table 11. Pin list (continued)

| Pin number | Net name     |  |

|------------|--------------|--|

| L14        | AVDD33_RCOSC |  |

| M1         | TX0_AUX_N    |  |

| M2         | AVDD12_TX0   |  |

| M3         | TX0_LN2_N    |  |

| M4         | TX0_LN2_P    |  |

| M5         | AVDD12_TX0   |  |

| M6         | AVDD12_OSC0  |  |

| M7, M8     | VSS          |  |

| M9         | TX1_REXT     |  |

| M10        | AVDD12_TX1   |  |

| M11        | TX1_LN2_N    |  |

| M12        | TX1_LN2_P    |  |

| M13        | AVDD33_TX1   |  |

| M14        | TX1_LN0_P    |  |

| N1         | TX0_AUX_P    |  |

| N2         | TX0_LN3_P    |  |

| N5         | TX0_LN1_N    |  |

| N6         | AVDD33_TX0   |  |

| N7         | TCLK         |  |

| N8         | XTAL         |  |

| N9         | AVDD12_TX1   |  |

| N10        | TX1_LN3_P    |  |

| N13        | TX1_LN1_N    |  |

| N14        | TX1_LN0_N    |  |

| P1         | VSS          |  |

| P2         | TX0_LN3_N    |  |

| P5         | TX0_LN1_P    |  |

| P6         | TX0_LN0_N    |  |

| P7         | TX0_LN0_P    |  |

| P8         | TX1_AUX_N    |  |

| P9         | TX1_AUX_P    |  |

| P10        | TX1_LN3_N    |  |

| P13        | TX1_LN1_P    |  |

| P14        | VSS          |  |

# 6. Connections

## 6.1 Pin list

I/O Legend: I = Input; O = Output; P = Power; G = Ground; IO = Bi-direction; AI = Analog input; AO = Analog output; AIO = Analog I/O; TRI = Tristate; TOL = Tolerance; PD = Internal 50K pulldown; PU = Internal 50K pull-up; OPENDR = Open drain output

Note: Some pins can have multiple functionalities, which are configured under register control. The alternate functionality for each pin is listed in the Description column.

| Pin | Assignment | I/O             | Description                                                                                                                   | Reset state |

|-----|------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------|-------------|

| D6  | RX0_REXT   | AIO, 3V3<br>TOL | Connect to External 249 Ohm Resistor to VDD33                                                                                 | NA          |

| A5  | RX0_LN0_P  | AIO, 3V3<br>TOL | DUAL MODE RX HDMI CLOCKP OR DP RX_LN0P.                                                                                       | TRISTATE    |

| B5  | RX0_LN0_N  | AIO, 3V3<br>TOL | DUAL MODE RX HDMI CLOCKN OR DP RX_LN0N.                                                                                       | TRISTATE    |

| C4  | RX0_LN1_P  | AIO, 3V3<br>TOL | DUAL MODE RX HDMI RX0P OR DP RX_LN1P.                                                                                         | TRISTATE    |

| C3  | RX0_LN1_N  | AIO, 3V3<br>TOL | DUAL MODE RX HDMI RX0N OR DP RX_LN1N.                                                                                         | TRISTATE    |

| B2  | RX0_LN2_P  | AIO, 3V3<br>TOL | DUAL MODE RX HDMI RX1P OR DP RX_LN2P.                                                                                         | TRISTATE    |

| A2  | RX0_LN2_N  | AIO, 3V3<br>TOL | DUAL MODE RX HDMI RX1N OR DP RX_LN2N.                                                                                         | TRISTATE    |

| B1  | RX0_LN3_P  | AIO, 3V3<br>TOL | DUAL MODE RX HDMI RX2P OR DP RX_LN3P.                                                                                         | TRISTATE    |

| C1  | RX0_LN3_N  | AIO, 3V3<br>TOL | DUAL MODE RX HDMI RX2N OR DP RX_LN3N.                                                                                         | TRISTATE    |

| A6  | RX0_AUX_P  | AIO, 1V2<br>TOL | DUAL MODE RX DP RX_AUXP. AC Couple 0.1uF.<br>Use 20 Ohm damping resistor in series and 1M Ohm<br>pull up to 3.3 V before cap. | TRISTATE    |

| A7  | RX0_AUX_N  | AIO, 1V2<br>TOL | DUAL MODE RX DP RX_AUXN. AC Couple 0.1uF.<br>Use 20 Ohm damping resistor in series and 1M Ohm<br>pull down to GND before cap. | TRISTATE    |

#### Table 12. DisplayPort receiver pins

Note: The default DP and HDMI input signals mapping match the standard DP and HDMI connector pin mapping. However, lane swapping and polarity swapping are possible through software configuration.

Table 13. System function pins

| Pin | Assignment   | I/O                         | Description                                                                           | Reset state               |  |

|-----|--------------|-----------------------------|---------------------------------------------------------------------------------------|---------------------------|--|

| D2  | TEST         | I, 3V3 TOL,<br>INT PD       | Connect to GND                                                                        | INPUT,<br>Internal PD     |  |

| N7  | TCLK         | AIO, 1V2                    | Connect to 27 MHz crystal oscillator with 22 pF to                                    |                           |  |

| N8  | XTAL         | TOL                         | 1.2 V.                                                                                | NA                        |  |

| K1  | TCLK_3V3_OUT | IO, 3V3 TOL                 | TCLK output, Tristate 3.3 V pad                                                       | TRISTATE                  |  |

| L1  | TCLK_1V2_OUT | IO, 1V2 TOL                 | TCLK output, Tristate 1.2 V pad                                                       | TRISTATE                  |  |

| H12 | RESETn       | AIO, 3V3<br>TOL             | Use external 3K ohm resistor to 3.3 V                                                 | TRISTATE,<br>INPUT        |  |

| J3  | SPI_CSN      | IO, 3V3 TOL,<br>TRI, INT PU | To SPI chip select. Also see <i>Table 18: Bootstrap configuration</i> .               | TRISTATE,<br>Internal PU  |  |

| K2  | SPI_DO       | IO, 3V3 TOL,<br>TRI, INT PD | OL, To SPI data out. Also see <i>Table 18: Bootstrap</i><br>PD <i>configuration</i> . |                           |  |

| J1  | SPI_DI       | I, 3V3 TOL,<br>INT PD       | From SPI data in.                                                                     | INPUT with<br>Internal PD |  |

| H3  | SPI_CLK      | IO, 3V3 TOL,<br>TRI, INT PD | To SPI clock. Also see <i>Table 18: Bootstrap</i> configuration.                      | TRISTATE,<br>Internal PD  |  |

### Table 14. Multi-function pins

| Pin | Assignment               | I/O          | Description                                                                                            | Reset state              |

|-----|--------------------------|--------------|--------------------------------------------------------------------------------------------------------|--------------------------|

| E3  | HDMI_CEC                 |              | HDMI CEC not supported in the current silicon<br>rev. Connect this pin to external pull-up<br>DVDD3V3. | TRISTATE                 |