## Filterless and High-Efficiency +4V to +18V Audio Amplifier with Analog Input

#### **Description**

The MA12040 is a super-efficient audio power amplifier based on proprietary multi-level switching technology. It supports a wide supply voltage range, allowing it to be used in many different applications.

Multi-level switching enables very low power loss during operation. In addition, it allows the amplifier to be used in filterless configurations at full rated power in a wide range of audio products.

The MA12040 features an embedded digital power management scheme. The power management algorithm dynamically adjusts switching frequency and modulation to optimize power loss and EMI across the output power range.

A 4<sup>th</sup> order feedback loop ensures low distortion and a high PSRR.

The MA12040 operates from a single power stage supply voltage (PVDD) and a 5V system supply voltage (DVDD, AVDD).

Highly flexible output stage configurations are offered, ranging from four single-ended outputs to a single parallel-BTL output.

The MA12040 features protection against DC, short-circuits, over-temperature and under-voltage situations.

Flexible "Power Mode Profiles" allow the user to utilize the multi-level switching technique for very low power loss or very high audio performance.

Device configuration is controlled through an I2C interface as well as dedicated control pins.

#### **Applications**

- Battery Operated Speakers

- Wireless and Docking Speakers

- Soundbars

- Multiroom Systems

- Home Theater Systems

#### **Features**

- Proprietary Multi-level Switching Technology

- 3-level and 5-level modulation

- Low EMI emission

- Filterless amplification

- Digital Power Management Algorithm

- High Power Efficiency (PMP4)

- <100mW Idle power dissipation (18V PVDD, all channels switching)

- >79% Efficiency at 1W power (1kHz sine, 8Ω)

- >92% Efficiency at Full Power (1kHz sine, 8Ω)

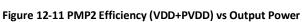

- Audio Performance (PMP2)

- >107dB DNR (A-w, rel. to 1% THD+N power level)

- 55μV output integrated noise (A-w)

- 0.003% THD+N at high output levels

- 4<sup>th</sup> Order Feedback Error Control

- High suppression of supply disturbance

- HD audio quality

- Supply Voltages: +4V to +18V (PVDD) and +5V (A/DVDD)

- Selectable Gain (20dB/26dB)

- 2×40W peak output power (18V PVDD,  $R_L = 4\Omega$ , 10% THD+N level)

- 2×20W continuous output power (RL = 8Ω at 18V, PMP4, 10% THD+N level, without heatsink)

- 2.0, 2.1, 4.0, 1.0 Output Stage Configurations

- Protection

- Under-voltage-lockout

- Over-temperature warning/error

- Short-circuit/overload protection

- Power stage pin-to-pin short-circuit

- Error-reporting through serial interface (I2C)

- DC protection

- I2C control (four selectable addresses)

- Heatsink free operation with EPAD-down package

#### **Package**

- 64-pin QFN Package with exposed thermal pad (EPAD)

- · Lead-free Soldering

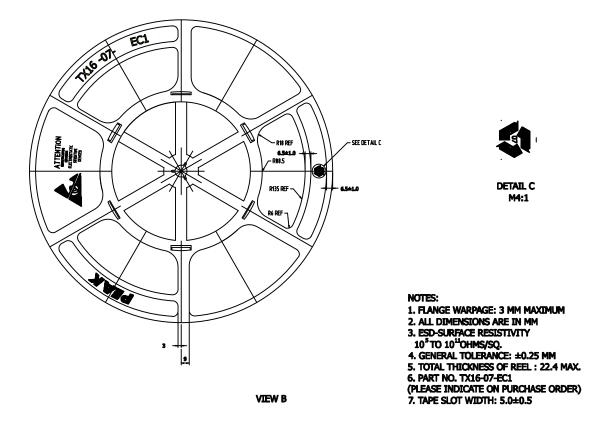

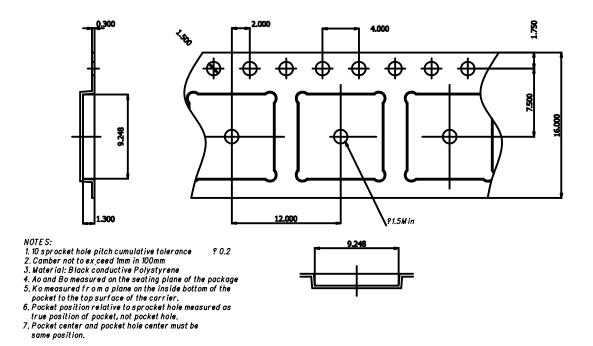

# 1 Ordering Information

#### Table 1-1

| Part Number | Package | Moisture<br>Sensitivity Level | Description                                                                |

|-------------|---------|-------------------------------|----------------------------------------------------------------------------|

| MA12040QFN  | QFN-64  | Level 3                       | Quad Flat No-leads package, EPAD-down (exposed thermal pad on bottom side) |

# 2 Known Issues and Limitations

Please refer to the "MA12040 / MA12040P Known Issues and Limitations" document for descriptions of issues and limitations relating to device operation and performance.

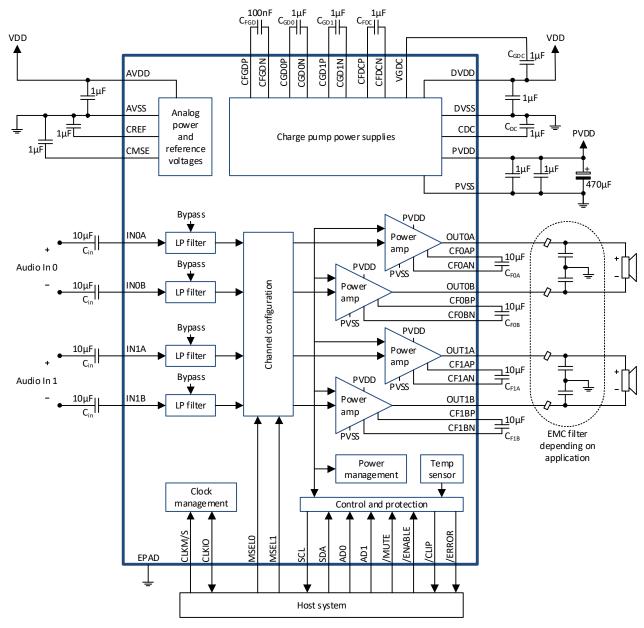

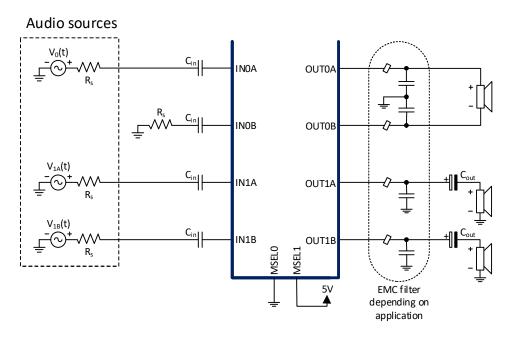

Figure 3-1 Typical application block diagram

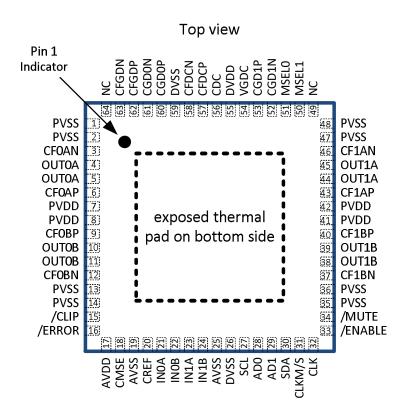

## 4.1 Pinout MA12040QFN

Figure 4-1 Pinout MA12040QFN

## 4.2 Pin Function

Table 4-1

| Table 4-1 |         |                   |                                                                                                                                    |

|-----------|---------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.   | Name    | Type <sup>1</sup> | Description                                                                                                                        |

| 1         | PVSS    | Р                 | Power ground for internal power amplifiers                                                                                         |

| 2         | PVSS    | Р                 | Power ground for internal power amplifiers                                                                                         |

| 3         | CF0AN   | Р                 | Connect to external flying capacitor negative terminal for amplifier channel 0A                                                    |

| 4         | OUT0A   | 0                 | Audio power output 0A                                                                                                              |

| 5         | OUT0A   | 0                 | Audio power output 0A                                                                                                              |

| 6         | CF0AP   | Р                 | Connect to external flying capacitor positive terminal for amplifier channel 0A                                                    |

| 7         | PVDD    | Р                 | Power supply for internal power amplifiers                                                                                         |

| 8         | PVDD    | Р                 | Power supply for internal power amplifiers                                                                                         |

| 9         | CF0BP   | Р                 | Connect to external flying capacitor positive terminal for amplifier channel OB                                                    |

| 10        | OUT0B   | 0                 | Audio power output 0B                                                                                                              |

| 11        | OUT0B   | 0                 | Audio power output 0B                                                                                                              |

| 12        | CF0BN   | Р                 | Connect to external flying capacitor negative terminal for amplifier channel 0B                                                    |

| 13        | PVSS    | Р                 | Power ground for internal power amplifiers                                                                                         |

| 14        | PVSS    | Р                 | Power ground for internal power amplifiers                                                                                         |

| 15        | /CLIP   | 0                 | Audio clipping indicator (open drain output), pulled low when clipping occurs                                                      |

| 16        | /ERROR  | 0                 | Error indicator (open drain output), pulled low when an error occurs                                                               |

| 17        | AVDD    | Р                 | Power supply for internal analog circuitry                                                                                         |

| 18        | CMSE    | 0                 | Decoupling pin for internally generated common-mode voltage in SE configuration. Should be externally decoupled to AVSS.           |

| 19        | AVSS    | Р                 | Ground for internal analog circuitry                                                                                               |

| 20        | CREF    | 0                 | Decoupling pin for internally generated analog reference voltage. Should be externally decoupled to AVSS.                          |

| 21        | IN0A    | 1                 | Analog audio input 0A                                                                                                              |

| 22        | INOB    | I                 | Analog audio input OB                                                                                                              |

| 23        | IN1A    | I                 | Analog audio input 1A                                                                                                              |

| 24        | IN1B    | I                 | Analog audio input 1B                                                                                                              |

| 25        | AVSS    | Р                 | Ground for internal analog circuitry                                                                                               |

| 26        | DVSS    | Р                 | Ground for internal digital circuitry                                                                                              |

| 27        | SCL     | Ю                 | I2C bus serial clock                                                                                                               |

| 28        | AD0     | I                 | I2C device address select 0 (see "MCU/Serial control interface" section)                                                           |

| 29        | AD1     | I                 | I2C device address select 1 (see "MCU/Serial control interface" section)                                                           |

| 30        | SDA     | Ю                 | I2C bus serial data                                                                                                                |

| 31        | CLKM/S  | I                 | Clock master/slave mode select. When pulled low the device is in clock slave mode.  When pulled high the device is in master mode. |

| 32        | CLKIO   | Ю                 | Clock input when in clock slave mode (CLKM/S is pulled low) or clock output when in master mode (CLKM/S is pulled high)            |

| 33        | /ENABLE | I                 | When pulled high, the device is reset and kept in an inactive state with minimum power consumption.                                |

| 34        | /MUTE   | I                 | Mute audio output when pulled low                                                                                                  |

| 35        | PVSS    | Р                 | Power ground for internal power amplifiers                                                                                         |

| 36        | PVSS    | Р                 | Power ground for internal power amplifiers                                                                                         |

| 37        | CF1BN   | Р                 | Connect to external flying capacitor negative terminal for amplifier channel 1B                                                    |

| 38        | OUT1B   | 0                 | Audio power output 1B                                                                                                              |

| 39        | OUT1B   | 0                 | Audio power output 1B                                                                                                              |

| Pin No. | Name  | Type <sup>1</sup> | Description                                                                                        |

|---------|-------|-------------------|----------------------------------------------------------------------------------------------------|

| 40      | CF1BP | Р                 | Connect to external flying capacitor positive terminal for amplifier channel 1B                    |

| 41      | PVDD  | Р                 | Power supply for power amplifiers                                                                  |

| 42      | PVDD  | Р                 | Power supply for power amplifiers                                                                  |

| 43      | CF1AP | Р                 | Connect to external flying capacitor positive terminal for amplifier channel 1A                    |

| 44      | OUT1A | 0                 | Audio power output 1A                                                                              |

| 45      | OUT1A | 0                 | Audio power output 1A                                                                              |

| 46      | CF1AN | Р                 | Connect to external flying capacitor negative terminal for amplifier channel 1A                    |

| 47      | PVSS  | Р                 | Power ground for internal power amplifiers                                                         |

| 48      | PVSS  | Р                 | Power ground for internal power amplifiers                                                         |

| 49      | NC    | Р                 | Internally connected to DVDD                                                                       |

| 50      | MSEL1 | I                 | SE/BTL/PBTL configuration select 1                                                                 |

| 51      | MSEL0 | I                 | SE/BTL/PBTL configuration select 0                                                                 |

| 52      | CGD1N | Р                 | Connect to external decoupling capacitor negative terminal for internal gate driver power supply 1 |

| 53      | CGD1P | Р                 | Connect to external decoupling capacitor positive terminal for internal gate driver power supply 1 |

| 54      | VGDC  | Р                 | Internally generated virtual ground voltage for digital core. Should be decoupled to DVDD.         |

| 55      | DVDD  | Р                 | Power supply for internal digital circuitry and charge pumps                                       |

| 56      | CDC   | Р                 | Connect to external decoupling capacitor for digital core internal power supply                    |

| 57      | CFDCP | Р                 | Connect to external flying capacitor positive terminal for internal digital core power supply      |

| 58      | CFDCN | Р                 | Connect to external flying capacitor negative terminal for internal digital core power supply      |

| 59      | DVSS  | Р                 | Power ground for internal digital circuitry                                                        |

| 60      | CGD0P | Р                 | Connect to external decoupling capacitor positive terminal for internal gate driver power supply 0 |

| 61      | CGD0N | Р                 | Connect to external decoupling capacitor negative terminal for internal gate driver power supply 0 |

| 62      | CFGDP | Р                 | Connect to external flying capacitor negative terminal for internal gate driver power supplies     |

| 63      | CFGDN | Р                 | Connect to external flying capacitor positive terminal for internal gate driver power supplies     |

| 64      | NC    | Р                 | Internally connected to DVDD                                                                       |

**Type**<sup>1</sup>: P = Power; I = Input; O = Output; IO = Input/Output

# **5 Absolute Maximum Ratings**

Table 5-1

| Parameter                                          | Value        | Unit |

|----------------------------------------------------|--------------|------|

| Power Supplies                                     |              |      |

| Power stage supply voltage, PVDD                   | -0.5 to +20  | V    |

| System supply voltage, DVDD, AVDD                  | -0.5 to +6.0 | V    |

| Input / Output                                     |              |      |

| Analog: IN0A, IN0B, IN1A, IN1B                     | -0.5 to +6.0 | V    |

| Logic: /ENABLE, /MUTE, /ERROR, /CLIP, MSEL0, MSEL1 | -0.5 to +6.0 | V    |

| Clock: CLKIO, CLKM/S                               | -0.5 to +6.0 | V    |

| Interface: SCL, SDA, AD0, AD1                      | -0.5 to +6.0 | V    |

| Output current, Logic and Interface                | 25           | mA   |

| Thermal Conditions                                 |              |      |

| Ambient temperature range, T <sub>A</sub>          | -40 to +85   | °C   |

| Junction temperature range, T <sub>J</sub>         | -40 to +150  | °C   |

| Storage temperature range                          | -65 to +150  | °C   |

| Thermal resistance, Junction-to-Ambient            | 23           | °C/W |

| Thermal resistance, Junction-to-EPAD               | 2.3          | °C/W |

| Lead soldering temperature, 10s                    | +300         | °C   |

| Electrostatic Discharge (ESD)                      |              |      |

| Human body model (HBM)                             | ± 2000       | V    |

| Charged device model (CDM)                         | ± 1000       | V    |

#### PLEASE NOTE:

Device usage beyond the above stated ratings may cause permanent damage to the device. Permanent usage at the above stated ratings may limit device lifetime and result in reduced reliability. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied.

See "Recommended Operation Conditions" for continuous functional ratings.

# **6 Recommended Operating Conditions**

Table 6-1

| Symbol                | Parameter                                                                               | Min  | Тур | Max  | Unit |

|-----------------------|-----------------------------------------------------------------------------------------|------|-----|------|------|

| PVDD                  | Power Stage Power Supply                                                                | 4    |     | 18   | V    |

| DVDD                  | Digital Power Supply                                                                    | 4.75 | 5   | 5.25 | V    |

| AVDD                  | Analog Power Supply                                                                     | 4.75 | 5   | 5.25 | V    |

| V <sub>IH</sub>       | High Level for Logic, Clock, Interface                                                  | 2    |     |      | V    |

| V <sub>IL</sub>       | Low Level for Logic, Clock, Interface                                                   |      |     | 0.8  | V    |

| V <sub>IN_dc</sub>    | DC Offset Level for Analog Inputs                                                       | 1.2  | 2.5 | 3.8  | V    |

| V <sub>IN_ac</sub>    | Audio Signal Level for Analog Inputs                                                    |      | 1.8 |      | Vpp  |

| R <sub>L</sub> (BTL)  | Minimum Load in Bridge-Tied Load Mode                                                   | 3.2  | 4   |      | Ω    |

| R <sub>L</sub> (PBTL) | Minimum Load in Parallel Bridge-Tied Load Mode                                          | 1.6  | 2   |      | Ω    |

| R <sub>L</sub> (SE)   | Minimum Load in Single Ended Mode                                                       | 2.4  | 3   |      | Ω    |

| $\mathbf{L}_{Leq}$    | Minimum required equivalent load inductance per output pin for short circuit protection | 0.5  |     |      | μН   |

| T <sub>A</sub>        | Ambient temperature range                                                               | 0    | +25 | +85  | °C   |

**Note:** Minimum Load resistance was measured in Filterless output condition.

# 7 Electrical and Audio Characteristics

Table 7-1Power Mode Profile = 0; VDD (Analog & Digital) = +5V; PVDD = +18V;  $T_A = 0^{\circ}$ C to +85°C. Typical values are at  $T_A = +25^{\circ}$ C

| Symbol                  | Parameter                                                    | Conditions                                      | Min    | Тур    | Max    | Unit |

|-------------------------|--------------------------------------------------------------|-------------------------------------------------|--------|--------|--------|------|

| P <sub>OUT</sub> (BTL)  | Output Power per channel (peak) Without Heatsink, see Note 1 | THD+N = 10%, RL = $8\Omega$ , f = 1kHz          |        | 20     |        | W    |

|                         |                                                              | THD+N = 10%, RL = $4\Omega$ , f = 1kHz          |        | 40     |        | W    |

|                         |                                                              | THD+N = 1%, RL = $8\Omega$ , f = 1kHz           |        | 15     |        | W    |

|                         |                                                              | THD+N = 1%, RL = $4\Omega$ , f = 1kHz           |        | 30     |        | W    |

|                         | Output Power per channel                                     | RL = $8\Omega$ , f = 1kHz, PVDD = +18V          |        | 20     |        | W    |

|                         | (continuous) Without Heatsink, see Note 2                    | RL = $4\Omega$ , f = 1kHz, PVDD = +13V          |        | 20     |        | W    |

| P <sub>OUT</sub> (PBTL) | Output Power (peak), see Note 1                              | THD+N = 10%, RL = $2\Omega$ , f = 1kHz          |        | 80     |        | W    |

|                         |                                                              | THD+N = 1%, RL = $2\Omega$ , f= 1kHz            |        | 60     |        | W    |

| P <sub>OUT</sub> (SE)   | Output Power per channel (peak), see Note 1                  | THD+N = 10%, RL = $4\Omega$ , f = 1kHz          |        | 10     |        | W    |

|                         |                                                              | THD+N = 10%, RL = $3\Omega$ , f = 1kHz          |        | 14     |        | W    |

|                         |                                                              | THD+N = 1%, RL = $4\Omega$ , f = 1kHz           |        | 8      |        | W    |

|                         |                                                              | THD+N = 1%, RL = $3\Omega$ , f = 1kHz           |        | 11     |        | W    |

| T <sub>ENABLE</sub>     | Shutdown/Full Operation Timing                               | NENABLE = 1 → 0                                 | 1      |        |        | ms   |

| T <sub>MUTE</sub>       | Mute/Unmute Timing                                           | NMUTE = $1 \rightarrow 0$ and $0 \rightarrow 1$ | 0.3    |        |        | ms   |

| _                       | Input Impedance per output                                   | High gain mode                                  |        | 14     |        | kΩ   |

| R <sub>IN</sub>         | channel                                                      | Low gain mode                                   |        | 21     |        | kΩ   |

| Vos                     | Output Offset Voltage                                        | Low gain                                        |        |        | ±60    | mV   |

| PSRR                    | Power Supply Rejection Ratio                                 | ± 100mVpp ripple voltage                        |        | 70     |        | dB   |

| CMRR                    | Common-Mode Rejection Ratio                                  | 1kHz common-mode input                          |        | 94     |        | dB   |

| Ron                     | Resistance, switch on                                        |                                                 | 0.10   | 0.15   | 0.20   | Ω    |

|                         |                                                              | Power Mode A                                    | 618    | 672    | 726    | kHz  |

| f <sub>sw</sub>         | Power MOSFET Switching<br>Frequency, see Note 3              | Power Mode B & C                                | 316    | 336    | 356    | kHz  |

|                         | rrequeriey, see Note s                                       | Power Mode D                                    | 158    | 168    | 178    | kHz  |

| f <sub>CLK_IO</sub>     | Clock Output Frequency                                       |                                                 | 2.7151 | 2.8224 | 2.9296 | MHz  |

| _                       |                                                              | Low gain                                        | 19     | 19.6   | 21     | dB   |

| $A_V$                   | Gain                                                         | High gain                                       | 25     | 25.3   | 27     | dB   |

| I <sub>OUT</sub>        | Maximum Output Current                                       |                                                 | 6      |        |        | А    |

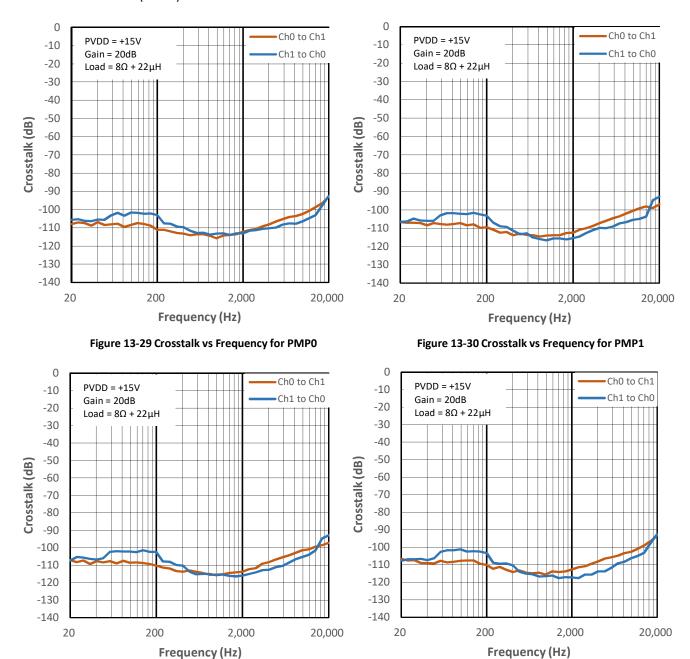

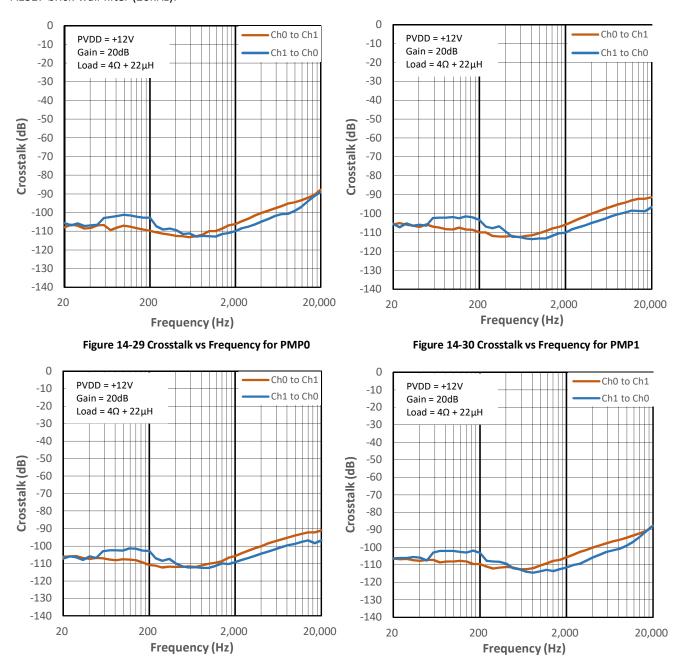

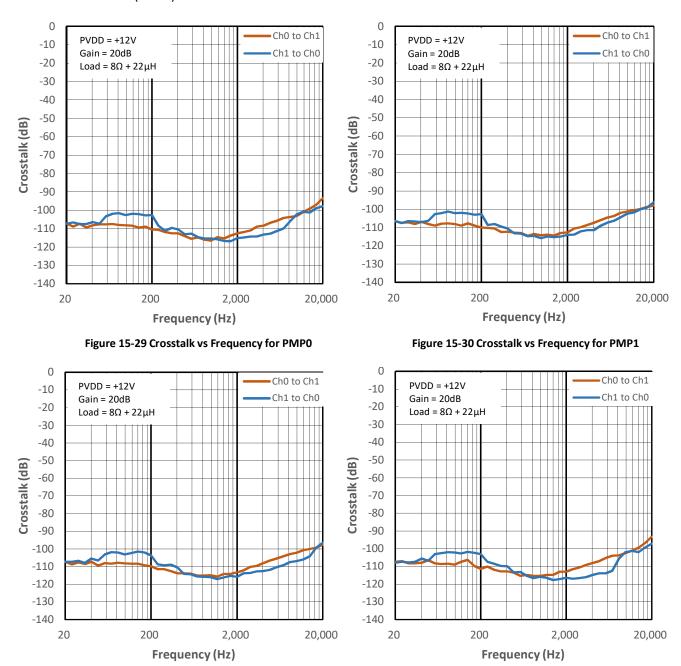

| X <sub>Talk</sub>       | Crosstalk                                                    | BTL, POUT = 1W, f=1kHz, Ch1 & 2                 |        | -110   |        | dB   |

**Note 1:** The thermal design of the target application will significantly impact the ability to achieve the peak output power levels for extended time. See "Thermal Characteristics and Test Signals" section for thermal optimization recommendations.

**Note 2:** Continuous power measurements were performed on the MA12040/MA12040P proprietary Amplifier EVK without heatsinking at 25°C ambient temperature in Power Mode Profile 4.

**Note 3:** Power MOSFET switching frequency depends on which properties are assigned to the individual power modes of the device. Detailed information on this can be found in "Power Mode Management" section.

Table 7-2 VDD (Analog & Digital) = +5V; PVDD = +18V; Typical values are at  $T_A$  = +25°C; Output Configuration: BTL

| Symbol | Parameter  | Conditions                                    | Min | Тур | Max | Unit |

|--------|------------|-----------------------------------------------|-----|-----|-----|------|

| η      | Efficiency | POUT = $2\times20W$ , $8\Omega$ , PMP = $0$   |     | 91  |     | %    |

|        |            | POUT = $2 \times 20W$ , $8\Omega$ , PMP = $1$ |     | 91  |     | %    |

|        |            | POUT = $2\times20W$ , $8\Omega$ , PMP = $2$   |     | 90  |     | %    |

|        |            | POUT = $2\times20W$ , $8\Omega$ , PMP = $4$   |     | 92  |     | %    |

|        |            | POUT = $2\times40W$ , $4\Omega$ , PMP = $0$   |     | 87  |     | %    |

|        |            | POUT = $2\times40W$ , $4\Omega$ , PMP = $1$   |     | 87  |     | %    |

|        |            | POUT = $2\times40W$ , $4\Omega$ , PMP = $2$   |     | 86  |     | %    |

|        |            | POUT = $2\times40W$ , $4\Omega$ , PMP = $4$   |     | 88  |     | %    |

Table 7-3Power Mode Profile = 0; VDD (Analog & Digital) = +5V; PVDD = +18V;  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$

| Symbol                   | Parameter                         | Conditions                        | Min | Тур   | Max | Unit  |

|--------------------------|-----------------------------------|-----------------------------------|-----|-------|-----|-------|

| I <sub>shutdown</sub>    | Current Consumption, PVDD         | Shutdown                          | 10  | 35    | 180 | μΑ    |

| l <sub>idle,mute</sub>   | Current Consumption, PVDD         | Idle, mute                        | 4   | 5.5   | 8   | mA    |

| l <sub>idle,unmute</sub> | Current Consumption, PVDD         | Idle, unmute, inputs grounded     | 4   | 6     | 12  | mA    |

| I <sub>AVDD+DVDD</sub>   | Current Consumption, AVDD+DVDD    | Idle, unmute, inputs grounded     | 25  | 30    | 37  | mA    |

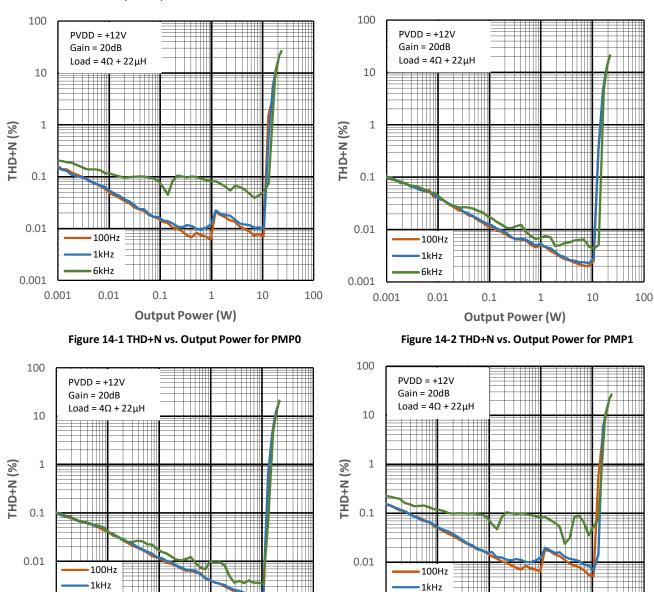

| TUDAN                    | Tabal Haymania Distantian - Naisa | 1kHz, POUT = 1W, RL = $4\Omega$   |     | 0.008 |     | %     |

| THD+N                    | Total Harmonic Distortion + Noise | 1kHz, POUT = 20W, RL = $4\Omega$  |     | 0.010 |     | %     |

| DND                      | Dimensia Denna 1                  | 20-20kHz, A-weighted, Gain = low  |     | 105   |     | dB    |

| DNR                      | Dynamic Range <sup>1</sup>        | 20-20kHz, A-weighted, Gain = high |     | 102   |     | dB    |

| .,                       | Outside and desire level          | 20-20kHz, A-weighted, Gain = low  | 30  | 65    | 110 | μVrms |

| V <sub>noise</sub>       | Output integrated noise level     | 20-20kHz, A-weighted, Gain = high | 60  | 90    | 120 | μVrms |

**Table 7-4**Power Mode Profile = 2; VDD (Analog & Digital) = +5V; PVDD = +18V;  $T_A = 0^{\circ}\text{C}$  to +85°C. Typical values are at  $T_A = +25^{\circ}\text{C}$

| Symbol                   | Parameter                          | Conditions                        | Min | Тур   | Max | Unit  |

|--------------------------|------------------------------------|-----------------------------------|-----|-------|-----|-------|

| I <sub>shutdown</sub>    | Current Consumption, PVDD          | Shutdown                          | 10  | 35    | 180 | μΑ    |

| l <sub>idle,mute</sub>   | Current Consumption, PVDD          | Idle, mute                        | 4   | 5.5   | 8   | mA    |

| l <sub>idle,unmute</sub> | Current Consumption, PVDD          | Idle, unmute, inputs grounded     | 4   | 8     | 14  | mA    |

| I <sub>AVDD+DVDD</sub>   | Current Consumption, AVDD+DVDD     | Idle, unmute, inputs grounded     | 28  | 33    | 40  | mA    |

| TUDAN                    | Tatal Hamasania Diatantian I Naisa | 1kHz, POUT = 1W, RL = $4\Omega$   |     | 0.004 |     | %     |

| THD+N                    | Total Harmonic Distortion + Noise  | 1kHz, POUT = 20W, RL = $4\Omega$  |     | 0.003 |     | %     |

| DAID                     | Domanda Banasi                     | 20-20kHz, A-weighted, Gain = low  |     | 107   |     | dB    |

| DNR                      | Dynamic Range <sup>1</sup>         | 20-20kHz, A-weighted, Gain = high |     | 103   |     | dB    |

| .,                       | Output into material maior level   | 20-20kHz, A-weighted, Gain = low  | 30  | 55    | 85  | μVrms |

| V <sub>noise</sub>       | Output integrated noise level      | 20-20kHz, A-weighted, Gain = high | 60  | 80    | 105 | μVrms |

|                          |                                    |                                   |     |       |     |       |

Dynamic Range $^1$ : Output power at THD+N < 1% reference to noise floor at -60dBFS signal.

**NOTE**: MA12040 gives users the freedom to choose Power Mode Profiles (PMP) independently. As noted in the specifications table, the choice in power mode profiles gives a trade-off between power efficiency and audio performance as an individual set of performance characteristics. See "Power Mode Profiles" section for more details.

## 8 Functional description

## **Multi-level modulation**

The power stage of the MA12040 is a true multi-level switching topology. Each half-bridge is capable of delivering a PWM output with three voltage levels, rather than the conventional two. The three-level half-bridges are each driven with a two-phase PWM signal, so that the switching frequency seen at the PWM output is twice that of the individual power MOSFET switching frequency.

For very low EMI in BTL configuration, the two half-bridges are operated in a complementary fashion (i.e. with 180° phase shift), which removes common-mode PWM output content. This configuration is ideal for driving long speaker cables without an output filter. Differentially, this modulation method drives the filter/load assembly with three PWM levels.

For reduced power loss in the BTL configuration, the half-bridges can also be driven in a quadrature phase shifted fashion (i.e. with 90° phase shift). It provides five PWM levels at the load, along with a quadrupling of MOSFET switching frequency with respect to the differential PWM switching frequency. With this modulation scheme, the MOSFET switching frequency can therefore be lowered, in order to decrease switching losses. The five-level modulation scheme produces a common-mode voltage on the load wires, but with less high-frequency content compared to conventional two-level BD modulation.

The multi-level switching topology of the MA12040 makes filterless operation viable, since the modulation schemes ensure little or no idle losses in the speaker magnetic system.

For applications with stringent EMC requirements or long speaker cables, the MA12040 can operate with a very small and inexpensive EMI/EMC output filter. This can be enabled by multiple PWM output levels and the frequency multiplication seen on the PWM switching nodes. Notably, with the multi-level modulation of the MA12040, there is no tradeoff between idle power loss and inductor cost/size, which is due to the absence of inductor ripple current under idle conditions in all configurations. Due to the high filter cutoff frequency, non-linearities of LC components have less impact on audio performance than with a conventional amplifier. Therefore, the MA12040 can operate with inexpensive iron-powder cored inductors and ceramic (X7R) filter capacitors with no significant audio performance penalty.

#### Very low power consumption

The MA12040 achieves very low power loss under idle and near-idle operating conditions. This is due to the zero idle ripple property of the multi-level PWM scheme, in combination with the programmable automatic reduction of switching frequency at low modulation index levels; resulting in a state-of-the-art power efficiency at low and medium output power levels.

For high output power levels, power efficiency is determined primarily by the on-resistance (Rdson) of the output power MOSFETs. With music and music-like (e.g. pink noise) output signals with high crest factor, the reduced near-idle losses of the MA12040 contribute to reducing power losses compared to a conventional amplifier with the same Rdson. In most applications, this allows the MA12040 to run at high power levels without a heatsink.

#### **Power Mode Management**

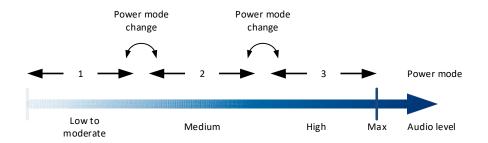

The MA12040 is equipped with an intelligent power management algorithm which applies automatic power mode selection during audio playback. In this state, the amplifier will seamlessly transition between three different power modes depending on the audio level in order to achieve optimal performance in terms of power loss, audio performance and EMI. These transitions will not give rise to any audible artifacts. Figure 8-1 shows an illustration of the basic power mode management. Alternatively, it is possible to manually select the desired power mode for the MA12040 via the serial interface.

In both manual and automatic power mode selection, the power mode can be configured and set on-the-fly during audio playback, with no audible artifacts. This makes it possible to optimize the target application to achieve the best possible operating performance at all audio power levels.

During automatic power mode selection, the MA12040 can transition between power modes at programmable audio level thresholds. The thresholds can be set via the serial control interface, by addressing the associated registers.

Figure 8-1 Illustration of automatic power mode selection ranges

To allow easy use of the power mode management, "Power Mode Profiles" have been defined. The "Power Mode Profiles" address the appropriate power modes for a variety of applications.

#### **Power Modes Profiles**

The MA12040 provides 5 different power mode profiles for operating the internal power amplifiers. The power mode profiles give the user freedom to choose optimal settings of the amplifier for the intended application. The available power modes profiles are referred to as 0, 1, 2, 3 and 4 and can be set by programming the according register (see Register Map). The power mode profile selection affects various parameters such as switching frequency, modulation scheme and loop-gain, thus providing flexibility in design tradeoffs such as audio performance, power loss and EMI. The details of each power mode profiles are described in Table 8-1.

**Table 8-1 Power Mode Profile characteristics**

| Property                               | Profile 0                                                       | Profile 1                                                                        | Profile 2                                                                 | Profile 3                                                                                 | Profile 4                                                                 |

|----------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| PM switch seq.                         | $D \leftrightarrow D \leftrightarrow C$                         | B↔B↔B                                                                            | B↔B↔A                                                                     | D↔B↔A                                                                                     | $D \longleftrightarrow D \longleftrightarrow D$                           |

| Idle loss                              | Very low                                                        | Low                                                                              | Low                                                                       | Very low                                                                                  | Very low                                                                  |

| Full scale efficiency                  | Good                                                            | Good                                                                             | Good                                                                      | Normal                                                                                    | Best                                                                      |

| THD+N                                  | Good                                                            | Best                                                                             | Best                                                                      | Good/Best                                                                                 | Good                                                                      |

| Common-mode content, idle              | Only DC                                                         | Only DC                                                                          | Only DC                                                                   | Only DC                                                                                   | Only DC                                                                   |

| Common-mode content, full-scale audio  | Only DC                                                         | DC + Sidebands<br>around 660kHz,<br>1.98MHz, 3.3MHz                              | Only DC                                                                   | Only DC                                                                                   | DC + sidebands<br>around 330kHz,<br>990kHz, 1.65MHz                       |

| Differential content low-to-mid-power  | Audio + sidebands<br>around multiples<br>of 1.2MHz              | Audio + sidebands<br>around multiples<br>of 1.32MHz                              | Audio + sidebands<br>around multiples<br>of 1.32MHz                       | Audio + sidebands<br>around multiples<br>of 660kHz                                        | Audio + sidebands<br>around multiples<br>of 660kHz                        |

| Differential content mid-to-high power | Audio + sidebands<br>around multiples<br>of 600kHz              | Audio + sidebands<br>around multiples<br>of 1.32MHz                              | Audio + sidebands<br>around multiples<br>of 1.32MHz                       | Audio + sidebands<br>around multiples<br>of 1.32MHz                                       | Audio + sidebands<br>around multiples<br>of 660kHz                        |

| Application                            | Filterfree:<br>optimized<br>efficiency, default<br>applications | Filterfree:<br>optimized audio<br>performance,<br>active speaker<br>applications | Filterfree:<br>optimized audio<br>performance,<br>default<br>applications | LC filter: high<br>efficiency, high<br>audio<br>performance, good<br>EMI, low ripple loss | Filterfree:<br>optimized<br>efficiency, active<br>speaker<br>applications |

Note: There is a programmable "Profile 5" which allows the user to set up a custom profile.

The first row of Table 8-1 shows that each Power Mode Profile follows a certain Power Mode transition sequence. This means that each Power Mode within every Power Mode Profile will have its specific set of properties (A,B,C or D). The exact details of each assigned set of properties is reflected in Table 8-2.

Table 8-2 Set of properties assigned to Power Modes in the selectable Power Mode Profiles

| Property                                          | Α                                                   | В                                                   | С                                                  | D                                                   |

|---------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|----------------------------------------------------|-----------------------------------------------------|

| FET switching frequency, f <sub>FET</sub>         | 660kHz                                              | 330kHz                                              | 330kHz                                             | 165kHz                                              |

| Modulation scheme                                 | 3-level                                             | 5-level                                             | 3-level                                            | 5-level                                             |

| Switching frequency seen at load, f <sub>sw</sub> | 1.32MHz (2 x f <sub>FET</sub> )                     | 1.32MHz (4 x f <sub>FET</sub> )                     | 660kHz (2 x f <sub>FET</sub> )                     | 660kHz (4 x f <sub>гет</sub> )                      |

| Idle loss                                         | Reduced                                             | Low                                                 | Low                                                | Very low                                            |

| Full scale efficiency                             | Normal                                              | Good                                                | Good                                               | Best                                                |

| Open-loop gain                                    | High                                                | High                                                | Low                                                | Low                                                 |

| THD+N                                             | Best                                                | Best                                                | Good                                               | Good                                                |

| Common-mode content, idle                         | Only DC                                             | Only DC                                             | Only DC                                            | Only DC                                             |

| Common-mode<br>content, full-scale<br>audio       | Only DC                                             | DC + sidebands around<br>660kHz, 1.98MHz,<br>3.3MHz | Only DC                                            | DC + sidebands around<br>330kHz, 990kHz,<br>1.65MHz |

| Differential content                              | Audio + sidebands<br>around multiples of<br>1.32MHz | Audio + sidebands<br>around multiples of<br>1.32MHz | Audio + sidebands<br>around multiples of<br>660kHz | Audio + sidebands<br>around multiples of<br>660kHz  |

Next to the pre-defined Power Mode Profiles it is also possible to define a custom profile which will be available under Power Mode Profile 5. This profile can be configured using the "custom power mode profile" register (address 30). See "Register Map" section for more details.

The MA12040 employs feedback of the output PWM signals in order to compensate for noise and other non-idealities in the power processing path. A fourth-order analog feedback loop is used, which typically provides a loop gain of 60dB to suppress errors in the audio band. For the typical high efficiency application this results in low THD (Total Harmonic Distortion) at all audio frequencies, as well as excellent immunity (in excess of 80dB) to power supply borne interferences. See also PSRR in Table 7-1.

Maximum achievable loop-gain is typically set by the PWM frequency stability criteria. Inherent frequency multiplication of the multilevel topology therefore allows for a much more aggressive loop-filter (and therefore better THD and noise properties) because of a higher effective PWM switching frequency seen at the output. See "Profile 1 and Profile 2" in Table 8-1 for high-fidelity Power Mode Profiles.

For the lowest switching frequencies, the proprietary loop filter architecture seamlessly reduces feedback bandwidth to ensure loop stability. In most applications (e.g. filterless applications), no further special attention is required to ensure loop stability. In applications with very stringent EMI requirements, an LC filter can be used. In these cases attention to loop stability is required since an un-damped LC filter effectively represents a short-circuit to ground at the resonance frequency. In extreme cases, this can cause instability of the analog feedback loops. In order to avoid this, an LC filter should use an inductor with more than  $10m\Omega$  DC resistance, and a series R-C circuit should be used to limit the Q of the LC circuit to around 5.

#### **Power supplies**

The MA12040 generates internal supply voltages and uses external capacitors for this purpose and for decoupling.

## **Gate driver supplies**

The MA12040 utilizes a floating supply voltage for the gate driver circuitry generated internally by a charge pump. The gate driver on power supply voltage is approximately 6V to 9V higher than PVDD. Table 8-3 shows the required external charge pump and decoupling capacitors.

**Table 8-3 Gate driver supply capacitors**

| Name             | Purpose                                    | Connection   | Туре                              | Value |

|------------------|--------------------------------------------|--------------|-----------------------------------|-------|

| C <sub>GD0</sub> | Decoupling of gate driver supply voltage 0 | CGD0P, CGD0N | 16V, high capacity, low precision | 1uF   |

| $C_{GD1}$        | Decoupling of gate driver supply voltage 1 | CGD1P, CGD1N | 16V, high capacity, low precision | 1uF   |

| $C_{\text{FGD}}$ | Charge pump flying capacitor               | CFGDP, CFGDN | 50V, high capacity, low precision | 100nF |

## **Digital core supply**

The digital control unit in the MA12040 uses a supply voltage generated internally by a charge pump and a voltage regulator for highest efficiency. Table 8-4 lists the external capacitors required and describes their function and connection.

**Table 8-4 Digital supply capacitors**

| Name             | Purpose                                                                                                                                                | Connection   | Туре                                 | Value |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------|-------|

| C <sub>DC</sub>  | Charge pump output voltage decoupling to GND                                                                                                           | CDC, GND     | >=6.3V, high capacity, low precision | 1uF   |

| $C_{FDC}$        | Charge pump flying capacitor                                                                                                                           | CFDCP, CFDCN | >=6.3V, high capacity, low precision | 1uF   |

| C <sub>GDC</sub> | Decoupling of digital core virtual ground voltage<br>on the VGDC pin. The voltage on the VGDC pin is<br>approximately 1.8V below DVDD, i.e. about 3.2V | VGDC, DVDD   | >=6.3V, high capacity, low precision | 1uF   |

#### Flying capacitors

The MA12040 power stage uses flying capacitors to generate a ½PVDD supply voltage to enable multi-level operation. Each output switch node OUTXX has a corresponding flying capacitor, with a positive and a negative terminal, CFXXP and CFXXN.

The two flying capacitor terminals are to be considered high power switching nodes carrying voltages and currents similar to that on the OUTXX nodes. Care must be taken in the PCB design to reduce both the inductance and the resistance of these nodes. Table 8-5 lists the flying capacitors, incl. connection, type and value.

**Table 8-5 Flying capacitors**

| Name             | Purpose                         | Connection   | Туре                                | Value |

|------------------|---------------------------------|--------------|-------------------------------------|-------|

| C <sub>FOA</sub> | Half-bridge OA flying capacitor | CFOAP, CFOAN | >=25V, high capacity, low precision | 10uF  |

| C <sub>FOB</sub> | Half-bridge OB flying capacitor | CFOBP, CFOBN | >=25V, high capacity, low precision | 10uF  |

| C <sub>F1A</sub> | Half-bridge 1A flying capacitor | CF1AP, CF1AN | >=25V, high capacity, low precision | 10uF  |

| C <sub>F1B</sub> | Half-bridge 1B flying capacitor | CF1BP, CF1BN | >=25V, high capacity, low precision | 10uF  |

Care must be taken when choosing flying capacitors in applications where maximum output power is needed. The effective capacitance of poor ceramic capacitors can be greatly reduced when a DC bias voltage is applied. A recommended part is the GRM21BZ71E106KE15L capacitor from Murata. Other parts may also be used as long as the effective capacitance is minimum 3.0  $\mu$ F at 0.5\*PVDD voltage.

#### **Protection**

The MA12040 integrates a range of protection features to protect the device and attached speakers from damage. Protection features include:

- Current protection on OUTXX nodes during operation.

- Pin-to-pin low impedance detection on OUTXX, CFXXP and CFXXN switching nodes. Prevents the device from starting to switch into a shorted output.

- On-chip temperature sensor for protection against device over-heating.

- Undervoltage supply monitors on AVDD, DVDD, VGDC and PVDD.

- DC protection, preventing DC to be present on the amplifier outputs.

#### **Over-current protection on OUTXX nodes**

During switching operation the output stage monitors the forward current flow in all output switches that are turned on. This is done to limit the maximum power dissipated in the switches and prevent damage to the device and the speaker load. The current in the output stage can exceed unwanted levels if:

- The speaker load impedance drops to a low value while the device is powered from a high PVDD supply.

- A failure occurs on the speaker terminals causing a low impedance short.

- The speaker is damaged and thereby exhibiting a low impedance.

Over-current protection and short-circuit protection use a latching mechanism. If an over current or a short-circuit condition occurs, it will shut down the power stage and report the error on the /ERROR pin. By default the device will restart. Current limiting will not occur for currents below the OCE<sub>THR</sub> level, see Table 7-1.

Current protection against speaker terminal shorts requires an equivalent load inductance L<sub>Leq</sub> on each of the output OUTXX pins (see Table 6-1). Load inductance from loudspeaker cables and, if used, ferrite beads (EMC filter) will typically be sufficient.

#### **Temperature protection**

An on-chip temperature sensor effectively safeguards the device against a thermally induced failure due to overloading and/or insufficient cooling.

A high junction temperature initially causes a temperature warning, TW. This can be detected by reading the error register (address 124, bit 4) via I2C. If the temperature continues to rise the device will reach the temperature error (TE) level and set the TE bit in the error register (address 124, bit 5). This will cause the device to stop all switching activity. The device will restart after sufficient cooling down of the system. Both TW and TE will report the error on the /ERROR pin.

**Table 8-6 High-Temperature Warning and Error Signaling Levels**

| Name                  | Parameter                                     | Test Conditions     | Typical Value | Unit |

|-----------------------|-----------------------------------------------|---------------------|---------------|------|

| TE <sub>THR,SET</sub> | High-Temperature Error (TE) Set Threshold     | Temperature rising  | 150           | °C   |

| TE <sub>THR,CLR</sub> | High-Temperature Error (TE) Clear Threshold   | Temperature falling | 135           | °C   |

| TW <sub>THR,SET</sub> | High-Temperature Warning (TW) Set Threshold   | Temperature rising  | 125           | °C   |

| TW <sub>THR,CLR</sub> | High-Temperature Warning (TW) Clear Threshold | Temperature falling | 105           | °C   |

## **Power supply monitors**

The MA12040 features integrated PVDD, DVDD and AVDD under-voltage lockout. Table 8-7 shows typical limits for the supply monitors.

Table 8-7 Under-voltage lockout levels.

| Name                | Parameter                          | Test Conditions | Typical Value | Unit |

|---------------------|------------------------------------|-----------------|---------------|------|

| UVP <sub>DVDD</sub> | DVDD under-voltage error threshold | DVDD Rising     | 4.2           | V    |

|                     |                                    | DVDD Falling    | 4.0           | V    |

| UVP <sub>AVDD</sub> | AVDD under-voltage error threshold | AVDD Rising     | 4.2           | V    |

|                     |                                    | AVDD Falling    | 4.0           | V    |

| UVP <sub>PVDD</sub> | PVDD under-voltage error threshold | PVDD Rising     | 4.3           | V    |

|                     |                                    | PVDD Falling    | 4.1           | V    |

## **DC** protection

The MA12040 incorporates a circuit, detecting whether a DC is present on the amplifier output terminals driving the loudspeaker. In case of an unexpected DC being present on any of the amplifier outputs, the power stage will be shut down to protect the loudspeaker from harmful DC content. Furthermore, a failure is reported on the /ERROR pin and in the error register readable by the device serial interface. The power stage can be restarted by resetting the device by cycling the /ENABLE pin or toggle the eh\_clear bit (bit 2, address 45) to clear the error register. DC protection is default on. It can be disabled by clearing bit 2 of Eh dcShdn (address 0x26).

For the DC protection circuit to trigger, the DC value of an output pin must be staying above 0.63\*PVDD or below 0.37\*PVDD for more than 700ms.

## **Clock system**

The MA12040 incorporates a clock system consisting of an input clock divider and PLL, a low-jitter low-TC oscillator (2.8224 MHz) and control logic.

The input clock frequency is auto-detected by the input clock divider and the corresponding divider ratio is selected as a function of the input frequency and the internal oscillator frequency. The correct PLL reference clock is generated from this. The internal PLL divider ratio is also selected as a function of the master clock base frequency (2.8224 or 3.072 MHz).

The MA12040 accepts input master clock frequencies that are 1, 2, 4 or 8 times the base frequency.

This clock system automatically handles clock errors and master clock frequency changes without requiring an external system controller, thereby significantly reducing the overall system complexity.

The MA12040 can operate in two clock modes:

- Master-mode (CLKM/S=1): In this mode the MA12040 uses the internal oscillator as a reference for the internal PLL. The internal master clock is accessible via the CLKIO pin and can be distributed to other MA12040 ICs operating in slave-mode.

- 2. Slave-mode (CLKM/S=0): In this clock mode, the input master clock (via the CLKIO pin) provides the reference for the internal PLL through the input clock divider circuit. In slave-mode the MA12040 accepts input master clock frequencies in the range specified above.

## **Clock synchronization**

In the situation where multiple MA12040 devices are going to be used in one system it is advisable to use one MA12040 in master mode and the other MA12040 devices in slave mode. This way the mutual PWM switching frequencies are synchronized which minimizes cross-coupling between devices that could cause inter-modulated audio-in-band tones.

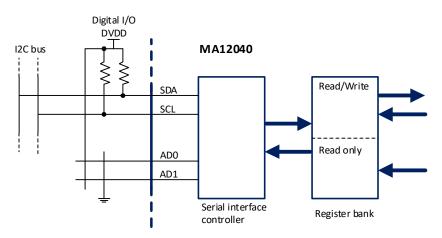

## MCU/Serial control interface

The I2C serial control interface of the MA12040 allows an I2C master to read and/or modify a wide range of device parameters.

The I2C interface consists of four physical pins, SDA, SCL, ADO and AD1. I2C decoder logic handles transaction protocol and read/write access to the device register bank. SDA and SCL are standard bidirectional I2C slave pins for data and clock, respectively. Both SDA and SCL must be pulled-up to a digital I/O (3.3V - 5V) with a 5k resistor on each pin and operated in standard I2C mode up to 100 kbps transmission rate. Pins ADO and AD1 are used to configure the 7-bit I2C address of the device. The I2C address is decoded according to Table 8-8.

| I2C device address | AD1 pin | AD0 pin | 7-bit I2C address |

|--------------------|---------|---------|-------------------|

| 0x20               | 0       | 0       | 0b0100000         |

| 0x21               | 0       | 1       | 0b0100001         |

| 0x22               | 1       | 0       | 0b0100010         |

| 0x23               | 1       | 1       | 0b0100011         |

Table 8-8 I2C address decoding

The I2C interface enables read/write operations to the device register bank. The register bank is organized as a 128 entry, byte wide memory, holding device configuration and status registers. The address space from 0 to 80 holds read/write registers and the address space from 96 to 127 are read only. The complete address map and description of each register is presented in "Register Map" section. Figure 8-2 shows the block schematic of the I2C interface between: I2C bus and MA12040 (serial interface controller and the register bank).

Figure 8-2. I2C bus interface and register bank

## **I2C** write operation

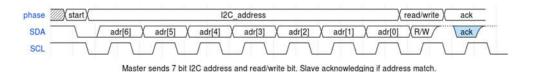

Each I2C transaction is initiated from a master by sending an I2C start condition followed by the 7-bit I2C device address and cleared read/write bit. The device address and read/write bit is signaled on the SDA bus by pulling the bus to ground indicating a '0' or releasing the bus to indicate a '1'. The I2C SDA input is sampled by the device on the rising edge of the SCL bus.

If the transmitted I2C address matches the configured address of the device, the device will acknowledge the request by pulling the SDA bus to ground. The master samples the acknowledged bit from the device on the next rising edge of SCL. The I2C initialization as described is shown in the waveform in Figure 8-3.

Figure 8-3. I2C init addressing sequence

To complete the device register write operation, the master must continue transmitting the address and at least one data byte. The device continues to acknowledge each byte received on the 9<sup>th</sup> SCL rising edge. Each additional data written to the device is written to the next address in the register bank.

The write transaction is terminated when the master sends a stop signal to the device. The stop signal consists of a rising edge on SDA during SCL kept high. Figure 8-4 shows a single write operation.

Figure 8-4 I2C write operation

#### **I2C** read operation

To read data from the device register bank, the read transaction is started by sending a write command to the I2C address with the R/W bit cleared, followed by the device address to read from. See Figure 8-5.

Figure 8-5 I2C read transaction, register bank to be read from is written to the device

The device will acknowledge the two bytes. Then data can be fetched from the device by sending a repeated start, followed by an I2C read command consisting of a byte with the device I2C address and the R/W bit set.

The device will acknowledge the read request and start to drive the SDA bus with the bits from the requested register bank address. See Figure 8-6.

Figure 8-6 I2C read transaction last part

The read transaction continues until the master does not acknowledge the 9<sup>th</sup> bit of the data read byte transaction and sends a stop signal. The stop condition is defined as a rising edge of SDA while SCL is high.

Table 8-9 I2C timing requirements

| Parameter                    | Min | Тур | Max | Unit |

|------------------------------|-----|-----|-----|------|

| Clock frequency <sup>1</sup> | 0   | 100 | 400 | kHz  |

| SDA and SCL rise time        |     |     | 1   | μs   |

| SDA and SCL fall time        |     |     | 1   | μs   |

| SCL clock high               | 1   |     |     | μs   |

| SCL clock low                | 1   |     |     | μs   |

| Data, setup                  | 300 |     |     | ns   |

| Data, hold                   | 10  |     |     | ns   |

| Min stop to start condition  | 1   |     |     | μs   |

NOTE<sup>1</sup>: Pull up resistance is equal to  $2.2k\Omega$  for 400kHz.

## /CLIP pin and soft-clipping

The /CLIP pin changes from a HIGH state to LOW state when audio output is close to clipping. A system microcontroller can at this instance decrease volume level or, if possible, increase power stage voltage in order to avoid clipping. The associated modulation index for both channel 0 and channel 1 can be read out by reading address 98 and address 102 respectively. Note that /CLIP pin is an open-drain output which means that it should be pulled-up through a pull-up resistor to the digital I/O DVDD of the system.

To minimize possible audible artifacts from sticky clipping or ringing around the clipping region, it is possible to enable a soft-clipping scheme. This clipping scheme prevents the amplifier to sticky clip and minimizes ringing which subsequently minimizes possible audible artifacts apart from normal clipping audibility. The soft-clipping scheme can be enabled by setting bit 7 of address 10.

#### /ERROR pin and error handling

The /ERROR pin changes from a HIGH state to a LOW state when one of the associated error sources is triggered. A system microcontroller can at this instance read out the error registers (address 45 and 109). According to the type of error or warning the right measures can be taken. The errors will be shown in the error register (address 124) which shows the live status of the error sources. Another register error\_acc (address 109) will contain all the errors accumulated over time. The error\_acc register can be cleared by toggling the eh\_clear bit (bit 2, address 45).

Table 8-10 shows the content of the error vector which is mapped to both the error register and the accumulated error register. A more detailed explanation can be found in "Register Map" section.

**Table 8-10 Error vector**

| Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|

| dc_prot | pps   | ote   | otw   | uvp   | pll   | оср   | fcov  |

Note that the /ERROR pin has an open-drain output and should be pulled up to the interface I/O rail.

## 9 Application Information

## **Input/Output Configurations**

The MA12040 is highly flexible regarding configuration of the four power amplifier channels. MA12040 can be set to four different output configurations. By setting the configuration pins MSEL0 and MSEL1 according to Table 9-1, the device is configured to one of the four different configurations. Each configuration is individually described in the following sections.

| MSEL0 pin | MSEL1 pin | Configuration                                                          |

|-----------|-----------|------------------------------------------------------------------------|

| 0         | 0         | 1 channel parallel bridge tied load (PBTL)                             |

| 0         | 1         | 2 channels single ended load (SE) and 1 channel bridge tied load (BTL) |

| 1         | 0         | 2 channels bridge tied load (BTL)                                      |

| 1         | 1         | 4 channels single ended load (SE)                                      |

**Table 9-1 Signal configuration**

### **Bridge Tied Load (BTL) Configuration**

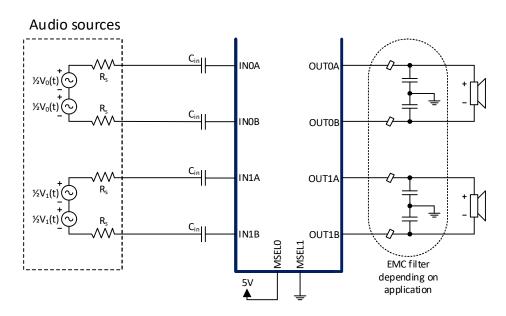

In BTL configuration, two input- and output terminals are used per channel as shown in Figure 9-1 and Figure 9-2. This configuration will enable the full potential of multi-level technology where the speaker load will experience up to 5 levels. This enables low near-idle power consumption and beneficial noise properties. Figure 9-1 shows a Bridge Tied Load (BTL) configuration (2 audio channels) with symmetrical audio sources having a differential output signal. In default recommended configuration external AC-coupling capacitors are used to allow the MA12040 to self-bias the DC voltage on the input terminals. Alternatively, the input can be driven without the AC-coupling capacitors. In this case the common-mode offset voltage should be selected to ensure that the voltage on the input terminals at full-scale audio levels are within the recommended range (see Table 6-1).

Figure 9-1 Bridge tied load (BTL) configuration, with symmetrical audio sources

Figure 9-2 shows a Bridge Tied Load (BTL) configuration (2 audio channels) with single ended audio sources. Note that the drive impedance of the two input terminals are matched to achieve optimum audio performance.

Figure 9-2 Bridge tied load (BTL) configuration, with single ended audio sources

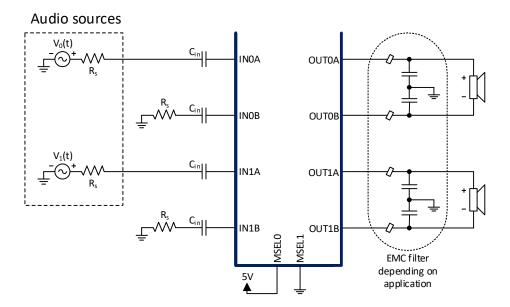

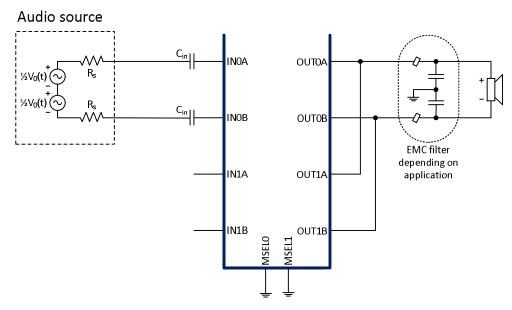

## **Single Ended (SE) Configuration**

In single ended (SE) configuration, the MA12040 is able to drive one loudspeaker per output power stage, i.e. up to four loudspeakers. The output is biased to half the power supply voltage,  $\frac{1}{2}$  PVDD. One of the solutions to drive a speaker in this configuration is to use AC-coupling capacitors ( $C_{out}$ ) in series with the load, as shown in Figure 9-3. The value of the capacitors depends on the load resistance and the desired audio bandwidth.

Table 9-2 shows examples of AC-coupling capacitor values. The DC voltage across the capacitors at the output is approximately ½PVDD. However, significant AC-voltage swing might occur at low frequencies, which must be accounted for in the voltage rating of the capacitors.

Figure 9-3 Four channel, single ended (SE) configuration

Table 9-2 Typical values for the output AC-coupling capacitor, Cout

| Load Resistance | Output AC-coupling capacitor, Cout | -3dB frequency |

|-----------------|------------------------------------|----------------|

| 8Ω              | 220μF                              | 90Hz           |

| 8Ω              | 1000μF                             | 20Hz           |

| 4Ω              | 2200μF                             | 18Hz           |

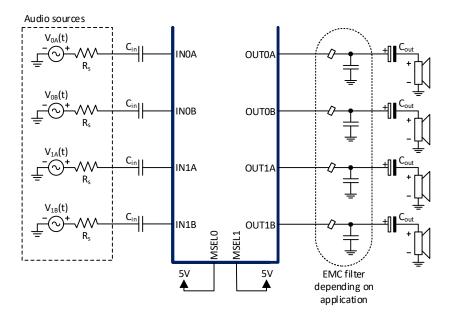

## **Combined SE and BTL Configuration**

A combination of SE and BTL configuration can be used as shown in Figure 9-4. In this configuration two half-bridges are combined to run in BTL configuration and the two remaining half-bridges are configured to run in SE configuration.

Figure 9-4 Combined Bridge tied load (BTL) and single ended (SE) configuration, with SE audio sources

## **Parallel Bridge Tied Load (PBTL)**

For providing additional power the MA12040 can be configured for mono operation using a parallel BTL mode (PBTL), as shown in Figure 9-5. In this fashion the two BTL output stages are combined to be able to deliver twice the current. This makes high output power sub-woofer application possible. Note: Input pins IN1A and IN1B are unused and can be left floating.

Figure 9-5 Parallel Bridge Tied Load (PBTL) configuration

Regardless the application, it is recommended to use AC-coupling capacitors, C<sub>in</sub>, at the analog audio input terminals INXX to allow the internal biasing circuitry to set a suitable DC bias operating voltage on the input terminals. The value of the capacitors depends on the configuration, see Table 9-3. Ceramic capacitors are recommended, e.g. of type X5R.

Table 9-3 Recommended values for input ac-coupling capacitors, Cin

| Input Impedance Configuration MA12040 |                | Recommended minimum AC-coupling capacitor, C <sub>in</sub> | Gain drop at<br>20Hz |  |

|---------------------------------------|----------------|------------------------------------------------------------|----------------------|--|

| 14kΩ                                  | High gain mode | 2.2μF                                                      | -0.6dB               |  |

| 21kΩ                                  | Low gain mode  | 1μF                                                        | -1dB                 |  |

#### **EMC output filter Considerations**

The proprietary 5-level modulation significantly reduces EMC emissions, and the amplifiers can pass the Radiated Emission test with speaker cables lengths up to 80 cm with just a small ferrite filter. For cables longer than 80 cm it is recommended to use a LC-filter.

For more information regarding filter type, components and measurements, see the document "Applications note – EMC Output Filter Recommendations" at the Infineon homepage.

#### **Audio Performance Measurements**

In a typical audio application the outputs of the MA12040 will be connected directly to the speaker loads. However, for audio performance evaluation it can be beneficial to configure the circuit board with an LC filter. This is due to the fact that many audio analyzers do not handle PWM signals at their inputs well.

When using an audio analyzer configured with an external and/or internal measurement filter the use of an LC filter is not necessary. However, be sure to verify the audio analyzer's input limits before connecting it to a filterless amplifier output.

When using an LC filter, the design depends on the specific load. L and C values should therefore be optimized for this.

## **Thermal Characteristics and Test Signals**

Performing audio measurements by use of an audio analyzer is typically very helpful during the evaluation of an amplifier. However, using an audio analyzer can be misleading when evaluating thermal performance.

Audio analyzers typically generate full tone, continuous sine wave signals as the input signal for the amplifier. While this is required to perform many audio measurements, it is also the worst-case thermal scenario for the device. Using full-scale continuous sine waves for thermal evaluation or testing will lead to an overly conservative and more costly thermal design which will be unnecessary in almost all real audio applications.

Actual audio content, such as music, has much lower RMS values compared to its maximum peak output power than a full-scale continuous sine wave. This results in significantly less heat dissipation from the device when amplifying actual audio. For thermal evaluation it is therefore recommended to use actual music signals during tests. Alternatively, a pink noise signal can be used to emulate a music signal.

It is not uncommon for an amplifier solution to have limited thermal performance, potentially resulting in thermal protection shutdown, when amplifying full-scale continuous sine wave signals.

### **Start-up procedure**

It is recommended to follow the start-up procedure as described below:

- 1) Make sure the all hardware pins are configured correctly: e.g. BTL, Slave Clock mode.

- 2) Keep the device in disable and mute: /ENABLE = 1; /MUTE = 0.

- 3) Bring up 5V VDD supply and PVDD supply (it does not matter if VDD or PVDD comes up first, provided that the device is held in disable).

- 4) Wait for VDD and PVDD to be stable.

- 5) Enable device: /ENABLE = 0.

- 6) Program applicable initialization to registers.

- 7) Unmute device: /MUTE = 1.

- 8) The device is now in normal operation state.

### Shut-down / power-down procedure

It is recommended to follow the start-up procedure as described below:

- 1) The device is in normal operation state.

- 2) Mute device: /MUTE = 0.

- 3) Disable device: /ENABLE = 1.

- 4) The device is now power-down state.

- 5) Bring down 5V VDD supply and PVDD supply.

- 6) The device is now in shut-down state.

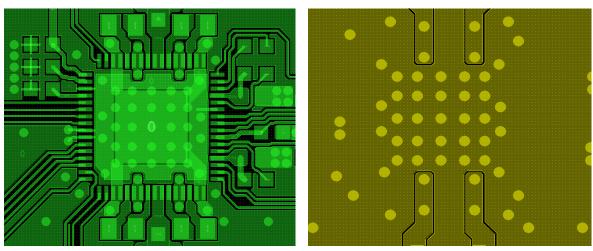

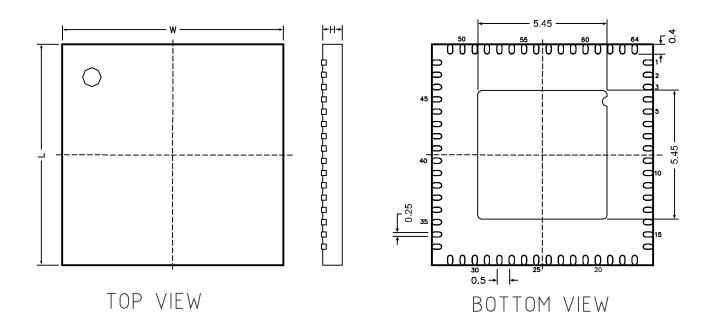

#### Recommended PCB Design for MA12040QFN (EPAD-down package)

The QFN package with exposed thermal pad at the bottom side is thermally sufficient for most applications. However, in order to remove heat from the package care should be taken in designing the PCB.

The PCB footprint for the device should include a thermal relief pad underneath the device with a size of 6 x 6 mm. This thermal relief pad must be centered so the device can be soldered easily. It is recommended to use a PCB design with two or more layers of copper for good thermal performance. Using multiple layers enables a design with a large area of copper connected to the EPAD.

To achieve best thermal performance it is also important to design the surrounding connections in such a way that avoids cutting up the copper area into many sections.

Figure 9-6 shows a PCB design using 26 via connections directly underneath the chip between the top and bottom layers. These should be placed on a grid each with a 0.65 mm plated through hole. These connections ensure good thermal transfer from the top side EPAD to a large section of ground connected copper area on the bottom side of the PCB.

Figure 9-6 Example of 2-layer PCB layout, top and bottom layers

It is recommended to use a PCB made from glass/epoxy laminate (e.g. FR-4) material. This type of material works well with PCB designs that require thermal relief as it can endure high temperatures for a long duration of time.

PCB copper thickness is recommended to be a minimum of  $35\mu$  (1 oz) and the PCB must be made to the IPC 6012C, Class 2 standard.

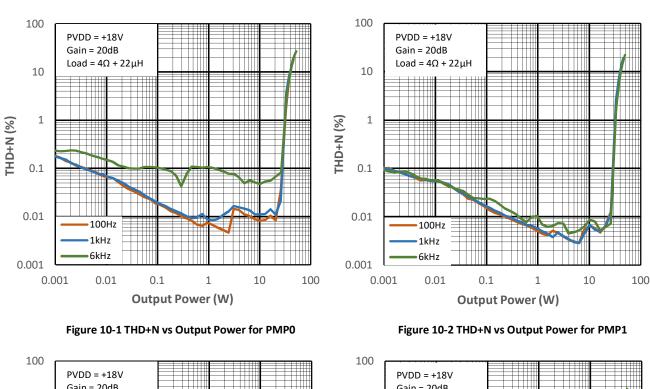

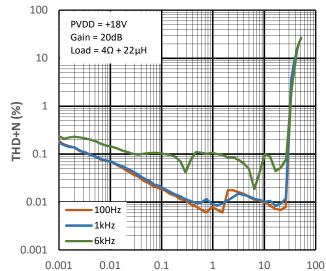

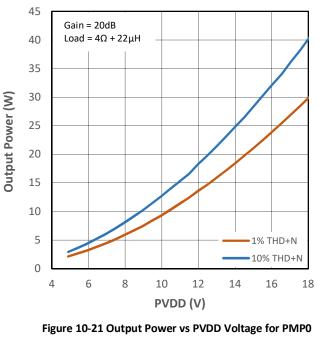

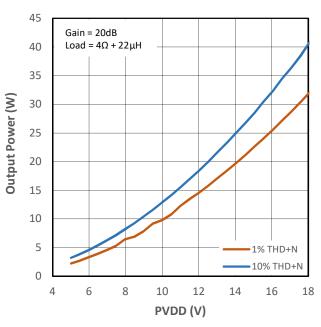

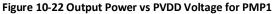

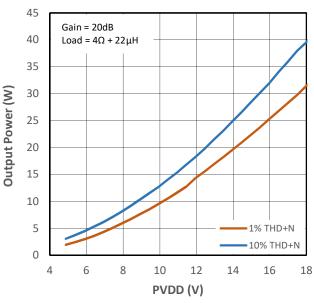

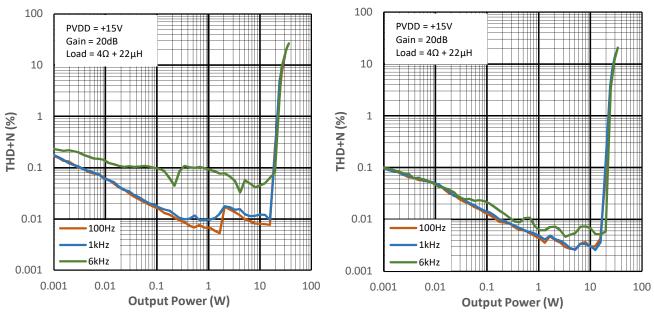

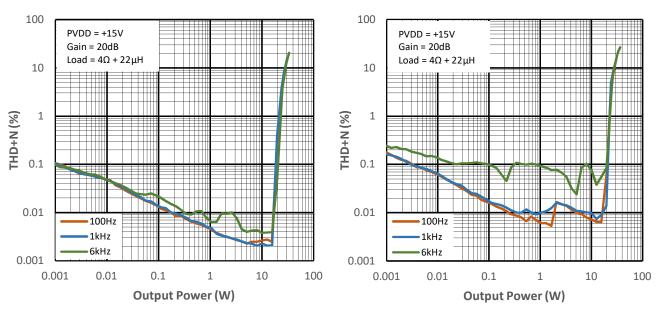

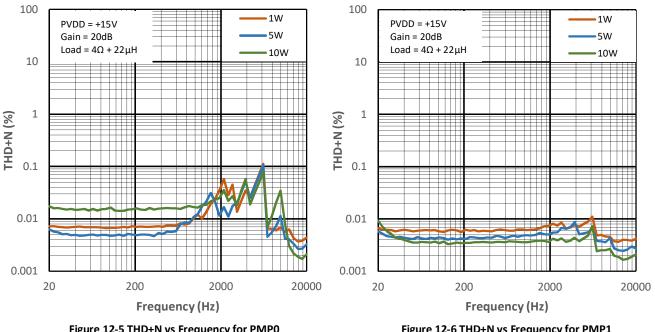

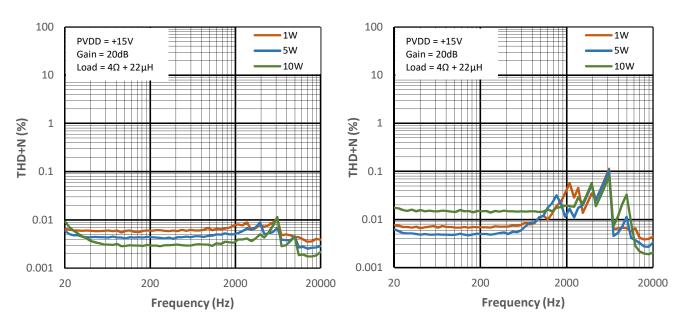

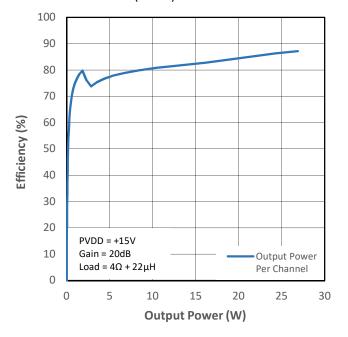

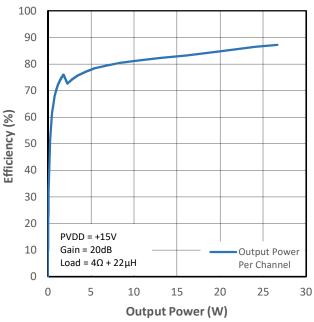

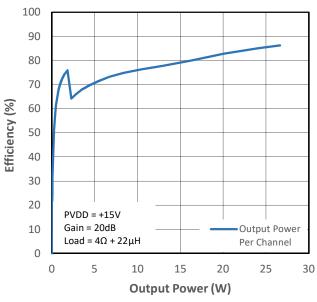

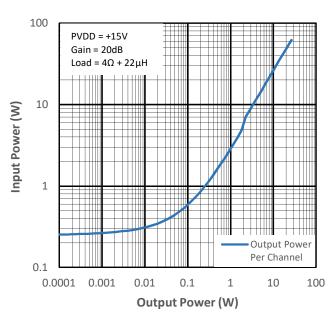

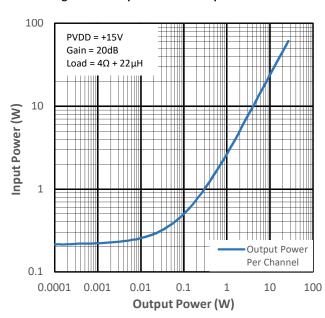

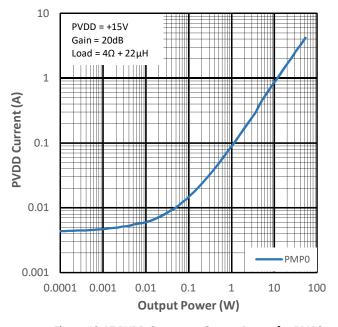

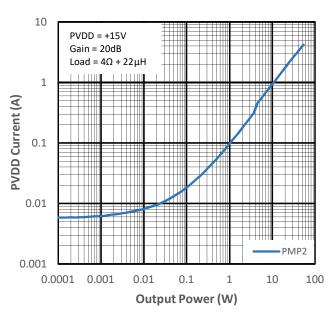

# 10 Typical Characteristics (PVDD = +18V, Load = $4\Omega + 22\mu H$ )

PVDD = +18V

Gain = 20dB

Load = 4Ω + 22μH

0.1

0.01

100Hz

1kHz

6kHz

0.001

0.001

0.001

0.001

0.001

0.001

0.001

0.001

0.001

0.001

0.001

0.001

0.001

0.001

0.001

0.001

0.001

0.001

Figure 10-3 THD+N vs Output Power for PMP2

Output Power (W)

Figure 10-4 THD+N vs Output Power for PMP4

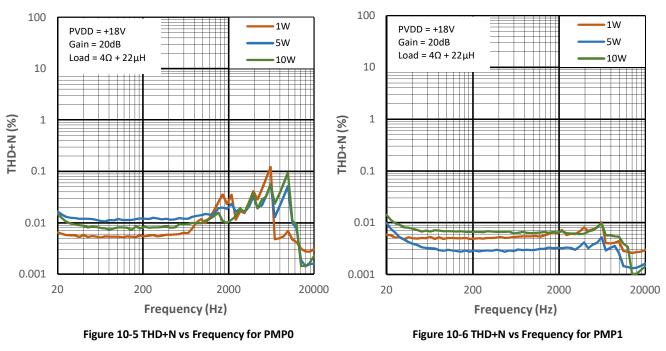

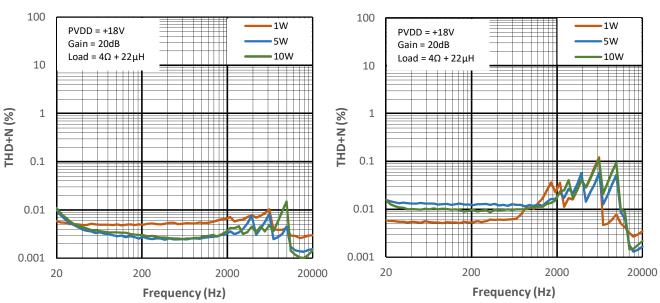

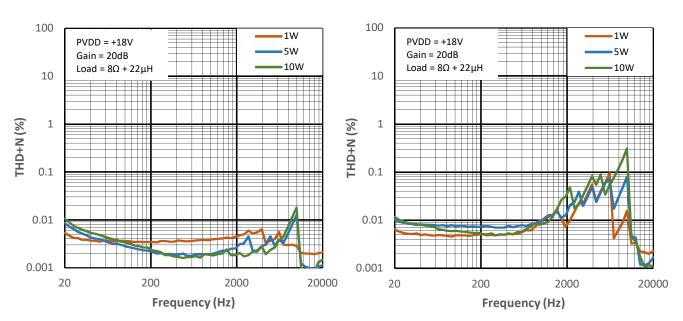

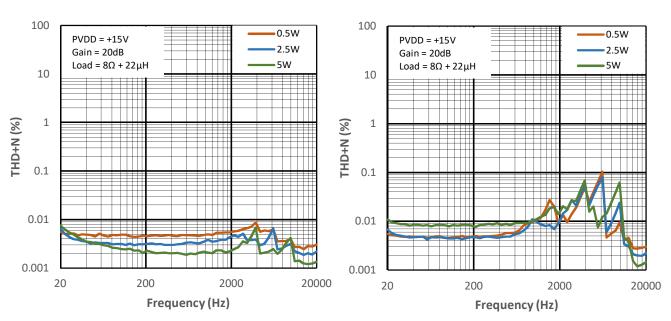

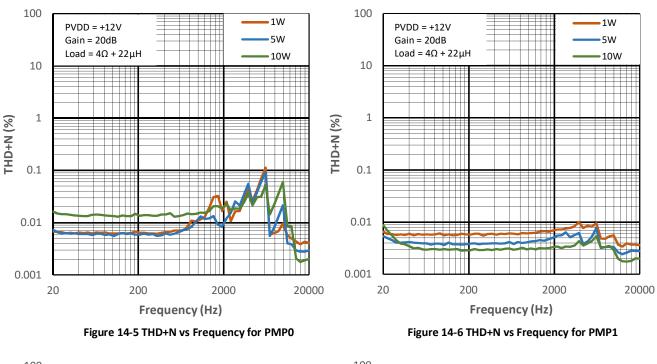

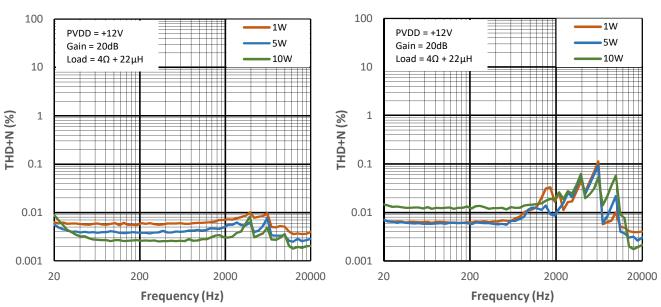

Figure 10-7 THD+N vs Frequency for PMP2

Figure 10-8 THD+N vs Frequency for PMP4

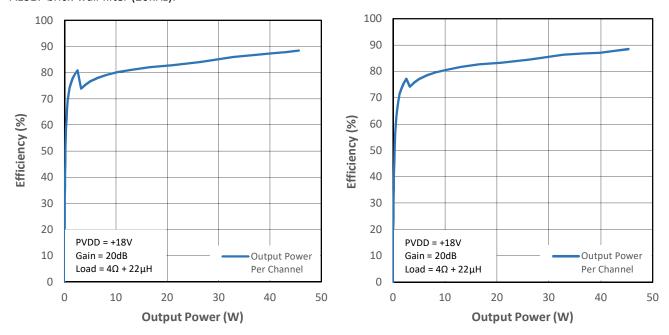

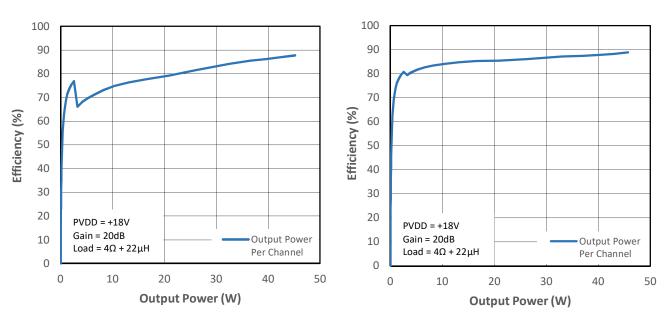

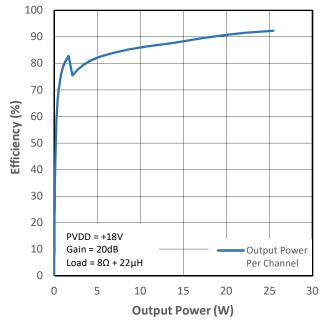

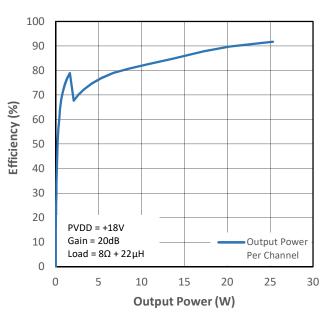

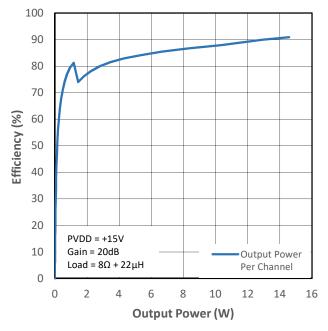

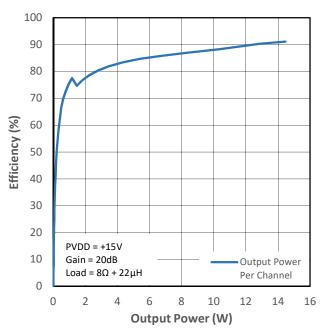

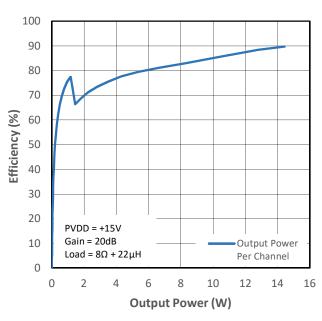

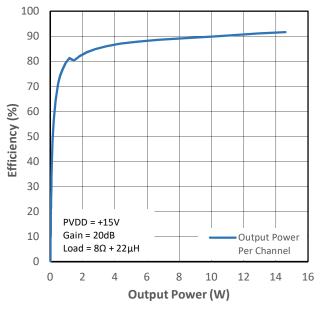

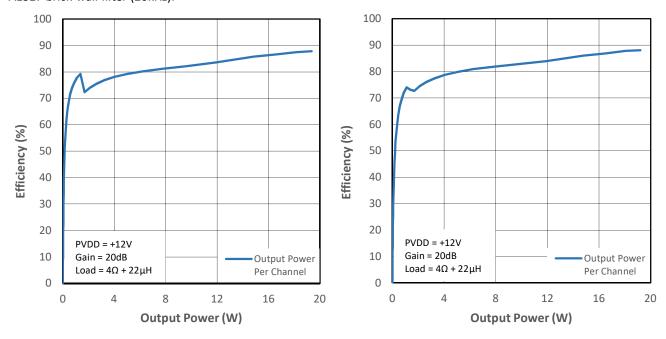

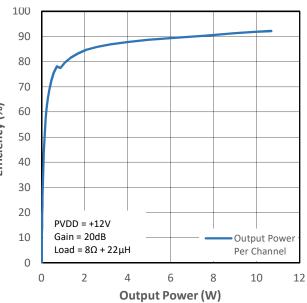

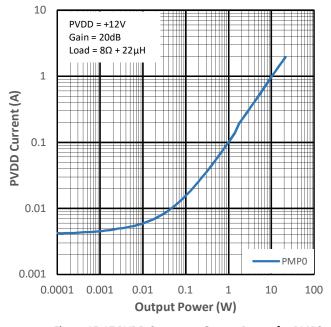

Figure 10-9 PMP0 Efficiency (VDD+PVDD) vs Output Power

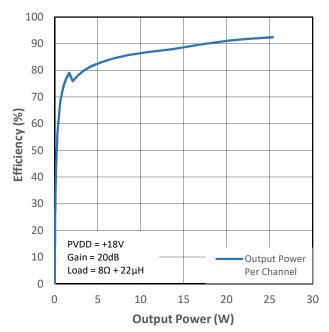

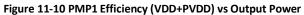

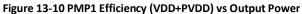

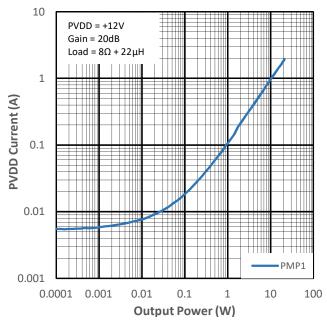

Figure 10-10 PMP1 Efficiency (VDD+PVDD) vs Output Power

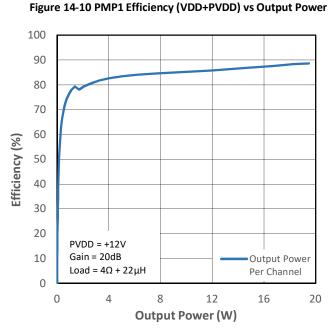

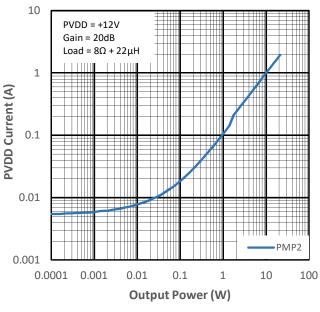

Figure 10-11 PMP2 Efficiency (VDD+PVDD) vs Output Power

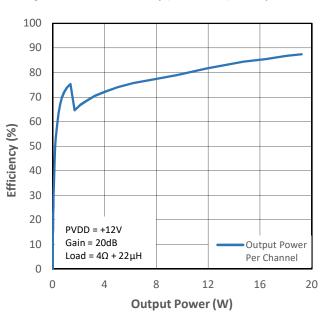

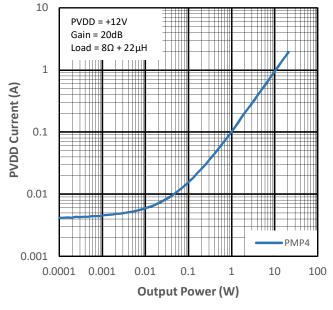

Figure 10-12 PMP4 Efficiency (VDD+PVDD) vs Output Power

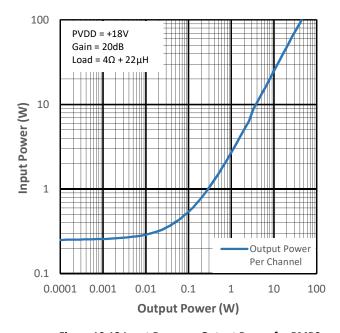

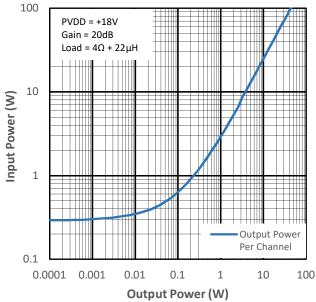

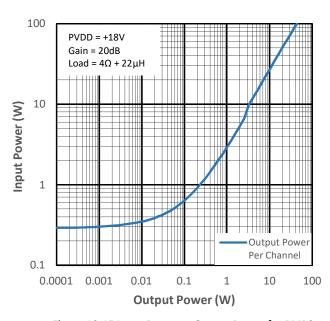

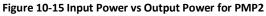

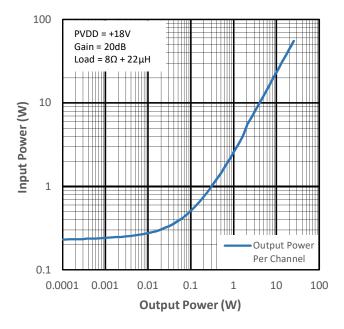

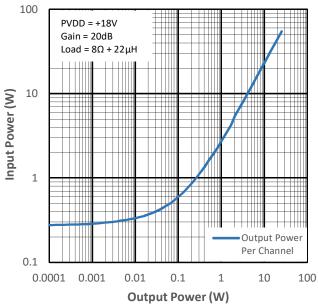

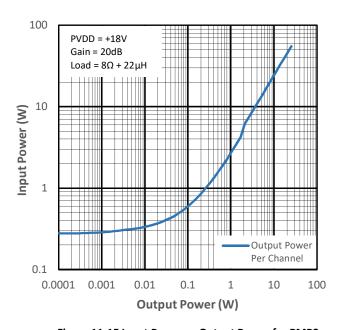

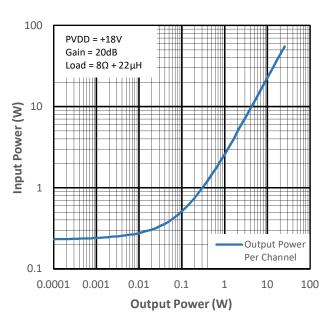

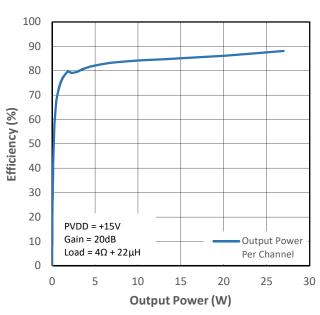

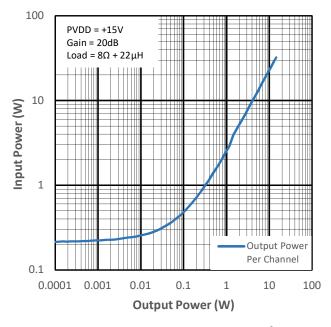

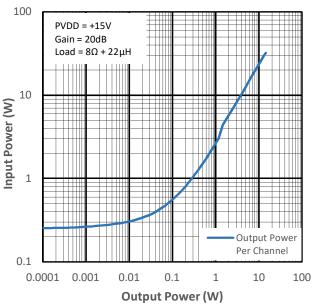

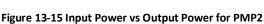

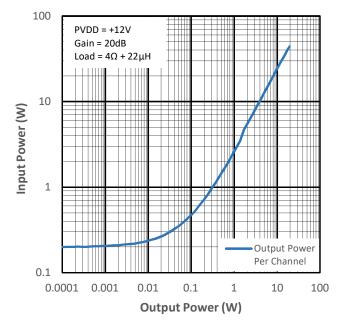

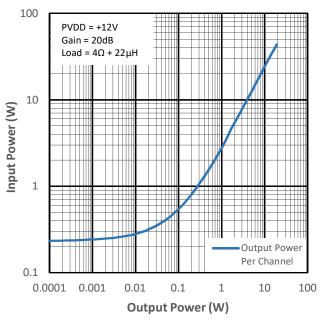

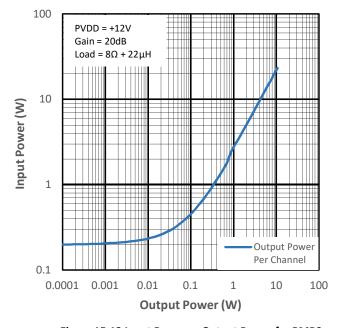

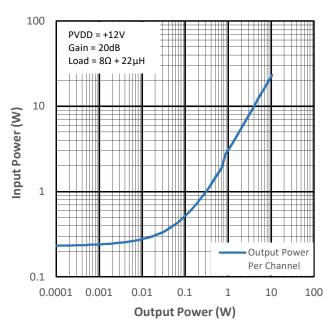

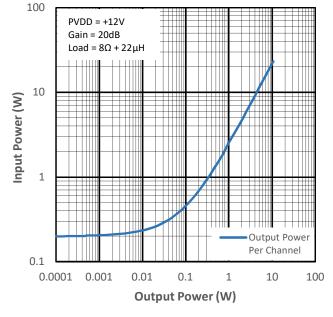

Figure 10-13 Input Power vs Output Power for PMP0

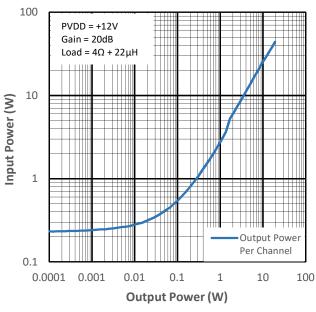

Figure 10-14 Input Power vs Output Power for PMP1

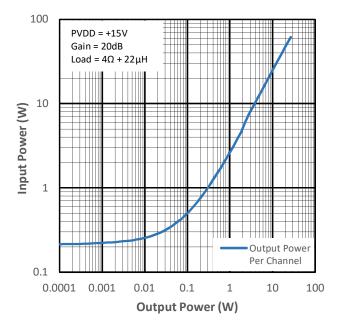

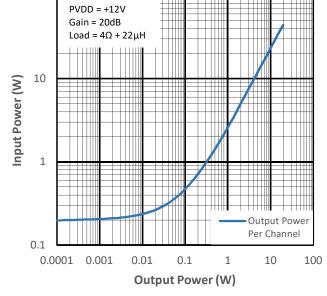

Figure 10-16 Input Power vs Output Power for PMP4

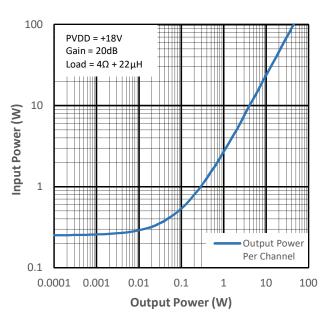

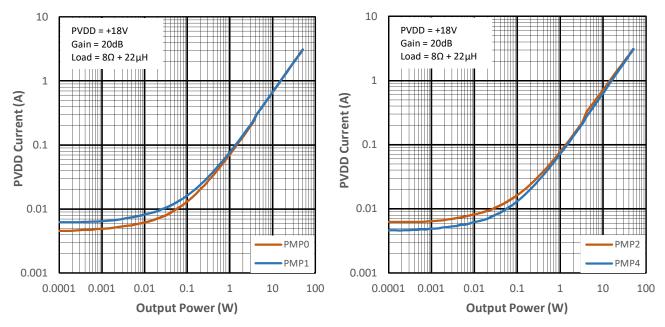

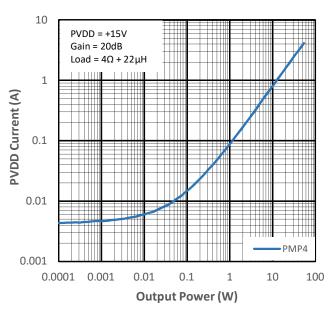

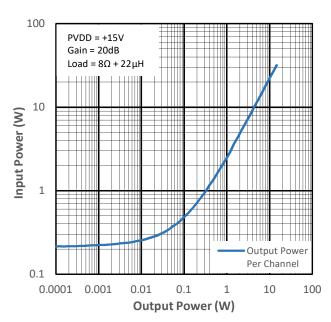

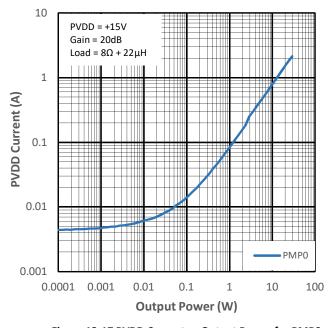

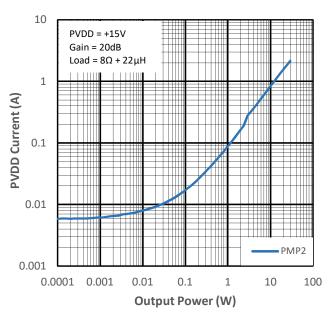

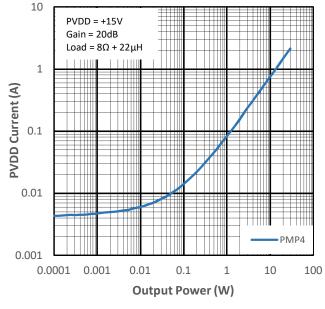

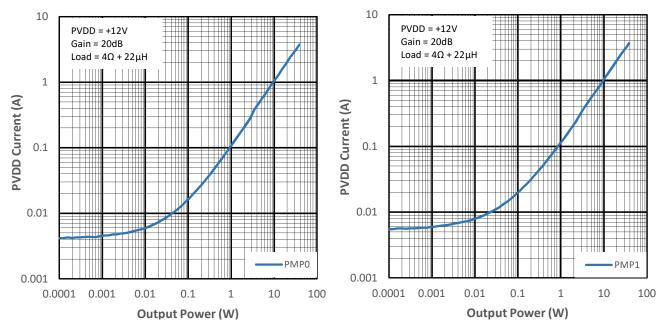

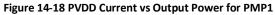

Figure 10-17 PVDD Current vs Output Power for PMP0 & PMP1

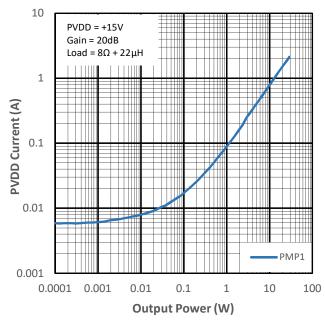

Figure 10-18 PVDD Current vs Output Power for PMP2 & PMP4

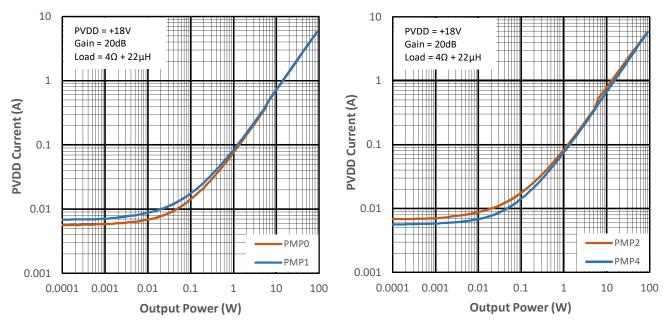

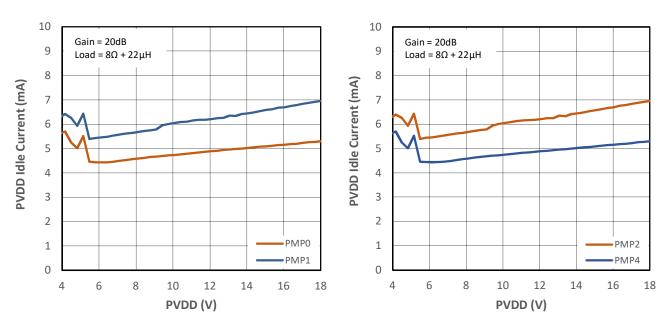

Figure 10-19 PVDD Idle Current vs PVDD for PMP0 & PMP1

Figure 10-20 PVDD Idle Current vs PVDD for PMP2 & PMP4

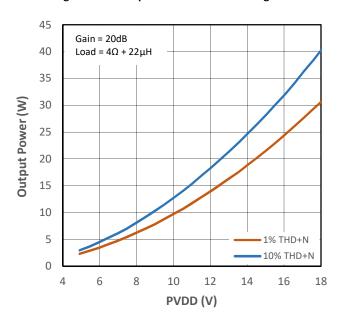

Figure 10-23 Output Power vs PVDD Voltage for PMP2

Figure 10-24 Output Power vs PVDD Voltage for PMP4

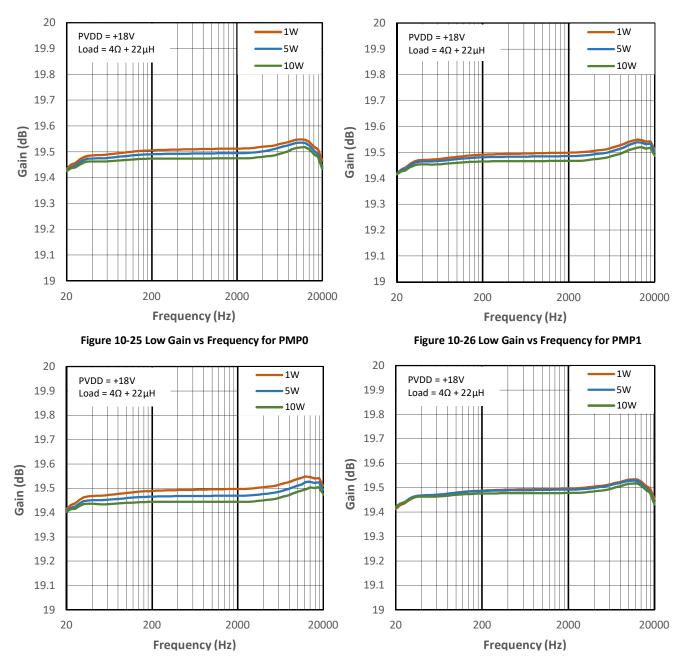

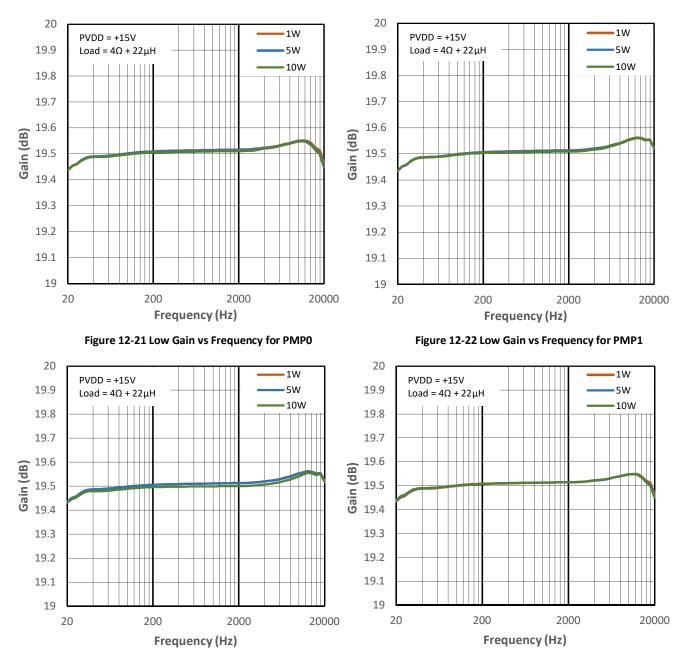

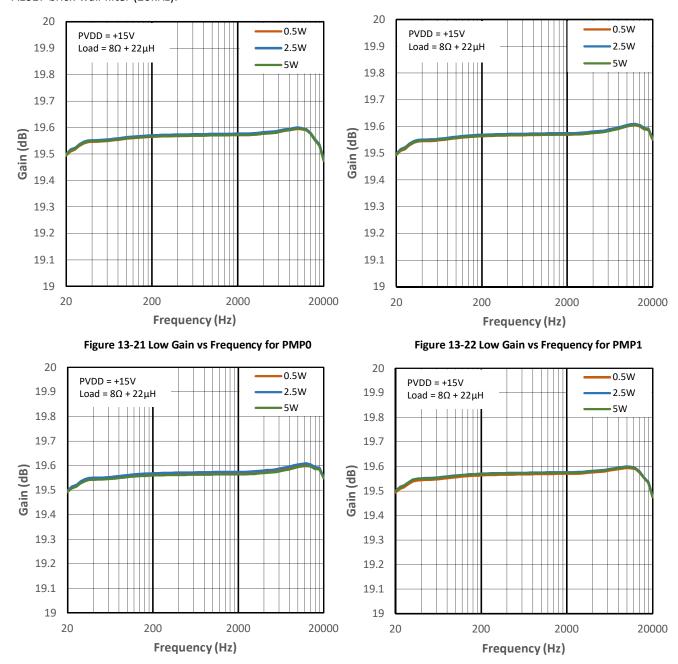

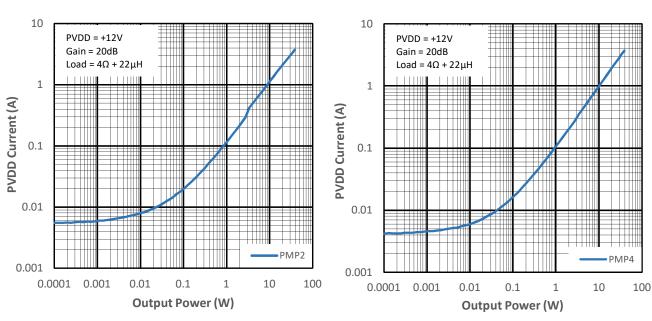

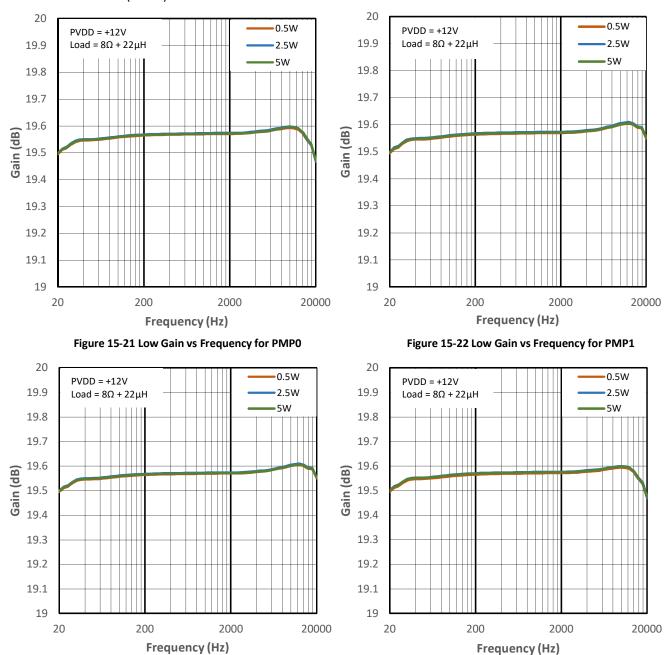

Figure 10-27 Low Gain vs Frequency for PMP2

Figure 10-28 Low Gain vs Frequency for PMP4

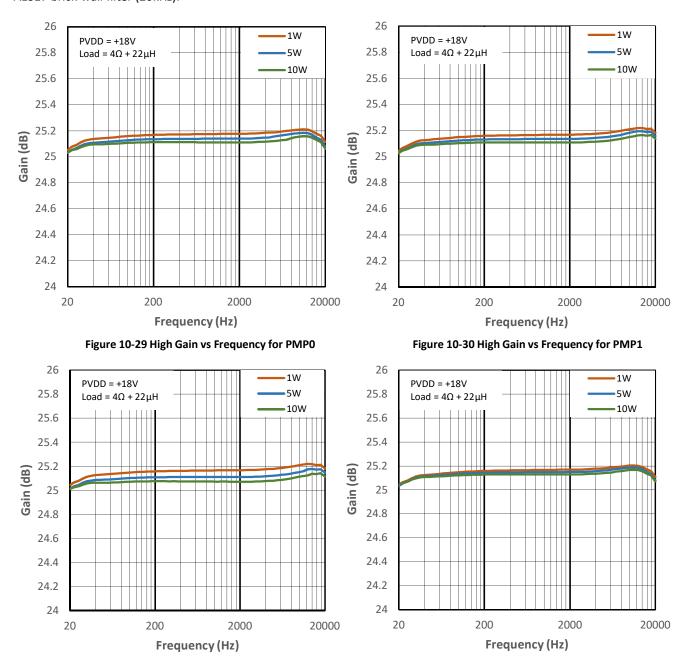

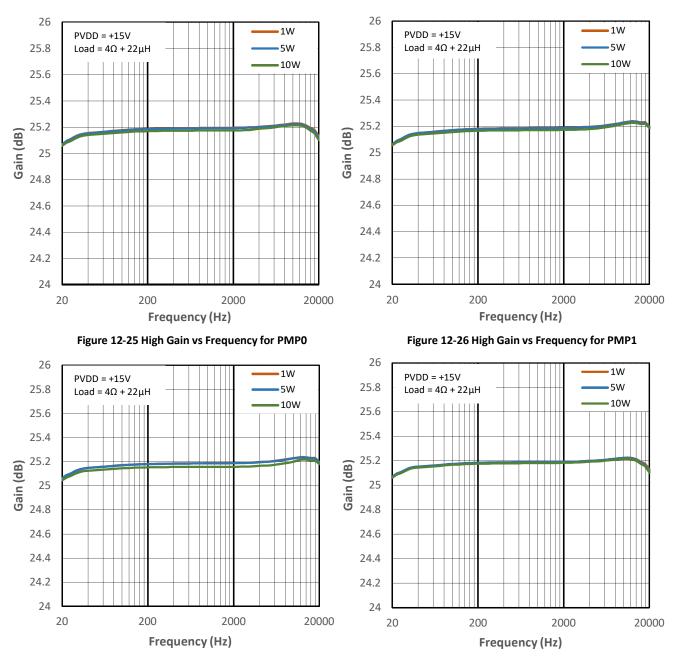

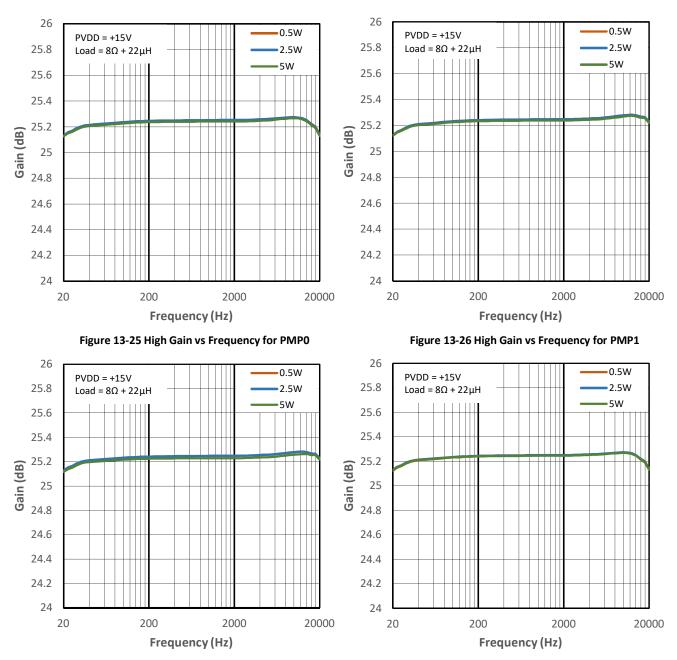

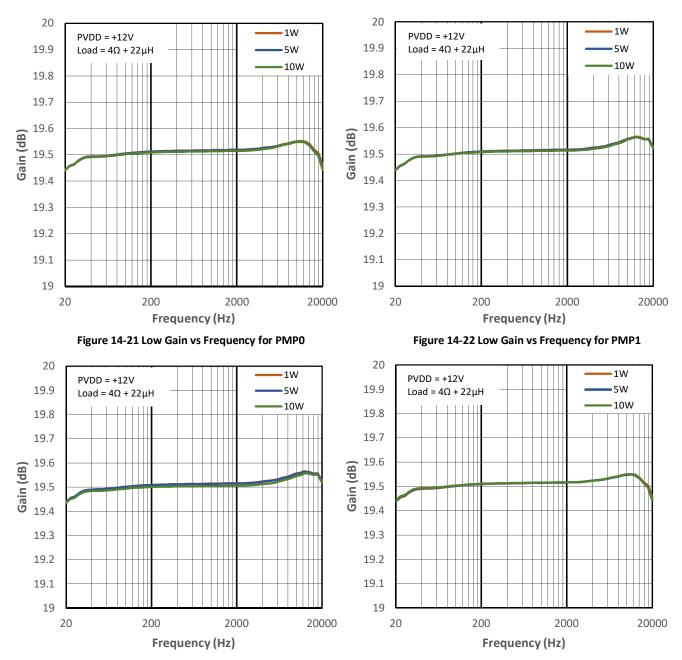

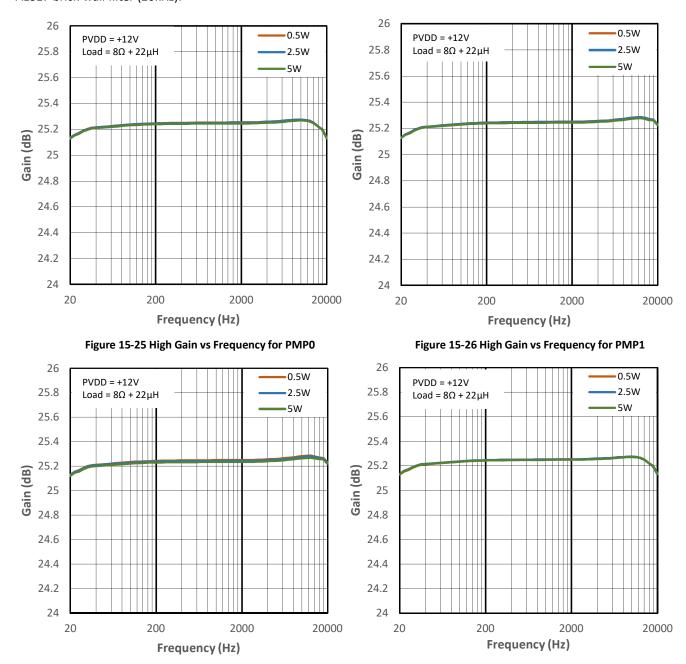

Figure 10-31 High Gain vs Frequency for PMP2

Figure 10-32 High Gain vs Frequency for PMP4

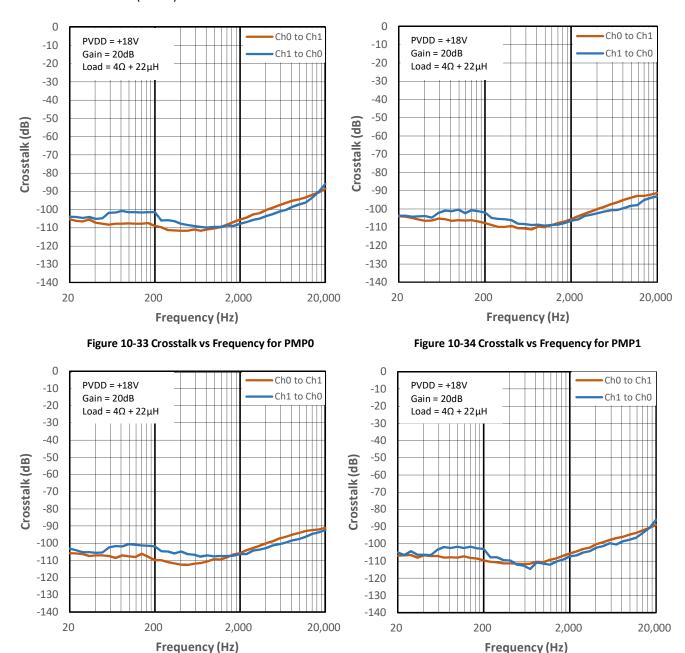

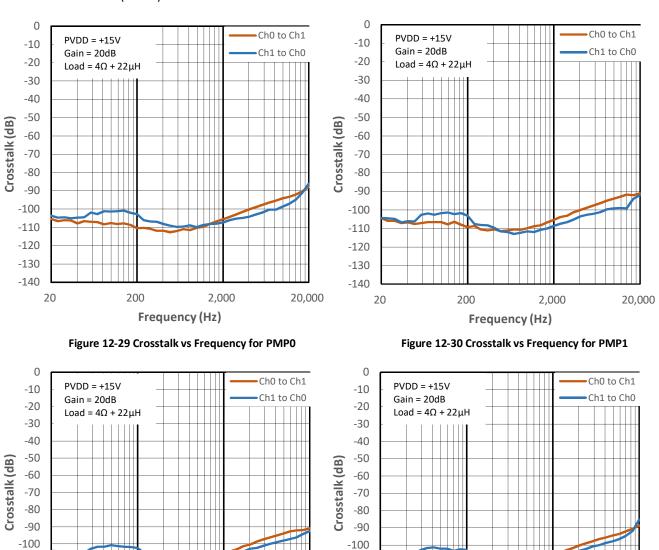

Figure 10-35 Crosstalk vs Frequency for PMP2

Figure 10-36 Crosstalk vs Frequency for PMP4

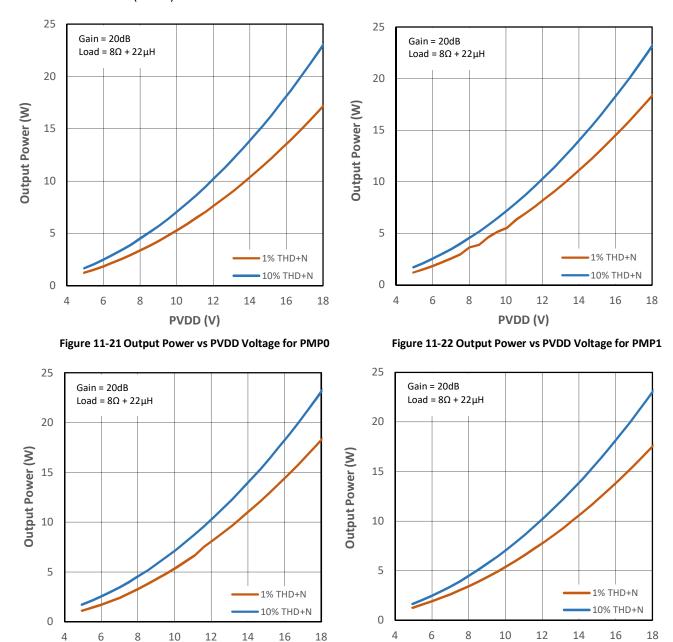

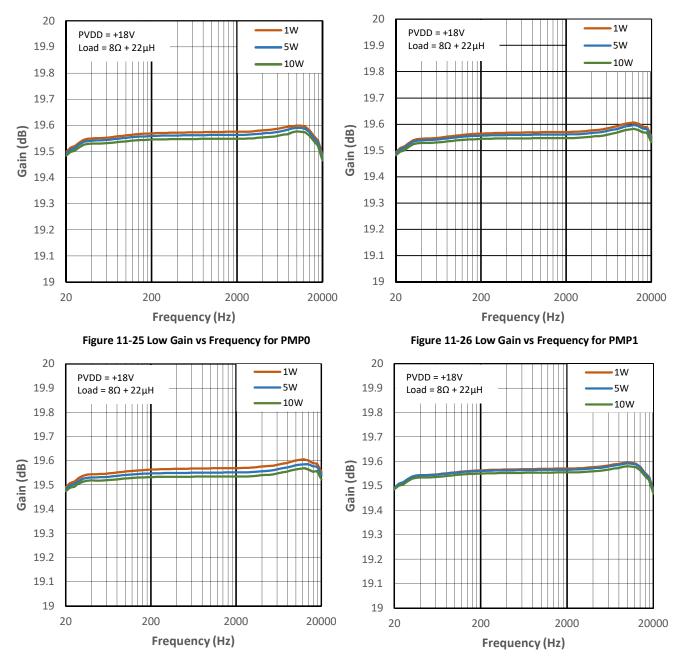

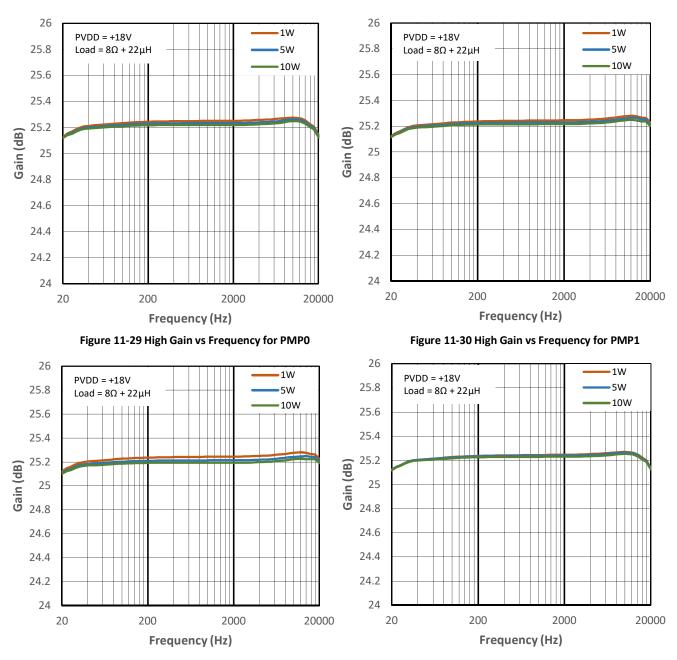

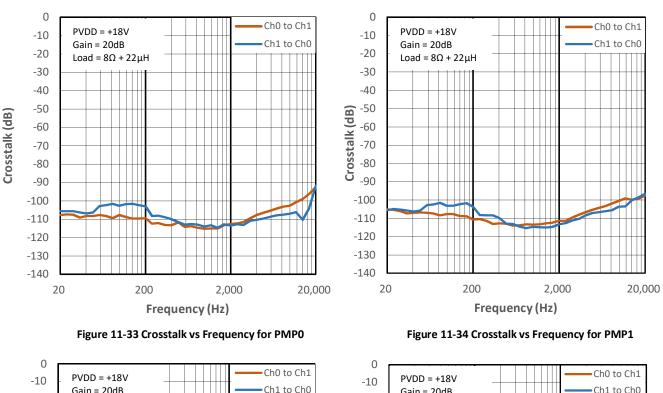

# 11 Typical Characteristics (PVDD = +18V, Load = $8\Omega + 22\mu H$ )

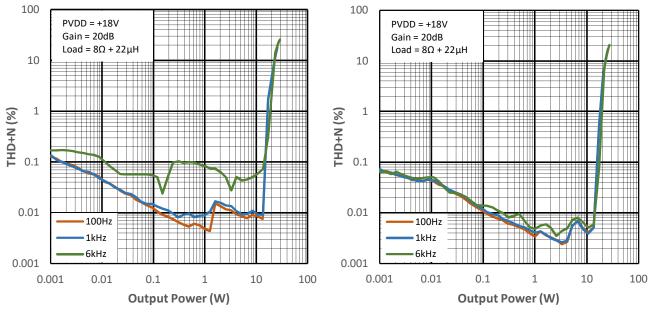

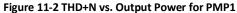

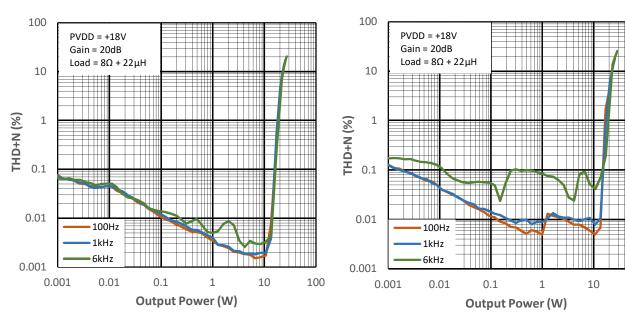

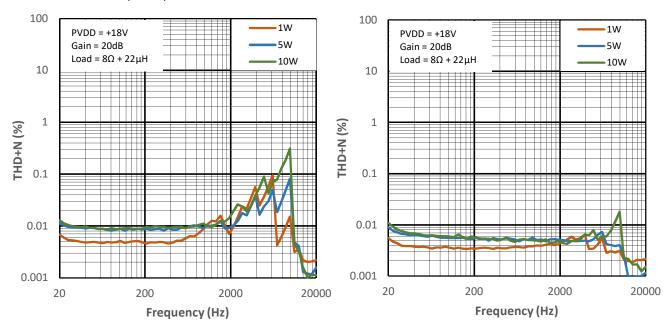

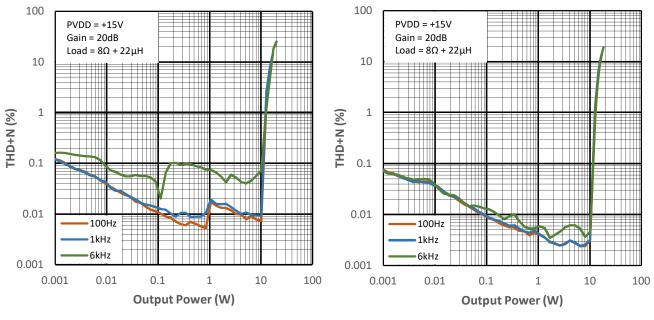

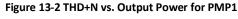

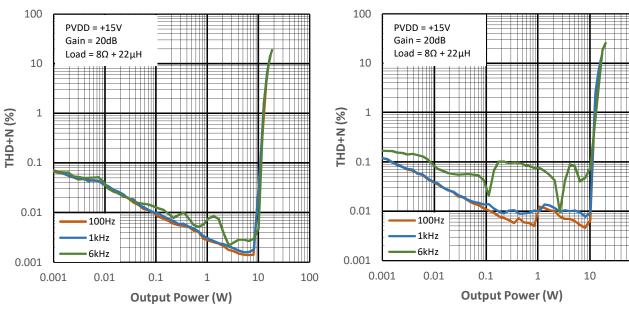

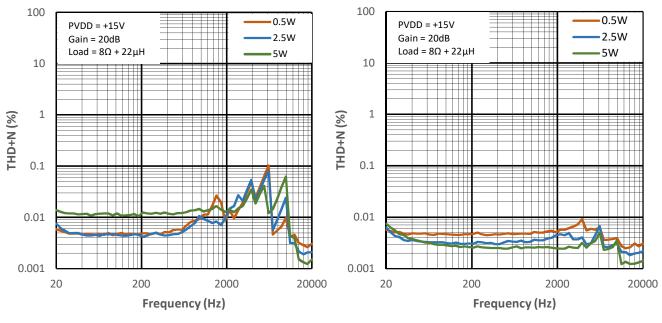

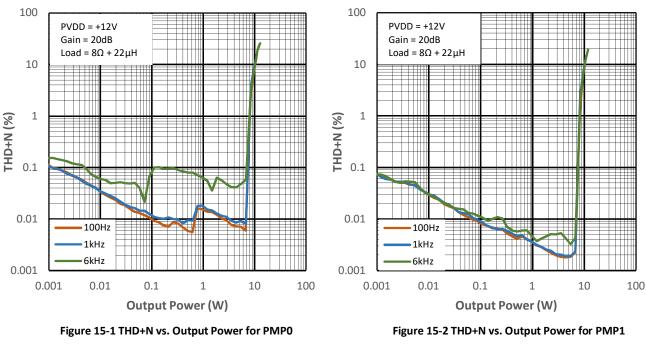

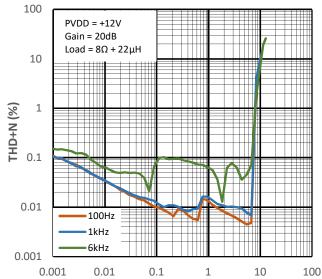

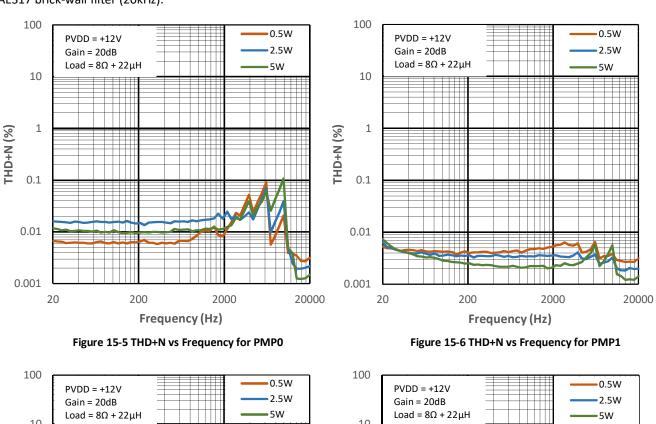

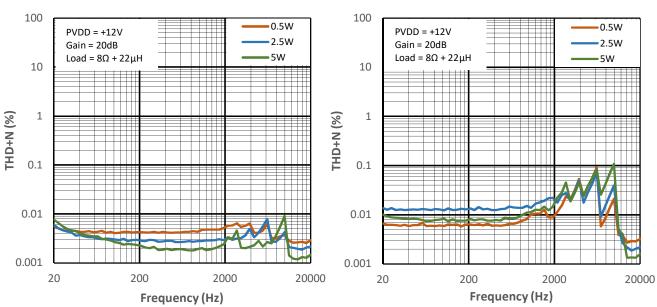

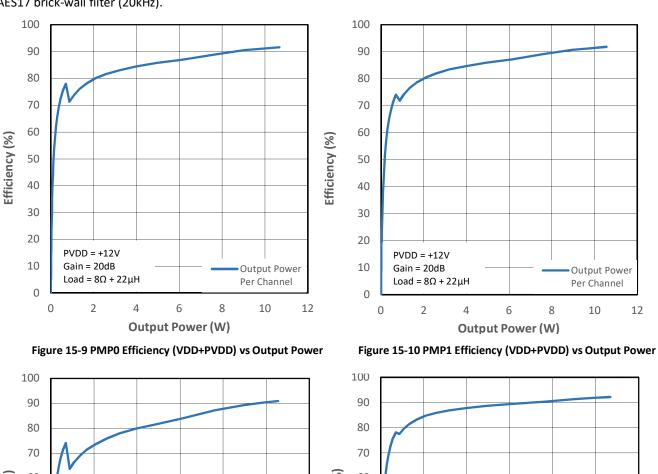

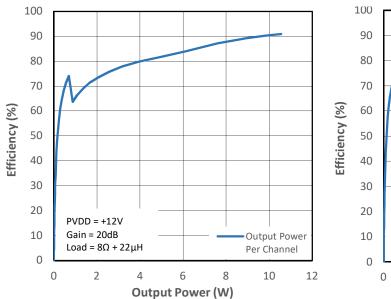

**BTL configuration; Load = 8\Omega + 22\muH**; Measurements carried out with APx 515 + AUX-0025 input filter; APx uses AES17 brick-wall filter (20kHz).

Figure 11-1 THD+N vs. Output Power for PMP0

Figure 11-3 THD+N vs. Output Power for PMP2

Figure 11-4 THD+N vs. Output Power for PMP4

100

Figure 11-5 THD+N vs Frequency for PMP0

Figure 11-6 THD+N vs Frequency for PMP1

Figure 11-7 THD+N vs Frequency for PMP2

Figure 11-8 THD+N vs Frequency for PMP4

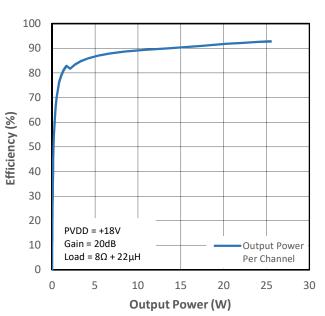

Figure 11-9 PMP0 Efficiency (VDD+PVDD) vs Output Power

Figure 11-11 PMP2 Efficiency (VDD+PVDD) vs Output Power

Figure 11-12 PMP4 Efficiency (VDD+PVDD) vs Output Power