# 6A, 18V, Synchronous Step-Down Converter

# **General Description**

The RT2856 is a high efficiency, monolithic synchronous step-down DC-DC converter that can deliver up to 6A output current from a 4.5V to 18V input supply. The RT2856 current-mode architecture with external compensation allows the transient response to be optimized over a wide range of loads and output capacitors. Cycle-by-cycle current limit provides protection against shorted outputs, and soft-start eliminates input current surge during start-up. Fault condition protections include output under-voltage protection, output over-voltage protection, and over-temperature protection. The low current shutdown mode provides output disconnection, enabling easy power management in battery-powered systems.

# **Marking Information**

00=YM DNN 00= : Product Code YMDNN : Date Code

## **Features**

- Low R<sub>DS(ON)</sub> Power MOSFET Switches 26mΩ/19mΩ

- Input Voltage Range: 4.5V to 18V

- Adjustable Switching Frequency: 200kHz to 1.6MHz

- Current-Mode Control

- Synchronous to External Clock: 200kHz to 1.6MHz

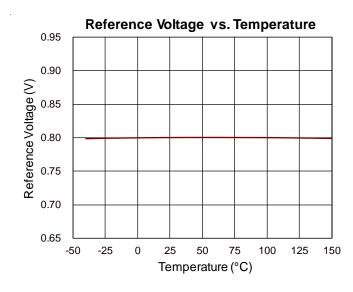

- Accurate Voltage Reference

- → 0.8V ± 1%, Over -40°C to 85°C

- → 0.8V ± 1.5%, Over -40°C to 150°C

- Monotonic Start-Up into Pre-biased Outputs

- Adjustable Soft-Start

- Power Good Indicator

- Under-Voltage and Over-Voltage Protection

- Input Under-Voltage Lockout

- RoHS Compliant and Halogen Free

## **Applications**

- High Performance Point of Load Regulation

- Notebook Computers

- High Density and Distributed Power Systems

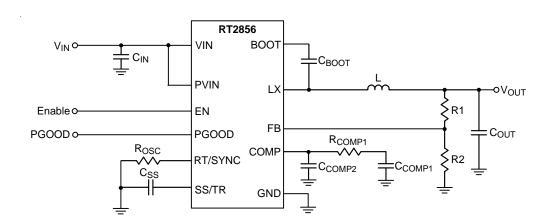

# **Simplified Application Circuit**

# **Ordering Information**

RT2856 🗆 🗖 Package Type QW: WQFN-14AL 3.5x3.5 (W-Type) Lead Plating System G: Green (Halogen Free and Pb Free)

#### Note:

Richtek products are:

- > RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

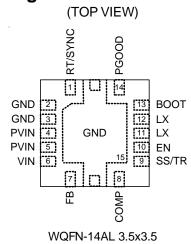

# **Pin Configuration**

# **Functional Pin Description**

| Pin No.                       | Pin Name | Pin Function                                                                                                                                                                                                                                       |

|-------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                             | RT/SYNC  | Oscillator resistor and external frequency synchronization input. Connecting a resistor from this pin to GND sets the switching frequency or connecting an external clock to this pin changes the switching frequency.                             |

| 2, 3,<br>15 (Exposed Pad) GND |          | System ground. Provide the ground return path for the control circuitry and low-side power MOSFET. The exposed pad must be soldered to a large PCB and connected to GND for minimum power dissipation.                                             |

| 4, 5                          | PVIN     | Power input. Supplies the power switches of the device.                                                                                                                                                                                            |

| 6                             | VIN      | Supply voltage input. Supplies the control circuitry and internal reference of the device.                                                                                                                                                         |

| 7                             | FB       | Feedback voltage input. This pin is used to set the desired output voltage via an external resistive divider. The feedback reference voltage is 0.8V typically.                                                                                    |

| 8                             | COMP     | Compensation node. The current comparator threshold increases with this control voltage. Connect external compensation elements to this pin to stabilize the control loop.                                                                         |

| 9                             | SS/TR    | Soft-start and tracking control input. Connect a capacitor from SS to GND to set the soft-start period. The soft-start period can be used to track and sequence when the external voltage on this pin overrides the internal reference.            |

| 10                            | EN       | Enable control input. Floating this pin or connecting this pin to logic high can enable the device and connecting this pin to GND can disable the device.                                                                                          |

| 11, 12                        | LX       | Switch node. LX is the switching node that supplies power to the output and connect the output LC filter from LX to the output load.                                                                                                               |

| 13                            | воот     | Bootstrap supply for high-side gate driver. Connect a 100nF or greater capacitor from LX to BOOT to power the high-side switch.                                                                                                                    |

| 14                            | PGOOD    | Power good indicator output. This pin is an open-drain logic output that is pulled to ground when the output voltage is lower or higher than its specified threshold under the conditions of OVP, OTP, dropout, EN shutdown, or during slow start. |

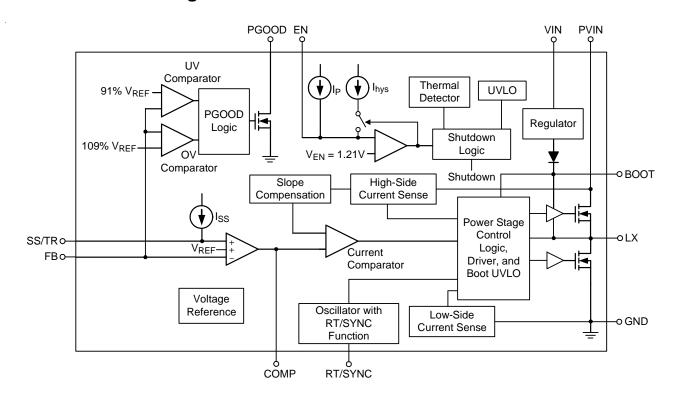

## **Functional Block Diagram**

## **Operation**

### **UV** Comparator

If the feedback voltage ( $V_{FB}$ ) is lower than threshold voltage (91% of  $V_{REF}$ ), the UV Comparator's output goes high and the logic control circuit is allowed to turn on the MOSFET to pull PGOOD pin to low.

#### **OV** Comparator

If the feedback voltage ( $V_{FB}$ ) is higher than threshold voltage (109% of  $V_{REF}$ ), the OV Comparator's output goes high and the logic control circuit is allowed to turn on the MOSFET to pull PGOOD pin to low.

### Voltage Reference

The converter produces a precise  $\pm 1\%$  voltage reference over-temperature by scaling the output of a temperature stable bandgap circuit.

#### **Error Amplifier**

The device uses a transconductance error amplifier. The error amplifier compares the FB pin voltage with the SS/TR pin voltage and the internal reference voltage which is 0.8V. The transconductance of the error amplifier is 1300  $\mu$ A/V during normal operation. The compensation network should be connected between the COMP pin and ground.

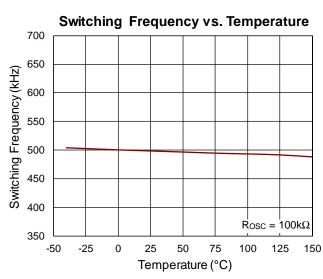

#### Oscillator with RT/SYNC function

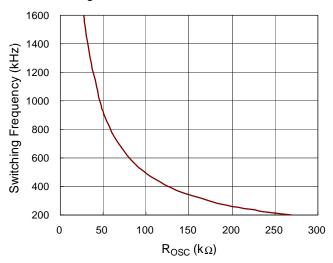

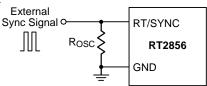

The switching frequency is adjustable by an external resistor connected between the RT/SYNC pin and GND. The available frequency range is from 200kHz to 1.6MHz. An internal synchronized circuit has been implemented to switch from RT mode to SYNC mode. To implement the synchronization function, connect a square wave clock signal to the RT/SYNC pin with a duty cycle between 10% to 90%. The switching cycle is synchronized to the falling edge of the external clock at RT/SYNC pin.

Copyright ©2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

## **Absolute Maximum Ratings** (Note 1)

| Supply Input Voltage, VIN, PVIN         | -0.3V to 20V   |

|-----------------------------------------|----------------|

| • Switch Node Voltage, LX               | -1V to 20.3V   |

| LX (t $\leq$ 10ns)                      | -8V to 26.3V   |

| • VIN to LX                             | -1V to 20.3V   |

| VIN to LX (t $\leq$ 10ns)               | -8V to 26.3V   |

| • BOOT to LX                            | -0.3V to 7V    |

| • BOOT Pin Voltage                      | -0.3V to 27.3V |

| • Other Pins                            | -0.3V to 6V    |

| • Junction Temperature                  | 150°C          |

| • Lead Temperature (Soldering, 10 sec.) | 260°C          |

| Storage Temperature Range               | –65°C to 150°C |

|                                         |                |

# ESD Ratings (Note 2)

• HBM (Human Body Model) ----- 2kV

# **Recommended Operating Conditions** (Note 3)

| Power Input Voltage, PVIN   | 1.6V to 18V |

|-----------------------------|-------------|

| • Supply Input Voltage, VIN | 4.5V to 18V |

# Thermal Information (Note 4 and Note 5)

|                     | Thermal Parameter                                       | WQFN-14AL 3.5x3.5 | Unit |

|---------------------|---------------------------------------------------------|-------------------|------|

| θJΑ                 | Junction-to-ambient thermal resistance (JEDEC standard) | 38.2              | °C/W |

| $\theta$ JC(Top)    | Junction-to-case (top) thermal resistance               | 34.3              | °C/W |

| $\theta$ JC(Bottom) | Junction-to-case (bottom) thermal resistance            | 1.9               | °C/W |

| $\theta$ JA(EVB)    | Junction-to-ambient thermal resistance (specific EVB)   | 31.1              | °C/W |

| <b>Ψ</b> ЈС(Тор)    | Junction-to-top characterization parameter              | 0.5               | °C/W |

| ΨЈВ                 | Junction-to-board characterization parameter            | 20.7              | °C/W |

# **Electrical Characteristics**

(V<sub>IN</sub> = 4.5V to 18V, V<sub>PVIN</sub> = 1.6V to 18V,  $T_A = T_J = -40^{\circ}C$  to 150°C, unless otherwise specified)

| Parameter                                     | Symbol             | Test Conditions                                                     | Min   | Тур  | Max   | Unit   |  |

|-----------------------------------------------|--------------------|---------------------------------------------------------------------|-------|------|-------|--------|--|

| Supply Voltage                                |                    |                                                                     |       |      |       |        |  |

| PVIN Power Input<br>Operating Voltage         | PVIN               |                                                                     | 1.6   |      | 18    |        |  |

| VIN Supply Input<br>Operating Voltage         | VIN                |                                                                     | 4.5   |      | 18    | V      |  |

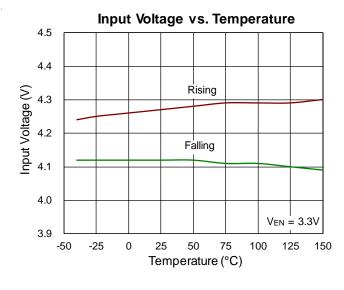

| Under-Voltage Lockout<br>Threshold            | Vuvlo              | V <sub>IN</sub> Rising                                              |       | 4    | 4.5   |        |  |

| Under-Voltage Lockout<br>Threshold Hysteresis | ΔV <sub>UVLO</sub> |                                                                     |       | 150  | 1     | mV     |  |

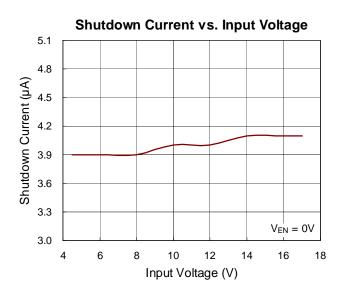

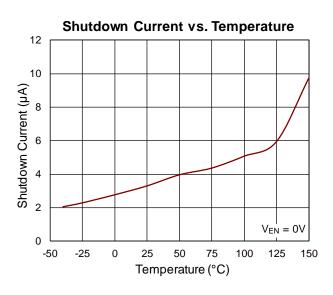

| VIN Shutdown Current                          |                    | $V_{EN} = 0V$ , $T_A = T_J = -40^{\circ}C$ to $85^{\circ}C$         |       | 3    | 9     |        |  |

| VIIN Shuldown Current                         |                    | $V_{EN} = 0V$                                                       |       | 3    | 11    | μΑ     |  |

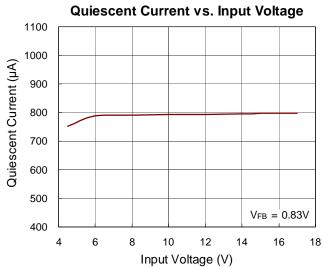

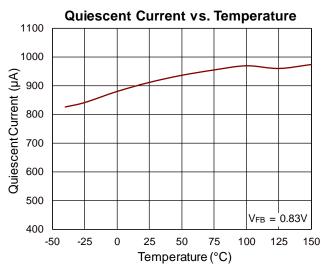

| VIN Quiescent Current                         |                    | V <sub>FB</sub> = 0.83V, Not Switching                              |       | 600  | 1000  |        |  |

| Enable Voltage                                |                    |                                                                     |       |      |       |        |  |

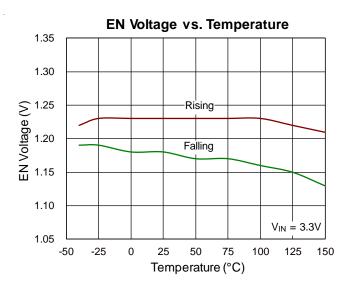

|                                               | V <sub>IH</sub>    | V <sub>EN</sub> Rising                                              |       | 1.21 | 1.26  |        |  |

| EN Threshold Voltage                          | V/                 | $V_{EN}$ Falling, $T_A = T_J = -40^{\circ}C$ to $85^{\circ}C$       | 1.1   | 1.17 | -     | V      |  |

|                                               | VIL                | V <sub>EN</sub> Falling                                             | 1.0   | 1.17 |       |        |  |

| Pull-Up Current                               |                    | V <sub>EN</sub> = 1.1V                                              |       | 1    |       | ^      |  |

| Hysteresis Current                            |                    | V <sub>EN</sub> = 1.3V                                              |       | 3    | 1     | μΑ     |  |

| Reference Voltage                             |                    |                                                                     |       |      |       |        |  |

| Reference Voltage                             | \/                 | $T_A = T_J = -40^{\circ}C$ to $85^{\circ}C$                         | 0.792 | 0.8  | 0.808 | V      |  |

| Neierence voltage                             | V <sub>REF</sub>   |                                                                     | 0.788 | 0.8  | 0.812 |        |  |

| Timing Resistor and Ex                        | xternal Cloc       | K                                                                   |       |      |       |        |  |

|                                               | face               | $R_{OSC} = 27k\Omega$ , $T_A = T_J = -40^{\circ}C$ to $85^{\circ}C$ | 1440  | 1600 | 1760  |        |  |

| Switching Frequency                           |                    | $R_{OSC} = 27k\Omega$                                               | 1400  | 1600 | 1760  |        |  |

| Switching Frequency                           | fosc               | $Rosc = 110k\Omega$                                                 | 400   | 480  | 560   | kHz    |  |

|                                               |                    | $R_{OSC} = 270k\Omega$                                              | 160   | 200  | 240   | 11112  |  |

| Switching Frequency<br>Range                  |                    | Include Sync mode and RT mode set point                             | 200   |      | 1600  |        |  |

| Minimum Sync Pulse<br>Width                   |                    |                                                                     |       | 20   |       | ns     |  |

| SYNC Threshold                                |                    | High-Level                                                          |       |      | 2     | V      |  |

| Voltage                                       |                    | Low-Level                                                           | 0.8   |      |       | V      |  |

| SYNC Falling Edge to LX Rising Edge Delay     |                    | Measure at 500kHz with R <sub>OSC</sub> resistor in series          |       | 66   |       | ns     |  |

| Internal MOSFET                               |                    |                                                                     |       |      |       |        |  |

| High-Side<br>On-Resistance                    | RDS(ON)_H          | V <sub>BOOT</sub> – V <sub>L</sub> X = 5.5V                         |       | 26   | 40    | mΩ     |  |

| Low-Side<br>On-Resistance                     | RDS(ON)_L          | V <sub>IN</sub> = 12V                                               |       | 19   | 30    | 1112.2 |  |

Copyright ©2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

| Parameter                                  | Symbol                | Test Conditions                                           | Min  | Тур  | Max | Unit              |

|--------------------------------------------|-----------------------|-----------------------------------------------------------|------|------|-----|-------------------|

| LX and BOOT                                | <u> </u>              |                                                           | 1    | •    | •   |                   |

| Minimum On-Time                            |                       | Measured at 90% to 90% of $V_{LX}$ , $I_{LX} = 2A$ , 25°C |      |      | 135 | ns                |

| Minimum Off-Time                           |                       | $V_{BOOT} - V_{LX} \ge 3V$                                |      | 0    |     |                   |

| BOOT-LX UVLO                               | V <sub>BL-U</sub> VLO |                                                           |      |      | 3   | V                 |

| Soft-Start and Tracking                    |                       |                                                           |      |      |     |                   |

| Internal Charge Current                    |                       |                                                           |      | 2    |     | μΑ                |

| SS to Feedback Offset                      |                       | Vss = 0.4V                                                |      | 20   | 60  | mV                |

| Current Limit                              |                       |                                                           |      |      |     |                   |

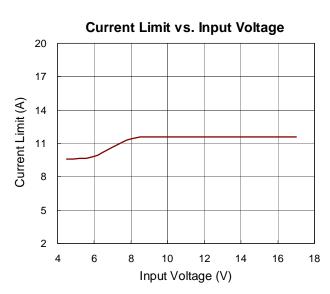

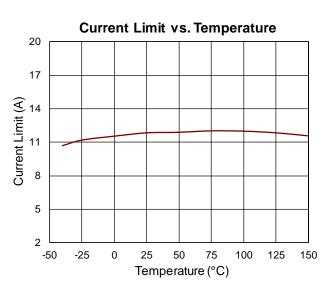

| High-Side Switch Current Limit             |                       |                                                           | 8    | 11   |     |                   |

| Low-Side Switch Sourcing                   |                       | $T_A = T_J = -40$ °C to 85°C                              | 7    | 10   |     |                   |

| Current Limit                              |                       |                                                           | 6.5  | 10   |     | A                 |

| Low-Side Switch Sinking<br>Current Limit   |                       |                                                           |      | 2.3  |     |                   |

| Error Amplifier                            |                       |                                                           | •    |      |     |                   |

| Error Amplifier<br>Trans-conductance       | gm                    | -2μA < I <sub>COMP</sub> < 2μA,<br>V <sub>COMP</sub> = 1V |      | 1300 |     | μΑ/V              |

| Error Amplifier DC Gain                    |                       | V <sub>FB</sub> = 0.8V                                    | 1000 | 3100 |     | V/V               |

| Error Amplifier<br>Sink/Source Current     |                       | V <sub>COMP</sub> = 1V, 100mV input overdrive             |      | ±110 |     | μА                |

| COMP to I <sub>switch</sub> gm             |                       |                                                           |      | 16   |     | A/V               |

| Power Good                                 |                       | L                                                         |      |      | l   | l                 |

| Power Good Rising                          |                       | V <sub>FB</sub> Rising (Good)                             |      | 94   |     |                   |

| Threshold                                  |                       | V <sub>FB</sub> Rising (Fault)                            |      | 109  |     | %V <sub>REF</sub> |

| Power Good Falling                         |                       | V <sub>FB</sub> Falling (Fault)                           |      | 91   |     |                   |

| Threshold                                  |                       | V <sub>FB</sub> Falling (Good)                            |      | 106  |     | %V <sub>REF</sub> |

| Power Good Sink Current<br>Capability      |                       | PGOOD signal fault, IPGOOD sinks 2mA                      |      |      | 0.3 | V                 |

| Power Good Leakage<br>Current              |                       | PGOOD signal good, VPGOOD = 5.5V                          |      | 30   | 100 | nA                |

| Minimum VIN for Indicating PGOOD           |                       | V <sub>PGOOD</sub> < 0.5V, I <sub>PGOOD</sub> sinks 100μA |      | 0.6  | 1   | .,                |

| Minimum SS/TR Voltage for Indicating PGOOD |                       |                                                           |      |      | 2.6 | V                 |

| Over-Temperature Protect                   | tion                  |                                                           |      |      | •   |                   |

| Thermal Shutdown                           | T <sub>SD</sub>       |                                                           | 160  | 175  |     |                   |

| Thermal Shutdown<br>Hysteresis             | ΔTsD                  |                                                           |      | 10   |     | °C                |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precautions are recommended.

- Note 3. The device is not guaranteed to function outside its operating conditions.

- **Note 4.** For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, AN061.

- Note 5.  $\theta_{JA(EVB)}$ ,  $\Psi_{JC(Top)}$  and  $\Psi_{JB}$  are measured on a high effective-thermal-conductivity four-layer test board which is in size of 70mm x 50mm; furthermore, each layer with 1 oz. Cu. Thermal resistance/parameter values may vary depending on the PCB material, layout, and test environmental conditions.

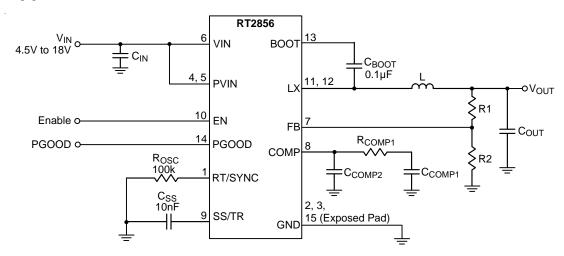

# **Typical Application Circuit**

**Table 1. Suggested Component Values**

| V <sub>OUT</sub> (V) | R1 (kΩ) | R2 (kΩ) | $R_{COMP1} \ (k\Omega)$ | C <sub>COMP1</sub> (nF) | C <sub>COMP2</sub> (pF) | C <sub>OUT</sub> (μF) | <b>L (</b> μ <b>H)</b> |

|----------------------|---------|---------|-------------------------|-------------------------|-------------------------|-----------------------|------------------------|

| 5.0                  | 126     | 24      | 4.3                     | 8.2                     | 180                     | 22 x 2                | 4.7                    |

| 3.3                  | 75      | 24      | 2.4                     | 8.2                     | 180                     | 22 x 2                | 3.7                    |

| 2.5                  | 51      | 24      | 1.8                     | 8.2                     | 180                     | 22 x 2                | 3.7                    |

| 1.8                  | 30      | 24      | 1.5                     | 8.2                     | 180                     | 22 x 2                | 2.2                    |

| 1.5                  | 21      | 24      | 1.0                     | 8.2                     | 180                     | 22 x 2                | 2.2                    |

| 1.2                  | 12      | 24      | 0.82                    | 8.2                     | 180                     | 22 x 2                | 2.2                    |

| 1.0                  | 6       | 24      | 0.68                    | 8.2                     | 180                     | 22 x 2                | 1.5                    |

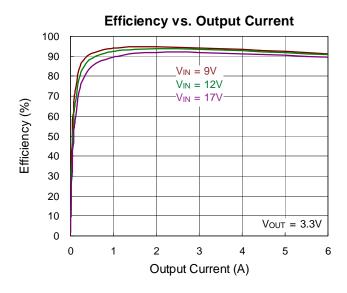

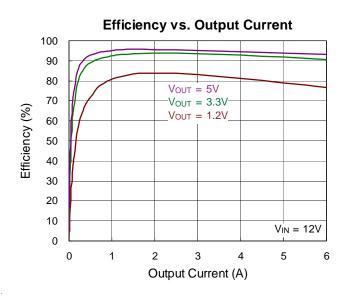

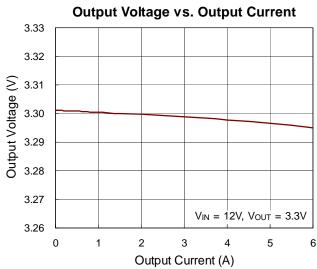

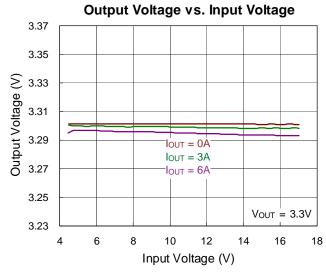

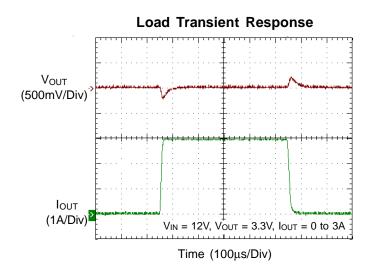

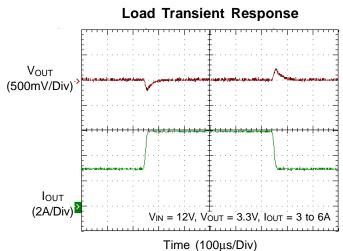

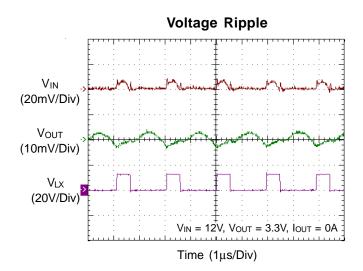

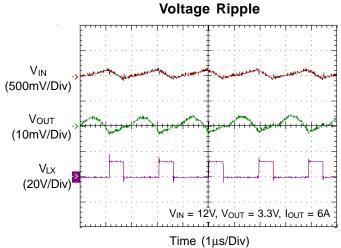

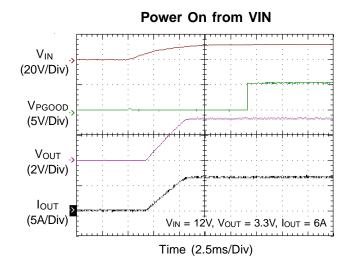

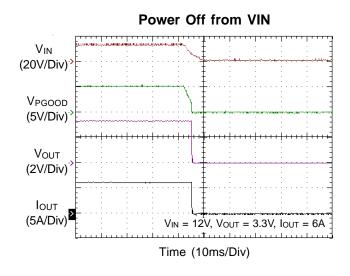

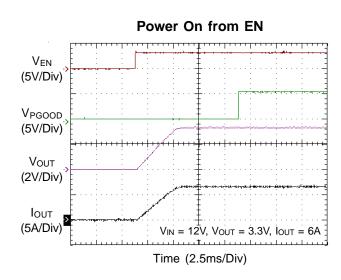

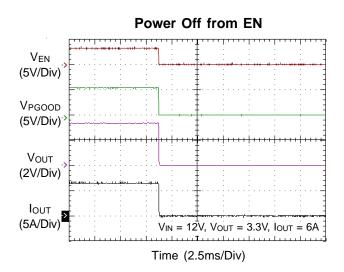

# **Typical Operating Characteristics**

Copyright ©2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Copyright ©2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Application Information**

This IC is a single phase Buck PWM converter with two integrated N-MOSFETs. It provides good performance during load and line transients by implementing a single feedback loop, current-mode control, and external compensation. The integrated synchronous power switches can increase efficiency and it is suitable for lower duty cycle applications. The switching frequency can be externally set from 200kHz to 1.6MHz, which allows for high efficiency and optimal size selection of output filter components. In addition, there is a synchronization mode control in this device which can be synchronized to the external clock frequency, and easily switched from internal switching mode to synchronization mode.

The device contains a power good protection and an external soft-start function that is able to monitor the system output voltage for normal regulation and provides a programmable power-up sequence for avoiding inrush currents efficiently. Furthermore, the device incorporates a lot of protections such as OVP, OCP, OTP and etc.

#### **Main Control Loop**

The device implements an adjustable fixed frequency with peak current-mode control which offers an excellent performance over various line and loading. During normal operation, the internal high-side power switch is turned on by the internal oscillator initiating. Current in the inductor increases until the high-side switch current reaches the current reference converted by the output voltage  $V_{\text{COMP}}$ of the error amplifier. The error amplifier adjusts its output voltage by comparing the feedback signal from a resistive voltage divider on the FB pin with an internal 0.8V reference. When the load current increases, it causes a reduction in the feedback voltage relative to the reference. The error amplifier increases its current reference until the average inductor current matches the new load current. When the high-side power MOSFET turns off, the lowside synchronous power switch (N-MOSFET) turns on until the beginning of the next clock cycle.

#### **VIN and PVIN Pins**

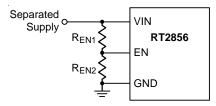

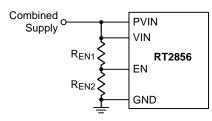

The VIN and PVIN pins can be used together or separately for a variety of applications. In this device, the VIN pin is an input for supplying internal reference and control circuitry, and the PVIN pin is an input for providing main power to device system and internal high-side power MOSFET. When the VIN and PVIN pins are tied together, both pins can operate from 4.5V to 18V. When the VIN and PVIN pins are used separately, VIN pin must be ranged from 4.5V to 18V, and the PVIN pin can be applied down to as low as 1.6V to 18V.

The device incorporates an internal under-voltage lockout (UVLO) circuitry on the VIN pin. If the VIN pin voltage exceeds the UVLO rising threshold voltage 4V, the converter resets and prepares the PWM for operation. If the VIN pin voltage falls below the falling threshold voltage 3.85V during normal operation, the device is disabled. Such wide internal UVLO hysteresis of 150mV can efficiently prevent noise-caused reset. There is also an external UVLO circuitry which can be achieved by configuring a resistive voltage divider on EN pin for both input VIN and PVIN pins and it is able to provide either input pins an adjustable UVLO function to ensure a proper power-up behavior. More discussions are provided in the section of Enable Operation.

### **Output Voltage Setting**

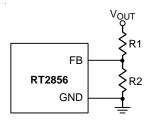

The resistive voltage divider allows the FB pin to sense the output voltage as shown in Figure 1.

Figure 1. Setting the Output Voltage

For high efficiency, the divider resistance must adopt larger values, but too large values may induce noises and voltage errors by the coupled FB pin input current. It is recommended to use the values between  $10k\Omega$  and 100k $\Omega$ . The output voltage is set by an external resistive voltage divider according to the following Equation (1):

$$V_{OUT} = V_{REF} \left( 1 + \frac{R1}{R2} \right)$$

(1)

where V<sub>REF</sub> is the feedback reference voltage (0.8V typ.).

#### Soft-Start

The device contains an external soft-start clamp that gradually raises the output voltage. The soft-start timing is programmed by the external capacitor between SS/TR pin and GND. The device provides an internal 2μA charge current for the external capacitor. If a 10nF capacitor is used to set the soft-start, the period can be 4ms. The calculations for external charge capacitor CSS and softstart time T<sub>SS</sub> are shown in Equation (2):

$$T_{SS} = \frac{C_{SS} \times V_{REF}}{I_{SS}}$$

(2)

where C<sub>SS</sub> is the external soft-start capacitor, I<sub>SS</sub> is the soft-start charge current (2µA), V<sub>REF</sub> is the feedback reference voltage (0.8V).

Once the input voltage falls below UVLO threshold, the EN pin is pulled low, or the OTP is triggered, the device stops switching and the SS/TR pin starts to discharge. It is held in such shutdown condition until the event is cleared and the SS/TR pin has already discharged to ground to ensure proper soft-start behavior.

During the pre-biased start-up sequence, the output of device is not discharged by low-side power switch because the device is designed to prevent low-side MOSFET sinking. It is allowed to sink when the SS/TR pin exceeds 2.1V.

### **Slope Compensation**

Slope compensation provides stability in constant frequency architectures by preventing sub-harmonic oscillations at duty cycles greater than 50%. It is accomplished internally by adding a compensating ramp to the inductor current signal. Normally, the peak inductor current is remained constant under the whole duty cycle range when slope compensation is added. For the device,

separated inductor current signal is used to monitor overcurrent condition, so the maximum output current stays relatively constant regardless of duty cycle. More discussions about over-current protection are described in the following sections.

### **Enable Operation**

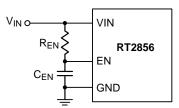

The EN pin is an device enable input. Pulling the EN pin to logic low (typically less than the set threshold voltage 1.17V), the device shuts down and enters to low quiescent current state about 2µA. The regulator starts switching again once the EN pin voltage exceeds the threshold voltage 1.21V. In addition, the EN pin is implemented with an internal pull-up current source which allows to enable the device when the EN pin is floating. For general external timing control, the EN pin can be externally pulled high by adding a capacitor and a resistor from the VIN pin as shown in Figure 2.

Figure 2. Enable Timing Control

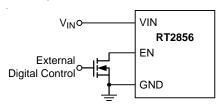

An external MOSFET can be added to implement digital control from the EN pin to ground, as shown in Figure 3. In this case, there is no need to connect a pull-up resistor between the VIN and EN pins since the EN pin is pulled up by the internal current source. The device can simply achieve the digital control only through an external MOSFET on EN pin.

Figure 3. Digital Enable Control

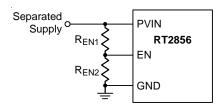

The EN pin can also be applied to adjust its under-voltage lockout (UVLO) threshold with two external resistors divider from the both input VIN and PVIN pins used together or separately, and the application structures are shown in Figure 4, Figure 5, and Figure 6.

Figure 4. Resistor Divider for PVIN UVLO Setting

Figure 5. Resistor Divider for VIN UVLO Setting,  $VIN \ge 4.5V$

Figure 6. Resistor Divider for PVIN and VIN UVLO Setting

Under above application structures, the adjustable UVLO function of EN pin allows to achieve a secondary UVLO on PVIN pin, a higher UVLO on VIN pin or even a common UVLO on both VIN and PVIN pins. For example, if the EN pin is configured as Figure 5 and the output voltage is set to a higher value 10V, the device may shut down after soft-start sequence is over, and the reason is that the V<sub>OUT</sub> is still lower than its set target during the V<sub>IN</sub> rising period even though V<sub>IN</sub> has already risen to its internal UVLO threshold 4V. To prevent this situation, an adjustable UVLO threshold from EN pin is useful to avoid such high output transfer condition. The exact UVLO thresholds can be calculated by Equation (3). The setting V<sub>OUT</sub> is 10V and V<sub>IN</sub> is from 0V to 18V. When V<sub>IN</sub> is higher than 12V, the device is triggered to enable the converter. Assume  $R_{EN1} = 56k\Omega$ . Then,

$$R_{EN2} = \frac{R_{EN1} \times V_{IH}}{V_{IN} S - V_{IH}}$$

(3)

where  $V_{IH}$  is the typical threshold of enable rising (1.21V) and  $V_{IN\_S}$  is the target turn on input voltage (12V in this example). According to the equation, the suggested resistor  $R_{EN2}$  is  $6.28k\Omega$ .

### Adjustable Operating Frequency-RT mode

Selection of the operating frequency is a tradeoff between efficiency and component size. Higher operating frequency allows the use of smaller inductor and capacitor values but it may compress the minimum controllable on-time to affect devices stability. Lower operating frequency improves efficiency by reducing internal gate charge and switching losses but requires larger inductance and capacitance to maintain low output ripple voltage.

The operating frequency of the device is determined by an external resistor  $R_{\rm OSC}$ , that is connected between the RT/SYNC pin and ground. The value of the resistor sets the ramp current which is used to charge and discharge an internal timing capacitor within the oscillator. The practical switching frequency ranges from 200kHz to 1.6MHz. Determine the  $R_{\rm OSC}$  resistor value by examining the curve in Figure 7.

Figure 7. Switching Frequency vs. Rosc Resistor

#### Synchronization-SYNC mode

The device is allowed to synchronize with an external square wave clock ranging from 200kHz to 1.6MHz applied to the RT/SYNC pin. The range of sync duty cycle must be from 20% to 80%, and the amplitude of sync signal must be higher than 2V and lower than 0.8V. During the SYNC mode operation, the switching cycle of LX pin is synchronized to the falling edge of the external sync signal.

Copyright ©2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Before the external sync signal is provided to the RT/ SYNC pin, the device operates at the original switching frequency set by resistor R<sub>OSC</sub>. When the sync signal is provided, the SYNC mode overrides the RT mode to force the device synchronizing to external frequency. This IC can easily switch between RT mode and SYNC mode, and the application structure can be configured as Figure 8.

Figure 8. External Sync Signal Control

### **Power Good Output**

The power good output is an open-drain output and needs to connect a voltage source below 5.5V with a pull-up resistor for avoiding the PGOOD floating. When the output voltage is 9% above or 9% below its set voltage, PGOOD is pulled low. It is held low until the output voltage returns within the allowed tolerances ±6% once more. During softstart, PGOOD is actively held low when V<sub>IN</sub> is greater than 1V and is only allowed to be high when soft-start period is over, that means the SS/TR pin exceeds 2.1V typically and the output voltage reaches 94% of its set voltage. Besides, the PGOOD pin is also pulled low when the input UVLO or OVP is triggered, EN pin is pulled below 1.21V or the OTP occurs.

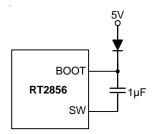

#### **External Bootstrap Diode**

Connect a 100nF low-ESR ceramic capacitor between the BOOT and SW pins. This capacitor provides the gate driver voltage for the high-side MOSFET.

It is recommended to add an external bootstrap diode between an external 5V and the BOOT pin for efficiency improvement when input voltage is lower than 5.5V or duty ratio is higher than 65% .The bootstrap diode can be a low-cost one such as IN4148 or BAT54. The external 5V can be a 5V fixed input from system or a 5V output of the RT2856. Note that the external boot voltage must be lower than 5.5V.

Figure 9. External Bootstrap Diode

#### **Inductor Selection**

For a given input and output voltage, the inductor value and operating frequency determine the ripple current. The ripple current ∆I<sub>L</sub> increases with higher VIN and decreases with higher inductance.

$$\Delta I_{L} = \left[\frac{V_{OUT}}{f \times L}\right] \times \left[1 - \frac{V_{OUT}}{V_{IN}}\right]$$

(4)

Having a lower ripple current reduces not only the ESR losses in the output capacitors but also the output voltage ripple. Highest efficiency operation is achieved by reducing ripple current at low frequency, but it requires a large inductor to attain this goal.

For the ripple current selection, the value of  $\Delta I_{L} = 0.24$ (I<sub>MAX</sub>) is a reasonable starting point. The largest ripple current occurs at the highest V<sub>IN</sub>. To guarantee that the ripple current stays below a specified maximum, the inductor value should be chosen according to the following equation:

$$L = \left[\frac{V_{OUT}}{f \times \Delta I_{L(MAX)}}\right] \times \left[1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right]$$

(5)

In this device, 3.7µH is recommended for initial design. The current rating of the inductor (caused a 40°C temperature rising from 25°C ambient) must be greater than the maximum load current and ensure that the peak current does not saturate the inductor during short-circuit condition. Referring to Table 1 for the inductor selection reference.

Table 1. Suggested Inductors for Typical **Application Circuit**

| Component<br>Supplier | Series   | Dimensions (mm)   |  |  |

|-----------------------|----------|-------------------|--|--|

| TDK                   | VLF10045 | 10 x 9.7 x 4.5    |  |  |

| TDK                   | SLF12565 | 12.5 x 12.5 x 6.5 |  |  |

| TAIYO YUDEN           | NR8040   | 8 x 8 x 4         |  |  |

| WE                    | 744325   | 10.2 x 10.2 x 4.7 |  |  |

| WE                    | 744355   | 12.8 x 12.8 x 6.2 |  |  |

Copyright ©2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

### Input and Output Capacitors Selection

The input capacitance  $C_{\text{IN}}$  is needed to filter the trapezoidal current at the Source of the high-side MOSFET. To prevent large ripple current, a low ESR input capacitor sized for the maximum RMS current should be used. The RMS current is given by Equation (6):

$$I_{RMS} = I_{OUT(MAX)} \frac{V_{OUT}}{V_{IN}} \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$$

(6)

The formula above has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT} / 2$ . This simple worst condition is commonly used for design because even significant deviations do not offer much relief.

Choose a capacitor rated at a higher temperature than required. Several capacitors may also be paralleled to meet size or height requirements in the design. For the input capacitor, two  $10\mu F$  and one  $4.7\mu F$  low-ESR ceramic capacitors are recommended for bypassing the PVIN pin and VIN pin respectively and an additional  $0.1\mu F$  is recommended to be placed as close as possible to the IC input side for high frequency filtering. For all the recommended input and output capacitors, refer to Table 2 for more details.

| Table | e 2. Su | ggested | Cap | oacitors | for ( | CIN | and | C <sub>OUT</sub> |

|-------|---------|---------|-----|----------|-------|-----|-----|------------------|

|       |         |         |     |          |       |     | _   |                  |

| Location         | Component Supplier | Part No.       | Capacitance (μF) | Case Size |

|------------------|--------------------|----------------|------------------|-----------|

| C <sub>IN</sub>  | MURATA             | GRM32ER71C226M | 22               | 1210      |

| C <sub>IN</sub>  | TDK                | C3225X5R1C226M | 22               | 1210      |

| C <sub>OUT</sub> | MURATA             | GRM31CR60J476M | 47               | 1206      |

| C <sub>OUT</sub> | TDK                | C3225X5R0J476M | 47               | 1210      |

| C <sub>OUT</sub> | MURATA             | GRM32ER71C226M | 22               | 1210      |

| C <sub>OUT</sub> | TDK                | C3225X5R1C226M | 22               | 1210      |

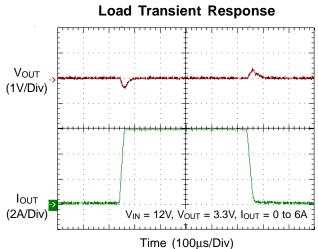

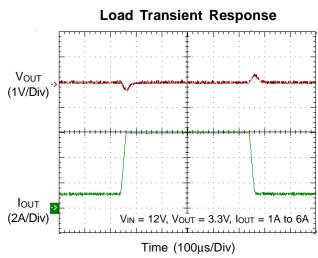

The selection of  $C_{OUT}$  is determined by the required ESR to minimize voltage ripple. Moreover, the amount of bulk capacitance is also a key for  $C_{OUT}$  selection to ensure that the control loop is stable. Loop stability can be checked by viewing the load transient response. The output ripple  $\Delta V_{OUT}$  is determined by Equation (7):

$$\Delta V_{OUT} \le \Delta I_{L} \left[ ESR + \frac{1}{8fC_{OUT}} \right]$$

(7)

Higher values, lower cost ceramic capacitors are now becoming available in smaller case sizes. Their high ripple current, high voltage rating and low ESR make them ideal for switching regulator applications. However, care must be taken when these capacitors are used at input and output. When a ceramic capacitor is used at the input and the power is supplied by a wall adapter through long wires, a load step at the output can induce ringing at the input  $V_{IN}$ . At best, this ringing can coupled to the output and be mistaken as loop instability. At worst, a sudden inrush of current through the long wires can potentially cause a voltage spike at  $V_{IN}$  large enough to damage the part.

### **Level Frequency Shift**

While the FB pin drops, switching frequency is proportional to the feedback voltage, this is a level frequency reduced function implemented in the device. For the same short-circuit example, when the output voltage drops during over-current condition, the switching frequency is reduced in direct proportion to the output voltage, so the low-side MOSFET is turned off long enough to reduce the inductor current to prevent a current runaway issue. With function of level frequency reducing, the switching frequency can reduce from 100%, 50%, then 25% as the voltage decreases from 0.8V to 0V on FB pin. The principle of level frequency reducing is also allowed to cover the soft-start sequence to increase the switching frequency as feedback voltage increases from 0V to 0.8V.

### **Output Over-Voltage Protection**

The device provides an output over-voltage protection (OVP) once the output voltage exceeds 109% of  $V_{OUT}$ , the OVP function turns off the high-side power MOSFET

Copyright ©2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

to stop current flowing to the output which can only be released when the output voltage drops below 106% of V<sub>OUT</sub>. There is a 5μs delay also built into the over-voltage protection circuit to prevent false transition. Using this OVP feature can easily minimize the output overshoot.

## **High-Side MOSFET Over-Current Protection**

The over-current protection (OCP) of high-side MOSFET is implemented in this device; it adopts monitoring inductor current during the on-state to control the COMP pin voltage for turning off the high-side MOSFET. Each cycle, the separated inductor current signal is compared through sensing the external inductor current to the COMP pin voltage from an error amplifier output. If the separated inductor current peak value exceeds the set current-limit threshold, the high-side power switch is turned off.

#### **Low-Side MOSFET Over-Current Protection**

The device not only implements the high-side over-current protection but also provides the over-sourcing current protection and over-sinking current protection for low-side MOSFET. With these three current protections, the IC can easily control inductor current at both side power switches and avoid current runaway for short-circuit condition.

For the sourcing current protection, there is a specific comparator in internal circuitry to compare the low-side MOSFET sourcing current to the internal set current limit at the end of every clock cycle. When the low-side sourcing current is higher than the set sourcing limit, the high-side power switch is not turned on and low-side power switch is kept on until the following clock cycle, for releasing the above sourcing current to the load. It is allowed to turn on the high-side MOSFET again when the low-side current is lower than the set sourcing current limit at the beginning of a new cycle.

For the sinking current protection, it is implemented by detecting the voltage across the low-side power switch. If the low-side reverse current exceeds the set sinking limit, both power switches are off immediately, and it is held to stop switching until the beginning of next cycle. By

incorporating this additional protection, the device is able to prevent an excessive sinking current from the load during the condition of pre-biased output and the SS/TR pin is asserted high (that is, 2.1V or above).

### **Over-Temperature Protection**

An over-temperature protection (OTP) is contained in the device. The protection is triggered to force the device shutdown for protecting itself when the junction temperature exceeds 175°C typically. Once the junction temperature drops below the hysteresis 10°C typically, the device is re-enable and automatically reinstates the power-up sequence.

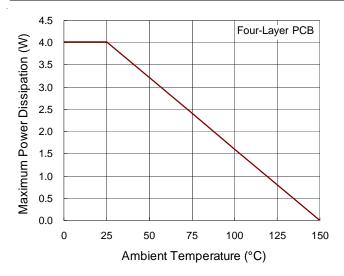

#### Thermal Considerations

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA(EVB)}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA(EVB)}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 150°C. The junction to ambient thermal resistance,  $\theta_{JA(EVB)}$ , is layout dependent. For WQFN-14AL 3.5x3.5 package, the thermal resistance,  $\theta_{JA(EVB)}$ , is 31.1°C/W on high effective-thermal-conductivity four-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}$ C can be calculated by the following formula:

$P_{D(MAX)} = (150^{\circ}C - 25^{\circ}C) / (31.1^{\circ}C/W) = 4.01W$  for WQFN-14AL 3.5x3.5 package

The maximum power dissipation depends on the operating ambient temperature for fixed T<sub>J(MAX)</sub> and thermal resistance,  $\theta_{JA(EVB)}$ . The derating curve in Figure 10 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 10. Derating Curve of Maximum Power Dissipation

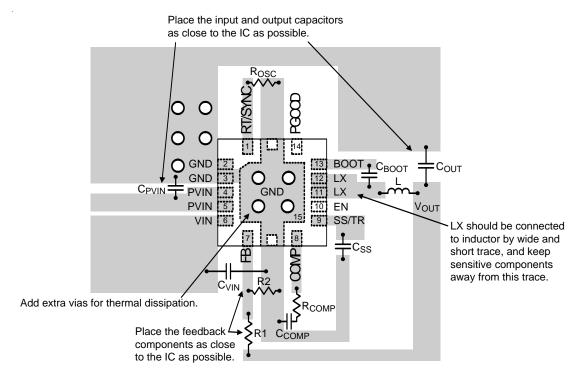

### **Layout Considerations**

Follow the PCB layout guidelines for optimal performance of the device.

- Keep the traces of the main current paths as short and wide as possible.

- Put the input capacitor as close as possible to VIN and PVIN pins.

- ▶ LX node is with high frequency voltage swing and should be kept at small area. Keep analog components away from the LX node to prevent stray capacitive noise pickup.

- Connect feedback network behind the output capacitors.

Keep the loop area small. Place the feedback components near the device.

- Connect all analog grounds to a common node and then connect the common node to the power ground behind the output capacitors.

- An example of PCB layout guide is shown in Figure 11 for reference.

Figure 11. PCB Layout Guide

Copyright ©2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

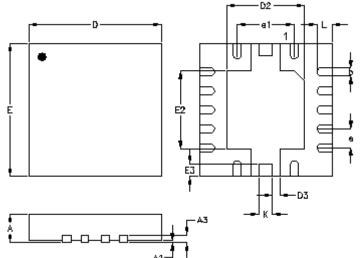

# **Outline Dimension**

**DETAIL A**Pin #1 ID and Tie Bar Mark Options

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min.         | Max.          | Min.                 | Max.  |  |

| А      | 0.700        | 0.800         | 0.028                | 0.031 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002 |  |

| А3     | 0.175        | 0.250         | 0.007                | 0.010 |  |

| b      | 0.200        | 0.300         | 0.008                | 0.012 |  |

| D      | 3.400        | 3.600         | 0.134                | 0.142 |  |

| D2     | 2.000        | 2.100         | 0.079                | 0.083 |  |

| D3     | 0.2          | 200           | 0.0                  | 008   |  |

| E      | 3.400        | 3.600         | 0.134                | 0.142 |  |

| E2     | 2.000        | 2.100         | 0.079                | 0.083 |  |

| E3     | 0.3          | 325           | 0.0                  | )13   |  |

| е      | 0.500        |               | 0.020                |       |  |

| e1     | 1.5          | 500           | 0.0                  | )59   |  |

| К      | 0.350        |               | 0.0                  | )14   |  |

| L      | 0.350        | 0.450         | 0.014                | 0.018 |  |

W-Type 14AL QFN 3.5x3.5 Package