# Single Phase Synchronous Rectified Buck MOSFET Driver

### **General Description**

The RT9624G is a high frequency, synchronous rectified, single phase MOSFET driver designed for normal MOSFET driving applications and high performance CPU VR driving capabilities.

The RT9624G can be supplied from 4.5V to 13.2V. The applicable power stage VIN range is from 5V to 24V. The RT9624G also builds in an internal power switch to replace external bootstrap diode.

The RT9624G can support switching frequency efficiently up to 500kHz. The RT9624G has both UGATE and LGATE driving circuits for synchronous rectified DC/DC converter applications. The shoot through protection mechanism is designed to prevent shoot through between high-side and low-side power MOSFETs. The RT9624G has tri-state PWM input with shutdown and EN input shutdown functions, which can force driver to output low UGATE and LGATE signals.

The RT9624G is available in a small footprint WDFN-8SL 2x2 package.

### Features

- Drive Two N-MOSFETs

- Shoot-Through Protection

- Embedded Bootstrap Switch

- Support High Switching Frequency

- Fast Output Rising Time

- Tri-State PWM Input for Output Shutdown

- Enable Control

- Small 8-Lead WDFN Package

- RoHS Compliant and Halogen Free

### Applications

- Core Voltage Supplies for Desktop, Motherboard CPU

- High Frequency Low Profile DC/DC Converters

- High Current Low Voltage DC/DC Converters

- Core Voltage Supplies for GFX Card

### **Marking Information**

2AW

2A : Product Code W : Date Code

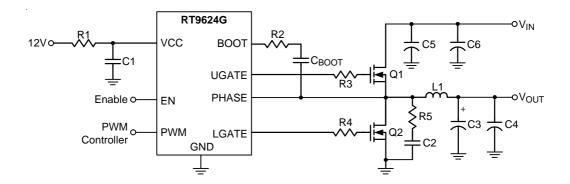

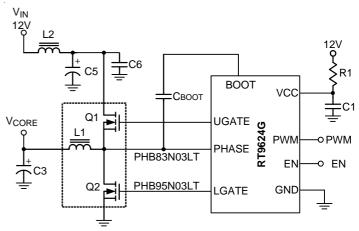

### **Simplified Application Circuit**

### **Ordering Information**

RT9624G 🗖 📮

Package Type QWA : WDFN-8SL 2x2 (W-Type) (Exposed Pad-Option 1)

Lead Plating System

G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

**Function Pin Description**

### Pin Configurations

(TOP VIEW)

| BOOT 11 00<br>PWM EN CC C | UGATE<br>PHASE<br>GND<br>LGATE |

|---------------------------|--------------------------------|

|---------------------------|--------------------------------|

WDFN-8SL 2x2

| Pin No.               | Pin Name | Pin Function                                                                                                |

|-----------------------|----------|-------------------------------------------------------------------------------------------------------------|

| 1                     | BOOT     | Bootstrap Supply for High-Side Gate Driver.                                                                 |

| 2                     | PWM      | PWM Signal Input. Connect this pin to the PWM output of the controller.                                     |

| 3                     | EN       | Enable Control Input (Active High). When this pin is low, both UGATE and LGATE are driven to low.           |

| 4                     | VCC      | Supply Voltage Input.                                                                                       |

| 5                     | LGATE    | Low-Side Gate Driver Output. Connect this pin to the Gate of low-side power N-MOSFET.                       |

| 6,<br>9 (Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation. |

| 7                     | PHASE    | Connect this pin to the Source of the high-side N-MOSFET and the Drain of the low-side N-MOSFET.            |

| 8                     | UGATE    | High-Side Gate Driver Output. Connect this pin to the Gate of high-side power N-MOSFET.                     |

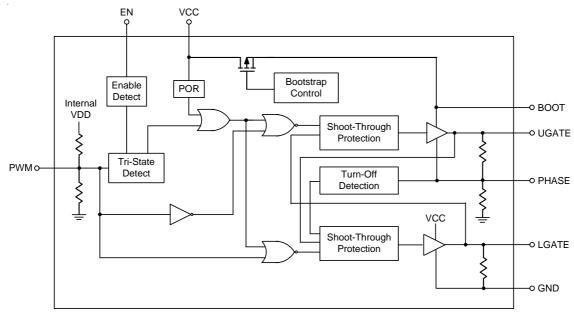

### **Function Block Diagram**

### Operation

### POR (Power On Reset)

The POR block detects the voltage at the VCC pin. When the VCC pin voltage is higher than POR rising threshold, the POR block output is high. The POR output is low when VCC is less than POR rising threshold. When the POR block output is high, UGATE and LGATE can be controlled by PWM input voltage. If the POR block output is low, both UGATE and LGATE will be pulled to low.

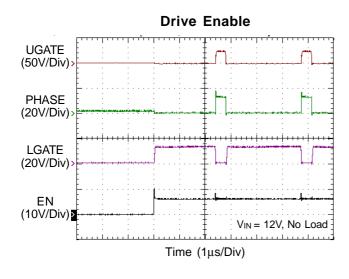

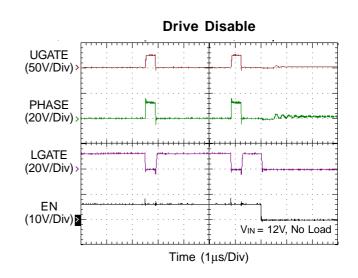

#### **Enable Detect**

When EN pin input voltage is higher than EN rising threshold, MOSFET driver is enabled. When the EN input and POR output are high, UGATE and LGATE can be controlled by PWM input voltage. When EN input is low, both UGATE and LGATE are pulled to low.

#### **Tri-State Detect**

When both POR block output and EN pin voltages are high, UGATE and LGATE can be controlled by PWM input. There are three PWM input modes, which are high, low, and shutdown state. If PWM input is within the shutdown window, both UGATE and LGATE output are low. When PWM input is higher than its rising threshold, UGATE is high and LGATE is low. When PWM input is lower than its falling threshold, UGATE is low and LGATE is high.

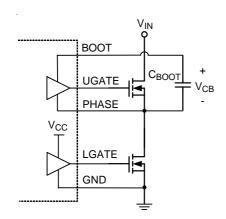

#### **Bootstrap Control**

The bootstrap control block controls the integrated bootstrap switch. When LGATE is high (low-side MOSFET is turned on), the bootstrap switch is turned on to charge the bootstrap capacitor connected to BOOT pin. When LGATE is low (low-side MOSFET is turned off), the bootstrap switch is turned off to disconnect VCC pin and BOOT pin.

#### **Turn-Off Detection**

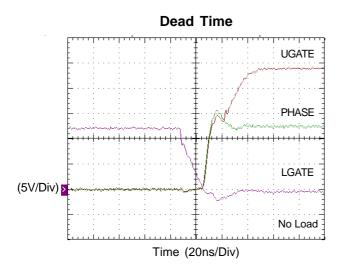

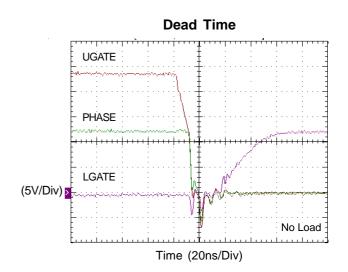

The turn-off detection block detects whether high-side MOSFET is turned off by monitoring the PHASE pin voltage. To avoid shoot-through between high-side and low-side MOSFETs, low-side MOSFET can be turned on only after high-side MOSFET is effectively turned off.

#### **Shoot-Through Protection**

The shoot-through protection block implements the dead time when both high-side and low-side MOSFETs are turned off. With shoot-through protection block, high-side and low-side MOSFET are never turned on simultaneously. Thus, shoot-through between high-side and low-side MOSFETs is prevented.

### Absolute Maximum Ratings (Note 1)

| Supply Voltage, VCC                            | 0.3V to 15V                                               |

|------------------------------------------------|-----------------------------------------------------------|

| BOOT to PHASE                                  | - –0.3V to 15V                                            |

| PHASE to GND                                   |                                                           |

| DC                                             | 0.3V to 30V                                               |

| < 100ns                                        | 10V to 35V                                                |

| LGATE to GND                                   |                                                           |

| DC                                             | 0.3V to (VCC + 0.3V)                                      |

| < 100ns                                        | 2V to (VCC + 0.3V)                                        |

| UGATE to GND                                   |                                                           |

| DC                                             | - ( $V_{PHASE} - 0.3V$ ) to ( $V_{BOOT} + 0.3V$ )         |

| < 100ns                                        | - (V <sub>PHASE</sub> – 2V) to (V <sub>BOOT</sub> + 0.3V) |

| • EN, PWM to GND                               | 0.3V to 7V                                                |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                                                           |

| WDFN-8SL 2x2                                   | - 2.17W                                                   |

| Package Thermal Resistance (Note 2)            |                                                           |

| WDFN-8SL 2x2, $\theta_{JA}$                    | - 46°C/W                                                  |

| WDFN-8SL 2x2, $\theta_{JC}$                    | - 11.5°C/W                                                |

| • Lead Temperature (Soldering, 10 sec.)        | - 260°C                                                   |

| Junction Temperature                           | - 150°C                                                   |

| Storage Temperature Range                      | - –65°C to 150°C                                          |

| ESD Susceptibility (Note 3)                    |                                                           |

| HBM (Human Body Model)                         | - 2kV                                                     |

### Recommended Operating Conditions (Note 4)

| Supply Voltage, VCC                      | - 4.5V to 13.2V |

|------------------------------------------|-----------------|

| • Input Voltage, (V <sub>IN</sub> + VCC) | - < 35V         |

| Junction Temperature Range               | 40°C to 125°C   |

| Ambient Temperature Range                | 40°C to 85°C    |

### **Electrical Characteristics**

(V\_{CC} = 12V, T\_A = 25^{\circ}C unless otherwise specified)

| Parameter             | Symbol             | Test Conditions                 | Min | Тур | Max  | Unit |  |

|-----------------------|--------------------|---------------------------------|-----|-----|------|------|--|

| Power Supply          |                    |                                 |     |     |      |      |  |

| Power Supply Voltage  | V <sub>CC</sub>    |                                 | 4.5 |     | 13.2 | V    |  |

| Power Supply Current  | Ivcc               | VBOOT = 12V, PWM Input Floating |     | 120 |      | μΑ   |  |

| Power On Reset (POR)  |                    |                                 |     |     |      |      |  |

| POR Rising Threshold  | V <sub>POR_r</sub> | V <sub>CC</sub> Rising          |     | 4   | 4.4  | V    |  |

| POR Falling Threshold | V <sub>POR_f</sub> | V <sub>CC</sub> Falling         | 3   | 3.5 |      | V    |  |

| EN Input              |                    |                                 |     |     |      |      |  |

| EN Rising Threshold   | V <sub>ENH</sub>   |                                 |     | 1.3 | 1.6  | V    |  |

| EN Falling Threshold  | V <sub>ENL</sub>   |                                 | 0.7 | 1   |      | V    |  |

| Parameter               | Symbol                 | Test Conditions                                     | Min | Тур | Max | Unit |

|-------------------------|------------------------|-----------------------------------------------------|-----|-----|-----|------|

| PWM Input               | 1                      |                                                     |     |     |     |      |

| Maximum Input Current   | IPWM                   | PWM = 0V or 5V                                      |     | 160 |     | μA   |

| PWM Floating Voltage    | V <sub>PWM_fl</sub>    | PWM = Open                                          |     | 1.8 |     | V    |

| PWM Rising Threshold    | VPWM_rth               |                                                     | 2.3 | 2.8 | 3.2 | V    |

| PWM Falling Threshold   | VPWM_fth               |                                                     | 0.7 | 1.1 | 1.4 | V    |

| Timing                  |                        |                                                     |     |     |     |      |

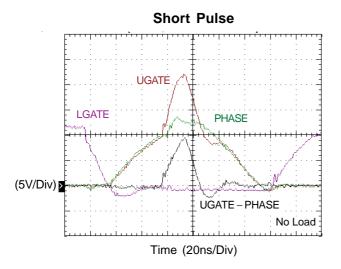

| UGATE Rising Time       | t <sub>UGATEr</sub>    | 3nF Load                                            |     | 25  |     | ns   |

| UGATE Falling Time      | tUGATEf                | 3nF Load                                            |     | 12  |     | ns   |

| LGATE Rising Time       | tlgater                | 3nF Load                                            |     | 24  |     | ns   |

| LGATE Falling Time      | tLGATEf                | 3nF Load                                            |     | 10  |     | ns   |

| UGATE Propagation Delay | t <sub>UGATEpdh</sub>  | V <sub>BOOT</sub> – V <sub>PHASE</sub> = 12V        |     | 60  |     | ns   |

|                         | tUGATEpdI              | See Timing Diagram                                  | 1   | 22  |     | 115  |

| LGATE Propagation Delay | tLGATE pdh             | See Timing Diagram                                  | 1   | 30  |     | 20   |

|                         | t <sub>LGATE pdl</sub> | See Timing Diagram                                  |     | 8   |     | ns   |

| Output                  |                        |                                                     |     |     |     |      |

| UGATE Drive Source      | R <sub>UGATEsr</sub>   | $V_{BOOT} - V_{PHASE} = 12V$ , $I_{Source} = 100mA$ |     | 1.7 |     | Ω    |

| UGATE Drive Sink        | R <sub>UGATEsk</sub>   | $V_{BOOT} - V_{PHASE} = 12V$ , $I_{Sink} = 100mA$   |     | 1.4 |     | Ω    |

| LGATE Drive Source      | R <sub>LGATEsr</sub>   | I <sub>Source</sub> = 100mA                         |     | 1.6 |     | Ω    |

| LGATE Drive Sink        | R <sub>LGATEsk</sub>   | I <sub>Sink</sub> = 100mA                           |     | 1.1 |     | Ω    |

**Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- **Note 2.**  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

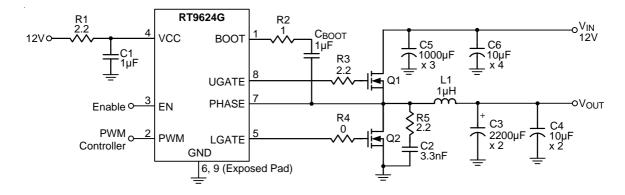

### **Typical Application Circuit**

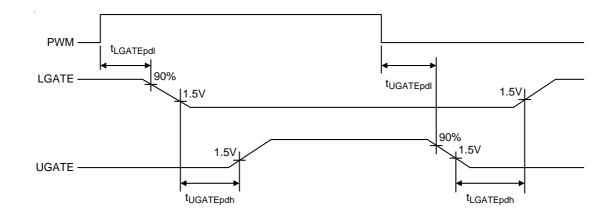

### **Timing Diagram**

### **Typical Operating Characteristics**

RICHTEK

### **Application Information**

The RT9624G is a high frequency, synchronous rectified, single phase dual MOSFET driver containing Richtek's advanced MOSFET driver technologies. The RT9624G is designed to be able to adapt from normal MOSFET driving applications to high performance CPU VR driving capabilities.

#### Supply Voltage and Power On Reset

The RT9624G can be utilized under both V<sub>CC</sub> = 5V or V<sub>CC</sub> = 12V applications which may happen in different fields of electronics application circuits. In terms of efficiency, higher V<sub>CC</sub> equals higher driving voltage of UGATE/LGATE which may result in higher switching loss and lower conduction loss of power MOSFETs. The choice of V<sub>CC</sub> = 12V or V<sub>CC</sub> = 5V can be a tradeoff to optimize system efficiency.

The RT9624G is designed to drive both high-side and lowside N-MOSFET through external input PWM control signal. It has power on protection function which held UGATE and LGATE low before the VCC voltage rises to higher than rising threshold voltage.

#### Enable and Disable

The RT9624G includes an EN pin for sequence control. When the EN pin rises above the V<sub>ENH</sub> trip point, the RT9624G begins a new initialization and follows the PWM command to control the UGATE and LGATE. When the EN pin falls below the V<sub>ENL</sub> trip point, the RT9624G shuts down and keeps UGATE and LGATE low.

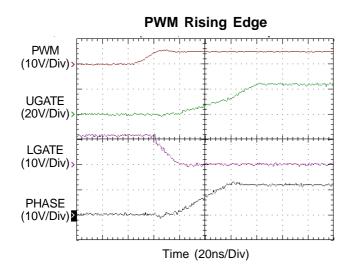

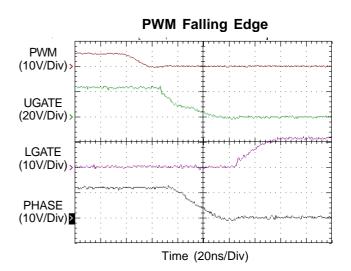

#### **Tri-state PWM Input**

After the initialization, the PWM signal takes the control. The rising PWM signal first forces the LGATE signal to turn low then UGATE signal is allowed to go high just after a non-overlapping time to avoid shoot through current. The falling of PWM signal first forces UGATE to go low. When UGATE and PHASE signal reach a predetermined low level, LGATE signal is allowed to turn high.

The PWM signal is acted as "High" if the signal is above the rising threshold and acted as "Low" if the signal is below the falling threshold. When PWM signal level enters and remains within the shutdown window, the output drivers are disabled and both MOSFET gates are pulled and held low. If the PWM signal is left floating, the pin will be kept around 1.8V by the internal divider and provide the PWM controller with a recognizable level.

#### Internal Bootstrap Power Switch

The RT9624G builds in an internal bootstrap power switch to replace external bootstrap diode, and this can facilitate PCB design and reduce total BOM cost of the system. Hence, no external bootstrap diode is required in real applications.

#### Non-overlap Control

To prevent the overlap of the gate drivers during the UGATE pull low and the LGATE pull high, the non-overlap circuit monitors the voltages at the PHASE node and high-side gate drive (UGATE-PHASE). When the PWM input signal goes low, UGATE begins to pull low (after propagation delay). Before LGATE is pulled high, the non-overlap protection circuit ensures that the monitored voltages have gone below 1.1V. Once the monitored voltages fall below 1.1V, LGATE begins to turn high. By waiting for the voltages of the PHASE pin and high-side gate driver to fall below 1.1V, the non-overlap protection circuit ensures that UGATE is low before LGATE pulls high.

Also to prevent the overlap of the gate drivers during LGATE pull low and UGATE pull high, the non-overlap circuit monitors the LGATE voltage. When LGATE goes below 1.1V, UGATE goes high after propagation delay.

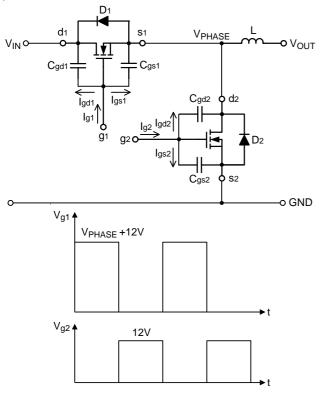

#### **Driving Power MOSFETs**

The DC input impedance of the power MOSFET is extremely high. When  $V_{gs1}$  or  $V_{gs2}$  is at 12V or 5V, the gate draws the current only for few nano-amperes. Thus once the gate has been driven up to "ON" level, the current could be negligible.

However, the capacitance at the gate to source terminal should be considered. It requires relatively large currents to drive the gate up and down 12V (or 5V) rapidly. It is also required to switch drain current on and off with the required speed. The required gate drive currents are calculated as follows.

Copyright ©2015 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

Figure 1. Equivalent Circuit and Waveforms (V<sub>CC</sub> = 12V)

In Figure 1, the current I<sub>g1</sub> and I<sub>g2</sub> are required to move the gate up to 12V. The operation consists of charging  $C_{ad1}$ ,  $C_{gd2}$ ,  $C_{gs1}$  and  $C_{gs2}$ .  $C_{gs1}$  and  $C_{gs2}$  are the capacitors from gate to source of the high-side and the low-side power MOSFETs, respectively. In general data sheets, the Cgs1 and C<sub>gs2</sub> are referred as "C<sub>iss</sub>" which are the input capacitors. Cgd1 and Cgd2 are the capacitors from gate to drain of the high-side and the low-side power MOSFETs, respectively and referred to the data sheets as "Crss" the reverse transfer capacitance. For example, tr1 and tr2 are the rising time of the high-side and the low-side power MOSFETs respectively, the required current Igs1 and Igs2, are shown as below :

$$I_{gs1} = C_{gs1} \frac{dV_{g1}}{dt} = \frac{C_{gs1} \times 12}{t_{r1}}$$

(1)

$$I_{gs2} = C_{gs1} \frac{dV_{g2}}{dt} = \frac{C_{gs1} \times 12}{t_{r2}}$$

(2)

Before driving the gate of the high-side MOSFET up to 12V, the low-side MOSFET has to be off; and the highside MOSFET will be turned off before the low-side is turned on. From Figure 1, the body diode "D<sub>2</sub>" will be turned on before high-side MOSFETs turn on.

## RICHTE

$$I_{gd1} = C_{gd1} \frac{dV}{dt} = C_{gd1} \frac{12}{t_{r1}}$$

(3)

Before the low-side MOSFET is turned on, the Cgd2 have been charged to V<sub>IN</sub>. Thus, as C<sub>ad2</sub> reverses its polarity and g<sub>2</sub> is charged up to 12V, the required current is

$$I_{gd2} = C_{gd2} \frac{dV}{dt} = C_{gd2} \frac{V_{IN} + 12}{t_{r2}}$$

(4)

It is helpful to calculate these currents in a typical case. Assume a synchronous rectified Buck converter, input voltage V<sub>IN</sub> = 12V, V<sub>gs1</sub> = 12V, V<sub>gs2</sub> = 12V. The high-side MOSFET is PHB83N03LT whose  $C_{iss} = 1660 pF$ ,  $C_{rss}$  = 380pF, and  $t_r$  = 14ns. The low-side MOSFET is PHB95N03LT whose C<sub>iss</sub> = 2200pF, C<sub>rss</sub> = 500pF and  $t_r = 30$  ns, from the equation (1) and (2) we can obtain

$$I_{gs1} = \frac{1660 \times 10^{-12} \times 12}{14 \times 10^{-9}} = 1.428 \quad (A)$$

(5)

$$I_{gs2} = \frac{2200 \times 10^{-12} \times 12}{30 \times 10^{-9}} = 0.88 \quad (A)$$

(6)

from equation. (3) and (4)

$$I_{gd1} = \frac{380 \times 10^{-12} \times 12}{14 \times 10^{-9}} = 0.326 \quad (A)$$

(7)

$$I_{gd2} = \frac{500 \times 10^{-12} \times (12+12)}{30 \times 10^{-9}} = 0.4 \quad (A)$$

(8)

the total current required from the gate driving source can be calculated as the following equations.

$$I_{g1} = I_{gs1} + I_{gd1} = (1.428 + 0.326) = 1.754 \quad (A) \tag{9}$$

$$I_{g2} = I_{gs2} + I_{gd2} = (0.88 + 0.4) = 1.28 \quad (A)$$

(10)

By a similar calculation, we can also get the sink current required from the turned off MOSFET.

#### Select the Bootstrap Capacitor

Figure 2 shows part of the bootstrap circuit of the RT9624G. The V<sub>CB</sub> (the voltage difference between BOOT and PHASE on RT9624G) provides a voltage to the gate of the high-side power MOSFET. This supply needs to be ensured that the MOSFET can be driven. For this, the capacitance C<sub>BOOT</sub> has to be selected properly. It is determined by the following constraints.

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. www.richtek.com

Figure 2. Part of Bootstrap Circuit of RT9624G

In practice, a low value capacitor  $C_{BOOT}$  will lead to the over charging that could damage the IC. Therefore, to minimize the risk of overcharging and to reduce the ripple on V<sub>CB</sub>, the bootstrap capacitor should not be smaller than 0.1µF, and the larger the better. In general design, using 1µF can provide better performance. At least one low-ESR capacitor should be used to provide good local de-coupling. It is recommended to adopt a ceramic or tantalum capacitor.

#### **Power Dissipation**

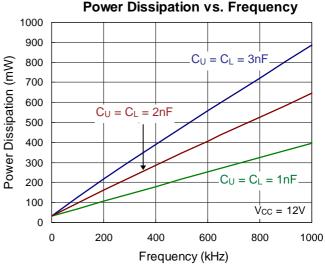

To prevent driving the IC beyond the maximum recommended operating junction temperature of 125°C, it is necessary to calculate the power dissipation appropriately. This dissipation is a function of switching frequency and total gate charge of the selected MOSFET.

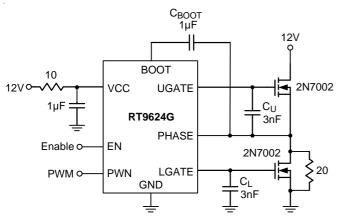

Figure 3 shows the power dissipation test circuit.  $C_L$  and  $C_U$  are the UGATE and LGATE load capacitors, respectively. The bootstrap capacitor value is  $1\mu$ F.

Figure 3. Power Dissipation Test Circuit

Figure 4 shows the power dissipation of the RT9624G as a function of frequency and load capacitance when  $V_{CC} = 12V$ . The value of  $C_U$  and  $C_L$  are the same and the frequency is varied from 100kHz to 1MHz.

Figure 4. Power Dissipation vs. Frequency

The operating junction temperature can be calculated from the power dissipation curves (Figure 4). Assume  $V_{CC} =$ 12V, operating frequency is 200kHz and  $C_U = C_L = 1nF$ which emulate the input capacitances of the high-side and low-side power MOSFETs. From Figure 4, the power dissipation is 100mW. Thus, for example, with the WDFN-8SL 2x2 package, the package thermal resistance  $\theta_{JA}$  is 46°C/W. The operating junction temperature is then calculated as :

$T_J = (46^{\circ}C/W \times 100 mW) + 25^{\circ}C = 29.6^{\circ}C$  (11)

where the ambient temperature is  $25^{\circ}$ C.

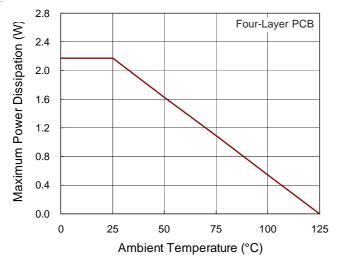

#### Thermal Considerations

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula :

$$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WDFN-8SL 2x2 package, the thermal resistance,  $\theta_{JA}$ , is 46°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25$ °C can be calculated by the following formulas :

$P_{D(MAX)}$  = (125°C - 25°C) / (46°C/W) = 2.17W for WDFN-8SL 2x2 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 5 allow the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 5. Derating Curve of Maximum Power Dissipation

#### Layout Consideration

Figure 6 shows the schematic circuit of a synchronous Buck converter to implement the RT9624G. The converter operates from 5V to 12V of input Voltage.

For the PCB layout, it should be very careful. The power circuit section is the most critical one. If not configured properly, it will generate a large amount of EMI. The location of Q1, Q2, L1 should be very close.

Next, the trace from UGATE, and LGATE should also be short to decrease the noise of the driver output signals. PHASE signals from the junction of the power MOSFET, carrying the large gate drive current pulses, should be as heavy as the gate drive trace. The bypass capacitor C1 should be connected to GND directly. Furthermore, the bootstrap capacitors ( $C_{BOOT}$ ) should always be placed as close to the pins of the IC as possible.

Figure 6. Synchronous Buck Converter Circuit