# High Voltage Smart Cap Divider and Direct Charge Charger

## **General Description**

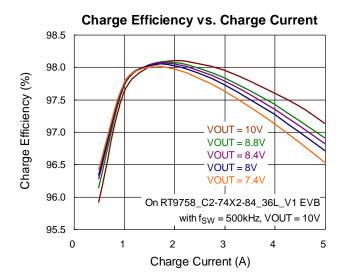

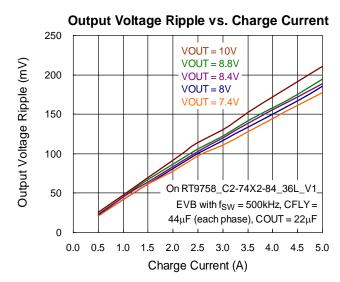

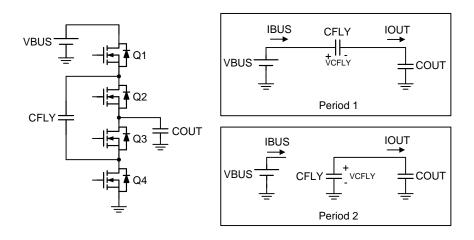

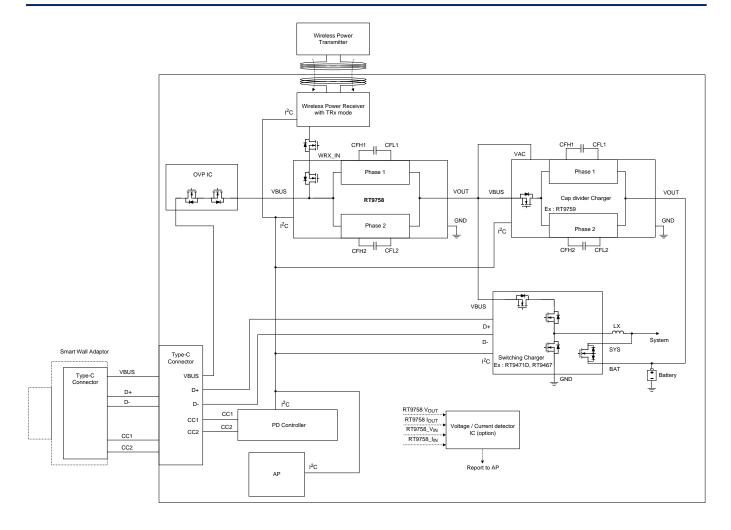

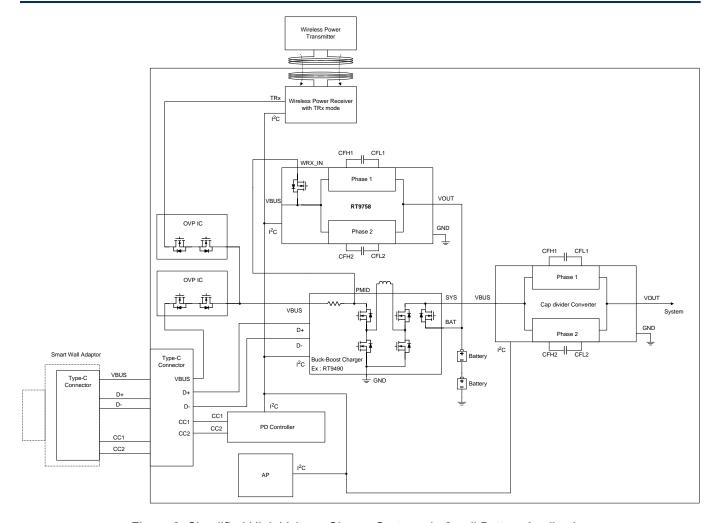

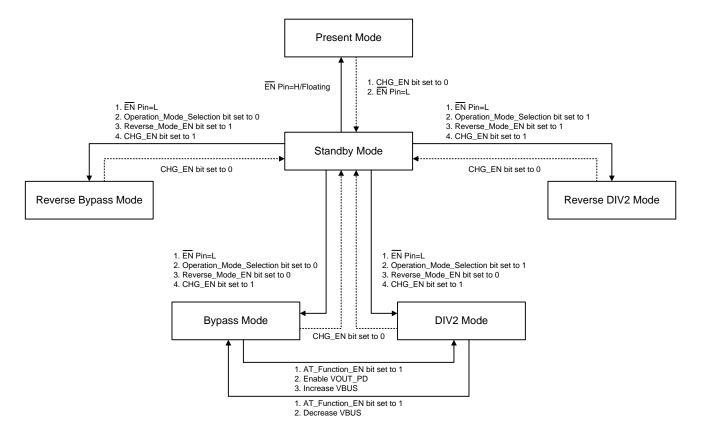

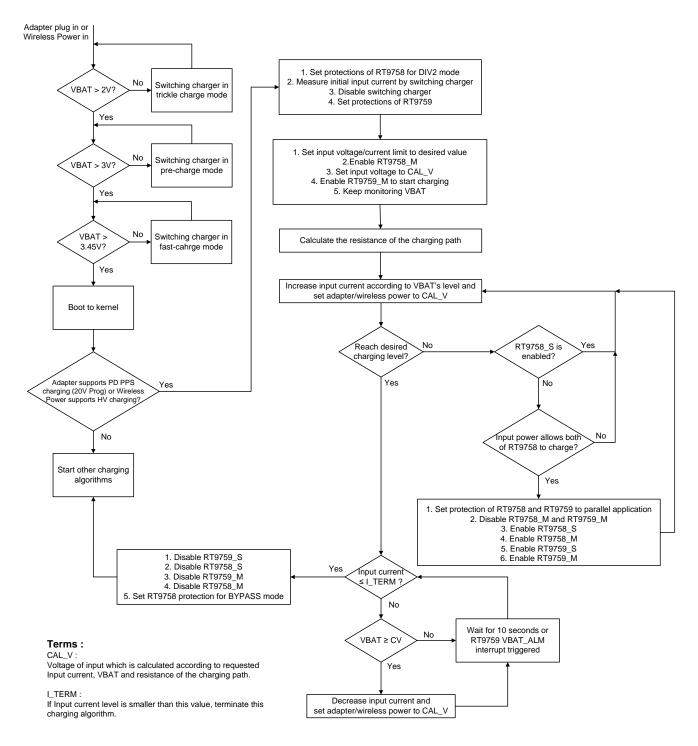

The RT9758 is a high efficiency and high charge current charger for high voltage application. The efficiency is up to 98.1% when Vout = 10V, Iout = 2A, switching frequency = 500 kHz, dual phase with VBUS input in cap divider mode. The RT9758 maximum charge current is up to 5A. The device integrates cap divider topology (DIV2 mode), direct charge topology (Bypass mode), an input reverse blocking NFET, a dual-phase charge pump core, the  $\overline{\text{EN}}$  pin control and 9-way protection. In present mode ( $\overline{\text{EN}}$  = H), the host can still order the command by I²C serial interface.

## **Applications**

- Smart Phones

- Tablet

- PC

## **Ordering Information**

RT9758 🗖

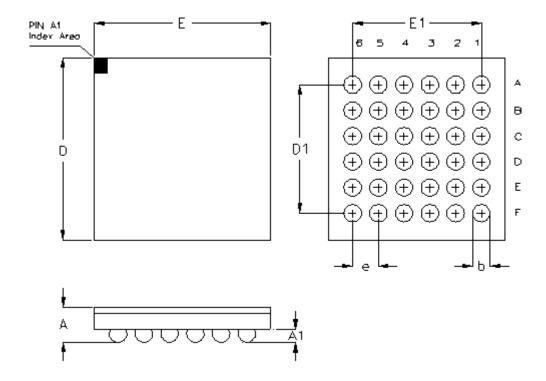

-Package Type WSC: WL-CSP-36B 2.74x2.84 (BSC)

### Note:

DS9758-03

#### Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

- Integrated Bidirectional Bypass Mode and Cap Divider Mode (DIV2 Mode)

- Input Reverse Blocking NFET between WRX\_IN Pin and VBUS Pin

- ▶ Block the Reverse Current

- Dual-Phase Charge Pump Core

- ▶ 5A Output Current Capability

- ► Efficiency Up to 98.1% when Vout = 10V, lout = 2A, Switching Frequency = 500kHz and Dual Phase with VBUS Input in DIV2 Mode

- ► 300kHz to 1.5MHz Variable Switching Frequency Stay Out of Audio Band

- Spread Spectrum Technology for EMI Reduction

- Adjustable Single-Phase or Dual-Phase for DIV2 Mode

- ▶ Programmable Pre-Charge Current and Pre-Charge Timing for Charge Soft-Start

- ► Support Converter Soft-Start with 200mA Loading

- Support Synchronize Function for Parallel Application

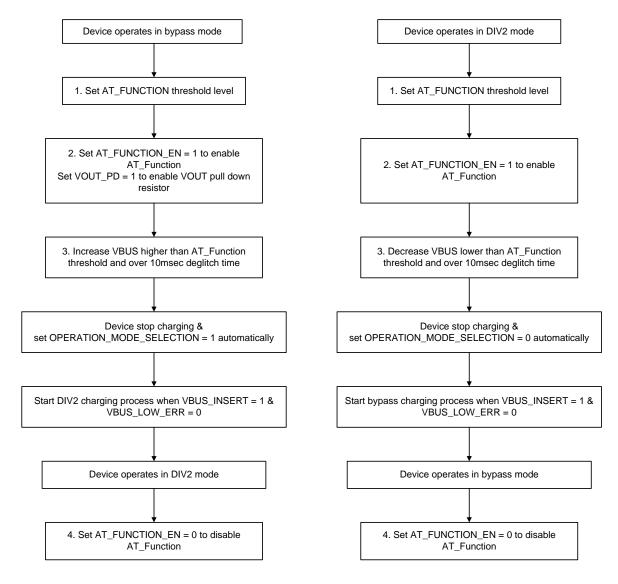

- Operation Mode Transfer Automatically between Bypass Mode and DIV2 Mode (AT\_Function)

- I<sup>2</sup>C is Available when Device in Present Mode

- 3-Error Charge Pump Switch Protection

- ▶ VBUS Voltage Too Low Error Protection before Switch (VBUS LOW ERR)

- ► CFLY Short Error Protection Before Switch (CFLY DIAG)

- ► Converter Over-Current Protection (CON\_OCP)

- 6-Way System Protection

- ▶ VBUS Over-Voltage Protection (VBUS OVP)

- ▶ IBUS Over-Current Protection (IBUS\_OCP)

- ► VOUT Over-Voltage Protection (VOUT\_OVP)

- ► WRX Reverse Over-Current Protection (WRX\_IRE\_OCP)

- ▶ VOUT Short Error Protection Before Charge (VOUT ERR)

- ► Junction Over-Temperature Protection (TDIE\_OTP)

May 2023

# **Marking Information**

2C YM DNN 2C: Product Code YMDNN: Date Code

# **Pin Configuration**

(TOP VIEW)

| (A1)   | (A2) | (A3) | (A4)<br>VOUT | (A5) | (A6) |

|--------|------|------|--------------|------|------|

| SCL    | VBUS | CFH2 | VOUT         | CFL2 | PGND |

| (B1)   | (B2) | (B3) | (B4)         | (B5) | (B6) |

| SDA    | VBUS | CFH2 | VOUT         | CFL2 | PGND |

| (C1)   | (C2) | (C3) | (C4)         | (C5) | (C6) |

| WRX_IN | VBUS | BST2 | VOUT         | ADDR | AGND |

| (D1)   | (D2) | (D3) | (D4)         | (D5) | (D6) |

| WRX_IN | VBUS | BST1 | VOUT         | EN   | INT  |

| (E1)   | (E2) | (E3) | (E4)         | (E5) | (E6) |

| WRX_OK | VBUS | CFH1 | VOUT         | CFL1 | PGND |

| (F1)   | (F2) | (F3) | (F4)         | (F5) | (F6) |

| SYNC   | VBUS | CFH1 | VOUT         | CFL1 | PGND |

WL-CSP-36B 2.74x2.84 (BSC)

# **Functional Pin Description**

| Pin No.                   | Pin Name | I/O | Pin Function                                                                                                                                                                                                 |

|---------------------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1                        | SCL      | DI  | I <sup>2</sup> C serial clock line. Connect to 1.8V/3.3V pull-up voltage via 10kohm pull-up resistor.                                                                                                        |

| A2, B2, C2,<br>D2, E2, F2 | VBUS     | Р   | These pins are the input power supply and must be connected together on the PCB. Two $4.7\mu F$ capacitors must be connected to VBUS and GND.                                                                |

| A3, B3                    | CFH2     | Р   | Flying capacitor positive node. Two 22µF capacitors must be connected to CFL2 and CFH2 and placed as close as possible to the device. These pins must be connected together on the PCB.                      |

| A4, B4, C4,<br>D4, E4, F4 | VOUT     | Р   | Power supply. Connect to positive terminal of the battery pack or the input of the next stage charger IC. Must be connected together on the PCB. One $22\mu F$ capacitors must be connected to VOUT and GND. |

| A5, B5                    | CFL2     | Р   | Flying capacitor negative node. Two $22\mu F$ capacitors must be connected to CFL2 and CFH2 and placed as close as possible to the device. These pins must be connected together on the PCB.                 |

| A6, B6, E6, F6            | PGND     | Р   | Power ground pin.                                                                                                                                                                                            |

| B1                        | SDA      | DIO | I <sup>2</sup> C serial data line. Connect to 1.8V/3.3V pull-up voltage via 10kohm pull-up resistor.                                                                                                         |

| C1, D1                    | WRX_IN   | Р   | Connect to wireless power receiver output. One 2.2μF capacitor must be connected to WRX_IN and GND.                                                                                                          |

| СЗ                        | BST2     | Р   | Charge pump for gate drive. Connect a 22nF capacitor between BST2 and CFH2.                                                                                                                                  |

| C5                        | ADDR     | DI  | Provide different voltage level at ADDR and GND to assign address of the device.                                                                                                                             |

| C6                        | AGND     | Р   | Analog ground pin.                                                                                                                                                                                           |

| Pin No. | Pin Name | I/O | Pin Function                                                                                                                                                                                 |

|---------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D3      | BST1     | Р   | Charge pump for gate drive. Connect a 22nF capacitor between BST1 and CFH1.                                                                                                                  |

| D5      | ĒN       | DI  | Device enable control pin. Pull high to disable device. I <sup>2</sup> C is still available when EN pin is pull high.                                                                        |

| D6      | INT      | DO  | Open drain interrupt output. Connect to pull-up voltage via $10k\Omega$ pull-up resistor. Normally high, when event happen, $\overline{\text{INT}}$ pin sends a 256µs low pulse to system.   |

| E1      | WRX_OK   | Р   | Push-pull structure. When WRX_IN over then WRX_INSERT level, this pin will pull high to inform system.                                                                                       |

| E3, F3  | CFH1     | Р   | Flying capacitor positive node. Two $22\mu F$ capacitors must be connected to CFL1 and CFH1 and placed as close as possible to the device. These pins must be connected together on the PCB. |

| E5, F5  | CFL1     | Р   | Flying capacitor negative node. Two $22\mu F$ capacitors must be connected to CFL1 and CFH1 and placed as close as possible to the device. These pins must be connected together on the PCB. |

| F1      | SYNC     | AIO | Push-pull structure. Master device's sync pin connect to slave device's sync pin. Let pin floating in standalone mode.                                                                       |

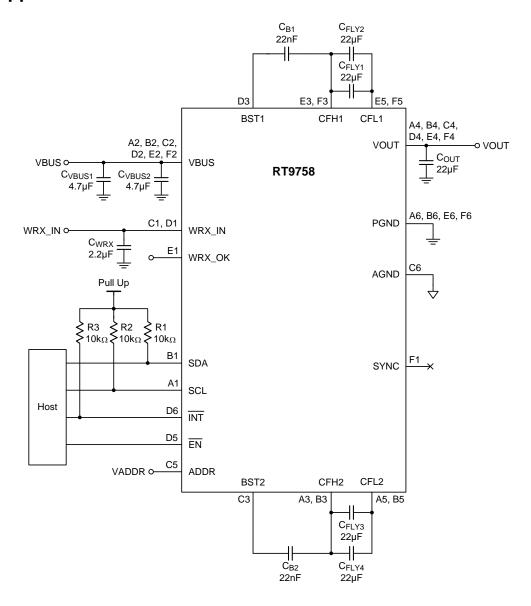

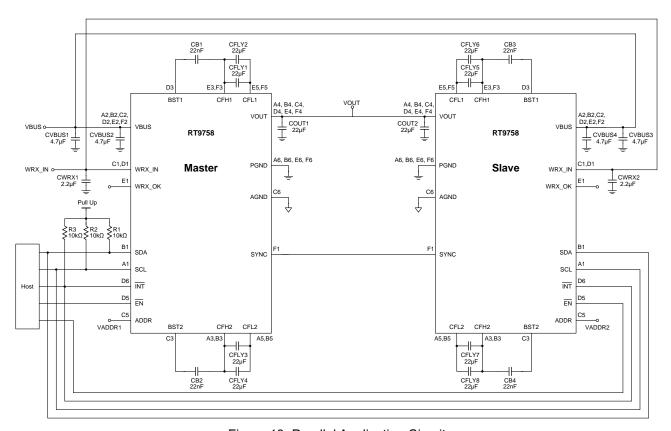

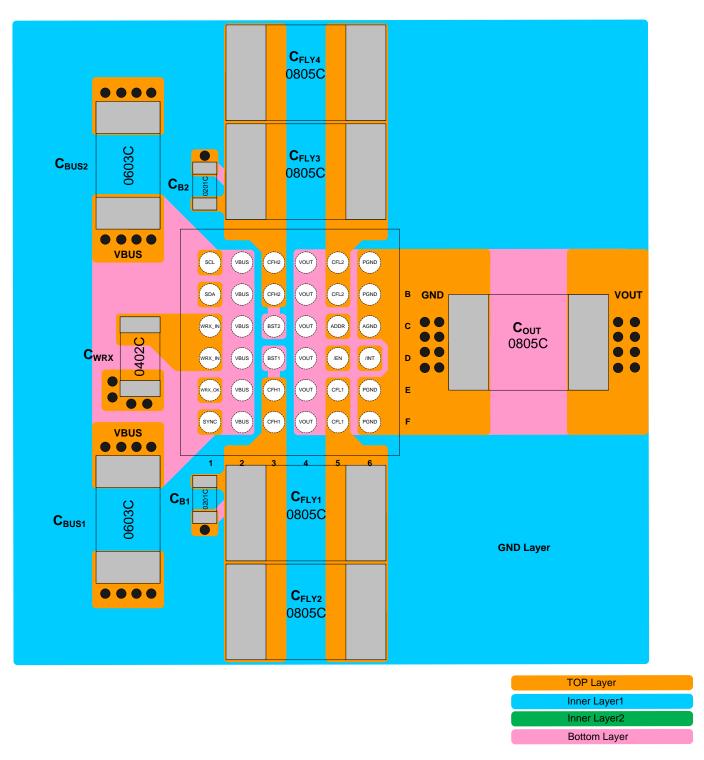

## **Typical Application Circuit**

**Table 1. BOM List**

| Name                                 | Part Number       | Description                      | Package | Manufacturer |

|--------------------------------------|-------------------|----------------------------------|---------|--------------|

| CVBUS1,<br>CVBUS2                    | GRM188R6YA475KE15 | CAP, CERM, 4.7μF, 35V, ±10%, X5R | 0603    | MuRata       |

| CWRX_IN                              | GRM155R6YA225ME11 | CAP, CERM, 2.2μF, 35V, ±20%, X5R | 0402    | MuRata       |

| CFLY1,<br>CFLY2,<br>CFLY3,<br>CFLY4, | GRM21BR61E226ME44 | CAP, CERM, 22μF, 25V, ±20%, X5R  | 0805    | MuRata       |

| Соит                                 | GRM21BR61E226ME44 | CAP, CERM, 22μF, 25V, ±20%, X5R  | 0805    | MuRata       |

| CB1, CB2                             | GRM033R61C223KE84 | CAP, CERM, 22nF, 16V, ±10%, X5R  | 0201    | MuRata       |

| R1, R2, R3                           | CRCW040210K0JNED  | RES, 10k, 5%, 0.063W             | 0402    | Vishay-Dale  |

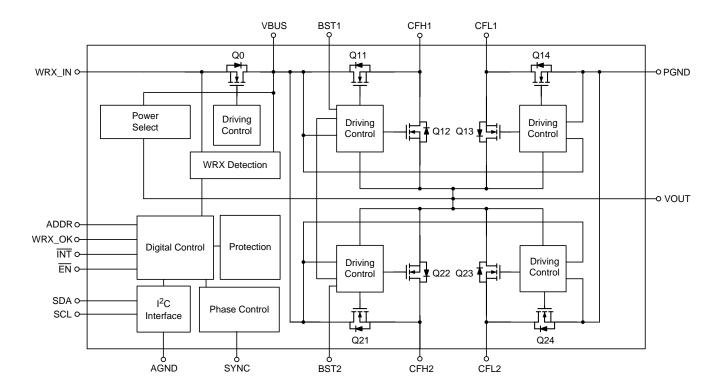

# **Functional Block Diagram**

May 2023

DS9758-03

| Absolute Maximum Ratings (Note 1)                      |                 |

|--------------------------------------------------------|-----------------|

| Supply Pin Voltage, WRX_IN                             | 1.4V to 28V     |

| Supply Pin Voltage, VBUS                               | 1.4V to 28V     |

| Supply Pin Voltage, VOUT                               | 1.4V to 16.5V   |

| Terminal Pin Voltage, BST1, BST2                       | 0.3V to 34V     |

| Terminal Pin Voltage, CFH1, CFH2                       | 0.3V to 24V     |

| Terminal Pin Voltage, CFL1, CFL2                       | 0.3V to 16.5V   |

| Differential Pin Voltage, VBUS to WRX_IN               | 0.3V to 28V     |

| Differential Pin Voltage, BST to CFH                   | 1V to 24V       |

| Terminal Pin Voltage, SDA, SCL, INT, EN                | 0.3V to 6V      |

| Terminal Pin Voltage, ADDR, SYNC, WRX_OK               | 0.3V to 6V      |

| Terminal Pin Current, INT                              | 0mA to 6mA      |

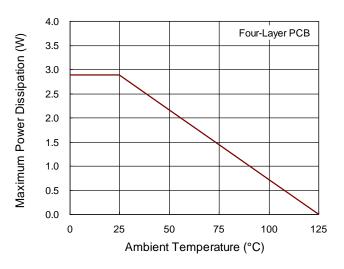

| <ul> <li>Power Dissipation, PD @ TA = 25°C</li> </ul>  |                 |

| WL-CSP-36B 2.74x2.84 (BSC)                             | 2.88W           |

| Package Thermal Resistance (Note 2)                    |                 |

| WL-CSP-36B 2.74x2.84 (BSC), $\theta$ JA                | 34.7°C/W        |

| Lead Temperature (Soldering, 10 sec.)                  | 260°C           |

| Junction Temperature                                   | 40°C to 150°C   |

| Storage Temperature Range                              | 65°C to 150°C   |

| • ESD Susceptibility (Note 3)                          |                 |

| HBM (Human Body Model), per ANSI/ESDA/JEDEC JS-001     | ±2kV            |

| Recommended Operating Conditions (Note 4)              |                 |

| Supply Input Voltage Range, WRX_IN, VBUS (Bypass Mode) | 4V to 13V       |

| Supply Input Voltage Range, WRX_IN, VBUS (DIV2 Mode)   | 7.4V to 21V     |

| Output Voltage Range, VOUT (Reverse Bypass Mode)       | 4V to 13V       |

| Output Voltage Range, VOUT (Reverse DIV2 Mode)         | 3.7V to 10.5V   |

| Positive flying capacitor Voltage Range, CFH1, CFH2    | - 0V to 21V     |

| Negative flying capacitor Voltage Range, CFL1, CFL2    | - 0V to 10.5V   |

| Analog Voltage Range, ADDR, SYNC, WRX_OK               | - 0V to 5V      |

| • I/O Control Voltage Range, SDA, SCL, INT, EN         | - 0V to 5V      |

| Charger Current Range, IOUT (DIV2 Mode)                | - 0A to 6A      |

| Charger Current Range, IOUT (BYPASS Mode)              | - 0A to 5A      |

| Ambient Temperature Range                              | - −40°C to 85°C |

| Junction Temperature Range                             | 40°C to 150°C   |

## **Electrical Characteristics**

(T<sub>A</sub> = 25°C, unless otherwise specified)

| Parameter               | Symbol          | Test Conditions                                                                                                                                                          | Min | Тур  | Max  | Unit |

|-------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| Power Select and Source | <b>!</b>        |                                                                                                                                                                          |     |      |      |      |

|                         |                 | EN = 1.8V, VBUS = 5.5V,<br>VOUT = 0V, WRX_IN = 0V, Q0<br>turn off, all of pull down resistor<br>disable, WDT disable, TA = 25°C                                          |     | 15   | 22   |      |

|                         | IBUS_IQ_PRESENT | EN = 1.8V, VBUS = 5.5V,<br>VOUT = 0V, WRX_IN = 0V, Q0<br>turn off, all of pull down resistor<br>disable, WDT disable, TA =<br>-40°C to 85°C                              | -1  |      | 35   | μА   |

|                         |                 | EN = 0V, VBUS = 5.5V,<br>VOUT = 0V, WRX_IN = 0V, Q0<br>turn off, all of pull down resistor<br>disable, WDT disable, CHG_EN<br>= 0, TA = 25°C                             | 1   |      | 300  |      |

|                         | IBUS_IQ_STANDBY | EN = 0V, VBUS = 5.5V,<br>VOUT = 0V, WRX_IN = 0V, Q0<br>turn off, all of pull down resistor<br>disable, WDT disable, CHG_EN<br>= 0, TA = -40°C to 85°C                    | 1   |      | 350  | - μΑ |

| VBUS Quiescent Current  | IBUS_IQ_DIV2    | EN = 0V, VBUS = 20V,<br>VOUT = 0V, WRX_IN = 0V, Q0<br>turn off, all of pull down resistor<br>disable, WDT disable, CHG_EN<br>= 1, in DIV2 Mode, TA = 25°C                | 1   |      | 12   | mA   |

|                         |                 | EN = 0V, VBUS = 20V,<br>VOUT = 0V, WRX_IN = 0V, Q0<br>turn off, all of pull down resistor<br>disable, WDT disable, CHG_EN<br>= 1, in DIV2 Mode, TA = -40°C to<br>85°C    | -1  |      | 13.2 |      |

|                         | IBUS_IQ_BYPASS  | EN = 0V, VBUS = 5.5V,<br>VOUT = 0V, WRX_IN = 0V, Q0<br>turn off, all of pull down resistor<br>disable, WDT disable, CHG_EN<br>= 1, in Bypass Mode, TA = 25°C             |     | 1.65 |      |      |

|                         |                 | EN = 0V, VBUS = 5.5V,<br>VOUT = 0V, WRX_IN = 0V, Q0<br>turn off, all of pull down resistor<br>disable, WDT disable, CHG_EN<br>= 1, in Bypass Mode, TA = -40°C<br>to 85°C |     |      | 2    | mA   |

| Parameter                   | Symbol                             | Test Conditions                                                                                                                                           | Min | Тур  | Max  | Unit |  |

|-----------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|--|

|                             |                                    | EN = 1.8V, WRX_IN = 5.5V,<br>VOUT = 0V, Q0 turn on, all of<br>pull down resistor disable, WDT<br>disable, TA = 25°C                                       | ı   | 15   | 22   |      |  |

|                             | IWRX_IN_IQ_PRESENT                 | EN = 1.8V, WRX_IN = 5.5V,<br>VOUT = 0V, Q0 turn on, all of<br>pull down resistor disable, WDT<br>disable, TA = -40°C to 85°C                              | 1   | 1    | 35   | μΑ   |  |

|                             |                                    | EN = 0V, WRX_IN = 5.5V, VOUT<br>= 0V, Q0 turn on, all of pull down<br>resistor disable, WDT disable,<br>CHG_EN = 0, TA = 25°C                             | 1   |      | 450  |      |  |

|                             | IWRX_IN_IQ_STANDBY                 | EN = 0V, WRX_IN = 5.5V, VOUT<br>= 0V, Q0 turn on, all of pull down<br>resistor disable, WDT disable,<br>CHG_EN = 0,<br>TA = -40°C to 85°C                 |     |      | 550  | μА   |  |

| WRX_IN Quiescent<br>Current | IWRX_IN_IQ_DIV2  IWRX_IN_IQ_BYPASS | EN = 0V, WRX_IN = 20V, VOUT<br>= 0V, Q0 turn on, all of pull down<br>resistor disable, WDT disable,<br>CHG_EN = 1, in DIV2 Mode, TA<br>= 25°C             | 1   |      | 12   | - mA |  |

|                             |                                    | EN = 0V, WRX_IN = 20V, VOUT<br>= 0V, Q0 turn on, all of pull down<br>resistor disable, WDT disable,<br>CHG_EN = 1, in DIV2 Mode, TA<br>= -40°C to 85°C    | 1   |      | 13.2 |      |  |

|                             |                                    | EN = 0V, WRX_IN = 5.5V, VOUT<br>= 0V, Q0 turn on, all of pull down<br>resistor disable, WDT disable,<br>CHG_EN = 1, in Bypass Mode,<br>TA = 25°C          |     | 1.65 |      |      |  |

|                             |                                    | EN = 0V, WRX_IN = 5.5V, VOUT<br>= 0V, Q0 turn on, all of pull down<br>resistor disable, WDT disable,<br>CHG_EN = 1, in Bypass Mode,<br>TA = -40°C to 85°C |     |      | 2    | - mA |  |

| Parameter                              | Symbol                          | Test Conditions                                                                                                                                   | Min | Тур | Max | Unit |

|----------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                                        | LOUT 10 DDESENT                 | EN = 1.8V, VOUT = 7.4V,<br>WRX_IN = 0V, Q0 turn off, all of<br>pull down resistor disable, WDT<br>disable, TA = 25°C                              |     | 15  | 22  | μА   |

| VOUT Quiescent Current                 | IOUT_IQ_PRESENT                 | $\overline{\text{EN}}$ = 1.8V, VOUT = 7.4V,<br>WRX_IN = 0V, Q0 turn off, all of<br>pull down resistor disable, WDT<br>disable, TA = -40°C to 85°C |     | -   | 35  | μΑ   |

| VOOT Quiescent Ourient                 | LOUT TO STANDRY                 | EN = 0V, VOUT = 7.4V, WRX_IN<br>= 0V, Q0 turn off, all of pull down<br>resistor disable, WDT disable,<br>CHG_EN = 0, TA = 25°C                    | I   | 1   | 300 |      |

|                                        | lout_iq_standby                 | EN = 0V, VOUT = 7.4V, WRX_IN<br>= 0V, Q0 turn off, all of pull down<br>resistor disable, WDT disable,<br>CHG_EN = 0, TA = -40°C to 85°            | I   | 1   | 350 | μΑ   |

| VDDA UVLO Threshold                    | VDDA_UVLO_TH                    | $V_{DDA}$ rising, $\overline{EN} = 0V$                                                                                                            | -   | 2.6 |     | V    |

| VDDA UVLO Hysteresis                   | VDDA_UVLO_HY                    | $V_{DDA}$ falling, $\overline{EN} = 0V$                                                                                                           | -   | 0.6 |     | V    |

| WRX_IN Insert Threshold                | VWRX_IN_INSERT_TH               | WRX_IN rising                                                                                                                                     | 3   | 3.1 | 3.2 | V    |

| WRX_IN Insert Threshold Deglitch Time  | twrx_in_insert_deg              |                                                                                                                                                   |     | 3   |     | μS   |

| WRX_IN Insert Hysteresis               | VWRX_IN_INSERT_HY               | WRX_IN falling                                                                                                                                    | 50  | 150 | 250 | mV   |

| VBUS Insert Threshold                  | VBUS_INSERT_TH                  | V <sub>BUS</sub> rising                                                                                                                           | 3   | 3.1 | 3.2 | V    |

| VBUS Insert Threshold<br>Deglitch Time | tvbus_insert_deg                |                                                                                                                                                   | -   | 3   |     | μS   |

| VBUS Insert Hysteresis                 | VBUS_INSERT_HY                  | VBUS falling                                                                                                                                      | 50  | 150 | 250 | mV   |

| VOUT Insert Threshold                  | Vout_insert_th                  | Vout rising                                                                                                                                       | 3.3 | 3.5 | 3.7 | V    |

| VOUT Insert Threshold<br>Deglitch Time | tVOUT_INSERT_DEG                |                                                                                                                                                   |     | 3   |     | μS   |

| VOUT Insert Hysteresis                 | VOUT_INSERT_HY                  | Vout falling                                                                                                                                      | 180 | 200 | 235 | mV   |

| Cap Divider and Bypass I               | Mode On-Resistance              |                                                                                                                                                   |     |     |     |      |

| Q0 RON                                 | RQ0                             | WRX_IN = 3.1V to 21V, Charge enable                                                                                                               |     | 25  | 35  | mΩ   |

| Q11, Q21 RON                           | RQ11, RQ21                      | VOUT = 3.5V to 10.5V, in DIV2 mode                                                                                                                | 1   | 35  | 49  | mΩ   |

| Q12, Q22 RON                           | RQ12, RQ22                      | VOUT = 3.5V to 10.5V, in DIV2 mode                                                                                                                | 1   | 25  | 35  | mΩ   |

| Q13, Q23 RON                           | RQ13, RQ23                      | VOUT = 3.5V to 10.5V, in DIV2 mode                                                                                                                |     | 25  | 35  | mΩ   |

| Q14, Q24 RON                           | RQ14, RQ24                      | VOUT = 3.5V to 10.5V, in DIV2 mode                                                                                                                |     | 25  | 35  | mΩ   |

| Bypass RON                             | (RQ11 + RQ12),<br>(RQ21 + RQ22) | VOUT = 3.5V to 14V, in Bypass mode                                                                                                                |     | 30  | 40  | mΩ   |

| Parameter                 | Symbol            | Test Conditions                                                                                                            | Min   | Тур  | Max   | Unit  |

|---------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| PWM Frequency             |                   |                                                                                                                            |       |      |       |       |

|                           |                   | Select by register 0x0F[5:3] = 111                                                                                         | 1350  | 1500 | 1650  |       |

|                           |                   | Select by register 0x0F[5:3] = 110                                                                                         | 900   | 1000 | 1100  |       |

|                           |                   | Select by register 0x0F[5:3] = 011                                                                                         | 765   | 900  | 1035  |       |

| Charge Switch Frequency   | fsw               | Select by register 0x0F[5:3] = 101                                                                                         | 675   | 750  | 825   | kHz   |

| Charge Switch Frequency   | 15W               | Select by register 0x0F[5:3] = 010                                                                                         | 510   | 600  | 690   | NI IZ |

|                           |                   | Select by register 0x0F[5:3] = 100, default                                                                                | 450   | 500  | 550   |       |

|                           |                   | Select by register 0x0F[5:3] = 001                                                                                         | 382.5 | 450  | 517.5 |       |

|                           |                   | Select by register 0x0F[5:3] = 000                                                                                         | 255   | 300  | 345   |       |

| Protection                |                   |                                                                                                                            |       |      |       |       |

| VOUT OVP Range            | VOUT_OVP_RAN      | Rising                                                                                                                     | 7     |      | 14    | V     |

| VOUT OVP Step Size        | VOUT_OVP_SIZE     |                                                                                                                            | -     | 1    |       | V     |

| VOUT OVP Accuracy         | VOUT_OVP_ACC      |                                                                                                                            | -1.5  |      | 1.5   | %     |

| VOUT OVP Deglitch Time    | tVOUT_OVP_DEG     |                                                                                                                            |       | 4    |       | μS    |

| WRX_IRE OCP Range         | IWRX_IRE_OCP_RAN  | Rising                                                                                                                     | 1     |      | 6     | Α     |

| WRX_IRE OCP Step Size     | IWRX_IRE_OCP_SIZE |                                                                                                                            |       | 500  |       | mA    |

| WDV IDE OCD Assures       | h                 | IWRX_IRE_OCP = 1A to 4A                                                                                                    | -5    |      | 5     | 0/    |

| WRX_IRE OCP Accuracy      | IWRX_IRE_OCP_ACC  | IWRX_IRE_OCP = 4.5A to 6A                                                                                                  | -10   |      | 10    | %     |

| WRX_IRE OCP Deglitch Time | twrx_ire_ocp_deg  |                                                                                                                            | 1     | 50   |       | μS    |

| VBUS OVP Range            | VBUS_OVP_RAN      | Rising                                                                                                                     | 7.25  |      | 22    | V     |

| VBUS OVP Step Size        | VBUS_OVP_SIZE     |                                                                                                                            |       | 250  |       | mV    |

| VBUS OVP Accuracy         | VBUS_OVP_ACC      | VBUS_OVP = 9V to 22V                                                                                                       | -2    |      | 2     | %     |

| VBUS OVP Hysteresis       | VBUS_OVP_HYS      |                                                                                                                            |       | 400  |       | mV    |

| VBUS OVP Reaction Time    | tvbus_ovp_re      | During between VBUS over VBUS_OVP threshold and device start to turn off charger, VBUS_OVP set 1.1 times the level of VBUS | ŀ     | 75   |       | ns    |

| IBUS OCP Range            | IBUS_OCP_RAN      | Rising                                                                                                                     | 2     | -    | 6     | Α     |

| IBUS OCP Step Size        | IBUS_OCP_SIZE     |                                                                                                                            | 1     | 500  |       | mA    |

|                           |                   | In bypass mode                                                                                                             | -10   | 1    | 10    |       |

| IBUS OCP Accuracy         | IBUS_OCP_ACC      | In DIV2 mode, fsw = 500kHz,<br>IBUS_OCP = 2A to 3A                                                                         | -15   |      | 15    | %     |

| IBUS OCP Deglitch         | tibus_ocp_deg     |                                                                                                                            |       |      | 100   | μS    |

| Parameter                           | Symbol             | Test Conditions                                                                                                  | Min  | Тур   | Max   | Unit  |

|-------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------|------|-------|-------|-------|

| VOUT_ERR Detect Level               | tvout_err          | VBUS = 5V, in Bypass or DIV2 mode                                                                                | 0.8  | 1     | 1.2   | V     |

| VOUT_ERR Off Time                   | tvout_err_off_time | Only active in Bypass mode, select by register 0x11[1] = 0, default                                              | 36   | 40    | 44    | ms    |

|                                     |                    | Only active in Bypass mode, select by register 0x11[1] = 1                                                       | 72   | 80    | 88    |       |

| CFLY_DIAG Detect Level              | VCFLY_DIAG         | Detect CFL pin voltage when CFLY pre-charge is finished in DIV2 mode or reverse DIV2 mode.                       | 0.8  | 1     | 1.2   | V     |

| Thermal Shutdown<br>Threshold       | TDIE_OTP_TH        |                                                                                                                  | 1    | 140   |       | °C    |

| Thermal Shutdown<br>Hysteresis      | TDIE_OTP_HYS       |                                                                                                                  | 1    | 20    |       | °C    |

| Thermal Shutdown<br>Deglitch Time   | ttdie_deg          | Rising/Falling                                                                                                   |      | 10    |       | ms    |

| VBUS_LOW_ERR                        | VBUS_LOW_ERR_ACC   | VBUS_LOW_ERR = VBUS/VOUT, falling threshold for device can start reverse DIV2 mode but can't start DIV2 mode.    | 1.95 | 1.975 | 2     | - V/V |

| Accuracy                            |                    | VBUS_LOW_ERR = VBUS/VOUT, falling threshold for device can start reverse bypass mode but can't start bypass mode | 0.98 | 0.99  | 1     |       |

| VBUS_LOW_ERR                        | VBUS_LOW_ERR_HYS   | VBUS_LOW_ERR rising hysteresis for device can start DIV2 mode but can't start reverse DIV2 mode.                 |      |       | 0.025 | \/\/  |

| Hysteresis                          |                    | VBUS_LOW_ERR rising hysteresis for device can start bypass mode but can't start reverse bypass mode.             |      |       | 0.018 | V/V   |

| VBUS LOW ERR Deglitch               | tvbus_low_err_deg  |                                                                                                                  |      |       | 15    | μS    |

| Converter OCP Threshold             | ICON_OCP_TH        | fsw = 500kHz, VBUS = 10V                                                                                         | 10.8 | 12    | 13.2  | Α     |

| Function Threshold and A            | Accuracy           |                                                                                                                  |      |       |       |       |

| VOUT Pre-Charge<br>Current Range    | IOUT_PRE_CHG_RAN   | Default = 500mA per phase                                                                                        | 330  |       | 660   | mA    |

| VOUT Pre-Charge<br>Current Accuracy | IOUT_PRE_CHG_ACC   | VBUS = 9.5V, in DIV2 single phase mode, PRECHARGE_CURRENT = 500mA                                                | -20  |       | 20    | %     |

|                                     |                    | Select by register 0x11[3:2] = 00                                                                                |      | 0.5   |       |       |

|                                     |                    | Select by register 0x11[3:2] = 01                                                                                |      | 1     |       |       |

| VOUT Pre-Charge Timing              | tvout_pre_chg      | Select by register 0x11[3:2] = 10, default                                                                       |      | 2     |       | ms    |

|                                     |                    | Select by register 0x11[3:2] = 11                                                                                |      | 4     |       |       |

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

DS9758-03 May 2023 www.richtek.com

| Parameter                           | Symbol            | Test Conditions                                                           | Min  | Тур  | Max  | Unit |

|-------------------------------------|-------------------|---------------------------------------------------------------------------|------|------|------|------|

| CFLY Pre-Charge Current Range       | ICFLY_PRE_CHG_RAN | Default = 500mA per phase                                                 | 330  |      | 660  | mA   |

| CFLY Pre-Charge Current<br>Accuracy | ICFLY_PRE_CHG_ACC | VBUS = 9.5V, in DIV2 single phase mode, PRECHARGE_CURRENT = 500mA         | -20  |      | 20   | %    |

|                                     |                   | Select by register 0x11[7:6] = 00                                         |      | 0.5  |      |      |

|                                     |                   | Select by register 0x11[7:6] = 01                                         |      | 1    |      |      |

| CFLY Pre-Charge Timing              | tCFLY_PRE_CHG     | Select by register 0x11[7:6] = 10, default                                |      | 2    |      | ms   |

|                                     |                   | Select by register 0x11[7:6] = 11                                         |      | 4    |      |      |

| AT Function Threshold Range         | VAT_FUNCTION_RAN  |                                                                           | 9    |      | 12   | V    |

| AT Function Threshold<br>Step Size  | VAT_FUNCTION_SIZE |                                                                           |      | 0.5  |      | V    |

| AT Function Threshold<br>Accuracy   | VAT_FUNCTION_ACC  | Rising                                                                    | -150 |      | 200  | mV   |

| AT Function Hysteresis              | VAT_FUNCTION_HYS  | Falling                                                                   |      | 400  |      | mV   |

| AT Function Deglitch                | tat_function_deg  |                                                                           | 8    | 10   | 12   | ms   |

| Synchronize Function                |                   |                                                                           |      |      |      |      |

| SYNC Output High Level              | Voh_sync          | VBUS = 5V to 21V, synchronize function enable, master mode                |      | 4.2  |      | V    |

| SYNC Output Low Level               | Vol_sync          | VBUS = 5V to 21V, synchronize function enable, master mode                | -0.3 |      | 0.3  | V    |

| SYNC Duty Cycle                     | DMAX_SYNC         | DIV2 mode, synchronize function enable, master mode                       |      |      | 50   | %    |

| SYNC Frequency                      | fsw_sync          | fsw = 500kHz, synchronize<br>frequency is twice as switching<br>frequency | 900  | 1000 | 1100 | kHz  |

| SYNC Output Current<br>Limit        | ILIM_SYNC         | SYNC pin short, WRX_IN = 10V                                              |      |      | 42   | mA   |

| Pull Down Resistor                  |                   |                                                                           |      |      |      |      |

| VBUS Pull Down                      | RVBUS_PD          | VBUS = 5V to 12V                                                          |      | 0.75 |      | kΩ   |

| WRX_IN Pull Down                    | RWRX_IN_PD        | WRX_IN = 5V to 12V                                                        |      | 1    |      | kΩ   |

| VOUT Pull Down                      | RVOUT_PD          | VOUT = 5V to 12V                                                          |      | 0.75 |      | kΩ   |

| Parameter                                         | Symbol                  | Test Conditions                                                                     | Min  | Тур   | Max  | Unit |

|---------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------|------|-------|------|------|

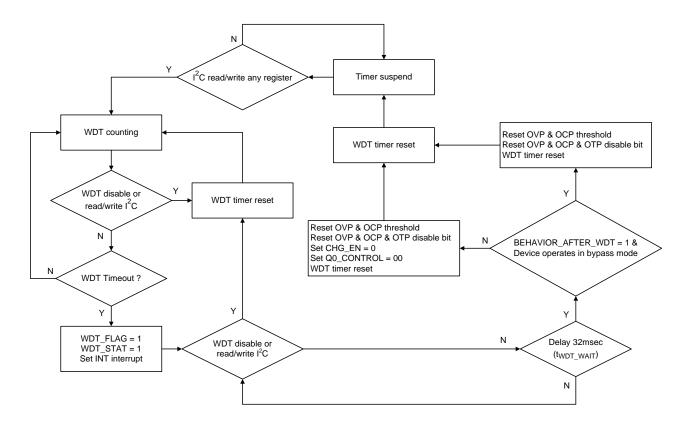

| Watchdog Time Out                                 |                         |                                                                                     |      |       |      |      |

|                                                   |                         | No $I^2C$ communication for 3.75s, set by Register 0x0E[6:4] = 000                  | 3    | 3.75  | 4.5  |      |

|                                                   |                         | No $I^2C$ communication for 7.5s, set by Register 0x0E[6:4] = 001                   | 6    | 7.5   | 9    |      |

|                                                   |                         | No I <sup>2</sup> C communication for<br>11.25s, set by Register 0x0E[6:4]<br>= 010 | 9    | 11.25 | 13.5 |      |

| Watchdag Time Out                                 | WDT                     | No $I^2C$ communication for 15s, set by Register 0x0E[6:4] = 011                    | 12   | 15    | 18   |      |

| Watchdog Time Out                                 | VVD1                    | No I <sup>2</sup> C communication for 30s, set by Register 0x0E[6:4] = 100, default | 24   | 30    | 36   | sec  |

|                                                   |                         | No $I^2C$ communication for 60s, set by Register 0x0E[6:4] = 101                    | 48   | 60    | 72   |      |

|                                                   |                         | No $I^2C$ communication for 90s, set by Register 0x0E[6:4] = 110                    | 72   | 90    | 108  | -    |

|                                                   |                         | No $I^2C$ communication for 120s, set by Register 0x0E[6:4] = 111                   | 96   | 120   | 144  |      |

| Control Input Pin (EN)                            |                         |                                                                                     |      |       |      |      |

| Input High Threshold<br>Voltage                   | VIH_EN                  |                                                                                     | 1.3  |       |      | V    |

| Input Low Threshold<br>Voltage                    | VIL_EN                  |                                                                                     |      |       | 0.4  | V    |

| Input Floating Threshold Voltage                  | VIH_EN_FLOATING         | EN pin is floating                                                                  |      | 1.7   |      | V    |

| Logic Output Pin (INT)                            |                         |                                                                                     |      |       |      |      |

| INT Pin Pull Low Time                             | tint_pull_low           |                                                                                     |      | 256   |      | μS   |

| Logic Output Pin (WRX_C                           | OK)                     |                                                                                     |      |       |      |      |

| WRX_OK Output High<br>Level                       | VOH_WRX_OK              | WRX_IN > 5V, Q0 turn on                                                             | 4.8  | 5     | 5.2  | V    |

| WRX_OK Output Low<br>Level                        | Vol_wrx_ok              | WRX_IN < WRX_INSERT                                                                 | -0.3 |       | 0.3  | V    |

| WRX_OK Output Current Limit                       | I <sub>LIM_WRX_OK</sub> | WRX_OK pin short                                                                    |      |       | 42   | mA   |

| Address Detection                                 |                         |                                                                                     |      |       |      |      |

| Input Low Threshold for Slave Address = 0x50      | VIL_ADDRESS             |                                                                                     |      |       | 0.4  | V    |

| Input Floating Threshold for Slave Address = 0x51 | VIM_ADDRESS             | ADDR pin is floating                                                                |      | 0.9   |      | V    |

| Input High Threshold for Slave Address = 0x52     | VIH_ADDRESS             |                                                                                     | 1.3  |       |      | V    |

| Input Leakage Current                             | ILKG_ADDRESS            | ADDR pin = 0V or 1.8V                                                               |      |       | 5    | μΑ   |

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

| Parameter                                  | Symbol             | Test Conditions                                                                                                                                                                                                                                                                                                  | Min | Тур | Max | Unit |

|--------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Timing                                     |                    |                                                                                                                                                                                                                                                                                                                  |     |     |     |      |

| Device Wake Up Time                        | twake_up           | Duration time between V <sub>DDA</sub> > V <sub>DDA_UVLO</sub> and device can start I <sup>2</sup> C communication                                                                                                                                                                                               | 1   | 500 |     | μS   |

| Device into Standby<br>Mode Time           | tSTANDBY_DELAY     | Duration time from Present mode to Standby mode                                                                                                                                                                                                                                                                  | 1   | 300 |     | μS   |

| Soft-Start Time for<br>Bypass Mode         | tss_bypass         | Timing about VOUT pre-charge to VBUS and Bypass RON fully turn on when Bypass mode is enabled with no load, Pre-charge current = 500mA,  VOUT_ERR_ON_TIME = 2msec, COUT = 22µF x 1, VBUS = 5V                                                                                                                    | 1   |     | 3   | ms   |

| Soft-Start Time for DIV2<br>Mode           | tss_DIV2           | Timing about CFLY and VOUT pre-charge to (VBUS/2) and start switching when DIV2 mode is enabled with no load, Pre-charge current = $500\text{mA}$ , CFLY_DIAG_TIME = $2\text{msec}$ , VOUT_ERR_ON_TIME = $2\text{msec}$ , CFLY = $22\mu\text{F}$ x 2 each phase, COUT = $22\mu\text{F}$ x 1, VBUS = $10\text{V}$ |     |     | 5   | ms   |

| Soft-Start Time for<br>Reverse Bypass Mode | tss_reverse_bypass | Timing about Bypass RON fully turn on when Reverse Bypass mode is enabled with no load, Pre-charge current = 500mA, VOUT_ERR_ON_TIME = 2msec, VOUT = 5V                                                                                                                                                          | 1   |     | 3   | ms   |

| Soft-Start Time for<br>Reverse DIV2 Mode   | tss_reverse_div2   | Timing about CFLY from 0V to 5V and start switching when reverse DIV2 mode is enabled with no load, Pre-charge current = 500mA, CFLY_DIAG_TIME = 2msec, CFLY = 22µF x 2 each phase, VOUT = 5V                                                                                                                    | 1   |     | 4   | ms   |

| Turn on Q0 Delay Time                      | tQ0_DELAY          | 0x0D[1:0] = 10, Duration time<br>between WRX_IN ><br>WRX_INSERT and Q0 start to<br>turn on                                                                                                                                                                                                                       | 1   | 2   |     | ms   |

| OVP Recovery Time                          | tova prodyrav      | Only active in Bypass mode with register 0x0E[7] = 1, Select by register 0x0F[7] = 0                                                                                                                                                                                                                             | 17  | 21  | 25  | me   |

| OVP Recovery Time                          | tovp_recovery      | Only active in Bypass mode with register 0x0E[7] = 1, Select by register 0x0F[7] = 1                                                                                                                                                                                                                             | 80  | 100 | 120 | ms   |

| WRX_OK Pull Up Time                        | twrx_ok_pull_up    | VBUS > 5V, in standby mode,<br>WRX_OK pin is floating, Duration<br>time between WRX_IN ><br>WRX_INSERT and WRX_OK<br>pull to high level                                                                                                                                                                          | 1   | 16  |     | μ\$  |

| Parameter                                         | Symbol    | Test Conditions                 | Min  | Тур | Max  | Unit  |  |  |  |

|---------------------------------------------------|-----------|---------------------------------|------|-----|------|-------|--|--|--|

| Watchdog Reset Wait<br>Time                       | twdt_wait |                                 |      | 32  |      | ms    |  |  |  |

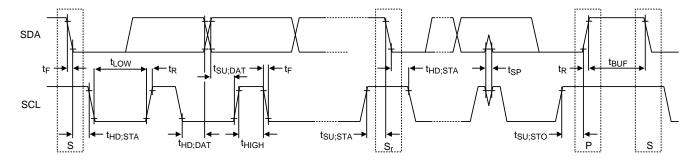

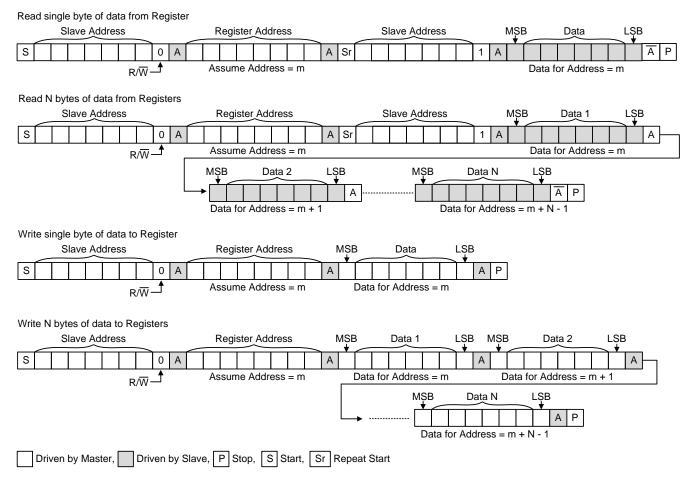

| I <sup>2</sup> C Characteristics                  |           | -                               | 1    | ·   | •    |       |  |  |  |

| SCL, SDA High-Level<br>Input Threshold Voltage    | VIH_I2C   |                                 | 1.5  |     |      | V     |  |  |  |

| SCL, SDA Low-Level<br>Input Threshold Voltage     | VIL_I2C   |                                 |      |     | 0.4  | V     |  |  |  |

|                                                   |           | Standard-mode                   |      |     | 100  | _     |  |  |  |

|                                                   |           | Fast-mode                       |      |     | 400  | kHz   |  |  |  |

| SCL Clock Frequency                               | fclk      | Fast-mode plus                  |      |     | 1000 |       |  |  |  |

|                                                   |           | High-speed mode Cb = 400pF      |      |     | 1.7  | MHz   |  |  |  |

|                                                   |           | High-speed mode Cb = 100pF      |      |     | 3.4  | IVITZ |  |  |  |

| Bus Free Time between<br>Stop and Start Condition |           | Standard-mode                   | 4.7  |     |      |       |  |  |  |

|                                                   | tBUF      | Fast-mode                       | 1.3  |     |      | μS    |  |  |  |

|                                                   |           | Fast-mode plus                  | 0.5  |     |      |       |  |  |  |

|                                                   |           | Standard-mode                   | 4    |     |      |       |  |  |  |

| (Repeated) Start Hold<br>Time                     |           | Fast-mode                       | 0.6  |     |      |       |  |  |  |

|                                                   | thd;sta   | Fast-mode plus                  | 0.26 |     |      | μS    |  |  |  |

|                                                   |           | High-speed mode Cb = 400pF      | 160  |     |      |       |  |  |  |

|                                                   |           | High-speed mode Cb = 100pF      | 160  |     |      |       |  |  |  |

|                                                   | tsu;sta   | Standard-mode                   | 4.7  |     |      |       |  |  |  |

|                                                   |           | Fast-mode                       | 0.6  |     |      | μs    |  |  |  |

| (Repeated) Start Setup<br>Time                    |           | Fast-mode Plus                  | 0.26 |     |      |       |  |  |  |

| Time                                              |           | High-speed mode Cb = 400 pF     | 160  |     |      |       |  |  |  |

|                                                   |           | High-speed mode Cb = 100 pF 160 |      |     |      | ns    |  |  |  |

|                                                   |           | Standard-mode                   | 4    |     |      |       |  |  |  |

|                                                   |           | Fast-mode                       | 0.6  |     |      | μS    |  |  |  |

| STOP Condition Setup Time                         | tsu;sto   | Fast-mode plus                  | 0.26 |     |      |       |  |  |  |

| Time                                              |           | High-speed mode Cb = 400pF      | 160  |     |      |       |  |  |  |

|                                                   |           | High-speed mode Cb = 100pF      | 160  |     |      | ns    |  |  |  |

|                                                   |           | Standard-mode                   | 0.1  |     |      |       |  |  |  |

|                                                   |           | Fast-mode                       | 0.1  |     |      |       |  |  |  |

| SDA Data Hold Time                                | thd;dat   | Fast-mode plus                  | 0.1  |     |      | ns    |  |  |  |

|                                                   |           | High-speed mode Cb = 400pF      | 0.1  |     | 150  |       |  |  |  |

|                                                   |           | High-speed mode Cb = 100pF      | 0.1  |     | 70   |       |  |  |  |

|                                                   |           | Standard-mode                   |      |     | 3.45 |       |  |  |  |

| SDA Valid Acknowledge                             | tvd;ack   | Fast-mode                       |      |     | 0.9  | μS    |  |  |  |

| ïme                                               |           | Fast-mode plus                  |      |     | 0.45 |       |  |  |  |

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

DS9758-03 May 2023 www.richtek.com

| Parameter           | Symbol  | Test Conditions            | Min  | Тур | Max | Unit |

|---------------------|---------|----------------------------|------|-----|-----|------|

|                     |         | Standard-mode              | 250  |     |     |      |

|                     |         | Fast-mode                  | 100  |     |     |      |

| SDA Setup Time      | tsu;dat | Fast-mode plus             | 50   |     |     | ns   |

|                     |         | High-speed mode Cb = 400pF | 10   |     |     |      |

|                     |         | High-speed mode Cb = 100pF | 10   |     |     |      |

|                     | tLOW    | Standard-mode              | 4.7  |     |     |      |

|                     |         | Fast-mode                  | 1.3  |     |     | μS   |

| SCL Clock Low Time  |         | Fast-mode plus             | 0.5  |     |     |      |

|                     |         | High-speed mode Cb = 400pF | 320  |     |     |      |

|                     |         | High-speed mode Cb = 100pF | 160  |     |     | ns   |

|                     |         | Standard-mode              | 4    |     |     |      |

|                     |         | Fast-mode                  | 0.6  |     |     | μS   |

| SCL Clock High Time | thigh   | Fast-mode plus             | 0.26 |     |     |      |

|                     |         | High-speed mode Cb = 400pF | 120  |     |     |      |

|                     |         | High-speed mode Cb = 100pF | 60   |     |     | ns   |

- Note 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2. θ<sub>JA</sub> is measured under natural convection (still air) at T<sub>A</sub> = 25°C with the component mounted on a high effective-thermalconductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- **Note 4.** The device is not guaranteed to function outside its operating conditions.

- Note 5. Specification is guaranteed by design and/or correlation with statistical process control.

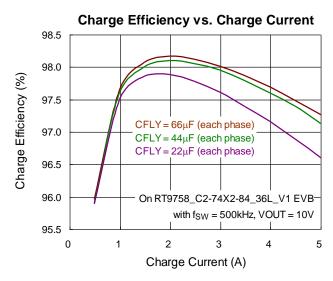

## **Typical Operating Characteristics**

May 2023

DS9758-03

# **Register Map**

### **Register Map Summary**

| Function Name              | STAT    | FLAG    | MASK    | Threshold | Enable  | Deglitch  |

|----------------------------|---------|---------|---------|-----------|---------|-----------|

| VOUT_OVP                   | 0x09[6] | 0x02[6] | 0x06[6] | 0x0A[2:0] | 0x12[7] |           |

| VBUS_OVP                   | 0x09[7] | 0x02[7] | 0x06[7] | 0x0B[5:0] | 0x12[6] |           |

| IBUS_OCP                   | 0x09[3] | 0x03[7] | 0x07[7] | 0x0C[7:4] | 0x12[4] |           |

| WRX_IRE_OCP                | 0x09[2] | 0x03[6] | 0x07[6] | 0x0C[3:0] | 0x12[3] |           |

| CON_OCP                    |         | 0x01[7] | 0x05[7] |           |         |           |

| TDIE_OTP                   | 0x09[1] | 0x02[1] | 0x06[1] |           | 0x12[5] |           |

| TDIE_OTP_EXIT              |         | 0x02[2] | 0x06[2] |           |         |           |

| VBUS_LOW_ERR               | 0x08[3] | 0x01[4] | 0x05[4] |           |         |           |

| CFLY_DIAG                  |         | 0x01[6] | 0x05[6] |           |         |           |

| VOUT_ERR                   |         | 0x01[3] | 0x05[3] |           |         |           |

| WRX_INSERT                 | 0x08[2] | 0x01[2] | 0x05[2] |           |         |           |

| VBUS_INSERT                | [0]80x0 | 0x01[0] | 0x05[0] |           |         |           |

| VOUT_INSERT                | 0x08[4] | 0x01[5] | 0x05[5] |           |         |           |

| WDT                        | 0x09[0] | 0x02[0] | 0x06[0] | 0x0E[6:4] | 0x0E[3] |           |

| SWITCHING_ENABLED          | 0x08[1] | 0x01[1] | 0x05[1] |           |         |           |

| IN_VALID_RECOVERY_DEGLITCH |         |         | 1       |           |         | 0x0F[7]   |

| CFLY_DIAG_TIME             |         |         |         |           |         | 0x11[7:6] |

| VOUT_ERR_ON_TIME           |         |         | -       |           |         | 0x11[3:2] |

| VOUT_ERR_OFF_TIME          |         |         | 1       |           |         | 0x11[1]   |

| AT_FUNCTION                |         |         | 1       | 0x10[2:0] | 0x10[3] |           |

| SINGLE_PHASE_MODE_EN       |         |         | 1       | 0x0D[5:4] |         |           |

| FSW                        |         |         | -       | 0x0F[5:3] |         |           |

| OPERATION_MODE_SELECTION   |         |         | 1       | 0x0F[0]   |         |           |

| PHASE_A_ANGLE              |         |         | -       | 0x10[7:6] |         |           |

| PHASE_B_ANGLE              |         |         | 1       | 0x10[5:4] |         |           |

| PRECHARGE_CURRENT          |         |         | 1       | 0x11[5:4] |         |           |

| REG_RST                    |         |         | 1       | 0x12[2]   |         |           |

| BEHAVIOR_AFTER_WDT         |         |         | -       |           | 0x11[0] |           |

| SPREAD_SPECTRUM            |         |         |         |           | 0x0F[6] |           |

| CHG_EN                     |         |         |         |           | 0x0F[2] |           |

| REVERE_MODE_EN             |         |         |         |           | 0x0F[1] |           |

| AUTO_RECOVERY_EN           |         |         |         |           | 0x0E[7] |           |

| OVERRIDE_WRX_OK_PIN_LOW    |         |         |         |           | 0x0E[2] |           |

| WRX_OK_EN                  |         |         |         |           | 0x0E[1] |           |

| WRX_OK_PSM                 |         |         |         |           | 0x0E[0] |           |

| Function Name    | STAT      | FLAG | MASK | Threshold | Enable    | Deglitch |

|------------------|-----------|------|------|-----------|-----------|----------|

| VBUS_PD_EN       |           |      |      |           | 0x0D[7]   |          |

| WRX_PD_EN        |           |      |      |           | 0x0D[6]   |          |

| VOUT_PD_EN       |           |      |      |           | 0x13[1]   |          |

| SYNC_SLAVE_EN    |           |      |      |           | 0x0D[3]   |          |

| SYNC_FUNCTION_EN |           |      |      |           | 0x0D[2]   |          |

| Q0_CONTROL       |           |      |      |           | 0x0D[1:0] |          |

| IC_STAT          | 0x04[2:0] |      |      |           |           |          |

### **Register Description**

R: Read only

RC: Read and clear RW: Read and write

RWSC: Read and write, also automatically set/clear by particular condition

Register Address: 0x00, Register Name: DEVICE\_INFO

| Bit | Bit Name           | Default | WDT<br>RST | REG<br>RST | Туре | Description                |

|-----|--------------------|---------|------------|------------|------|----------------------------|

| 7:4 | DEVICE<br>REVISION | XXXX    | N          | N          | R    | Device Revision            |

| 3:0 | Device ID          | 0011    | N          | N          | R    | Device ID<br>0011 = RT9758 |

Register Address: 0x01, Register Name: FLAG\_1

| Bit | Bit Name              | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                              |

|-----|-----------------------|---------|------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CON_OCP_<br>FLAG      | 0       | N          | N          | RC   | Set 1 and send an INT when converter current over than CON_OCP threshold. Clear upon read.  0: Normal 1: CON_OCP has occurred.                           |

| 6   | CFLY_DIAG_<br>FLAG    | 0       | N          | N          | RC   | Set 1 and send an INT when CFLY short during converter soft-start in DIV2 or reverse DIV2 mode. Clear upon read.  0 : Normal 1 : CFLY_DIAG has occurred. |

| 5   | VOUT_<br>INSERT_FLAG  | 0       | N          | N          | RC   | Set 1 and send an INT when VOUT voltage over than VOUT_INSERT threshold. Clear upon read.  0 : Normal 1 : VOUT_INSERT has occurred.                      |

| 4   | VBUS_LOW_<br>ERR_FLAG | 0       | N          | N          | RC   | Set 1 and send an INT when VBUS voltage lower than VBUS_LOW_ERR threshold. Clear upon read. 0 : Normal 1 : VBUS_LOW_ERR has occurred.                    |

| 3   | VOUT_ERR_<br>FLAG     | 0       | N          | N          | RC   | Set 1 and send an INT when VOUT short during converter soft-start in DIV2 mode or bypass mode. Clear upon read.  0 : Normal  1 : VOUT_ERR has occurred   |

| 2   | WRX_<br>INSERT_FALG   | 0       | N          | N          | RC   | Set 1 and send an INT when WRX_IN voltage over than WRX_INSERT threshold. Clear upon read.  0: Normal 1: WRX_INSERT has occurred.                        |

| Bit | Bit Name                       | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                       |

|-----|--------------------------------|---------|------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 1   | SWITCHING_<br>ENABLED_<br>FLAG | 0       | N          | N          | RC   | Set 1 and send an INT when the converter start working. Clear upon read.  0 : Normal  1 : Converter start switching.              |

| 0   | VBUS_<br>INSERT_FLAG           | 0       | N          | Y          | RC   | Set 1 and send an INT when VBUS voltage over than VBUS_INSERT threshold. Clear upon read.  0: Normal 1: VBUS_INSERT has occurred. |

Register Address: 0x02, Register Name: FLAG\_2

| Bit | Bit Name               | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                                              |

|-----|------------------------|---------|------------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VBUS_OVP_<br>FLAG      | 0       | N          | N          | RC   | Set 1 and send an INT when VBUS voltage over than VBUS_OVP threshold. Clear upon read.  0: Normal 1: VBUS_OVP has occurred.                                              |

| 6   | VOUT_OVP_<br>FLAG      | 0       | N          | N          | RC   | Set 1 and send an INT when VOUT voltage over than VOUT_OVP threshold. Clear upon read.  0: Normal 1: VOUT_OVP has occurred.                                              |

| 5:3 | Reserved               | 000     | NA         | NA         | NA   | Reserved                                                                                                                                                                 |

| 2   | TDIE_OTP_<br>EXIT_FLAG | 0       | N          | N          | RC   | Set 1 and send an INT when die temperature lower than TDIE_OTP release threshold after TDIE_OTP is triggered. Clear upon read.  0: Normal 1: TDIE_OTP_EXIT has occurred. |

| 1   | TDIE_OTP_<br>FLAG      | 0       | N          | N          | RC   | Set 1 and send an INT when die temperature over than TDIE threshold. Clear upon read.  0: Normal  1: TDIE_OTP has occurred.                                              |

| 0   | WDT_FLAG               | 0       | N          | N          | RC   | Set 1 and send an INT when watchdog timeout happen. Clear upon read.  0: Normal  1: WDT has occurred.                                                                    |

DS9758-03 May 2023 www.richtek.com

Register Address: 0x03, Register Name: FLAG\_3

| Bit | Bit Name             | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                           |

|-----|----------------------|---------|------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IBUS_OCP_<br>FLAG    | 0       | N          | N          | RC   | Set 1 and send an INT when IBUS current over than IBUS_OCP threshold. Clear upon read.  0: Normal  1: IBUS_OCP has occurred.                          |

| 6   | WRX_IRE_<br>OCP_FLAG | 0       | N          | N          | RC   | Set 1 and send an INT when current that from VBUS to WRX_IN over than WRX_IRE_OCP threshold. Clear upon read.  0: Normal 1: WRX_IRE_OCP has occurred. |

| 5:0 | Reserved             | 000000  | NA         | NA         | NA   | Reserved                                                                                                                                              |

Register Address: 0x04, Register Name: IC\_STAT

| Bit | Bit Name | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                                                                                               |

|-----|----------|---------|------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Reserved | 00000   | NA         | NA         | NA   | Reserved                                                                                                                                                                                                                  |

| 2:0 | IC_STAT  | 000     | N          | Y          | R/W  | Indicate converter operation status 000 : Present mode (default) 001 : Standby mode 010 : Forward DIV2 mode 011 : Forward bypass mode 100 : Reverse DIV2 mode 101 : Reverse bypass mode 110 : Charge Fault 111 : Reserved |

Register Address: 0x05, Register Name: MASK\_1

| Bit | Bit Name                       | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                         |

|-----|--------------------------------|---------|------------|------------|------|---------------------------------------------------------------------------------------------------------------------|

| 7   | CON_OCP_<br>MASK               | 1       | N          | Υ          | RW   | CON_OCP mask. 0 : Not mask IRQ of CON_OCP_FLAG 1 : Mask IRQ of CON_OCP_FLAG (default)                               |

| 6   | CFLY_DIAG_<br>MASK             | 1       | N          | Y          | RW   | CFLY_DIAG mask. 0 : Not mask IRQ of CFLY_DIAG_FLAG 1 : Mask IRQ of CFLY_DIAG_FLAG (default)                         |

| 5   | VOUT_<br>INSERT_<br>MASK       | 1       | N          | Y          | RW   | VOUT_INSERT mask. 0 : Not mask IRQ of VOUT_INSERT_FLAG 1 : Mask IRQ of VOUT_INSERT_FLAG (default)                   |

| 4   | VBUS_LOW_<br>ERR_MASK          | 1       | N          | Y          | RW   | VBUS_LOW_ERR mask. 0 : Not mask IRQ of VBUS_LOW_ERR_FLAG 1 : Mask IRQ of VBUS_LOW_ERR_FLAG (default)                |

| 3   | VOUT_ERR_<br>MASK              | 1       | N          | Υ          | RW   | VOUT_ERR mask. 0 : Not mask IRQ of VOUT_ERR_FLAG 1 : Mask IRQ of VOUT_ERR_FLAG (default)                            |

| 2   | WRX_INSERT<br>_MASK            | 1       | N          | Υ          | RW   | WRX_INSERT mask. 0 : Not mask IRQ of WRX_INSERT_FLAG 1 : Mask IRQ of WRX_INSERT_FLAG (default)                      |

| 1   | SWITCHING_<br>ENABLED_<br>MASK | 1       | N          | Y          | RW   | SWITCHING_ENABLED mask. 0 : Not mask IRQ of SWITCHING_ENABLED_FLAG 1 : Mask IRQ of SWITCHING_ENABLED_FLAG (default) |

| 0   | VBUS_<br>INSERT_<br>MASK       | 1       | N          | Υ          | RW   | VBUS_INSERT mask. 0 : Not mask IRQ of VBUS_INSERT_FLAG 1 : Mask IRQ of VBUS_INSERT_FLAG (default)                   |

Register Address: 0x06, Register Name: MASK\_2

| Bit | Bit Name               | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                             |

|-----|------------------------|---------|------------|------------|------|---------------------------------------------------------------------------------------------------------|

| 7   | VBUS_OVP_<br>MASK      | 1       | N          | Y          | RW   | VBUS_OVP mask. 0 : Not mask IRQ of VBUS_OVP_FLAG 1 : Mask IRQ of VBUS_OVP_FLAG (default)                |

| 6   | VOUT_OVP_<br>MASK      | 1       | N          | Y          | RW   | VOUT_OVP mask. 0 : Not mask IRQ of VOUT_OVP_FLAG 1 : Mask IRQ of VOUT_OVP_FLAG (default)                |

| 5:3 | Reserved               | 111     | NA         | NA         | NA   | Reserved                                                                                                |

| 2   | TDIE_OTP_<br>EXIT_MASK | 1       | N          | Y          | RW   | TDIE_OTP_EXIT mask. 0 : Not mask IRQ of TDIE_OTP_EXIT_FLAG 1 : Mask IRQ of TDIE_OTP_EXIT_FLAG (default) |

| 1   | TDIE_OTP_<br>MASK      | 1       | N          | Y          | RW   | TDIE_OTP mask. 0 : Not mask IRQ of TDIE_OTP_FLAG 1 : Mask IRQ of TDIE_OTP_FLAG (default)                |

| 0   | WDT_MASK               | 1       | N          | Y          | RW   | Watchdog timeout mask. 0 : Not mask IRQ of WDT_FLAG 1 : Mask IRQ of WDT_FLAG (default)                  |

Register Address: 0x07, Register Name: MASK\_3

| Bit | Bit Name             | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                       |

|-----|----------------------|---------|------------|------------|------|---------------------------------------------------------------------------------------------------|

| 7   | IBUS_OCP_<br>MASK    | 1       | N          | Υ          | RW   | IBUS_OCP mask. 0 : Not mask IRQ of IBUS_OCP_FLAG 1 : Mask IRQ of IBUS_OCP_FLAG (default)          |

| 6   | WRX_IRE_<br>OCP_MASK | 1       | N          | Υ          | RW   | WRX_IRE_OCP mask. 0 : Not mask IRQ of WRX_IRE_OCP_FLAG 1 : Mask IRQ of WRX_IRE_OCP_FLAG (default) |

| 5:0 | Reserved             | 111111  | NA         | NA         | NA   | Reserved                                                                                          |

Register Address: 0x08, Register Name: STAT\_1

| Bit | Bit Name                       | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                                                            |

|-----|--------------------------------|---------|------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Reserved                       | 000     | NA         | NA         | NA   | Reserved                                                                                                                                                                               |

| 4   | VOUT_<br>INSERT_STAT           | 0       | N          | N          | R    | Set 1 when VOUT voltage above the VOUT_INSERT threshold. Persists until condition is no longer valid.  0 : Normal 1 : VOUT_INSERT is occurring.                                        |

| 3   | VBUS_LOW_<br>ERR_STAT          | 0       | N          | N          | R    | Set 1 when VBUS voltage below the VBUS_LOW_ERR threshold. Persists until condition is no longer valid.  0 : Normal 1 : VBUS_LOW_ERR is occurring.                                      |

| 2   | WRX_<br>INSERT_STAT            | 0       | N          | N          | R    | Set 1 when WRX_IN voltage above the WRX_INSERT threshold. Persists until condition is no longer valid.  0 : Normal  1 : WRX_INSERT is occurring.                                       |

| 1   | SWITCHING_<br>ENABLED_<br>STAT | 0       | N          | N          | R    | Set 1 and send an INT when the converter start working. Only one INT is sent when switching starts. Persists until condition is no longer valid.  0: Normal 1: SWITCHING is occurring. |

| 0   | VBUS_<br>INSERT_STAT           | 0       | N          | N          | R    | Set 1 when VBUS voltage above the VBUS_INSERT threshold. Persists until condition is no longer valid.  0 : Normal  1 : VBUS_INSERT is occurring.                                       |

DS9758-03 May 2023

Register Address: 0x09, Register Name: STAT\_2

| Bit | Bit Name             | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                                         |

|-----|----------------------|---------|------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VBUS_OVP_<br>STAT    | 0       | N          | N          | R    | Set 1 when VBUS voltage above the VBUS_OVP threshold. Persists until condition is no longer valid.  0 : Normal  1 : VBUS_OVP is occurring.                          |

| 6   | VOUT_OVP_<br>STAT    | 0       | N          | N          | R    | Set 1 when VOUT voltage above the VOUT_OVP threshold. Persists until condition is no longer valid.  0 : Normal  1 : VOUT_OVP is occurring.                          |

| 5:4 | Reserved             | 00      | NA         | NA         | NA   | Reserved                                                                                                                                                            |

| 3   | IBUS_OCP_<br>STAT    | 0       | N          | N          | R    | Set 1 when IBUS current above the IBUS_OCP threshold. Persists until condition is no longer valid.  0 : Normal  1 : IBUS_OCP is occurring.                          |

| 2   | WRX_IRE_<br>OCP_STAT | 0       | N          | N          | R    | Set 1 when current that from VBUS to WRX_IN above the WRX_IRE_OCP threshold. Persists until condition is no longer valid.  0 : Normal 1 : WRX_IRE_OCP is occurring. |