Rev. 2 — 02/2023

Data Sheet: Technical Data

- This document provides electrical specifications for S32G3.

- For functional characteristics and the programming model, see S32G3 Reference Manual.

NXP reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

# Contents

| 1      | Introduction4                                   |

|--------|-------------------------------------------------|

| 1.1    | Overview4                                       |

| 1.2    | Applications4                                   |

| 2      | Block diagram5                                  |

| 3      | Feature comparison5                             |

| 4      | Ordering information8                           |

| 5      | Electrostatic Discharge (ESD) Characteristics9  |

| 6      | Absolute Max Ratings9                           |

| 7      | Operating conditions13                          |

| 7.1    | Operating Conditions13                          |

| 7.2    | Clock frequency ranges 19                       |

| 8      | Thermal Characteristics                         |

| 9      | DC electricals22                                |

| 9.1    | Total power specifications for 0.8V and 1.8V    |

|        | Analog Domains22                                |

| 9.2    | Static power specifications for I/O Domains. 24 |

| 9.3    | Device Power and Operating Current              |

|        | Specifications25                                |

| 10     | Power sequencing29                              |

| 10.1   | Power-up29                                      |

| 10.2   | Power-down                                      |

| 11     | Electromagnetic compatibility (EMC)             |

| 12     | GPIO Pads                                       |

| 13     | Aurora specifications40                         |

| 13.1   | Aurora Pads40                                   |

| 13.2   | Aurora Port Timing43                            |

| 13.3   | Aurora PLL44                                    |

| 14     | Power Management Controller (PMC) 46            |

| 14.1   | PMC Bandgap46                                   |

| 15     | Reset46                                         |

| 15.1   | Reset Duration46                                |

| 15.2   | Reset and Standby related pad electrical        |

|        | characteristics50                               |

| 15.3   | PMIC Standby Mode Entry / Exit Protocol 52      |

| 16     | Peripheral specifications54                     |

| 16.1   | Analog Modules54                                |

| 16.1.1 | SAR ADC54                                       |

| 16.1.2 | Temperature Monitoring Unit (TMU)56             |

| 16.1.3 | Glitch Filter57                                 |

| 16.1.4 | IRQ57                                           |

| 16.2   | Clock and PLL Interfaces58                      |

| 16.2.1 | DFS58                                           |

| 16.2.2 | FIRC59                                          |

| 16.2.3 | SIRC 59                                         |

| 16.2.4 | FXOSC59                                         |

| 16.2.5 | PLL61                                           |

| 16.3   | Communication modules63                         |

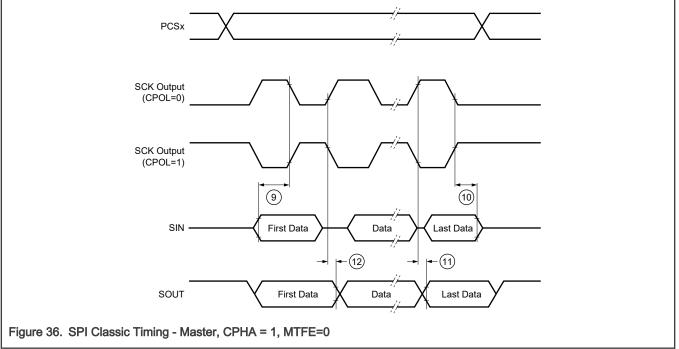

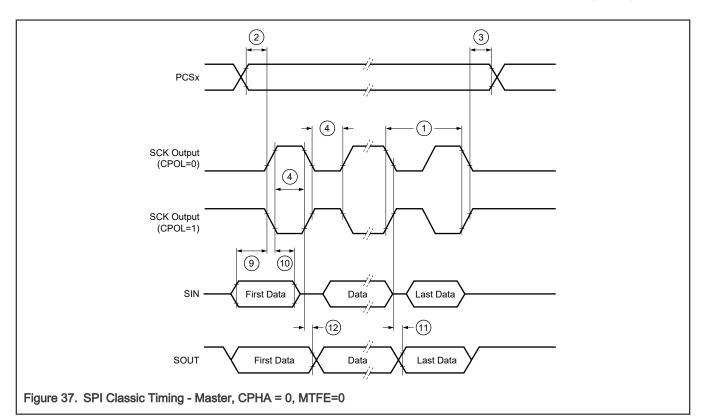

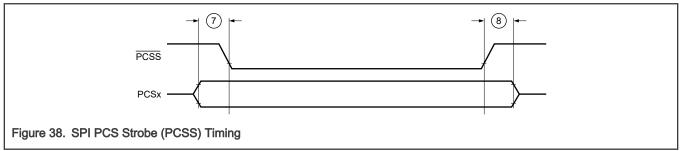

| 16.3.1 | SPI63                                           |

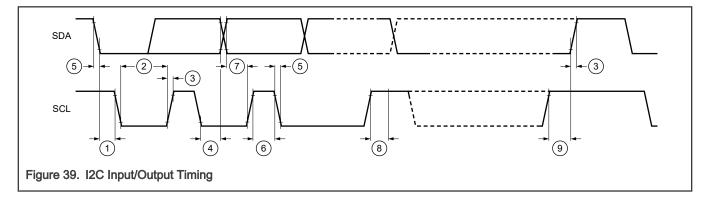

| 16.3.2 | I2C                                             |

| 16.3.4 | LIN                                             |

| 16.3.5  | LPSPI                             | 71    |

|---------|-----------------------------------|-------|

| 16.3.6  | CAN                               | 74    |

| 16.4    | FlexRay                           | 74    |

| 16.4.1  | FlexRay - RxD                     |       |

| 16.4.2  | FlexRay - TxD                     |       |

| 16.4.3  | FlexRay - TxEN                    |       |

| 16.9    | PCIe                              |       |

| 16.6    | GMAC and PFE                      | 81    |

| 16.6.1  | GMAC and PFE Management Interface |       |

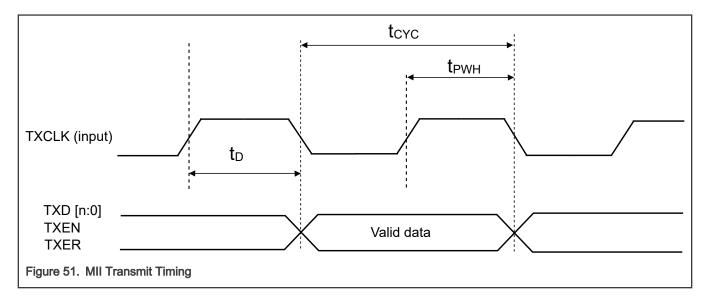

| 16.6.2  | GMAC and PFE MII                  | 82    |

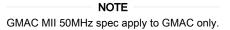

| 16.6.3  | GMAC MII 50MHz                    |       |

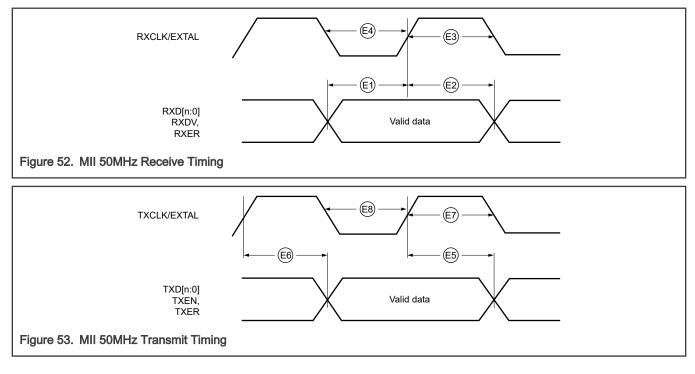

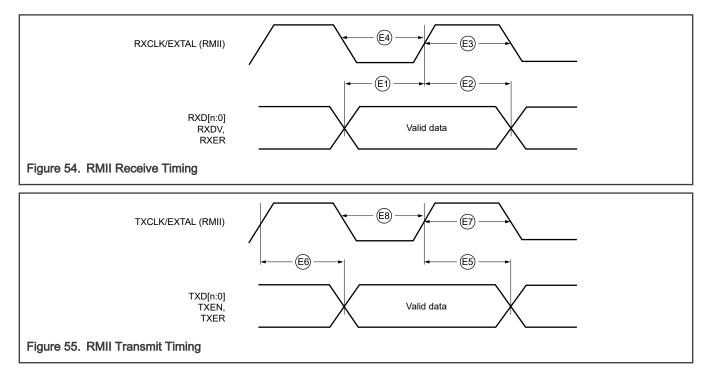

| 16.6.4  | GMAC and PFE RMII                 | 84    |

| 16.6.5  | GMAC and PFE RGMII                | 85    |

| 16.6.6  | GMAC and PFE SGMII                | 87    |

| 16.12   | USB-ULPI                          | 88    |

| 16.8    | Memory interfaces                 | 89    |

| 16.8.1  | QuadSPI                           |       |

| 16.8.2  | QuadSPI Quad 1.8V DDR 66MHz       | 89    |

| 16.8.3  | QuadSPI Octal 1.8V SDR 133MHz     | 90    |

| 16.8.4  | QuadSPI Octal 1.8V DDR 100MHz     | 90    |

| 16.8.5  | QuadSPI Octal 1.8V DDR 133MHz     | 91    |

| 16.8.6  | QuadSPI Octal 1.8V SDR 100MHz     | 92    |

| 16.8.7  | QuadSPI Quad 1.8V SDR 133MHz      | 93    |

| 16.8.8  | QuadSPI Quad 3.3V DDR 66MHz       | 93    |

| 16.8.9  | QuadSPI Quad 3.3V SDR 104MHz      | 94    |

| 16.8.10 | QuadSPI Octal 1.8V DDR 166MHz     | 95    |

| 16.8.11 | QuadSPI Octal 1.8V DDR 200MHz     | 95    |

| 16.8.12 | QuadSPI configurations            | 96    |

| 16.8.13 | QuadSPI interfaces                | 97    |

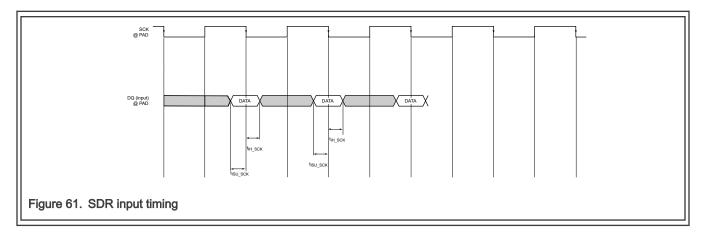

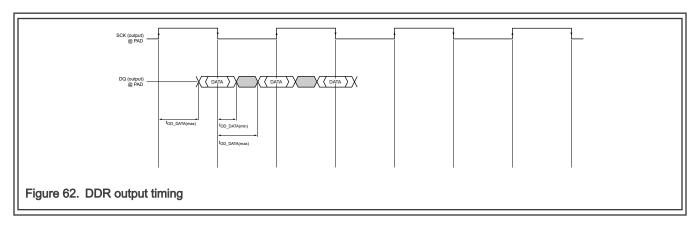

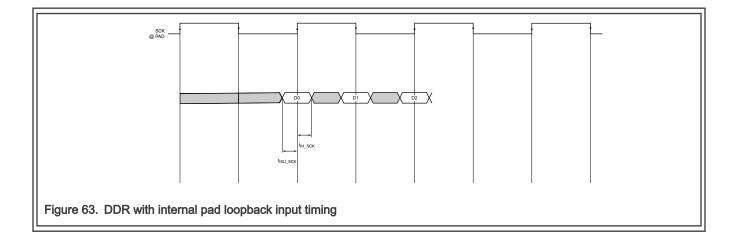

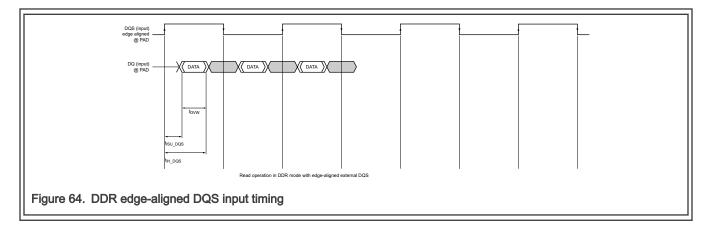

| 16.8.14 | QuadSPI timing diagrams           | 98    |

| 16.9    | DDR                               | 99    |

| 16.9.1  | DDR                               | 99    |

| 16.9.2  | DDR Common DC Input               | 99    |

| 16.9.3  | DDR Common DC Output              | 100   |

| 16.9.4  | DDR3L DC Input                    | 101   |

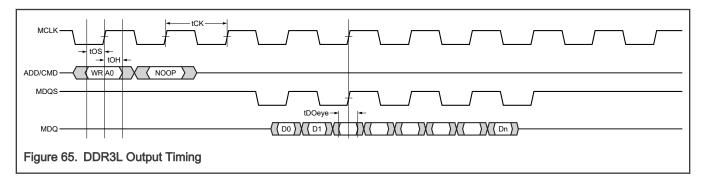

| 16.9.5  | DDR3L Output Timing               | 101   |

| 16.9.6  | LPDDR4 DC Input timing            |       |

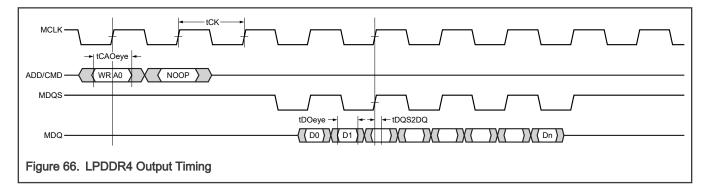

| 16.9.7  | LPDDR4 Output Timing              | . 102 |

| 16.10   | uSDHC                             |       |

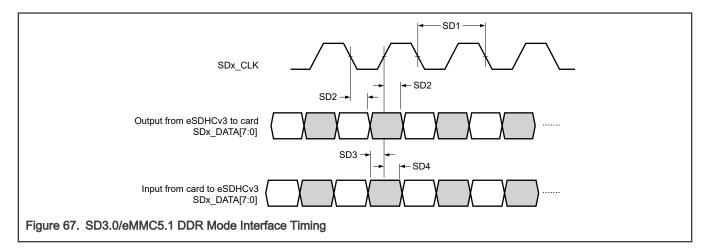

| 16.10.1 | uSDHC SD3.0/eMMC5.1 DDR           |       |

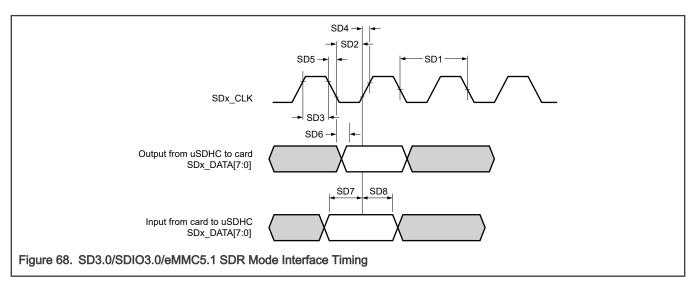

| 16.10.2 | uSDHC SD3.0/SDIO3.0/eMMC5.1 SDR   |       |

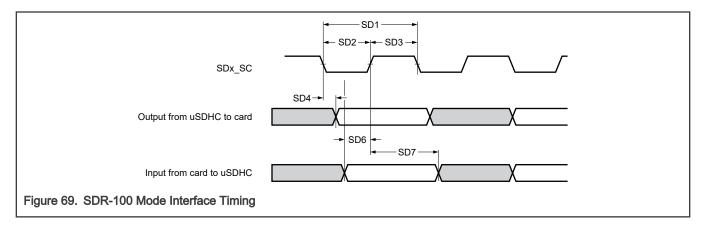

| 16.10.3 | uSDHC SDR-100MHz                  | 105   |

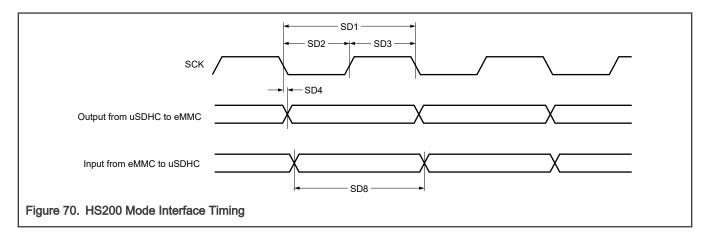

| 16.10.4 | uSDHC SDR-HS200                   |       |

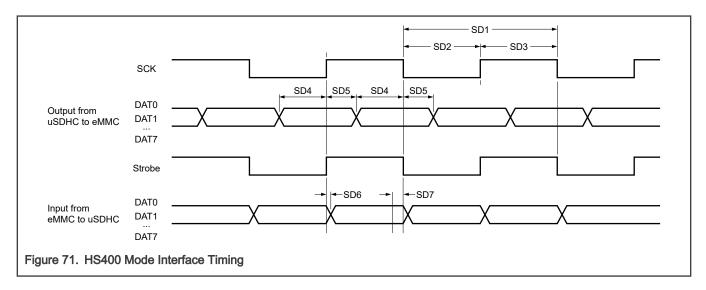

| 16.10.5 | uSDHC DDR-HS400                   | 107   |

| 16.11   | Debug modules                     |       |

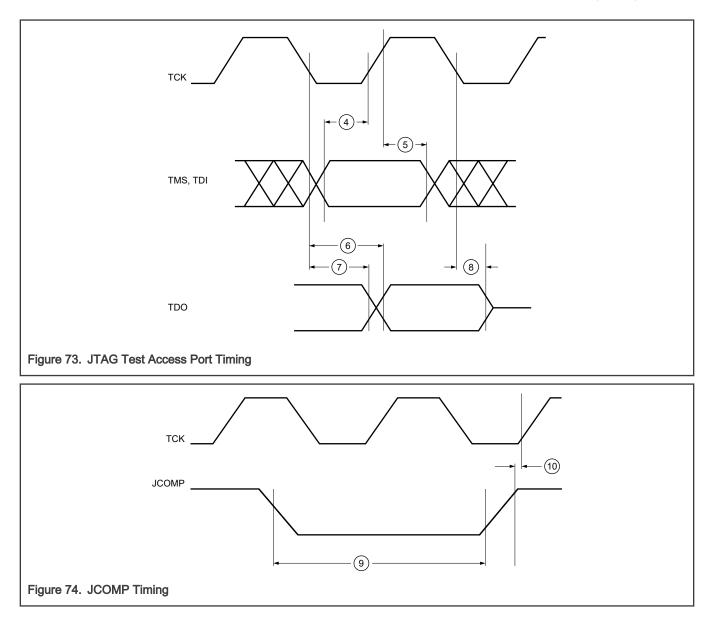

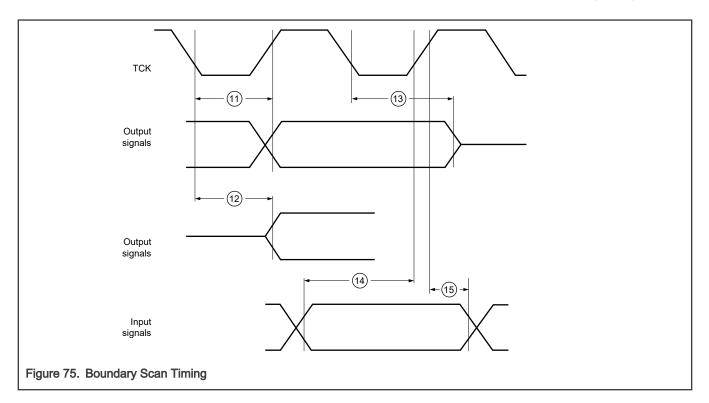

| 16.11.1 | JTAG Boundary Scan                |       |

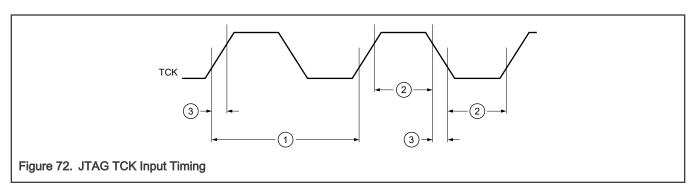

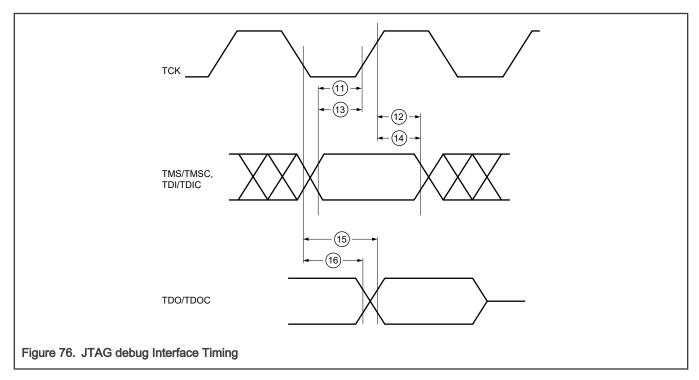

| 16.11.2 | JTAG Debug Interface Timing       |       |

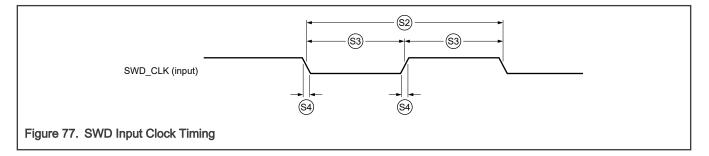

| 16.11.3 | SWD electrical specifications     |       |

| 17      | Pinouts                           |       |

| 18      | Packaging                         | 114   |

| 19 | Revision history120 |  |

|----|---------------------|--|

|----|---------------------|--|

## 1 Introduction

### 1.1 Overview

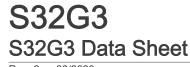

S32G3 is a family of high-performance vehicle network processors that combine controller area network (CAN), local interconnect network (LIN), and FlexRay networking with high data rate Ethernet networking. It also combines a functional safe-core infrastructure with MPU cores and includes high-level security features. The S32G3 chips are pin-for-pin compatible with S32G2 chips, providing over 2x performance and over 2x system RAM.

Table 1. S32G3 family key enhancements

| Feature                      | Enhancements                                                                                  |

|------------------------------|-----------------------------------------------------------------------------------------------|

| Compute performance          | Up to 2.6 x increase in applications performance (doubling Cortex-A53 cores @ 1.3x frequency) |

| Real-time memory             | Increase SRAM from 6 MB / 8 MB to 15 MB / 20 MB                                               |

| Real-time performance        | Additional pair of Cortex-M7 lockstep cores                                                   |

| Ethernet interface bandwidth | Increased speed from 1 Gbps to 2.5 Gbps on two SGMII interfaces                               |

| Ethernet packet routing      | Performance target increase from 2 Gbps@64B to 3 Gbps@64B                                     |

S32G3 family includes the following variants:

- S32G399A

- S32G398A

- S32G379A

- S32G378A

This document primarily represents the features offered by the superset S32G399A. To compare the features of the S32G3 family variants, see Feature comparison.

### 1.2 Applications

Combining ASIL D safety, hardware security, high-performance real-time and application processing and network acceleration, this chip targets applications that includes:

- · Service-oriented gateways and domain controllers

- · Safety processor for ADAS and autonomous driving

- · High-performance central compute nodes

- · FOTA masters controlling secure software image downloads and their distribution to the ECUs in the network

- Security services and key management

- Smart antennas

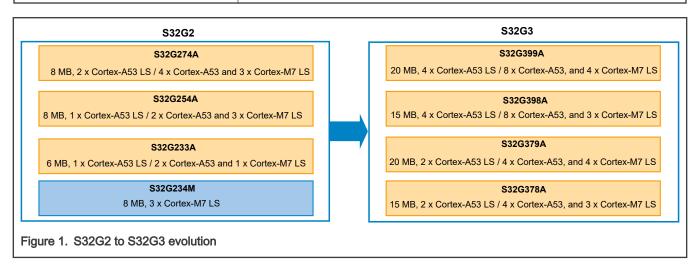

## 2 Block diagram

The following is the block diagram for S32G399A, the superset chip in the S32G3 family.

### 3 Feature comparison

This table compares the features of the chips in the S32G3 family.

| Table 2. | S32G3 | feature | list and | supported | functionality |

|----------|-------|---------|----------|-----------|---------------|

|----------|-------|---------|----------|-----------|---------------|

| Feature           | S32G399A          | S32G398A                      | S32G379A                      | S32G378A                      |

|-------------------|-------------------|-------------------------------|-------------------------------|-------------------------------|

|                   | (                 | Compute and bus module        | S                             |                               |

| Applications CPUs | 4 x Cortex-A53 LS | 4 x Cortex-A53 LS             | 2 x Cortex-A53 LS             | 2 x Cortex-A53 LS             |

|                   | (8 x Cortex-A53)  | (8 x Cortex-A53)              | (4 x Cortex-A53) <sup>1</sup> | (4 x Cortex-A53) <sup>1</sup> |

| Real-time CPUs    | 4 x Cortex-M7 LS  | 3 x Cortex-M7 LS <sup>2</sup> | 4 x Cortex-M7 LS              | 3 x Cortex-M7 LS <sup>2</sup> |

|                   |                   | Cortex-A53                    |                               |                               |

| L1 cache          | 32                | KB I-cache and 32 KB D        | -cache per Cortex-A53 co      | pre                           |

| L2 cache          |                   | 1 МВ ре                       | er cluster                    |                               |

| Feature                         | S32G399A                                                     | S32G398A                                                                  | S32G379A                  | S32G378A            |  |  |

|---------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------|---------------------|--|--|

| Cache coherency<br>interconnect | Supported                                                    |                                                                           |                           |                     |  |  |

| Interrupt controller            | GIC-500                                                      |                                                                           |                           |                     |  |  |

| Maximum frequency               |                                                              | Up to 1                                                                   | .3 GHz                    |                     |  |  |

| Functional safety               | Configurable                                                 | Configurable ASIL D lockstep clusters and two ASIL B independent clusters |                           |                     |  |  |

|                                 |                                                              | Cortex-M7                                                                 |                           |                     |  |  |

| L1 cache                        |                                                              | 32 KB I-cache and 32 KB                                                   | D-cache per Cortex-M7     |                     |  |  |

| Cache coherency<br>interconnect |                                                              | Not sup                                                                   | ported                    |                     |  |  |

| Interrupt controller            |                                                              | 4 x N                                                                     | IVIC                      |                     |  |  |

| Maximum frequency               |                                                              | 400 1                                                                     | MHz                       |                     |  |  |

| Functional safety               |                                                              | Dual-core                                                                 | lockstep                  |                     |  |  |

| DTCM                            |                                                              | 64 KB per                                                                 | Cortex-M7                 |                     |  |  |

| ·                               |                                                              | System modules                                                            |                           |                     |  |  |

| DMA                             | 2x safe eDMA (supporting lockstep) with 32 channels per eDMA |                                                                           |                           |                     |  |  |

| DMAMUX                          |                                                              | 128 inputs                                                                | per DMA                   |                     |  |  |

| Debug: Run control              |                                                              | Arm CoreSight JT                                                          | AG (IEEE 1149.1)          |                     |  |  |

| Debug: Trace                    |                                                              | 4-lane                                                                    | Aurora                    |                     |  |  |

| SWT instances                   |                                                              | 1:                                                                        | 2                         |                     |  |  |

| STM instances                   |                                                              | 1;                                                                        | 3                         |                     |  |  |

|                                 |                                                              | Memory modules                                                            |                           |                     |  |  |

| Internal RAM                    | 20 MB                                                        | 15 MB <sup>3</sup>                                                        | 20 MB                     | 15 MB <sup>3</sup>  |  |  |

| RAM ports                       | 16 (four groups of                                           | four ports each), and port                                                | s in each group are inter | rleaved at 64 bytes |  |  |

| DRAM                            |                                                              | DDR3L and LPDI                                                            | DR4 – up to 4 GB          |                     |  |  |

| DRAM PHY                        |                                                              | x3                                                                        | 2                         |                     |  |  |

| QuadSPI instances               |                                                              | 1                                                                         |                           |                     |  |  |

| uSDHC instances                 |                                                              | 1                                                                         |                           |                     |  |  |

| Fuses                           |                                                              | 8 KB                                                                      | bank                      |                     |  |  |

| Standby SRAM with               |                                                              | 32                                                                        | KB                        |                     |  |  |

| ECC                             |                                                              |                                                                           |                           |                     |  |  |

|                                 |                                                              | Security modules                                                          |                           |                     |  |  |

| Security subsystem              |                                                              | HSE                                                                       | E_H                       |                     |  |  |

Table 2. S32G3 feature list and supported functionality (continued)

| Table 2. | S32G3 feature | list and supported | I functionality | (continued) |

|----------|---------------|--------------------|-----------------|-------------|

|----------|---------------|--------------------|-----------------|-------------|

| Feature                                  | S32G399A  | S32G398A                  | S32G379A                   | S32G378A |  |  |  |

|------------------------------------------|-----------|---------------------------|----------------------------|----------|--|--|--|

| Resource isolation                       |           | XRDC support              | ing 16 domains             |          |  |  |  |

| Arm TrustZone                            |           | Supp                      | orted                      |          |  |  |  |

| Life cycle                               | Supported |                           |                            |          |  |  |  |

| Secure debug                             |           | Supp                      | orted                      |          |  |  |  |

|                                          | Со        | mmunication interface mod | lules                      |          |  |  |  |

| Communication acceleration               |           | LL                        | CE                         |          |  |  |  |

| CAN with flexible data rate              |           | 16 in LLCE and            | 4 outside LLCE             |          |  |  |  |

| FlexRay 2.1 (dual-<br>channel) instances |           | 1 in LLCE and             | 1 outside LLCE             |          |  |  |  |

| LINFlexD instances                       |           | 4 in LLCE and             | 3 outside LLCE             |          |  |  |  |

| Ethernet acceleration                    |           | Pi                        | Ē                          |          |  |  |  |

| Ethernet MAC                             |           | 3 in PFE and              | 1 outside PFE              |          |  |  |  |

| Ethernet interface                       |           | MII, RMII, R              | GMII, SGMII                |          |  |  |  |

| PCIe controller                          |           | 2x Gen3 controlle         | rs (X1, X2 modes)          |          |  |  |  |

| SerDes subsystem                         |           | Four lanes (configura     | able PCIe and SGMII)       |          |  |  |  |

| USBOTG instances                         |           | 1, supporting USB 2.0     | ) and a ULPI interface     |          |  |  |  |

| I <sup>2</sup> C instances               | 4         | + 1 for power management  | nt integrated circuits (PM | IC)      |  |  |  |

| SPI instances                            | 4 (in     | LLCE, can be enabled with | h firmware) and 6 outside  | LLCE     |  |  |  |

| CRC instances                            |           |                           | 1                          |          |  |  |  |

| · · ·                                    |           | Generic modules           |                            |          |  |  |  |

| PIT instances                            |           | 2                         | 2                          |          |  |  |  |

| SAR_ADC instances                        |           | 12-bit 2 x (              | 6 channels                 |          |  |  |  |

| FTM instances                            |           | 2 x 6 cł                  | nannels                    |          |  |  |  |

| CTU instances                            |           |                           | 1                          |          |  |  |  |

| SEMA42 instances                         |           |                           | 1                          |          |  |  |  |

| · · ·                                    | Cloc      | king, power, and reset mo | dules                      |          |  |  |  |

| FIRC frequency                           |           | 48 1                      | MHz                        |          |  |  |  |

| SIRC frequency                           |           | 32                        | KHz                        |          |  |  |  |

| FXOSC frequency                          |           | 20-40                     | ) MHz                      |          |  |  |  |

| PLLDIG instances                         |           | Ę                         | 5                          |          |  |  |  |

| Low-power mode                           |           | Supp                      | orted                      |          |  |  |  |

| Table 2. | S32G3 feature | list and supported | functionality | (continued) |

|----------|---------------|--------------------|---------------|-------------|

|----------|---------------|--------------------|---------------|-------------|

| Feature                                                                                                     | S32G399A                | S32G398A           | S32G379A | S32G378A |  |  |  |

|-------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|----------|----------|--|--|--|

| RTC                                                                                                         | RTC 1 with API function |                    |          |          |  |  |  |

| Wake-up                                                                                                     |                         | 24 wake-up sources |          |          |  |  |  |

|                                                                                                             |                         | Miscellaneous      |          |          |  |  |  |

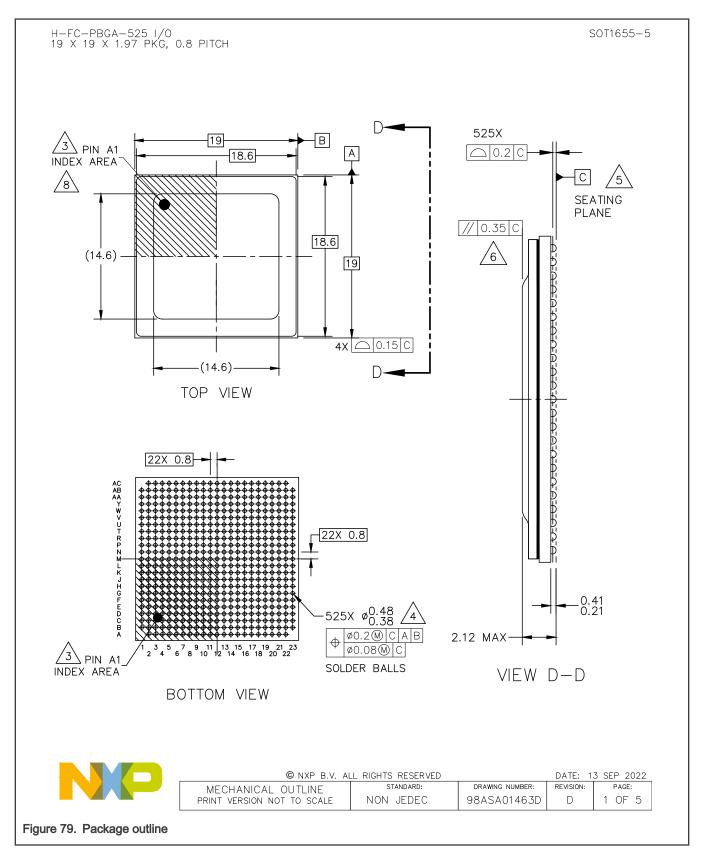

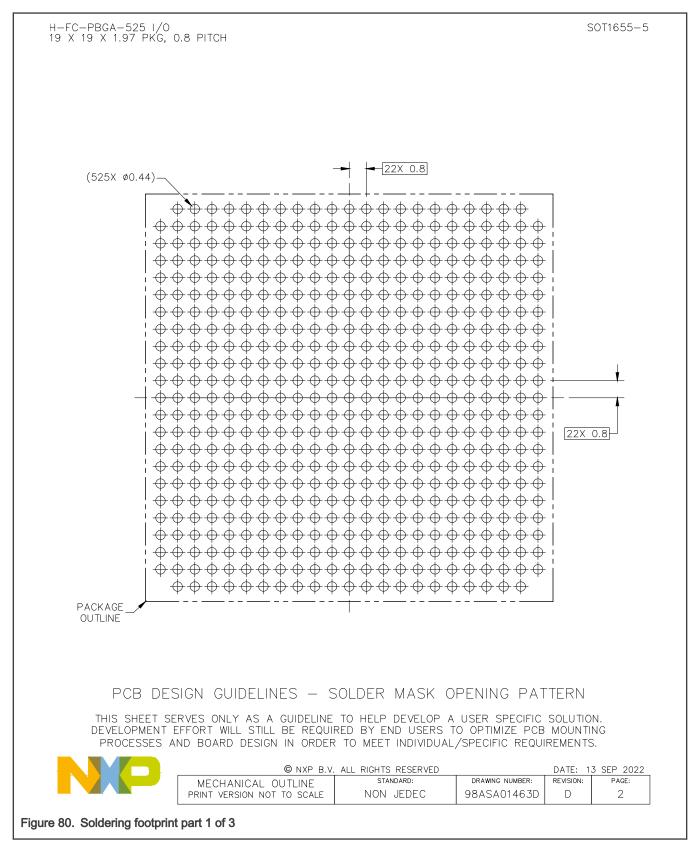

| Package specifications<br>and dimensions       525 flip-chip plastic ball-grid array; 19 mm x 19mm x 0.8 mm |                         |                    |          |          |  |  |  |

1. Cortex-A53\_2 and Cortex-A53\_3 have been defeatured in cluster 0 and cluster 1.

- 2. Cortex-M7\_2 has been defeatured. See the System RAM Controller chapter of the S32G3 Reference Manual for details.

- 3. SRAM (12, 13, 14, 15) i.e., the highest address range (0x34F0\_0000–0x353F\_FFFF) associated to Cortex-M7\_2 have been defeatured. See the System RAM Controller chapter of the S32G3 Reference Manual for details on internal RAM support across the family.

## 4 Ordering information

|     |       | Product brand and                                    | 1 <sup>st</sup> 2 <sup>nd</sup> , 3 <sup>rd</sup> Character                                       | s                                                                       | 9 <sup>th</sup> Cha                                                                |                                                |                                                 |            |

|-----|-------|------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------|------------|

| S32 | 1-3   | Status                                               | Product brand and status                                                                          |                                                                         | Chip conf<br>A = Stand                                                             | •                                              |                                                 |            |

| G   | 4     | Product line                                         | P32 = Prototype chip<br>S32 = Qualified device                                                    |                                                                         | S = Prem                                                                           | ium security c                                 | hip                                             |            |

|     | _     |                                                      |                                                                                                   |                                                                         | 10 <sup>th</sup> Ch                                                                |                                                |                                                 |            |

| 3   | 5     | Family                                               | 4 <sup>th</sup> Character                                                                         |                                                                         | $Arm \ core$<br>$\mathbf{A} = 400 \ \mathbf{N}$                                    | ,                                              | 17), 1000 MHz                                   | (Cortex-A5 |

| 9   | 6     | MPU performance<br>identifier                        | Product line<br><b>G</b> = Gateway                                                                |                                                                         | B = 400 N                                                                          | /Hz (Cortex-M                                  | 17), 1100 MHz<br>17), 1100 MHz<br>17), 1300 MHz | (Cortex-A5 |

| 9   | 7     | MCU performance<br>identifier and<br>system RAM size | 5 <sup>th</sup> Character<br>Family<br>3 = S32G3 family                                           |                                                                         | Fab and r                                                                          | <b>d 12<sup>th</sup> Char</b><br>mask revision | acters                                          |            |

| Α   | 8     | Product type                                         |                                                                                                   |                                                                         | K = TSM0<br>x = Mask                                                               |                                                | first mask revis                                | sion)      |

| S   | 9     | Chip configuration                                   | 6 <sup>th</sup> Character<br>MPU performance identifier<br>7 – 4x Cortex-A53<br>9 – 8x Cortex-A53 | <b>13<sup>th</sup> Character</b><br>Temperature (T <sub>A</sub> ) range |                                                                                    |                                                |                                                 |            |

| С   | 10    | Arm core speeds                                      |                                                                                                   |                                                                         | <b>C</b> = -40 °C to 85 °C<br><b>V</b> = -40 °C to 105 °C                          |                                                |                                                 |            |

| K0  | 11-12 | Fab and mask revision                                | <b>7<sup>th</sup> Character</b><br>MCU performance identifier<br>system RAM size                  | and                                                                     | <b>14<sup>th</sup> and</b><br>Package                                              | d 15 <sup>th</sup> Char                        | acters                                          |            |

| V   | 13    | Temperature (T <sub>A</sub> ) range                  | 8 = 3x Cortex-M7 and 15 M<br>9 = 4x Cortex-M7 and 20 M                                            |                                                                         | UC = 525                                                                           | FC-PBGA, 19                                    | 9x19mm, 0.8m                                    | nm pitch   |

| UC  | 14-15 | Package code                                         | 8 <sup>th</sup> Character<br>Product type<br>A = MCU + MPU                                        |                                                                         | <b>16<sup>th</sup> Ch</b><br><i>Shipping</i><br><b>T</b> = Tray<br><b>R</b> = Reel |                                                |                                                 |            |

| R   | 16    | Shipping method                                      |                                                                                                   |                                                                         |                                                                                    |                                                |                                                 |            |

|     |       |                                                      |                                                                                                   | S32G378A                                                                |                                                                                    | S32G398A                                       |                                                 |            |

|     |       |                                                      | ARM Cortex-M7 Cores                                                                               | 3                                                                       | 4                                                                                  | 3                                              | 4                                               |            |

|     |       |                                                      | ARM Cortex-A53 Cores                                                                              | 4<br>15 MB                                                              | 4<br>20 MB                                                                         | 8<br>15 MB                                     | 8<br>20 MB                                      |            |

|     |       |                                                      | System RAM Size                                                                                   | 13 MB                                                                   | 20 MB                                                                              |                                                | 20 MB                                           |            |

## 5 Electrostatic Discharge (ESD) Characteristics

The following table gives the ESD ratings and test conditions for the device.

#### Table 3. Electrostatic Discharge (ESD) Characteristics

| Symbol | Description                                             | Min | Тур | Max  | Unit | Condition | Spec<br>Number |

|--------|---------------------------------------------------------|-----|-----|------|------|-----------|----------------|

| -      | ESD Human Body<br>Model (HBM) <sup>1, 2, 3</sup>        | _   | _   | 2000 | V    | All pins  | —              |

| _      | ESD Charged<br>Device Model<br>(CDM) <sup>1, 3, 4</sup> | —   | —   | 250  | V    | All pins  | —              |

1. Device failure is defined as: "If after exposure to ESD pulses, the device does not meet the device specification requirements."

2. This parameter is tested in conformity with AEC-Q100-002

- 3. All ESD testing conforms with AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

- 4. This parameter is tested in conformity with AEC-Q100-011.

## 6 Absolute Max Ratings

This table defines the absolute maximum ratings for the device in terms of reliability characteristics. Absolute maximum rating specifications are stress ratings only, and functional operation is not guaranteed under these conditions. Functional operating conditions are given in the Operating Conditions section of this document.

| NOTE                                                                |

|---------------------------------------------------------------------|

| All specifications associated with VIN are measured at the SoC pin. |

| Symbol              | Description                                                | Min  | Тур | Max  | Unit | Condition | Spec<br>Number |

|---------------------|------------------------------------------------------------|------|-----|------|------|-----------|----------------|

| VDD                 | Core voltage<br>Supply <sup>1, 2</sup>                     | -0.3 |     | 0.96 | V    | -         | _              |

| VSS                 | Ground Supply <sup>1</sup>                                 | -0.3 | —   | 0.3  | V    | —         | -              |

| VDD_STBY            | Standby domain supply voltage <sup>1, 2</sup>              | -0.3 | _   | 0.96 | V    | -         | _              |

| VDD_LV_PLL_AUR      | Aurora PLL digital voltage supply <sup>1, 2</sup>          | -0.3 | _   | 0.96 | V    | -         | —              |

| VDD_LV_PLL_<br>DDR0 | DDR0 PLL digital voltage supply <sup>1, 2</sup>            | -0.3 | —   | 0.96 | V    | -         | —              |

| VDD_VP_PCIEn        | PCIE0/1 core<br>voltage supply (n=0,<br>1) <sup>1, 2</sup> | -0.3 | -   | 0.96 | V    | -         | -              |

| VDD_FIRC            | FIRC high voltage supply <sup>1, 3</sup>                   | -0.3 | -   | 2.16 | V    | -         | -              |

| VDD_EFUSE           | EFUSE high voltage supply <sup>1, 3</sup>                  | -0.3 | -   | 2.16 | V    | -         | -              |

#### Table 4. Absolute Max Ratings

Table 4. Absolute Max Ratings (continued)

| Symbol              | Description                                          | Min  | Тур | Max  | Unit | Condition                | Spec<br>Number |

|---------------------|------------------------------------------------------|------|-----|------|------|--------------------------|----------------|

| VDD_IO_x            | GPIO 3.3V<br>supply <sup>1, 4</sup>                  | -0.3 | -   | 4    | V    | -                        | -              |

| VDD_IO_A            | GPIO A 3.3V supply <sup>1, 4</sup>                   | -0.3 | —   | 4    | V    | _                        | -              |

| VDD_IO_B            | GPIO B 3.3V supply <sup>1, 4</sup>                   | -0.3 | —   | 4    | V    | _                        | -              |

| VDD_IO_GMAC0        | GMAC0 I/O voltage supply <sup>1, 4</sup>             | -0.3 | —   | 4    | V    | -                        | -              |

| VDD_IO_GMAC1        | GMAC1 I/O voltage supply <sup>1, 4</sup>             | -0.3 | —   | 4    | V    | -                        | -              |

| VDD_IO_QSPI         | QSPI A I/O voltage supply <sup>1, 3</sup>            | -0.3 | _   | 2.16 | V    | -                        | -              |

| VDD_IO_SDHC         | uSDHC / QSPI B I/O<br>voltage supply <sup>1, 4</sup> | -0.3 | —   | 4    | V    | -                        | -              |

| VDD_IO_CLKOUT       | CLKOUT 1.8V I/O supply <sup>1, 3</sup>               | -0.3 | —   | 2.16 | V    | -                        | -              |

| VDD_IO_AUR          | Aurora 1.8V I/O supply <sup>1, 3</sup>               | -0.3 | —   | 2.16 | V    | -                        | -              |

| VDD_IO_DDR0         | DDR0 I/O voltage supply <sup>1</sup>                 | -0.3 | —   | 2.16 | V    | -                        | -              |

| VDD_IO_USB          | USB I/O voltage supply <sup>1, 4</sup>               | -0.3 | —   | 4    | V    | -                        | -              |

| VDD_IO_STBY         | Standby domain I/O voltage supply <sup>1, 4</sup>    | -0.3 | —   | 4    | V    | -                        | -              |

| VDD_VREF            | Supply detector high voltage supply <sup>1, 3</sup>  | -0.3 | —   | 2.16 | V    | -                        | -              |

| VDD_ADC             | ADC voltage supply <sup>1, 3</sup>                   | -0.3 | —   | 2.16 | V    | Reference to VSS_<br>ADC | -              |

| VSS_ADC             | ADC ground supply <sup>1</sup>                       | -0.3 | _   | 0.3  | V    | Reference to VSS         | -              |

| VDD_HV_PLL          | PLL high voltage supply <sup>1, 3</sup>              | -0.3 | _   | 2.16 | V    | -                        | -              |

| VDD_HV_PLL_<br>AUR  | Aurora PLL high voltage supply <sup>1, 3</sup>       | -0.3 | -   | 2.16 | V    | -                        | -              |

| VDD_HV_PLL_<br>DDR0 | DDR PLL voltage supply <sup>1, 3</sup>               | -0.3 | _   | 2.16 | V    | -                        | -              |

| VDD_DDR0            | DDR0 high voltage supply <sup>1, 3</sup>             | -0.3 | -   | 2.16 | V    | DDR PHY PLL              | -              |

#### Table 4. Absolute Max Ratings (continued)

| Symbol       | Description                                                                 | Min              | Тур | Max                | Unit | Condition                  | Spec<br>Number |

|--------------|-----------------------------------------------------------------------------|------------------|-----|--------------------|------|----------------------------|----------------|

| VDD_FXOSC    | FXOSC high voltage supply <sup>1, 3</sup>                                   | -0.3             | -   | 2.16               | V    | Reference to VSS_<br>FXOSC | -              |

| VSS_FXOSC    | FXOSC ground supply <sup>1</sup>                                            | -0.3             | _   | 0.3                | V    | Reference to VSS           | -              |

| VEXTAL       | FXOSC EXTAL input voltage range <sup>1, 3, 5</sup>                          | -0.3             | _   | 2.16               | V    | _                          | -              |

| VXTAL        | FXOSC XTAL input voltage range <sup>1, 3, 5</sup>                           | -0.3             | _   | 2.16               | V    | —                          | -              |

| VDD_IO_PCIEn | PCIE0/1 high<br>voltage supply (n=0,<br>1) <sup>1, 3</sup>                  | -0.3             | _   | 2.16               | V    | -                          | _              |

| VDD_TMU      | Thermal Monitoring<br>Unit (TMU) high<br>voltage supply <sup>1, 3</sup>     | -0.3             | _   | 2.16               | V    | -                          | -              |

| VREFH_ADC    | ADC reference high voltage <sup>1, 3</sup>                                  | -0.3             | _   | 2.16               | V    | Reference to VREFL_<br>ADC | -              |

| VREFL_ADC    | ADC reference low voltage <sup>1</sup>                                      | -0.3             | _   | 0.3                | V    | Reference to VSS           | -              |

| VAD_INPUT    | ADC input voltage<br>range <sup>1, 6, 7</sup>                               | VSS_AD<br>C -0.6 | _   | VDD_AD<br>C +0.5   | V    | -                          | -              |

| VIN          | GPIO input voltage<br>range <sup>1, 8, 9, 10</sup>                          | VSS - 0.3        | _   | VDD_IO_<br>* + 0.3 | V    | -                          | -              |

| IINJ_D       | Maximum DC<br>current injection<br>digital I/O pin <sup>1, 11</sup>         | -3               | _   | 3                  | mA   | _                          | _              |

| IINJ_A       | Maximum DC<br>current injection<br>analog input<br>pin <sup>1, 6, 12</sup>  | -1               | _   | 1                  | mA   | _                          | _              |

| IINJ_LVDS    | Max LVDS RX or<br>TX pin injection<br>current <sup>1, 13</sup>              | 0                | _   | 100                | uA   | -                          | _              |

| IINJ_LVDS    | Max LVDS RX or<br>TX pin injection<br>current <sup>1</sup>                  | 0                | _   | 100                | uA   | -                          | -              |

| IMAXSEG      | Maximum RMS<br>current per GPIO<br>supply domain<br>(VDD_IO_*) <sup>1</sup> | _                | _   | 140                | mA   | _                          | _              |

| TSTG         | Storage temperature range <sup>1</sup>                                      | -55              | -   | 150                | С    | -                          | -              |

| Symbol      | Description                                    | Min  | Тур | Max  | Unit | Condition                                                                                     | Spec<br>Number |

|-------------|------------------------------------------------|------|-----|------|------|-----------------------------------------------------------------------------------------------|----------------|

| TSDR        | Maximum solder<br>temperature <sup>1, 14</sup> | _    | _   | 260  | С    | Pb free                                                                                       | _              |

| MSL         | Moisture Sensitivity<br>Level <sup>1, 15</sup> | _    | _   | 3    | _    | —                                                                                             | _              |

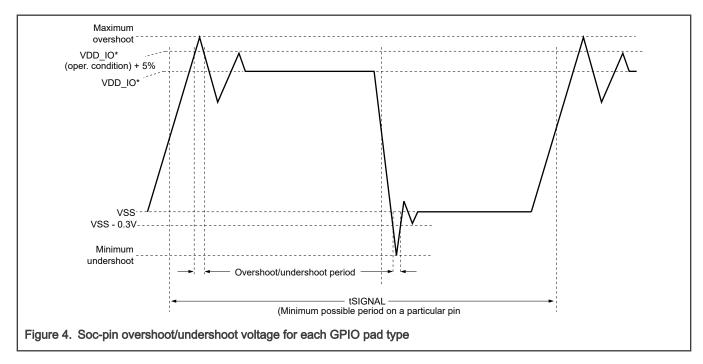

| V_OS_US_10  | Voltage at 10 % of tSIGNAL <sup>16</sup>       | -0.4 | —   | 3.7  | V    | 3.3V, See "SoC-pin<br>overshoot/undershoot<br>voltage for each GPIO<br>pad type" figure below | —              |

| V_OS_US_7p5 | Voltage at 7.50 % of tSIGNAL <sup>16</sup>     | -0.5 | —   | 3.8  | V    | 3.3V, See "SoC-pin<br>overshoot/undershoot<br>voltage for each GPIO<br>pad type" figure below | —              |

| V_OS_US_2p5 | Voltage at 2.50 % of tSIGNAL <sup>16</sup>     | -0.6 | —   | 3.9  | V    | 3.3V, See "SoC-pin<br>overshoot/undershoot<br>voltage for each GPIO<br>pad type" figure below | —              |

| V_OS_US_1p6 | Voltage at 1.60 % of tSIGNAL <sup>16</sup>     | -0.7 | —   | 4    | V    | 3.3V, See "SoC-pin<br>overshoot/undershoot<br>voltage for each GPIO<br>pad type" figure below | —              |

| V_OS_US_10  | Voltage at 10 % of tSIGNAL <sup>17</sup>       | -0.7 | —   | 2.31 | V    | 1.8V, See "SoC-pin<br>overshoot/undershoot<br>voltage for each GPIO<br>pad type" figure below | —              |

Table 4. Absolute Max Ratings (continued)

1. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the listed maxima may affect device reliability or cause permanent damage to the device. See the operating conditions table for functional specifications.

- 2. Allowed 0.88V 0.96V for 60 seconds cumulative over lifetime with no operating restrictions, 2.0 hours cumulative over lifetime with device in reset, at maximum Tj = 125 °C

- 3. Allowed 1.92V 2.16V for 60 seconds cumulative over lifetime with no operating restrictions, 2.6 hours cumulative over lifetime with device in reset, at maximum Tj = 125 °C

- Allowed 3.52V 4.0V for 60 seconds cumulative over lifetime with no operating restrictions, 2.6 hours cumulative over lifetime with device in reset, at maximum Tj = 125 °C

- 5. VEXTAL/ VXTAL (min) is for powered condition. VEXTAL/VXTAL (min) can be lower in unpowered condition.

- Allowed for a cumulative duration of 50 hours operation over the lifetime of the device at maximum Tj, with VDD\_ADC <= 1.92V, VSS\_ADC = 0V. Allowed for unlimited duration if the device is unpowered.

- The maximum input voltage on an I/O pin tracks with the associated I/O supply maximum. For the injection current condition on a pin, the voltage equals the supply plus the voltage drop across the internal ESD diode from I/O pin to supply.

- Absolute maximum DC VIN levels for a powered device are 3.82V and 2.22V, for 3.3V and 1.8V domains, respectively. For powered devices when VIN ≥ VDD\_IO\*, VIN must simultaneously follow the constraint that VIN-VDD\_IO\* ≤ 0.3V for the DC case. For unpowered devices, the allowed VIN max level is +0.9V. Unpowered devices must simultaneously follow IINJ\_D unpowered current injection constraints.

- 9. Absolute minimum DC VIN level for a powered device is -0.3V. For unpowered devices, the allowed VIN min level is -0.9V. Unpowered devices must simultaneously follow IINJ\_D unpowered current injection constraints.

- 10. DC case limit. Overshoot/Undershoot beyond this range is allowed, but only for the limited durations as constrained by temporal percentages of tSIGNAL.

- 11. IINJ\_D specifications are per pin for an unpowered condition of the associated supply. The maximum simultaneous injection per supply is 30mA.

- 12. Non-disturb of ADC channels during current injection cannot be guaranteed. The degradation in channel performance cannot be specified due to the dynamic operation of the ADC input mux and potential for varying charge distribution. For the max +/-1mA DC injection quoted here, VAD\_INPUT would be +0.5/-0.6V relative to VREFH\_ADC/VREFL\_ADC at max Tj. ADC Output of the channel into which injection occurs will saturate depending on the direction of injection and for the channels not subject to current injection Offset error would be -12 LSB to 6 LSB and TUE would be -12 LSB to 8 LSB.

- 13. Applies exclusively to ZipWire and does not apply to Aurora. Allowed for a cumulative of 14 hours over the life of the part. The voltage on the RX or TX pin must not exceed 2.16 V at any time during the power-cycling or normal operation.

- 14. Solder profile per IPC/JEDEC J-STD-020D.

- 15. Moisture sensitivity per JEDEC test method A112.

- 16. For AC Signals in a 3.3V supply domain, if VDD\_IO ≤ 3.3V, max VIN overshoot is limited to VDD\_IO+20%. If VDD\_IO > 3.3V, then max VIN overshoot is limited to 4V.

- 17. For AC Signals in a 1.8V supply domain, max VIN overshoot is limited to VDD\_IO+20% for 10% of tSIGNAL.

## 7 Operating conditions

### 7.1 Operating Conditions

The following table describes the functional operating conditions for the device, and for which all specifications in this datasheet are valid, except where explicitly noted. Device behavior is not guaranteed for operation outside of the conditions in this table.

**NOTE**  $\Delta VDD^*$  specifications are applicable to the supplies mentioned in the condition column when the device is not in standby mode. VDD\_IO\_B, VDD\_IO\_QSPI and VDD\_DDR0 may stay powered in standby mode as applicable to the group.

> **NOTE** All specifications associated with VIN are measured at the SoC pin.

#### Table 5. Operating Conditions

| Symbol              | Description                                               | Min  | Тур | Max  | Unit | Condition | Spec<br>Number |

|---------------------|-----------------------------------------------------------|------|-----|------|------|-----------|----------------|

| fSYS_A53            | Cortex-A53<br>core operating<br>frequency <sup>1, 2</sup> | -    | _   | 1311 | MHz  | -         | -              |

| fSYS_CM7            | Cortex-M7<br>core operating<br>frequency <sup>1, 2</sup>  | -    | -   | 400  | MHz  | -         | _              |

| fSYS_PFE_PE         | PFE PE operating frequency <sup>1, 2</sup>                | —    | _   | 600  | MHz  | —         | —              |

| Tj                  | Junction<br>Temperature<br>Range <sup>1, 3, 4</sup>       | -40  | -   | 125  | С    | _         | _              |

| Та                  | Ambient<br>Temperature<br>Range <sup>1, 4</sup>           | -40  | -   | 105  | С    | _         | _              |

| VDD                 | Core voltage<br>Supply <sup>1</sup>                       | 0.75 | 0.8 | 0.87 | V    | -         | -              |

| VSS                 | Ground Supply <sup>1</sup>                                | _    | 0   | -    | V    | —         | _              |

| VDD_STBY            | Standby domain supply voltage <sup>1, 5</sup>             | 0.75 | 0.8 | 0.87 | V    | -         | —              |

| VDD_LV_PLL_AUR      | Aurora PLL digital voltage supply <sup>1</sup>            | 0.75 | 0.8 | 0.87 | V    | _         | -              |

| VDD_LV_PLL_<br>DDR0 | DDR0 PLL digital voltage supply <sup>1</sup>              | 0.75 | 0.8 | 0.87 | V    | -         | -              |

| VDD_VP_PCIE0        | PCIE0/1 core<br>voltage supply <sup>1, 6</sup>            | 0.75 | 0.8 | 0.87 | V    | -         | —              |

| VDD_IO_A            | GPIO A 3.3V<br>supply <sup>1</sup>                        | 3.08 | 3.3 | 3.52 | V    | -         | —              |

| VDD_IO_B            | GPIO B 3.3V<br>supply <sup>1, 7</sup>                     | 3.08 | 3.3 | 3.52 | V    | -         | —              |

| VDD_IO_GMAC0        | GMAC0 I/O voltage supply <sup>1</sup>                     | 1.68 | 1.8 | 1.92 | V    | 1.8V      | —              |

| VDD_IO_GMAC0        | GMAC0 I/O voltage supply <sup>1</sup>                     | 3.08 | 3.3 | 3.52 | V    | 3.3V      | -              |

| VDD_IO_GMAC1        | GMAC1 I/O voltage supply <sup>1</sup>                     | 1.68 | 1.8 | 1.92 | V    | 1.8V      | -              |

| VDD_IO_GMAC1        | GMAC1 I/O voltage supply <sup>1</sup>                     | 3.08 | 3.3 | 3.52 | V    | 3.3V      | -              |

| VDD_IO_QSPI         | QuadSPI A I/O<br>voltage supply <sup>1, 8</sup>           | 1.68 | 1.8 | 1.92 | V    | 1.8V      | -              |

Table 5. Operating Conditions (continued)

| Symbol              | Description                                       | Min   | Тур  | Max  | Unit | Condition                     | Spec<br>Number |

|---------------------|---------------------------------------------------|-------|------|------|------|-------------------------------|----------------|

| VDD_IO_SDHC         | uSDHC / QSPI B I/O<br>voltage supply <sup>1</sup> | 1.68  | 1.8  | 1.92 | V    | 1.8V                          | -              |

| VDD_IO_SDHC         | uSDHC I/O voltage supply <sup>1</sup>             | 3.08  | 3.3  | 3.52 | V    | 3.3V                          | -              |

| VDD_IO_CLKOUT       | CLKOUT 1.8V I/O supply <sup>1</sup>               | 1.68  | 1.8  | 1.92 | V    | _                             | -              |

| VDD_IO_AUR          | Aurora 1.8V I/O supply <sup>1</sup>               | 1.68  | 1.8  | 1.92 | V    | Aurora LVDS Tx + ref<br>clock | _              |

| VDD_IO_STBY         | Standby domain I/O voltage supply <sup>1, 7</sup> | 3.08  | 3.3  | 3.52 | V    | -                             | _              |

| VDD_IO_USB          | USB I/O voltage supply <sup>1</sup>               | 1.68  | 1.8  | 1.92 | V    | 1.8V                          | _              |

| VDD_IO_USB          | USB I/O voltage supply <sup>1</sup>               | 3.08  | 3.3  | 3.52 | V    | 3.3V                          | -              |

| VDD_IO_DDR0         | DDR3L I/O voltage supply <sup>1</sup>             | 1.283 | 1.35 | 1.45 | V    | -                             | -              |

| VDD_IO_DDR0         | LPDDR4 I/O voltage supply <sup>1</sup>            | 1.06  | 1.1  | 1.17 | V    | -                             | -              |

| δVDD_IO_DDR0        | DDR3L I/O supply<br>ripple voltage <sup>1</sup>   | -5    | _    | 5    | %    | _                             | -              |

| δVDD_IO_DDR0        | LPDDR4 I/O supply ripple voltage <sup>1</sup>     | -2.5  | —    | 2.5  | %    | -                             | -              |

| VDD_DDR0            | DDR0 high voltage supply <sup>1</sup>             | 1.68  | 1.8  | 1.92 | V    | -                             | -              |

| VDD_FIRC            | FIRC high voltage supply <sup>1</sup>             | 1.68  | 1.8  | 1.92 | V    | -                             | -              |

| VDD_VREF            | PMC high voltage supply <sup>1</sup>              | 1.68  | 1.8  | 1.92 | V    | -                             | _              |

| VDD_EFUSE           | EFUSE high voltage supply <sup>1, 9, 10, 11</sup> | 1.68  | 1.8  | 1.92 | V    | -                             | -              |

| VDD_ADC             | ADC high voltage supply <sup>1</sup>              | 1.68  | 1.8  | 1.92 | V    | _                             | -              |

| VDD_HV_PLL          | PLL high voltage supply <sup>1</sup>              | 1.68  | 1.8  | 1.92 | V    | _                             | -              |

| VDD_HV_PLL_<br>AUR  | Aurora PLL high voltage supply <sup>1</sup>       | 1.68  | 1.8  | 1.92 | V    | -                             | -              |

| VDD_HV_PLL_<br>DDR0 | DDR PLL voltage supply <sup>1</sup>               | 1.68  | 1.8  | 1.92 | V    | -                             | -              |

Table 5. Operating Conditions (continued)

| Symbol               | Description                                                                         | Min       | Тур | Max                | Unit | Condition                                                                                                                                                                                          | Spec<br>Number |

|----------------------|-------------------------------------------------------------------------------------|-----------|-----|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ðVDD_HV_PLL_<br>DDR0 | DDR PLL supply<br>ripple voltage <sup>1</sup>                                       | -2.5      | _   | 2.5                | %    | -                                                                                                                                                                                                  | -              |

| VDD_FXOSC            | FXOSC high voltage supply <sup>1</sup>                                              | 1.68      | 1.8 | 1.92               | V    | _                                                                                                                                                                                                  | -              |

| VDD_IO_PCIEn         | PCIE0/1 high<br>voltage supply <sup>1, 6</sup>                                      | 1.68      | 1.8 | 1.92               | V    | -                                                                                                                                                                                                  | _              |

| VDD_TMU              | Thermal Monitoring<br>Unit (TMU) high<br>voltage supply <sup>1</sup>                | 1.68      | 1.8 | 1.92               | V    | _                                                                                                                                                                                                  | _              |

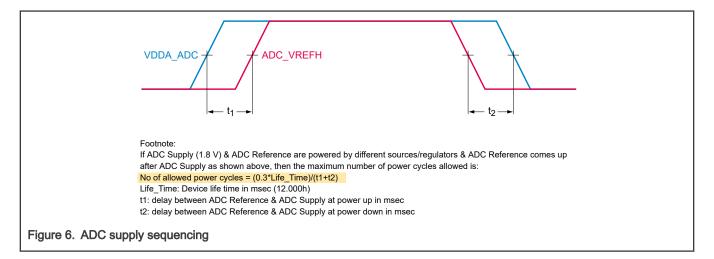

| VREFH_ADCn           | ADC reference high voltage (n=0, 1) <sup>1</sup>                                    | 1.68      | 1.8 | 1.92               | V    | -                                                                                                                                                                                                  | _              |

| VIN_33               | 3.3V GPIO<br>input voltage<br>range <sup>1, 12, 13, 14</sup>                        | VSS - 0.3 | _   | VDD_IO_<br>* + 0.3 | V    | -                                                                                                                                                                                                  | -              |

| VIN_18               | 1.8V GPIO<br>input voltage<br>range <sup>1, 12, 13, 14</sup>                        | VSS - 0.3 | _   | VDD_IO_<br>* + 0.3 | V    | -                                                                                                                                                                                                  | -              |

| ΔVDD                 | 0.8V supply voltage differential <sup>1, 15</sup>                                   | -25       | _   | 25                 | mV   | Applies to all 0.8V supplies on the device.                                                                                                                                                        | _              |

| ΔVDD_HV_18_IO        | 1.8V I/O supply<br>voltage differential<br>group <sup>1, 15</sup>                   | -25       |     | 25                 | mV   | Applies to VDD_IO_<br>QSPI, VDD_IO_SDHC,<br>VDD_IO_GMAC0,<br>VDD_IO_GMAC1,<br>VDD_IO_USB                                                                                                           | _              |

| ΔVDD_HV_18_<br>ANA   | 1.8V analog supply<br>voltage differential<br>group <sup>1, 9, 10, 11, 15, 16</sup> | -25       |     | 25                 | mV   | Applies to<br>VDD_IO_CLKOUT,<br>VDD_IO_AUR, VDD_<br>TMU, VREFH_ADC*,<br>VDD_ADC, VDD_HV_<br>PLL*, VDD_VREF,<br>VDD_FXOSC, VDD_<br>FIRC, VDD_EFUSE,<br>VDD_DDR0, VDD_<br>IO_PCIE0, VDD_IO_<br>PCIE1 |                |

| ΔVDD_HV_33_IO        | 3.3V I/O supply<br>voltage differential<br>group <sup>1, 15</sup>                   | -25       | _   | 25                 | mV   | VDD_IO_A, VDD_IO_B                                                                                                                                                                                 | -              |

| ΔVSS_HV_18           | 1.8V supply<br>ground voltage<br>differential <sup>1, 15</sup>                      | -25       | _   | 25                 | mV   | Applies to VSS,<br>VREFL_ADCn, VSS_<br>ADC, VSS_FXOSC                                                                                                                                              | -              |

| Table 5. | Operating | Conditions | (continued)   |

|----------|-----------|------------|---------------|

| 10010 01 | oporating | oonanaono  | (containa da) |

| Symbol               | Description                                                        | Min                | Тур | Max                | Unit   | Condition                                                             | Spec<br>Number |

|----------------------|--------------------------------------------------------------------|--------------------|-----|--------------------|--------|-----------------------------------------------------------------------|----------------|

| VRAMP_LV             | LV supply voltage ramp-up rate <sup>1, 17</sup>                    | 0.001              | _   | 24                 | V / ms | Applies to 0.8V<br>supplies                                           | -              |

| VRAMP_HV             | HV supply voltage ramp-up rate <sup>1</sup>                        | 0.001              | _   | 24                 | V / ms | Applies to 1.8V<br>supplies and DDR I/O<br>supplies.                  | —              |

| VRAMP_HV_33_IO       | 3.3V I/O supply<br>voltage ramp-up<br>rate <sup>1</sup>            | 0.001              | _   | 50                 | V / ms | Applies to 3.3V I/O supplies.                                         | —              |

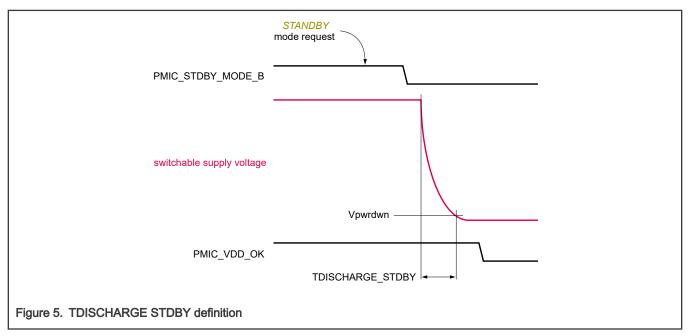

| TDISCHARGE_<br>STDBY | Supply discharge<br>time during Standby<br>mode entry <sup>1</sup> | 100                |     | —                  | us     | Applies to all<br>switchable supplies<br>during Standby mode<br>entry | —              |

| VAD_INPUT            | ADC input voltage range <sup>1, 18</sup>                           | VSS_AD<br>C - 0.35 | —   | VDD_AD<br>C + 0.25 | V      | —                                                                     | _              |

| IINJ_D               | GPIO Input DC<br>Injection Current <sup>1, 19</sup>                | -3                 | _   | 3                  | mA     | Unpowered                                                             | -              |

| IINJ_D               | GPIO Input DC<br>Injection Current <sup>1, 20</sup>                | 0                  | _   | 5                  | uA     | Powered                                                               | -              |

| IINJ_A               | SAR ADC Input DC<br>Injection Current <sup>1, 21</sup>             | -20                | _   | 20                 | uA     | _                                                                     | -              |

| IMAXSEG              | Maximum RMS<br>current per GPIO<br>supply domain <sup>1</sup>      | _                  | _   | 120                | mA     | _                                                                     | -              |

1. The operating conditions in this table apply as required conditions for all other specifications in this document, unless explicitly noted as an exception in another section of this document.

- The stated maximum operating frequency must be observed when using the PLL with frequency modulation enabled. Center-spread modulation is supported in cases where the nominal operating frequency plus half the modulation depth is less than the stated maximum frequency.

- 3. Lifetime operation at Tj max not guaranteed. Standard automotive temperature profile assumed for performance and reliability guarantees.

- 4. The junction temperature (Tj) range specification cannot be violated. The ambient temperature shown in the table, is a rough indicative value, for a typical system. Customers must ensure there is an appropriate thermal solution in their system to keep Tj within the spec range

- 5. The operating voltage range applies when the device is not in standby mode.

- 6. Both PCIe supplies must ramp for the SerDes PHY to safely power up into its reset state. Until both supplies are ramped, the SerDes PHY will be in an undefined state.

- 7. A minimum of 2.91V is supported on this supply when the device is in low-power standby mode if it is kept powered during this mode.

- 8. The device supports QSPI interface to 3.3V memories on the QSPI B bank, which is multiplexed with uSDHC functions on the VDD\_IO\_SDHC supply. QSPI A signals on VDD\_IO\_QSPI are limited to 1.8V.

- 9. The VDD\_EFUSE supply must be maintained within specification during fuse programming. Failure to do this may result in improper functionality of the device after fuse programming.

- 10. Refer to the Power Sequencing section for the relationship of VDD\_EFUSE powering up/down relative to the core, high-voltage, and I/O supplies.

- 11. VDD\_EFUSE must be grounded when not actively programming the fuses. This supply is not required to be powered for fuse reads. See device hardware design guidelines document for more details.

- 12. For AC signals, allowed max VIN ≤ VDD\_IO\* for lifetime operation. If AC overshoot beyond VDD\_IO\* occurs, then refer to the Abs Max duration constraints as a function of the amount of overshoot. For DC signals ≥ VDD\_IO, VIN-VDD\_IO\* ≤ 0.3V is allowed for lifetime operation.

- 13. The min DC VIN level for a powered device is -0.3V. If AC undershoot below -0.3V occurs, then refer to the Abs Max duration constraints as a function of the amount of undershoot.

- 14. DC case limit. Overshoot/Undershoot beyond this range is allowed, but only for the limited durations as constrained by temporal percentages of tSIGNAL.

- 15. The "voltage differential" refers to the difference between the lowest and highest voltages across all supplies within the supply group as defined under Condition column.

- 16. VREFH\_ADCn allows a differential voltage of +/-100mV.

- 17. On slow ramps, the RESET\_B pin may be observed to be asserted multiple times during the supply ramping. In order to prevent these pulses from being propagated into the system, it is recommended that the PMIC drives RESET\_B low during supply ramp or whenever POR\_B is asserted.

- 18. The maximum input voltage on an I/O pin tracks with the associated I/O supply maximum. For the injection current condition on a pin, the voltage equals the supply plus the voltage drop across the internal ESD diode from I/O pin to supply.

- 19. IINJ\_D specifications are per pin for an unpowered condition of the associated supply. The maximum simultaneous injection per supply is 30mA.

- 20. You must ensure that neither IINJ nor VIN specs are violated. Negligible DC injection currents are expected to flow during normal powered operation.

- 21. The SAR ADC electrical specifications are not guaranteed during any period when the operating injection current limit is violated. These specifications are at maximum Tj and VREFH\_ADC=1.8V; the injected current will reduce with reduced Tj.

The device hardware design guidelines document summarizes mandatory board design rules in table "Decaps and Ferrite Bead requirement" and section "PDN (Power Delivery Network) Guidelines".

### 7.2 Clock frequency ranges

The following table gives the frequency range minimum and maximums to use when programming the clock dividers on the device.

| Symbol                  | Description                                 | Min | Тур | Max   | Unit | Condition              | Spec<br>Number |

|-------------------------|---------------------------------------------|-----|-----|-------|------|------------------------|----------------|

| fA53_CORE_DIV2_<br>CLK  | Cortex-A53 core<br>div2 clock frequency     | 24  | _   | 655.5 | MHz  | A53_CORE_DIV2_CLK      | _              |

| fA53_CORE_<br>DIV10_CLK | Cortex-A53 core<br>div10 clock<br>frequency | 4.8 | _   | 131.1 | MHz  | A53_CORE_DIV10_<br>CLK | —              |

| fLBIST_CLK              | LBIST[7:0] clock<br>frequency               | _   | _   | 50    | MHz  | LBIST_CLK[7:0]         | _              |

| fXBAR_CLK               | XBAR clock<br>frequency                     | 24  | _   | 400   | MHz  | XBAR_CLK               | _              |

| fXBAR_2X_CLK            | XBAR 2X clock<br>frequency                  | 48  | _   | 800   | MHz  | XBAR_2X_CLK            | _              |

| fXBAR_DIV2_CLK          | XBAR div2 clock<br>frequency                | 12  | _   | 200   | MHz  | XBAR_DIV2_CLK          | —              |

| fXBAR_DIV3_CLK          | XBAR div3 clock<br>frequency                | 8   | _   | 133   | MHz  | XBAR_DIV3_CLK          | —              |

| fXBAR_DIV4_CLK          | XBAR div4 clock<br>frequency                | 6   | _   | 100   | MHz  | XBAR_DIV4_CLK          | _              |

| fXBAR_DIV6_CLK          | XBAR div6 clock<br>frequency                | 4   | _   | 66.7  | MHz  | XBAR_DIV6_CLK          | —              |

| fDAPB_CLK               | Debug clock<br>frequency                    | _   | -   | 133   | MHz  | fDAPB_CLK              | —              |

| fFRAY_CHI               | FlexRay CHI clock<br>frequency              | _   | -   | 133   | MHz  | _                      | _              |

Table 6. Clock frequency ranges

Table 6. Clock frequency ranges (continued)

| Symbol                 | Description                               | Min | Тур | Max   | Unit | Condition             | Spec<br>Number |

|------------------------|-------------------------------------------|-----|-----|-------|------|-----------------------|----------------|

| fSERDES_REF_<br>CLK    | SERDES reference<br>clock frequency       | 100 | -   | 125   | MHz  | SERDES_REF_CLK        | _              |

| fPER_CLK               | Peripheral clock<br>frequency             | _   | —   | 80    | MHz  | PER_CLK               | _              |

| fFTM_0_REF_CLK         | FlexTimer 0 external<br>clock frequency   | _   | —   | 20    | MHz  | FTM_0_REF_CLK         | _              |

| fFTM_1_REF_CLK         | FlexTimer 1 external<br>clock frequency   | _   | —   | 20    | MHz  | FTM_1_REF_CLK         | _              |

| fFLEXRAY_PE_<br>CLK    | FlexRay PE clock<br>frequency             | _   | —   | 40    | MHz  | FLEXRAY_PE_CLK        | _              |

| fCAN_PE_CLK            | CAN PE clock<br>frequency                 | 40  | -   | 80    | MHz  | CAN_PE_CLK            | _              |

| fLIN_BAUD_CLK          | LIN baud clock<br>frequency               | _   | _   | 133   | MHz  | LIN_BAUD_CLK          | _              |

| fLINFLEXD_CLK          | LIN clock frequency                       | —   | -   | 66.7  | MHz  | LINFLEXD_CLK          | —              |

| fGMAC_TS_CLK           | GMAC timestamp cl<br>ock frequency        | 5   | -   | 200   | MHz  | GMAC_TS_CLK           | _              |

| fGMAC_0_TX_CLK         | GMAC_0<br>transmit clock<br>frequency     | 2.5 | -   | 125   | MHz  | GMAC_0_TX_CLK         | _              |

| fGMAC_0_RX_CLK         | GMAC_0 receive<br>clock frequency         | 2.5 | —   | 125   | MHz  | GMAC_0_RX_CLK         | _              |

| fGMAC_0_REF_<br>CLK    | GMAC_0 reference<br>clock frequency       | _   | —   | 50    | MHz  | GMAC_0_REF_CLK        | —              |

| fPFE_MAC_0_TX_<br>CLK  | PFE MAC_0<br>transmit clock<br>frequency  | 2.5 | -   | 312.5 | MHz  | PFE_MAC_0_TX_CLK      | _              |

| fPFE_MAC_0_RX_<br>CLK  | PFE MAC_0 receive<br>clock frequency      | 2.5 | —   | 312.5 | MHz  | PFE_MAC_0_RX_CLK      | _              |

| fPFE_MAC_0_<br>REF_CLK | PFE MAC_0<br>reference clock<br>frequency | _   | -   | 50    | MHz  | PFE_MAC_0_REF_<br>CLK | -              |

| fPFE_MAC_1_TX_<br>CLK  | PFE MAC_1<br>transmit clock<br>frequency  | 2.5 | -   | 312.5 | MHz  | PFE_MAC_1_TX_CLK      | -              |

| fPFE_MAC_1_RX_<br>CLK  | PFE MAC_1 receive<br>clock frequency      | 2.5 | -   | 312.5 | MHz  | PFE_MAC_1_RX_CLK      | _              |

Table 6. Clock frequency ranges (continued)

| Symbol                 | Description                               | Min | Тур | Max   | Unit | Condition                         | Spec<br>Number |

|------------------------|-------------------------------------------|-----|-----|-------|------|-----------------------------------|----------------|

| fPFE_MAC_1_<br>REF_CLK | PFE<br>MAC_1 reference<br>clock frequency |     | -   | 50    | MHz  | PFE_MAC_1_REF_<br>CLK             |                |

| fPFE_MAC_2_TX_<br>CLK  | PFE<br>MAC_2 transmit cloc<br>k frequency | 2.5 | -   | 312.5 | MHz  | PFE_MAC_2_TX_CLK                  | _              |

| fPFE_MAC_2_RX_<br>CLK  | PFE MAC_2 receive<br>clock frequency      | 2.5 | —   | 312.5 | MHz  | PFE_MAC_2_RX_CLK                  | _              |

| fPFE_MAC_2_<br>REF_CLK | PFE<br>MAC_2 reference<br>clock frequency | _   | -   | 50    | MHz  | PFE_MAC_2_REF_<br>CLK             | _              |

| fSPI_CLK               | SPI clock frequency                       | 10  | _   | 100   | MHz  | SPI_CLK                           | _              |

| fQSPI_2X_CLK           | QSPI 2X clock<br>frequency                | -   | _   | 400   | MHz  | QSPI_2X_CLK - DDR<br>200MHz       | _              |

| fQSPI_2X_CLK           | QSPI 2X clock<br>frequency                | -   | -   | 333   | MHz  | QSPI_2X_CLK - DDR<br>166MHz       | _              |

| fQSPI_2X_CLK           | QSPI 2X clock<br>frequency                | -   | -   | 266   | MHz  | QSPI_2X_CLK - DDR /<br>SDR 133MHz | _              |

| fQSPI_2X_CLK           | QSPI 2X clock<br>frequency                | -   | -   | 208   | MHz  | QSPI_2X_CLK - SDR<br>104MHz       | _              |

| fQSPI_2X_CLK           | QSPI 2X clock<br>frequency                | _   | -   | 200   | MHz  | QSPI_2X_CLK - SDR<br>100MHz       | _              |

| fQSPI_2X_CLK           | QSPI 2X clock<br>frequency                | -   | -   | 133   | MHz  | QSPI_2X_CLK - DDR<br>66MHz        | _              |

| fQSPI_1X_CLK           | QSPI 1X clock<br>frequency                | -   | -   | 200   | MHz  | QSPI_1X_CLK - DDR<br>200MHz       | _              |

| fQSPI_1X_CLK           | QSPI 1X clock<br>frequency                | _   | -   | 166   | MHz  | QSPI_1X_CLK - DDR<br>166MHz       | _              |

| fQSPI_1X_CLK           | QSPI 1X clock<br>frequency                | _   | -   | 133   | MHz  | QSPI_1X_CLK - DDR /<br>SDR 133MHz | _              |

| fQSPI_1X_CLK           | QSPI 1X clock<br>frequency                | -   | -   | 104   | MHz  | QSPI_1X_CLK - SDR<br>104MHz       | _              |

| fQSPI_1X_CLK           | QSPI 1X clock<br>frequency                | -   | -   | 100   | MHz  | QSPI_1X_CLK - SDR<br>100MHz       | _              |

| fQSPI_1X_CLK           | QSPI 1X clock<br>frequency                | -   | -   | 66    | MHz  | QSPI_1X_CLK - DDR<br>66MHz        | _              |

| fSDHC_CLK              | uSDHC clock<br>frequency                  | -   | -   | 200   | MHz  | SDHC_CLK - DDR<br>HS400           | _              |

| Symbol       | Description                   | Min | Тур | Мах | Unit | Condition                     | Spec<br>Number |

|--------------|-------------------------------|-----|-----|-----|------|-------------------------------|----------------|

| fSDHC_CLK    | uSDHC clock<br>frequency      | 133 | _   | 200 | MHz  | SDHC_CLK - DDR<br>HS400       | —              |

| fSDHC_CLK    | uSDHC clock<br>frequency      | _   | _   | 200 | MHz  | SDHC_CLK - SDR<br>HS200       | _              |

| fSDHC_CLK    | uSDHC clock<br>frequency      | —   | —   | 100 | MHz  | SDHC_CLK - SDR<br>100MHz      | —              |

| fSDHC_CLK    | uSDHC clock<br>frequency      | —   | —   | 52  | MHz  | SDHC_CLK - DDR /<br>SDR 52MHz | —              |

| fPFE_PE_CLK  | PFE PE clock<br>frequency     | _   | _   | 600 | MHz  | PFE_PE_CLK                    | _              |

| fPFE_SYS_CLK | PFE system clock<br>frequency | _   | _   | 300 | MHz  | PFE_SYS_CLK                   | —              |

#### Table 6. Clock frequency ranges (continued)

## 8 Thermal Characteristics

Thermal characteristics are targets based on simulation from preliminary die and package definitions. The specified characteristics are subject to change per final device design and characterization. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

| Table | 7. | Thermal   | Resistance    |

|-------|----|-----------|---------------|

| 10010 |    | 1 HOIHIGH | 1100101011100 |

| Board type <sup>1</sup> | Symbol           | Description                                            | Value | Unit |

|-------------------------|------------------|--------------------------------------------------------|-------|------|

| JESD51-9, 2s2p          | R <sub>θJA</sub> | Junction to ambient<br>Thermal Resistance              | 15.6  | °C/W |

| JESD51-9, 2s2p          | $\Psi_{JT}$      | Junction to Lid Top<br>Thermal Resistance <sup>2</sup> | 0.3   | °C/W |

| NA                      | R <sub>θJC</sub> | Junction to Case<br>Thermal Resistance <sup>3</sup>    | 0.4   | °C/W |

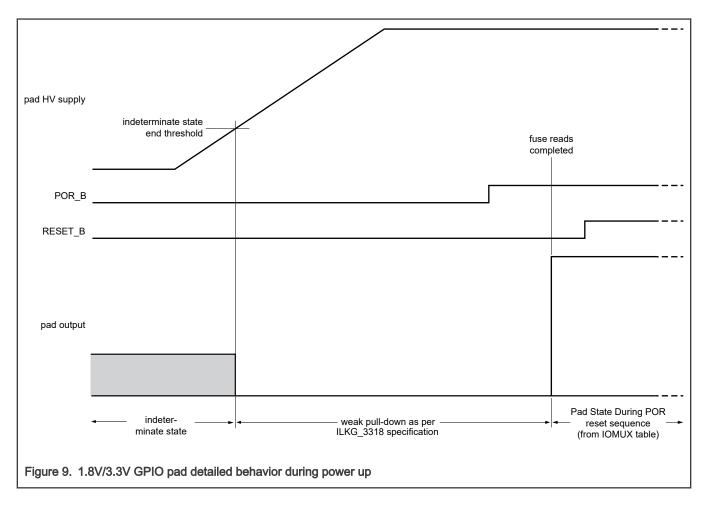

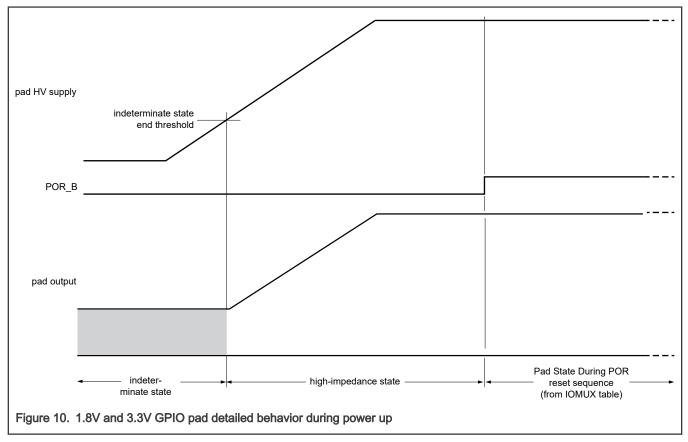

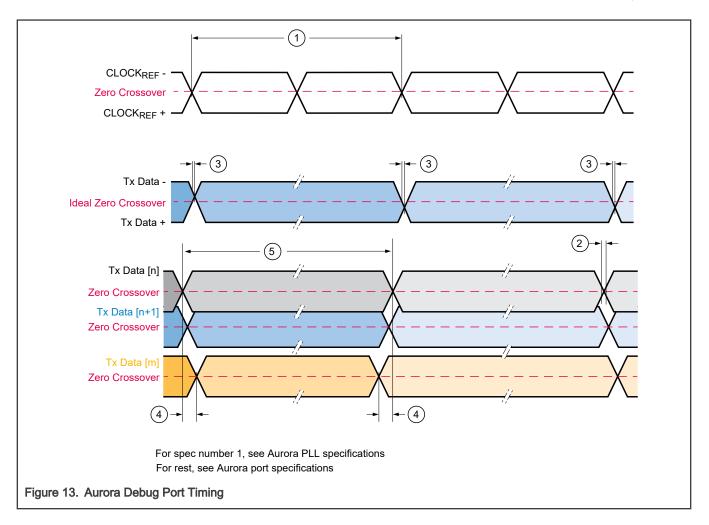

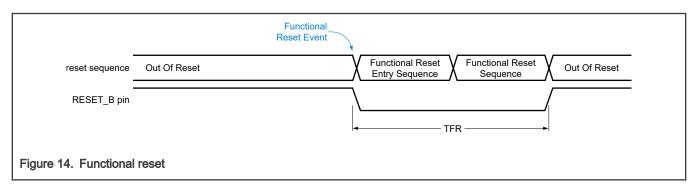

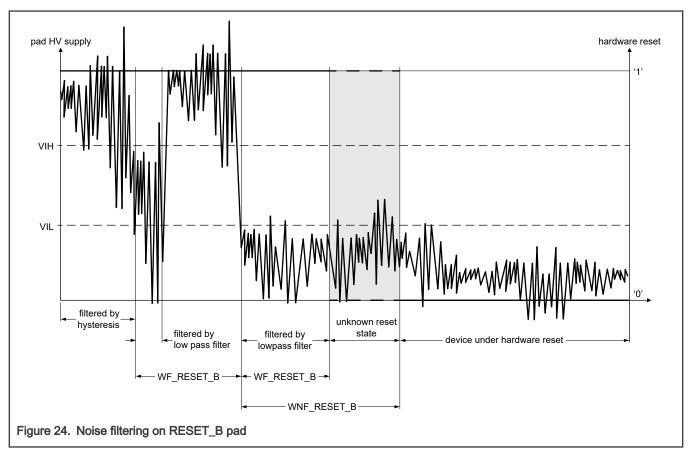

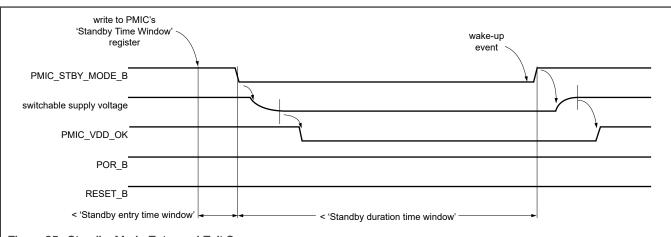

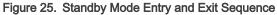

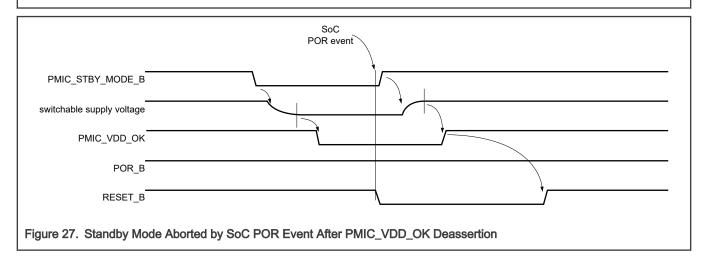

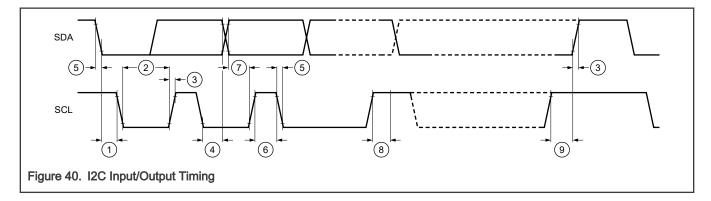

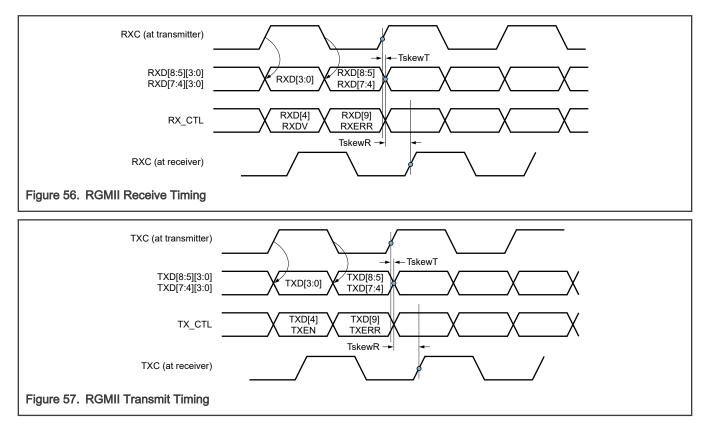

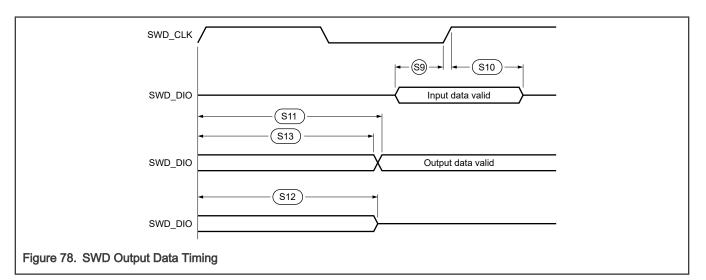

1. Thermal test board meets JEDEC specification for this package (JESD51-9).