# 8Gb, 3 V, 1-bit ECC, x8 I/O, SLC NAND Flash Memory for Embedded

### **General Description**

The SkyHigh S34ML08G1 8-Gb NAND is offered in  $3.3\ V_{CC}$  with x8 I/O interface. This document contains information for the S34ML08G1 device, which is a dual-die stack of two S34ML04G1 die. For detailed specifications, please refer to the discrete diedatasheet: S34ML04G1.

### **Distinctive Characteristics**

- Density

- $-8 \text{ Gb} (4 \text{ Gb} \times 2)$

- Architecture (For each 4 Gb device)

- Input / Output Bus Width: 8-bits

- Page Size: (2048 + 64) bytes; 64 bytes is spare area

- Block Size: 64 Pages or (128k + 4k) bytes

- Plane Size

- 2048 Blocks per Plane or (256M + 8M) bytes

- Device Size

- 2 Planes per Device or 512 Mbyte

- NAND Flash Interface

- Open NAND Flash Interface (ONFI) 1.0 compliant

- Address, Data and Commands multiplexed

- Supply Voltage

- 3.3 V device: Vcc = 2.7 V ~ 3.6 V

#### ■ Security

- One Time Programmable (OTP) area

- Hardware program/erase disabled during power transition

- Additional Features

- Supports Multiplane Program and Erase commands

- Supports Copy Back Program

- Supports Multiplane Copy Back Program

- Supports Read Cache

- Electronic Signature

- Manufacturer ID: 01h

- Operating Temperature

- Industrial: -40 °C to 85 °C

- Automotive: -40 °C to 105 °C

#### **Performance**

- Page Read / Program

- Random access: 25 µs (Max)

- Sequential access: 25 ns (Min)

- Program time / Multiplane Program time: 200 µs (Typ)

- Block Erase / Multiplane Erase (S34ML04G1)

- Block Erase time: 3.5 ms (Typ)

#### ■ Reliability

- 100,000 Program / Erase cycles (Typ)(with 1 bit / 512 + 16 byte ECC)

- 10 Year Data retention (Typ)

- Blocks zero and one are valid and will be valid for at least 1000 program-erase cycles with ECC

- Package Options

- Lead Free and Low Halogen

- -48-Pin TSOP  $12 \times 20 \times 1.2$  mm

- 63-Ball BGA  $9 \times 11 \times 1$  mm

### **Contents**

| 1.  | Connection Diagram   | 3  |

|-----|----------------------|----|

| 2.  | Pin Description      | 5  |

| 3.  | Block Diagrams       | 6  |

| 4.  | Addressing           | 8  |

| 5.  | Read Status Enhanced | 8  |

| 6.  | Extended Read Status | 8  |

| 7.  | Read ID              | 9  |

| 7.1 | Read Parameter Page  | 10 |

| 8.                | Electrical Characteristics             | 12             |

|-------------------|----------------------------------------|----------------|

| 8.1               | Valid Blocks                           | 12             |

| 8.2               | Recommended Operating Conditions       | 12             |

| 8.3               | DC Characteristics                     | 13             |

| 8.4               | Pin Capacitance                        | 13             |

| 8.5               | Power Consumptions and Pin Capacitance |                |

|                   | for Allowed Stacking Configurations    | 13             |

|                   | 101 7 monou stacking configurations    | 10             |

| 9.                | Physical Interface                     |                |

|                   |                                        | 14             |

| 9.1               | Physical Interface                     | 14<br>14       |

| 9.1<br><b>10.</b> | Physical Interface                     | 14<br>14<br>16 |

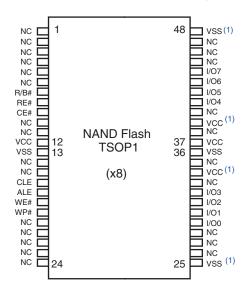

### 1. Connection Diagram

#### Note:

1. These pins should be connected to power supply or ground (as designated) following the ONFI specification, however they might not be bonded internally.

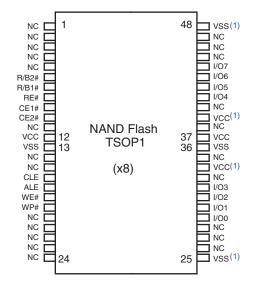

Figure 1.2 48-Pin TSOP1 Contact x8 Device (2 CE 8 Gb)

#### Note:

1. These pins should be connected to power supply or ground (as designated) following the ONFI specification, however they might not be bonded internally.

Document Number: 002-00483 Rev. \*L Page 3 of 19

(A2) NC (A1) NC (A9) NC (A10) NC (B1) NC (B9) NC (B10) NC (C4) ALE (C6) CE# (C5) VSS (C8) RB# (C3) WP# (C7) WE# (D3) VCC(1) (D4) (D6) (D5) (D7) (D8) RE# CLE NC NC NC NC NC (E6) NC (E7) NC (E8) NC (E4) NC (E5) NC (F3) NC (F6) NC (F4) (F5) NC (F7) VSS(1) (F8) NC (G3) NC (G6) NC (G7) NC (G4) (G8) NC (G5) NC VCC(1) (H3) NC (H4) I/O0 (H5) NC (H6) NC (H7) NC (H8) V<sub>cc</sub> (J3) NC (J4) I/O1 (J6) V<sub>CC</sub> (J8) I/O7 (J5) NC (J7) I/O5 (K3) (K5) (K7) (K4) (K6) (K8) NC (M1) (L2) NC (L9) NC (L10) NC (M9) NC (M2) (M10) NC

Figure 1.3 63-BGA Contact, x8 Device, Single CE (Top View)

#### Note:

1. These pins should be connected to power supply or ground (as designated) following the ONFI specification, however they might not be bonded internally.

### 2. Pin Description

Table 2.1 Pin Description

| Pin Name    | Description                                                                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1/00 - 1/07 | Inputs/Outputs. The I/O pins are used for command input, address input, data input, and data output. The I/O pins float to High-Z when the device is deselected or the outputs are disabled.                                                       |

| CLE         | <b>Command Latch Enable.</b> This input activates the latching of the I/O inputs inside the Command Register on the rising edge of Write Enable (WE#).                                                                                             |

| ALE         | Address Latch Enable. This input activates the latching of the I/O inputs inside the Address Register on the rising edge of Write Enable (WE#).                                                                                                    |

| CE#         | Chip Enable. This input controls the selection of the device. When the device is not busy CE# low selects the memory.                                                                                                                              |

| WE#         | Write Enable. This input latches Command, Address and Data. The I/O inputs are latched on the rising edge of WE#.                                                                                                                                  |

| RE#         | <b>Read Enable.</b> The RE# input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid t <sub>REA</sub> after the falling edge of RE# which also increments the internal column address counter by one. |

| WP#         | <b>Write Protect.</b> The WP# pin, when low, provides hardware protection against undesired data modification (program / erase).                                                                                                                   |

| R/B#        | Ready Busy. The Ready/Busy output is an Open Drain pin that signals the state of the memory.                                                                                                                                                       |

| VCC         | <b>Supply Voltage</b> . The $V_{CC}$ supplies the power for all the operations (Read, Program, Erase). An internal lock circuit prevents the insertion of Commands when $V_{CC}$ is less than $V_{LKO}$ .                                          |

| VSS         | Ground.                                                                                                                                                                                                                                            |

| NC          | Not Connected.                                                                                                                                                                                                                                     |

#### Notes:

Document Number: 002-00483 Rev. \*L Page 5 of 19

A 0.1 μF capacitor should be connected between the V<sub>CC</sub> Supply Voltage pin and the V<sub>SS</sub> Ground pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations.

<sup>2.</sup> An internal voltage detector disables all functions whenever  $V_{CC}$  is below 1.8V to protect the device from any involuntary program/erase during power transitions.

### 3. Block Diagrams

Address Register/ Counter Program Erase Controller HV Generation 4096 Mbit + 128 Mbit (4 Gb Device) DECODER NAND Flash ALE Memory Array CLE WE# CE# Command Interface Logic WP# RE# Page Buffer Y Decoder Command Register

Data Register I/O Buffer

I/O0~I/O7

Figure 3.1 Functional Block Diagram — 4 Gb

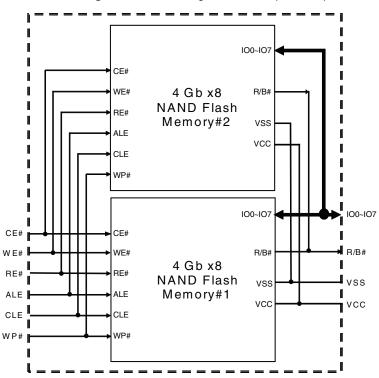

Figure 3.2 Block Diagram — 1 CE (4 Gb x 8)

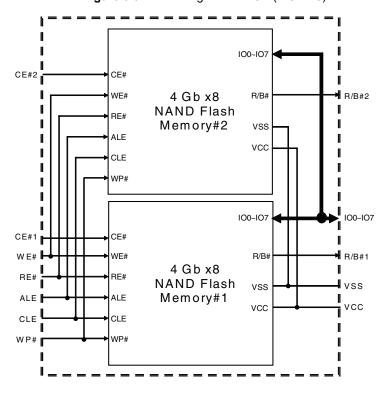

Figure 3.3 Block Diagram — 2 CE (4 Gb x 8)

### 4. Addressing

Table 4.1 Address Cycle Map

| Bus Cycle               | I/O0      | I/O1       | I/O2       | I/O3       | 1/04      | I/O5      | I/O6       | 1/07      |

|-------------------------|-----------|------------|------------|------------|-----------|-----------|------------|-----------|

| 1st / Col. Add. 1       | A0 (CA0)  | A1 (CA1)   | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)   | A7 (CA7)  |

| 2nd / Col. Add. 2       | A8 (CA8)  | A9 (CA9)   | A10 (CA10) | A11 (CA11) | Low       | Low       | Low        | Low       |

| 3rd / Row Add. 1        | A12 (PA0) | A13 (PA1)  | A14 (PA2)  | A15 (PA3)  | A16 (PA4) | A17 (PA5) | A18 (PLA0) | A19 (BA0) |

| 4th / Row Add. 2        | A20 (BA1) | A21 (BA2)  | A22 (BA3)  | A23 (BA4)  | A24 (BA5) | A25 (BA6) | A26 (BA7)  | A27 (BA8) |

| 5th / Row Add. 3<br>(6) | A28 (BA9) | A29 (BA10) | A30 (BA11) | Low        | Low       | Low       | Low        | Low       |

#### Notes:

- 1. CAx = Column Address bit.

- 2. PAx = Page Address bit.

- 3. PLA0 = Plane Address bit zero.

- 4. BAx = Block Address bit.

- 5. Block address concatenated with page address and plane address = actual page address, also known as the row address.

- 6. A30 for 8 Gb (4 Gb x 2 DDP) (1CE).

For the address bits, the following rules apply:

- A0 A11: column address in the page

- A12 A17: page address in the block

- A18: plane address (for multiplane operations) / block address (for normal operations)

- A19 A30: block address

#### 5. Read Status Enhanced

Read Status Enhanced is used to retrieve the status value for a previous operation in the following cases:

In the case of concurrent operations on a multi-die stack.

When two dies are stacked to form a dual-die package (DDP), it is possible to run one operation on the first die, then activate a different operation on the second die, for example: Erase while Read, Read while Program, etc.

■ In the case of multiplane operations in the same die.

### 6. Extended Read Status

Multi-die stack devices support the Extended Read Status operation. When two operations are active in separate dies at the same time, this feature allows the host to check the status of a given die. For example, the first die could be executing a Page Program while the second die is performing a Page Read. Refer to Table 6.1 for a description of each command.

Table 6.1 Extended Read Status

| Command | Die    | Row Address with 4 Gb Dies |

|---------|--------|----------------------------|

| F2h     | First  | 0 to 3FFFFh                |

| F3h     | Second | 40000h to 7FFFFh           |

Document Number: 002-00483 Rev. \*L Page 8 of 19

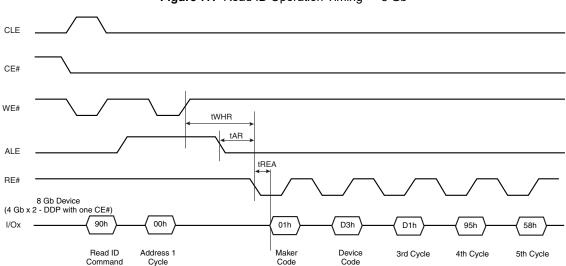

### 7. Read ID

The device contains a product identification mode, initiated by writing 90h to the command register, followed by an address input of 00h.

**Note**: If you want to execute Read Status command (0x70) after Read ID sequence, you should input dummy command (0x00) before Read Status command (0x70).

For the S34ML04G1 device, five read cycles sequentially output the manufacturer code (01h), and the device code and 3rd, 4th, and 5th cycle ID, respectively. The command register remains in Read ID mode until further commands are issued to it.

**Table 7.1** Read ID for Supported Configurations (1)

| Density                                      | Org | v <sub>cc</sub> | 1st | 2nd | 3rd | 4th | 5th |

|----------------------------------------------|-----|-----------------|-----|-----|-----|-----|-----|

| 4 Gb                                         | x8  | 3.3V            | 01h | DCh | 90h | 95h | 54h |

| 8 Gb<br>(4 Gb x 2 – DDP with<br>two CE#)     | x8  | 3.3V            | 01h | DCh | 90h | 95h | 54h |

| 8 Gb<br>(4 Gb x 2 – DDP with<br>one CE#) (1) | x8  | 3.3V            | 01h | D3h | D1h | 95h | 58h |

#### Note:

<sup>1.</sup> See See Appendix A — Errata on page 17. for information on READ ID in MCPs.

Figure 7.1 Read ID Operation Timing — 8 Gb

Document Number: 002-00483 Rev. \*L Page 9 of 19

#### 5th ID Data

Table 7.2 Read ID Byte 5 Description — S34ML04G1

|                      | Description | I/O7 | I/O6 I/O5 I/O4 | I/O3 I/O2 | I/O1 | I/O0 |

|----------------------|-------------|------|----------------|-----------|------|------|

| Plane Number         | 1           |      |                | 0 0       |      |      |

|                      | 2           |      |                | 0 1       |      |      |

|                      | 4           |      |                | 10        |      |      |

|                      | 8           |      |                | 11        |      |      |

|                      | 64 Mb       |      | 000            |           |      |      |

|                      | 128 Mb      |      | 0 0 1          |           |      |      |

|                      | 256 Mb      |      | 010            |           |      |      |

| Plane Size           | 512 Mb      |      | 011            |           |      |      |

| (without spare area) | 1 Gb        |      | 100            |           |      |      |

|                      | 2 Gb        |      | 101            |           |      |      |

|                      | 4 Gb        |      | 110            |           |      |      |

|                      | 8 Gb        |      | 111            |           |      |      |

| Reserved             |             | 0    |                |           | 0    | 0    |

### 7.1 Read Parameter Page

The device supports the ONFI Read Parameter Page operation, initiated by writing ECh to the command register, followed by an address input of 00h. The command register remains in Parameter Page mode until further commands are issued to it. Table 7.3 explains the parameter fields.

**Note:** For 41nm 2Gb/4Gb SkyHigh NAND, for a particular condition, the Read Parameter Page command does not give the correct values. To overcome this issue, the host must issue a Reset command before the Read Parameter Page command. Issuance ofReset before the Read Parameter Page command will provide the correct values and will not output 00h values. This does not apply to 48nm 1Gb.

Table 7.3 Parameter Page Description (Sheet 1 of 3)

| Byte  | O/M | Description                                                                                                                                                                                                                                                              | Values             |

|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|       |     | Revision Information and Features Block                                                                                                                                                                                                                                  |                    |

| 0-3   | М   | Parameter page signature  Byte 0: 4Fh, "O"  Byte 1: 4Eh, "N"  Byte 2: 46h, "F"  Byte 3: 49h, "I"                                                                                                                                                                         | 4Fh, 4Eh, 46h, 49h |

| 4-5   | М   | Revision number  2-15 Reserved (0)  1 1 = supports ONFI version 1.0  0 Reserved (0)                                                                                                                                                                                      | 02h, 00h           |

| 6-7   | М   | Features supported  5-15 Reserved (0)  4 1 = supports odd to even page Copyback  3 1 = supports interleaved operations  2 1 = supports non-sequential page programming  1 1 = supports multiple LUN operations  0 1 = supports 16-bit data bus width                     | 1Eh, 00h           |

| 8-9   | М   | Optional commands supported  6-15 Reserved (0)  5 1 = supports Read Unique ID  4 1 = supports Copyback  3 1 = supports Read Status Enhanced  2 1 = supports Get Features and Set Features  1 1 = supports Read Cache commands  0 1 = supports Page Cache Program command | 1Bh, 00h           |

| 10-31 |     | Reserved (0)                                                                                                                                                                                                                                                             | 00h                |

Document Number: 002-00483 Rev. \*L Page 10 of 19

Table 7.3 Parameter Page Description (Sheet 2 of 3)

| Byte     | O/M | Description                                                                                                                                                                                                                     | Values                                                                                                 |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| <u> </u> |     | Manufacturer Information Block                                                                                                                                                                                                  | •                                                                                                      |

| 32-43    | М   | Device manufacturer (12 ASCII characters)                                                                                                                                                                                       | 53h, 50h, 41h, 4Eh, 53h, 49h,<br>4Fh, 4Eh, 20h, 20h, 20h, 20h                                          |

| 44-63    | М   | Device model (20 ASCII characters)                                                                                                                                                                                              | 53h, 33h, 34h, 4Dh, 4Ch, 30h,<br>38h, 47h, 31h, 20h, 20h, 20h,<br>20h, 20h, 20h, 20h, 20h,<br>20h, 20h |

| 64       | М   | JEDEC manufacturer ID                                                                                                                                                                                                           | 01h                                                                                                    |

| 65-66    | 0   | Date code                                                                                                                                                                                                                       | 00h                                                                                                    |

| 67-79    |     | Reserved (0)                                                                                                                                                                                                                    | 00h                                                                                                    |

| <u> </u> |     | Memory Organization Block                                                                                                                                                                                                       | <u> </u>                                                                                               |

| 80-83    | М   | Number of data bytes per page                                                                                                                                                                                                   | 00h, 08h, 00h, 00h                                                                                     |

| 84-85    | М   | Number of spare bytes per page                                                                                                                                                                                                  | 40h, 00h                                                                                               |

| 86-89    | М   | Number of data bytes per partial page                                                                                                                                                                                           | 00h, 02h, 00h, 00h                                                                                     |

| 90-91    | М   | Number of spare bytes per partial page                                                                                                                                                                                          | 10h, 00h                                                                                               |

| 92-95    | М   | Number of pages per block                                                                                                                                                                                                       | 40h, 00h, 00h, 00h                                                                                     |

| 96-99    | М   | Number of blocks per logical unit (LUN)                                                                                                                                                                                         | 00h, 10h, 00h, 00h                                                                                     |

| 100      | М   | Number of logical units (LUNs)                                                                                                                                                                                                  | 02h                                                                                                    |

| 101      | М   | Number of address cycles  4-7 Column address cycles  0-3 Row address cycles                                                                                                                                                     | 23h                                                                                                    |

| 102      | М   | Number of bits per cell                                                                                                                                                                                                         | 01h                                                                                                    |

| 103-104  | М   | Bad blocks maximum per LUN                                                                                                                                                                                                      | 50h, 00h                                                                                               |

| 105-106  | М   | Block endurance                                                                                                                                                                                                                 | 01h, 05h                                                                                               |

| 107      | М   | Guaranteed valid blocks at beginning of target                                                                                                                                                                                  | 01h                                                                                                    |

| 108-109  | М   | Block endurance for guaranteed valid blocks                                                                                                                                                                                     | 01h, 03h                                                                                               |

| 110      | М   | Number of programs per page                                                                                                                                                                                                     | 04h                                                                                                    |

| 111      | М   | Partial programming attributes 5-7 Reserved 4 1 = partial page layout is partial page data followed by partial page spare 1-3 Reserved 0 1 = partial page programming has constraints                                           | 00h                                                                                                    |

| 112      | М   | Number of bits ECC correctability                                                                                                                                                                                               | 01h                                                                                                    |

| 113      | М   | Number of interleaved address bits  4-7 Reserved (0)  0-3 Number of interleaved address bits                                                                                                                                    | 01h                                                                                                    |

| 114      | 0   | Interleaved operation attributes  4-7 Reserved (0)  3 Address restrictions for program cache  2 1 = program cache supported  1 1 = no block address restrictions  0 Overlapped / concurrent interleaving support                | 04h                                                                                                    |

| 115-127  |     | Reserved (0)                                                                                                                                                                                                                    | 00h                                                                                                    |

|          |     | Electrical Parameters Block                                                                                                                                                                                                     | ·                                                                                                      |

| 128      | М   | I/O pin capacitance                                                                                                                                                                                                             | 0Ah                                                                                                    |

| 129-130  | М   | Timing mode support 6-15 Reserved (0) 5 1 = supports timing mode 5 4 1 = supports timing mode 4 3 1 = supports timing mode 3 2 1 = supports timing mode 2 1 1 = supports timing mode 1 0 1 = supports timing mode 0, shall be 1 | 1Fh, 00h                                                                                               |

Table 7.3 Parameter Page Description (Sheet 3 of 3)

| Byte    | O/M | Description                                                                                                                                                                                                                              | Values                      |

|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 131-132 | 0   | Program cache timing mode support  6-15 Reserved (0)  5 1 = supports timing mode 5  4 1 = supports timing mode 4  3 1 = supports timing mode 3  2 1 = supports timing mode 2  1 1 = supports timing mode 1  0 1 = supports timing mode 0 | 1Fh, 00h                    |

| 133-134 | М   | t <sub>PROG</sub> Maximum page program time (μs)                                                                                                                                                                                         | BCh, 02h                    |

| 135-136 | М   | t <sub>BERS</sub> Maximum block erase time (μs)                                                                                                                                                                                          | 10h, 27h                    |

| 137-138 | М   | t <sub>R</sub> Maximum page read time (μs)                                                                                                                                                                                               | 19h, 00h                    |

| 139-140 | М   | t <sub>CCS</sub> Minimum Change Column setup time (ns)                                                                                                                                                                                   | 64h, 00h                    |

| 141-163 |     | Reserved (0)                                                                                                                                                                                                                             | 00h                         |

|         |     | Vendor Block                                                                                                                                                                                                                             |                             |

| 164-165 | М   | Vendor specific Revision number                                                                                                                                                                                                          | 00h                         |

| 166-253 |     | Vendor specific                                                                                                                                                                                                                          | 00h                         |

| 254-255 | М   | Integrity CRC                                                                                                                                                                                                                            | 7Bh, 09h                    |

|         |     | Redundant Parameter Pages                                                                                                                                                                                                                | •                           |

| 256-511 | М   | Value of bytes 0-255                                                                                                                                                                                                                     | Repeat Value of bytes 0-255 |

| 512-767 | М   | Value of bytes 0-255                                                                                                                                                                                                                     | Repeat Value of bytes 0-255 |

| 768+    | 0   | Additional redundant parameter pages                                                                                                                                                                                                     | FFh                         |

Note:

### 8. Electrical Characteristics

### 8.1 Valid Blocks

Table 8.1 Valid Blocks — 4 Gb

| Device    | Symbol          | Min      | Тур | Max  | Unit   |

|-----------|-----------------|----------|-----|------|--------|

| S34ML04G1 | N <sub>VB</sub> | 4016     |     | 4096 | Blocks |

| S34ML08G1 | N <sub>VB</sub> | 8032 (1) |     | 8192 | Blocks |

Note:

### 8.2 Recommended Operating Conditions

Table 8.2 Recommended Operating Conditions

| Parameter             | Symbol | Min | Тур | Max | Units |

|-----------------------|--------|-----|-----|-----|-------|

| Vcc Supply Voltage    | Vcc    | 2.7 | 3.3 | 3.6 | V     |

| Ground Supply Voltage | Vss    | 0   | 0   | 0   | V     |

Document Number: 002-00483 Rev. \*L Page 12 of 19

<sup>1.</sup> O" Stands for Optional, "M" for Mandatory.

<sup>1.</sup> Each 4 Gb has maximum 80 bad blocks.

### 8.3 DC Characteristics

**Table 8.3** DC Characteristics and Operating Conditions

(Values listed are for each 4 Gb NAND, 8 Gb (4 Gb x 2) will be additive accordingly)

| Parameter                         |                 | Symbol                | Test Conditions                                                             | Min                   | Тур | Max                   | Units |

|-----------------------------------|-----------------|-----------------------|-----------------------------------------------------------------------------|-----------------------|-----|-----------------------|-------|

| Power-On Current                  |                 | I <sub>CC0</sub>      | Power up Current                                                            | _                     | 15  | 30                    | mA    |

|                                   | Sequential Read | I <sub>CC1</sub>      | $t_{RC} = t_{RC} \text{ (min), CE\# =}$ $V_{IL}$ , $I_{OUT} = 0 \text{ mA}$ |                       | 15  | 30                    | mA    |

| Operating Current                 | Program         |                       | Normal                                                                      | _                     | _   | 30                    | mA    |

|                                   | Flogram         | I <sub>CC2</sub>      | Cache                                                                       | _                     | 1   | 40                    | mA    |

|                                   | Erase           | I <sub>CC3</sub>      | _                                                                           | _                     | 15  | 30                    | mA    |

| Standby current, (TTL)            |                 | I <sub>CC4</sub>      | CE# = V <sub>IH</sub> ,<br>WP# = 0V/Vcc                                     | _                     | _   | 1                     | mA    |

| Standby current, (CMOS)           |                 | I <sub>CC5</sub>      | $CE\# = V_{CC}-0.2,$<br>$WP\# = 0/V_{CC}$                                   | _                     | 10  | 50                    | μΑ    |

| Input Leakage Current             |                 | ILI                   | V <sub>IN</sub> = 0 to 3.6V                                                 | _                     | _   | ±10                   | μA    |

| Output Leakage Current            |                 | I <sub>LO</sub>       | V <sub>OUT</sub> = 0 to 3.6V                                                | _                     | _   | ±10                   | μA    |

| Input High Voltage                |                 | V <sub>IH</sub>       | _                                                                           | V <sub>CC</sub> x 0.8 | _   | V <sub>CC</sub> + 0.3 | V     |

| Input Low Voltage                 |                 | V <sub>IL</sub>       | _                                                                           | -0.3                  | _   | V <sub>CC</sub> x 0.2 | V     |

| Output High Voltage               |                 | V <sub>OH</sub>       | I <sub>OH</sub> = -400 μA                                                   | 2.4                   | _   | _                     | V     |

| Output Low Voltage                |                 | V <sub>OL</sub>       | I <sub>OL</sub> = 2.1 mA                                                    | _                     | _   | 0.4                   | V     |

| Output Low Current (R/B#)         |                 | I <sub>OL(R/B#)</sub> | V <sub>OL</sub> = 0.4V                                                      | 8                     | 10  | _                     | mA    |

| Erase and Program Lockout Voltage |                 | V <sub>LKO</sub>      | _                                                                           | _                     | 1.8 | _                     | V     |

#### Notes:

- 1. All V<sub>CC</sub> pins, and V<sub>SS</sub> pins respectively, are shorted together.

- 2. Values listed in this table refer to the complete voltage range for V<sub>CC</sub> and to a single device in case of device stacking.

- 3. All current measurements are performed with a 0.1 µF capacitor connected between the V<sub>CC</sub> Supply Voltage pin and the V<sub>SS</sub> Ground pin.

- 4. Standby current measurement can be performed after the device has completed the initialization process at power-up.

### 8.4 Pin Capacitance

Table 8.4 Pin Capacitance (TA = 25°C, f=1.0 MHz)

| Parameter      | Symbol          | Test Condition       | Min | Max | Unit |

|----------------|-----------------|----------------------|-----|-----|------|

| Input          | C <sub>IN</sub> | V <sub>IN</sub> = 0V | _   | 10  | pF   |

| Input / Output | C <sub>IO</sub> | V <sub>IL</sub> = 0V | _   | 10  | pF   |

#### Note:

1. For the stacked devices version the Input is 10 pF x [number of stacked chips] and the Input/Output is 10 pF x [number of stacked chips].

## 8.5 Power Consumptions and Pin Capacitance for Allowed Stacking Configurations

When multiple dies are stacked in the same package, the power consumption of the stack will increase according to the number of chips. As an example, the standby current is the sum of the standby currents of all the chips, while the active power consumption depends on the number of chips concurrently executing different operations.

When multiple dies are stacked in the same package the pin/ball capacitance for the single input and the single input/output of the combo package must be calculated based on the number of chips sharing that input or that pin/ball.

Document Number: 002-00483 Rev. \*L Page 13 of 19

### 9. Physical Interface

### 9.1 Physical Diagram

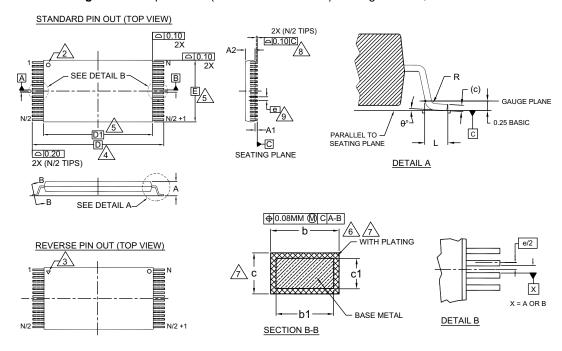

### 9.1.1 48-Pin Thin Small Outline Package (TSOP1)

Figure 9.1 48-pin TSOP (18.4 × 12.0 × 1.2 mm) Package Outline, 51-85183

| SYMBOL   | DIMENSIONS  |      |      |  |

|----------|-------------|------|------|--|

| STIVIBOL | MIN.        | NOM. | MAX. |  |

| Α        | _           | _    | 1.20 |  |

| A1       | 0.05        | 1    | 0.15 |  |

| A2       | 0.95        | 1.00 | 1.05 |  |

| b1       | 0.17        | 0.20 | 0.23 |  |

| b        | 0.17        | 0.22 | 0.27 |  |

| c1       | 0.10        | _    | 0.16 |  |

| С        | 0.10        | _    | 0.21 |  |

| D        | 20.00 BASIC |      |      |  |

| D1       | 18.40 BASIC |      |      |  |

| Е        | 12.00 BASIC |      |      |  |

| е        | 0.50 BASIC  |      |      |  |

| L        | 0.50        | 0.60 | 0.70 |  |

| θ        | 0°          | _    | 8    |  |

| R        | 0.08        | _    | 0.20 |  |

| N        | 48          |      |      |  |

#### NOTES:

1. DIMENSIONS ARE IN MILLIMETERS (mm).

PIN 1 IDENTIFIER FOR STANDARD PIN OUT (DIE UP).

PIN 1 IDENTIFIER FOR REVERSE PIN OUT (DIE DOWN): INK OR LASER MARK.

TO BE DETERMINED AT THE SEATING PLANE C. THE SEATING PLANE IS DEFINED AS THE PLANE OF CONTACT THAT IS MADE WHEN THE PACKAGE LEADS ARE ALLOWED TO REST FREELY ON A FLAT HORIZONTAL SURFACE.

DIMENSIONS D1 AND E DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION ON E IS 0.15mm PER SIDE AND ON D1 IS 0.25mm PER SIDE.

DIMENSION 6 DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF 6 DIMENSION AT MAX. MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND AN ADJACENT LEAD TO BE 0.07mm.

THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10mm AND 0.25mm FROM THE LEAD TIP.

LEAD COPLANARITY SHALL BE WITHIN 0.10mm AS MEASURED FROM THE SEATING PLANE.

DIMENSION "e" IS MEASURED AT THE CENTERLINE OF THE LEADS.

10. JEDEC SPECIFICATION NO. REF: MO-142(D)DD.

51-85183 \*F

Document Number: 002-00483 Rev. \*L Page 14 of 19

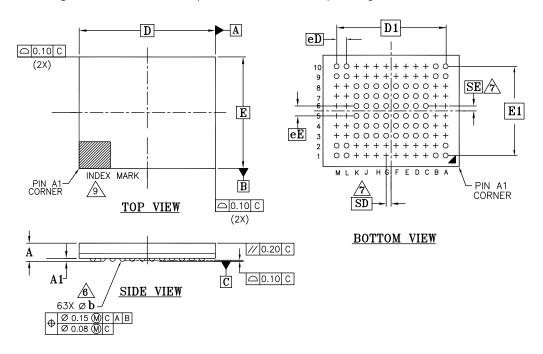

### 9.1.2 63-Pin Ball Grid Array (BGA)

Figure 9.2 63-ball VFBGA (11.00 × 9.00 × 1.00 mm) Package Outline, 002-19064

| SYMBOL | DIMENSIONS     |          |      |  |  |

|--------|----------------|----------|------|--|--|

| STMBUL | MIN.           | NOM.     | MAX. |  |  |

| A      | -              | -        | 1.00 |  |  |

| A1     | 0.25           | -        |      |  |  |

| D      | 11.00 BSC      |          |      |  |  |

| E      |                | 9.00 BSC |      |  |  |

| D1     | 8.80 BSC       |          |      |  |  |

| E1     | 7.20 BSC       |          |      |  |  |

| MD     | 12             |          |      |  |  |

| ME     | 10             |          |      |  |  |

| n      | 63             |          |      |  |  |

| Øb     | 0.40 0.45 0.50 |          |      |  |  |

| еE     | 0.80 BSC       |          |      |  |  |

| eD     | 0.80 BSC       |          |      |  |  |

| SD     | 0.40 BSC       |          |      |  |  |

| SE     | 0.40 BSC       |          |      |  |  |

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING METHODS PER ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.

- 3. BALL POSITION DESIGNATION PER JEP95, SECTION 3, SPP-020.

- 4. @ REPRESENTS THE SOLDER BALL GRID PITCH.

- 5. SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D" DIRECTION.

SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE "E" DIRECTION.

IN IS THE NUMBER OF POPULATED SOLDER BALL POSITIONS FOR MATRIX SIZE MD X ME.

- $\stackrel{\frown}{\triangle}$  dimension "b" is measured at the maximum ball diameter in a plane parallel to datum c.

- "SD" AND "SE" ARE MEASURED WITH RESPECT TO DATUMS A AND B AND DEFINE THE

POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW.

WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW "SD" OR "SE" = 0.

WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, "SD" = eD/2 AND "SE" = eE/2.

- 8. "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED BALLS.

- 41 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK MARK, METALLIZED MARK INDENTATION OR OTHER MEANS.

10. JEDEC REFERENCE SPEC: MO-207(M)

002-19064 \*\*

Document Number: 002-00483 Rev. \*L Page 15 of 19

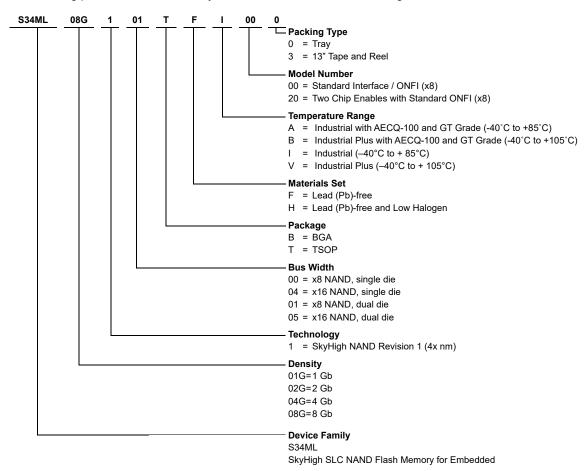

### 10. Ordering Information

The ordering part number is formed by a valid combination of the following:

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific valid combinations and to check on newly released combinations.

|                  | Valid Combinations   |            |              |                 |                      |                                |                 |                        |

|------------------|----------------------|------------|--------------|-----------------|----------------------|--------------------------------|-----------------|------------------------|

| Device<br>Family | Density              | Technology | Bus<br>Width | Package<br>Type | Temperature<br>Range | Additional<br>Ordering Options | Packing<br>Type | Package<br>Description |

| S34ML            | 08G                  | 1          | 01           | TF              | A B I V              | 00, 20                         | 0, 3            | TSOP                   |

| 334IVIL          | 08G 1 01 BH A, B, I, |            | A, B, I, V   | 00              | 0, 3                 | BGA (1)                        |                 |                        |

#### Note:

1. BGA package marking omits the leading "S34" and the Packing Type designator from the ordering part number.

### 11. Appendix A — Errata

For SkyHigh NAND MCPs (Multi-Chip Package) like the 8 Gb (2 x 4 Gb), due to the internal bonding, READ ID automatically changes to the hard-wired values and currently there is no way to change it electrically. Therefore, the SkyHigh NAND 8 Gb with one

CE# will not follow the same methodology of READ ID as SDPs (Single Die Package). The READ ID values for the 8-Gb SkyHigh NAND with one CE# will be as follows:

1st Byte: 01h 2nd Byte: D3h 3rd Byte: D1h 4th Byte: 95h 5th Byte: 58h

|                                             | 1st Byte | 2nd Byte | 3rd Byte | 4th Byte | 5th Byte |

|---------------------------------------------|----------|----------|----------|----------|----------|

| 8 Gb with one CE#<br>(Currently with error) | 01h      | D3h      | D1h      | 95h      | 58h      |

| 8 Gb with one CE# (SkyHigh methodology)     | 01h      | DCh      | 91h      | 95h      | 54h      |

Currently, SkyHigh does not plan to fix the problem. If there are any issues related to this, please contact SkyHigh NAND Product Marketing for further questions.

Document Number: 002-00483 Rev. \*L Page 17 of 19

### 12. Document History

| Rev. | ECN No. | Orig. of<br>Change             | Submission<br>Date                      | Description of Change                                                                                                                                                           |

|------|---------|--------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | _       | XILA                           | 08/23/2012                              | Initial release                                                                                                                                                                 |

| *A   | -       | XILA                           | 10/01/2012                              | Addressing: Address Cycle Map table: corrected data                                                                                                                             |

|      |         |                                |                                         | Read ID:                                                                                                                                                                        |

|      |         |                                |                                         | Read ID for Supported Configurations table: added row – 8 Gb (4 Gb x 2 DDP with two CE#)                                                                                        |

|      |         |                                |                                         | Read Parameter Page:                                                                                                                                                            |

|      |         |                                |                                         | Parameter Page Description table                                                                                                                                                |

|      |         |                                |                                         | corrected Electrical Parameters Block values for bytes 129-130 and byt 131-132                                                                                                  |

|      |         |                                |                                         | corrected Vendor Block values for bytes 254-255                                                                                                                                 |

|      |         |                                |                                         | Appendix A:                                                                                                                                                                     |

|      |         |                                |                                         | Added text                                                                                                                                                                      |

| *B   | _       | XILA                           | 11/29/2012                              | Ordering Information:                                                                                                                                                           |

|      |         |                                |                                         | Added Model Number                                                                                                                                                              |

| *C   | _       | XILA                           | 12/19/2012                              | Read Parameter Page:                                                                                                                                                            |

|      |         |                                |                                         | Parameter Page Description table                                                                                                                                                |

|      |         |                                |                                         | corrected Description for Bytes 129-130 and bytes 131-132                                                                                                                       |

|      |         |                                |                                         | DC Characteristics:                                                                                                                                                             |

|      |         |                                |                                         | DC Characteristics and Operating Conditions table                                                                                                                               |

|      |         |                                |                                         | corrected Test Conditions for ICC1 Output High Voltage: removed IOH = 100 μA row Output Low Voltage: removed IOL = 100 μA row Output Low Current (R/B#): removed VOL = 0.1V row |

|      |         |                                |                                         | Ordering Information:                                                                                                                                                           |

|      |         |                                |                                         | Valid Combinations table: removed Bus Width 05                                                                                                                                  |

| *D   | _       | XILA                           | 08/09/2013                              | Distinctive Characteristics:                                                                                                                                                    |

|      |         |                                |                                         | Security - Removed Serial number (unique ID)                                                                                                                                    |

|      |         |                                |                                         | Operating Temperature - removed Commercial and Extended temperature Performance:                                                                                                |

|      |         |                                |                                         | Updated Reliability                                                                                                                                                             |

|      |         |                                |                                         | Connection Diagram: Added figure - 48-Pin TSOP1 Contact x8 Device (1 CE 8 Gb) Addressing:                                                                                       |

|      |         |                                | Address Cycle Map table - appended Note |                                                                                                                                                                                 |

|      |         | Added text to Bus Cycle column |                                         |                                                                                                                                                                                 |

|      |         |                                |                                         | Extended Read Status:  Extended Read Status table - removed Commands F4h and F5h                                                                                                |

|      |         |                                |                                         | Read Parameter Page:                                                                                                                                                            |

|      |         |                                |                                         | Parameter Page Description table - corrected Byte 44-63, 100, and 254-2 Values                                                                                                  |

|      |         |                                |                                         | Valid Blocks:                                                                                                                                                                   |

|      |         |                                | 1                                       | Valid Blocks table - clarified Device values                                                                                                                                    |