# Pulse Width Modulation Amplifier

## **FEATURES**

- SINGLE SUPPLY OPERATION

- WIDE SUPPLY RANGE 16-100V

- 20A CONTINUOUS OUTPUT

- PROGRAMMABLE CURRENT LIMIT

- SHUTDOWN CONTROL

- HERMETIC PACKAGE

- 2 IN<sup>2</sup> FOOTPRINT

### **APPLICATIONS**

- BRUSH TYPE MOTOR CONTROL

- PELTIER CONTROL

- REACTIVE LOADS

- MAGNETIC COILS (MRI)

- ACTIVE MAGNETIC BEARING

- VIBRATION CANCELLING

#### **DESCRIPTION**

The SA01 amplifier is a pulse width modulation amplifier that can supply 2KW to the load. The full bridge output amplifier can be operated from a single power supply over a wide range of voltages. An error amplifier is included which can provide gain for the velocity control loop in brush type motor control applications. Current limit is programmable by a single resistor. A shutdown input turns off all four drivers of the H bridge output. A precision reference output is provided for use in offsetting the error amplifier. The error amplifier can then be scaled for standard input signals. The amplifier is protected from shorts to supply or ground. The H bridge output MOSFETs are protected from thermal overloads by directly sensing the temperature of the die. The 10-pin hermetic power package occupies only 2 square inches of board space and is isolated.

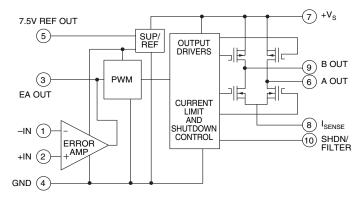

## **BLOCK DIAGRAM**

AS EA OUT (3) GOES MORE POSITIVE, HIGH STATE OF A OUT (6) INCREASES AND HIGH STATE OF B OUT (9) DECREASES.

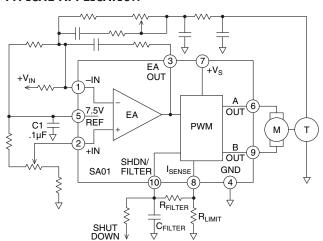

## TYPICAL APPLICATION

Motor Driver With Tach Feedback

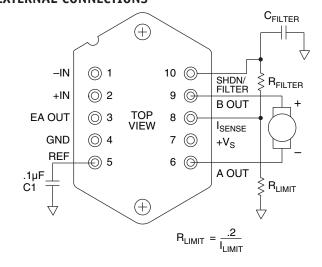

## **EXTERNAL CONNECTIONS**

ABSOLUTE MAXIMUM RATINGS SU

SHUTDOWN VOLTAGE

10V

REFERENCE LOAD CURRENT

10mA

ERROR AMP INPUT ±

0 to +12V

#### **SPECIFICATIONS**

| SPECIFICATIONS                                                                                                                                                                                                                                                                                                                           | I                                                                                                                                                        | SA01             |                 | I                                    | SA01-6  |              | I                 |                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|--------------------------------------|---------|--------------|-------------------|---------------------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                                                                | TEST CONDITIONS <sup>2</sup>                                                                                                                             | MIN              | TYP             | MAX                                  | MIN     | TYP          | MAX               | UNITS                                                                     |

| ERROR AMP  OFFSET VOLTAGE, initial  OFFSET VOLTAGE, vs. temperature  BIAS CURRENT, initial  BIAS CURRENT, vs. temperature  OFFSET CURRENT, vs. temperature  OFFSET CURRENT, vs. temperature  COMMON MODE VOLTAGE RANGE <sup>4</sup> COMMON MODE REJECTION, DC <sup>4</sup> SLEW RATE  OPEN LOOP GAIN <sup>4</sup> GAIN BANDWIDTH PRODUCT | T <sub>C</sub> = 25°C<br>Full Temperature Range⁵<br>T <sub>C</sub> = 25°C<br>Full Temperature Range⁵<br>T <sub>C</sub> = 25°C<br>Full Temperature Range⁵ | 2<br>75<br>75    | 15<br>2         | 10<br>50<br>5<br>400<br>1<br>80<br>8 | * *     | *            | * 50 * 400 * 80 * | mV<br>μV/°C<br>μA<br>nA/°C<br>μA<br>nA/°C<br>V<br>dB<br>V/μS<br>dB<br>MHz |

| OUTPUT TOTAL R <sub>ON</sub> EFFICIENCY, 10A OUTPUT SWITCHING FREQUENCY CURRENT, continuous <sup>4</sup> CURRENT, peak <sup>4</sup>                                                                                                                                                                                                      | V <sub>S</sub> = 100V<br>Full temperature range⁵                                                                                                         | 35.3<br>20<br>30 | .25<br>97<br>42 | 48.7                                 | 35<br>* | *<br>*<br>42 | 49                | Ω<br>%<br>KHz<br>A<br>A                                                   |

| REFERENCE VOLTAGE VOLTAGE VS. TEMP OUTPUT CURRENT LOAD REGULATION <sup>4</sup> LINE REGULATION                                                                                                                                                                                                                                           | I <sub>REF</sub> = 5mA<br>Full temperature range⁵                                                                                                        | 7.46             | 7.50<br>20<br>1 | 7.54<br>50<br>5<br>5                 | *       | * *          | *<br>50<br>5<br>* | V<br>PPM/°C<br>mA<br>PPM/mA<br>PPM/V                                      |

| POWER SUPPLY VOLTAGE CURRENT CURRENT, shutdown                                                                                                                                                                                                                                                                                           | Full temperature range <sup>5</sup> $I_{OUT} = 0, I_{REF} = 0,$ Full temperature range <sup>5</sup> $I_{REF} = 0$                                        | 16               | 50<br>76        | 100<br>90<br>25                      | 16      | 50<br>76     | 100<br>93<br>*    | V<br>mA<br>mA                                                             |

| SHUTDOWN TRIP POINT INPUT CURRENT                                                                                                                                                                                                                                                                                                        | REF - V                                                                                                                                                  | .18              |                 | .22<br>100                           | *       |              | *                 | V<br>nA                                                                   |

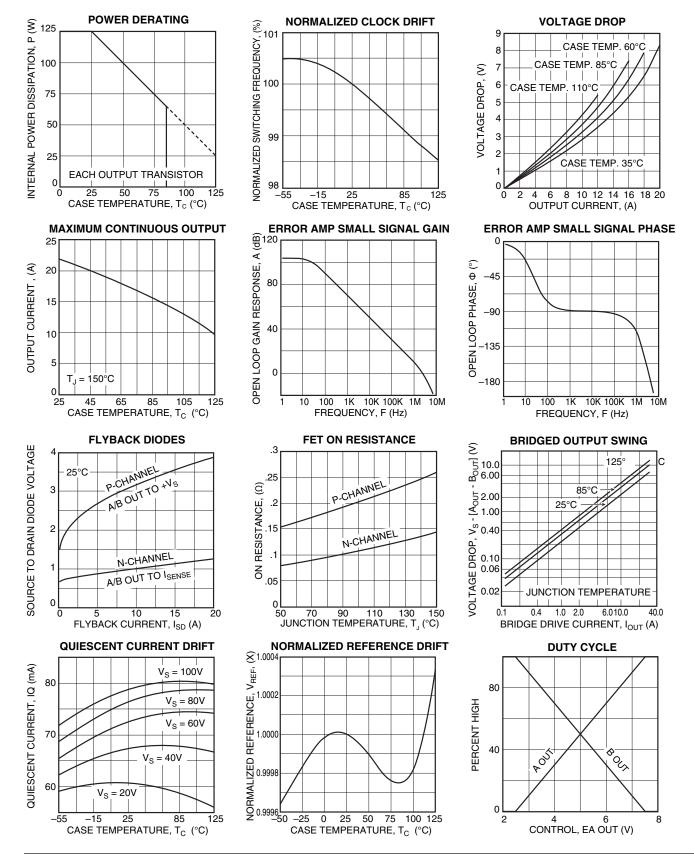

| THERMAL <sup>2</sup> RESISTANCE, junction to case <sup>4</sup> RESISTANCE, junction to air <sup>4</sup> TEMPERATURE RANGE, case                                                                                                                                                                                                          | Full temp range, for each transistor<br>Full temperature range<br>Meets full range specifications <sup>5</sup>                                           | -25              | 12              | 1.0<br>+85                           | -55     | *            | *<br>125          | °C/W<br>°C/W<br>°C                                                        |

NOTES: 1.

- Each of the two active output transistors can dissipate 125W, however the N-channel will be about 1/3 of the total dissipated power. Internal connection resistance is .05Ω.

- 2. Unless otherwise noted:  $T_c = 25$ °C.

- 3. Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation to achieve high MTTF. For guidance, refer to the heatsink data sheet.

- Guaranteed but not tested.

- Full temperature range specifications apply to the operating case temperature range as specified under THERMAL. For the SA01 these specifications are guaranteed but not tested. For the SA01-6 these specifications are tested over the SA01-6 operating case temperature range.

## **CAUTION**

The SA01 is constructed from MOSFET transistors. ESD handling procedures must be observed.

The internal substrate contains beryllia (BeO). Do not break the seal. If accidentally broken, do not crush, machine, or subject to temperatures in excess of 850°C to avoid generating toxic fumes.

2 SA01U

SA01U 3

#### **GENERAL**

Please read Application Note 30 on "PWM Basics". Refer to Application Note 1 "General Operating Considerations" for helpful information regarding power supplies, heat sinking and mounting. Visit www.apexanalog.com for design tools that help automate pwm filter design; heat sink selection; Apex Microtechnology's complete Application Notes library; Technical Seminar Workbook; and Evaluation Kits.

#### **CURRENT LIMIT**

The current limit function sets a peak limit on current flow in pin 8 (Isense). This limits load current and also limits current in the event of a short of either output to +Vs. This circuit can trip anytime during the conduction period and will hold the output transistors off for the remainder of that conduction period.

For proper operation the current limit sense resistor must be connected as shown in the external connection diagram. It is recommended that the resistor be a non-inductive type. Load current flows in pin 8. No current flows in pin 10 (Shutdown/filter) so no error will be introduced by the length of the connection to pin 10. However, the voltage at pin 10 is compared to GND (pin 4) and an error could be introduced if the grounded end of  $R_{\text{LIMIT}}$  is not directly tied to pin 4. Good circuit board layout practice would be to connect R, imit directly between pins 8 and 4.

Switching noise spikes will invariably be found at pin 8. The amplitude and duration will be load dependent. The noise spikes could trip the current limit threshold which is only 200 mV.  $\rm R_{\tiny FILTER}$  and  $\rm C_{\tiny FILTER}$  should be adjusted so as to reduce the switching noise well below 200 mV to prevent false current limiting. The sum of the DC level plus the noise peak will determine the current limiting value. Suggested starting values are  $C_{\text{FILTER}} = .01 \mu\text{F}$ ,  $R_{\text{FILTER}} = 5 \text{k}$ . The required value of  $R_{\text{LIMIT}}$  may be calculated by:

$$R_{\text{MMT}} = .2 \text{ V} / I_{\text{MMT}}$$

$R_{\text{\tiny LIMIT}} = .2~V~/~I_{\text{\tiny LIMIT}}$  where  $R_{\text{\tiny LIMIT}}$  is the required resistor value, and  $I_{\text{\tiny LIMIT}}$  is the maximum desired current.

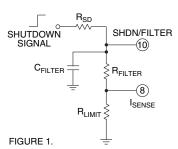

## **SHUTDOWN**

The shutdown circuitry makes use of the internal current limiting circuitry. The two functions may be externally combined as shown below in Figure 1.  $R_{\text{LIMIT}}$  will normally be a very low value resistor and can be considered zero for this application.  $\mathbf{R}_{\text{SD}}$  and  $\mathbf{R}_{\text{FILTER}}$  form a voltage divider for the shutdown signal. After a suitable noise filter is designed for the current limit adjust the value of  $R_{\rm sp}$  to give 317 mV of shutdown signal at pin 10 when the shutdown signal is high. This means pin 10 will reach the 200 mV trip point in about one time constant

with low output current and less time as output current increases. The voltage at pin 10 is referenced to pin 4 (GND). C<sub>FILTER</sub> will filter both the current limit noise spikes and the shutdown signal. Shutdown and current limit operate on each cycle of the internal switching rate. As long as

the shutdown signal is high the output will be disabled.

#### PROTECTION CIRCUITS

There are two conditions which will latch all the output transistors off. The first of these conditions is activation of the high side current limit. Specifically, current in pin 7 (+V<sub>s</sub>) is monitored. The DC trip level is about 35A and response time about 5us. As actual currents increase the response time decreases. The external fault generally associated with this condition is shorting one of the outputs to ground. However, a load fault can also activate this high side current limit if the current rise time is less than the response time of the filter discussed under "Current Limit". The second of these conditions is activation of any of the four output transistor over-temperature sensors at about 165°C. Ambient temperature, air flow, amplifier mounting problems and all the previously mentioned high current faults contribute to junction temperature. When either of these protection circuits are activated, the root fault must be corrected and power cycled to restore normal operation.

#### **DEAD TIME**

There is a dead time between the on and off of each output. The dead time removes the possibility of a momentary conduction path through the upper and lower transistors of each half bridge output during the switching interval. During the dead time all output transistors are off. Noise or flyback may be observed at the outputs during this time due to the high impedance of the outputs in the off state. This will vary with the nature of the load.

#### **ERROR AMPLIFIER**

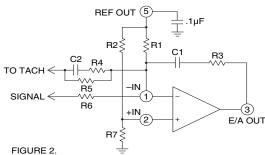

The internal error amplifier is an operational amplifier. For highest loop accuracy it is best to configure the op amp as an integrator (See Figure 2). Feedback can be adjusted with appropriate poles and zeroes to properly compensate the velocity loop for optimum stability.

The op amp is operated from a single supply voltage generated internally. The non-inverting input of the op amp does not have a common mode range which includes ground. R2 and R7 are used with the reference voltage provided at pin 5 to bias the non-inverting input to +5 volts, which is approximately half of the voltage supplied internally to the op amp. Similarly, R1 and the parallel combination of R5 R6 are selected to bias the inverting input also at +5 volts. Resistors R1 R2 must be matched. Likewise the parallel combination of R5 R6 must be matched with R7. The source impedances of the tach and the signal source may affect the matching and should be considered in the design.

4 **SA01U**