# **Digital Power Processor SA4041 (IXC2)**

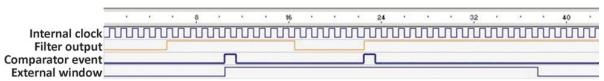

# **Device Overview**

SA4041 Digital Power Processor is a highly integrated mixed-signal IC with the industry's most complete set of analog and digital power peripherals for high-performance power system designs. The processor enables designs with low parts count, high power density and a low BOM cost. It supports variable frequency operation and control methodologies for low EMI/RFI. SA4041 also optimizes efficiency at all power levels by seamlessly changing between burst mode, continuous-conduction mode & transition mode control methods. It has enough bandwidth to control SiC/GaN devices.

#### **Features**

Rich power control-centric analog Peripherals:

- Sixteen-channel, 10-bit, 1.4 MS/s ADC

- 2 four-channel, 10-bit, 1.4 MS/s ADC

- 17 10 ns fast comparators

- 24 10-bit analog DACs for internal comparator threshold settings

- Two differential high-speed current sensing amplifier interfaces

- Programmable anti-alias low-pass filters

- Temperature sensing

Digital Power Engine and Peripherals:

- 32-bit RISC CPU with 64 KiB RAM

- 256 KiB internal SPI flash memory

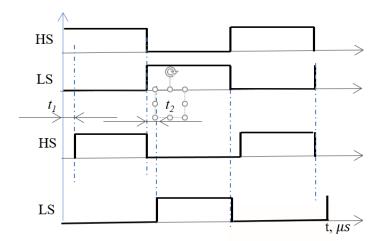

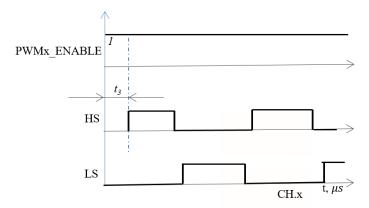

- Switching engine for up to 8 drivers with gate control for cross-conduction protection

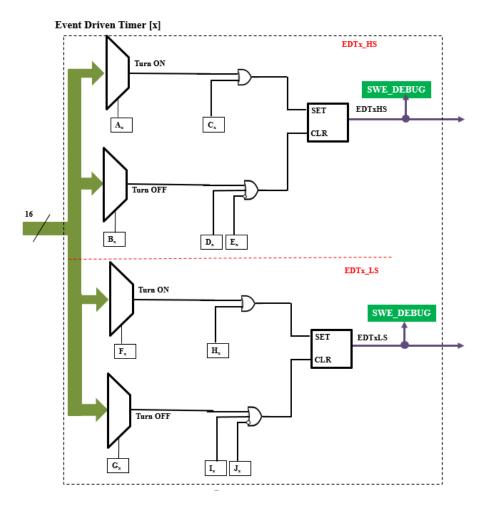

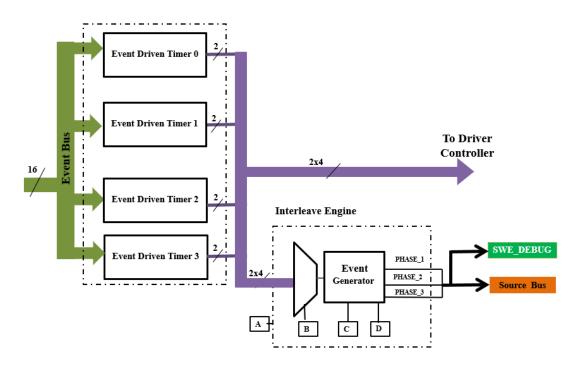

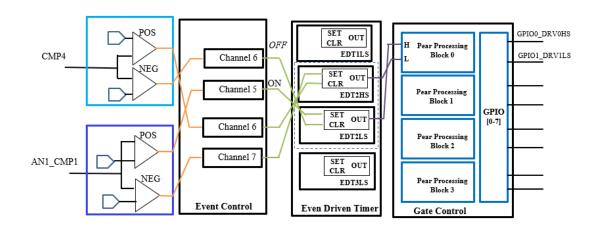

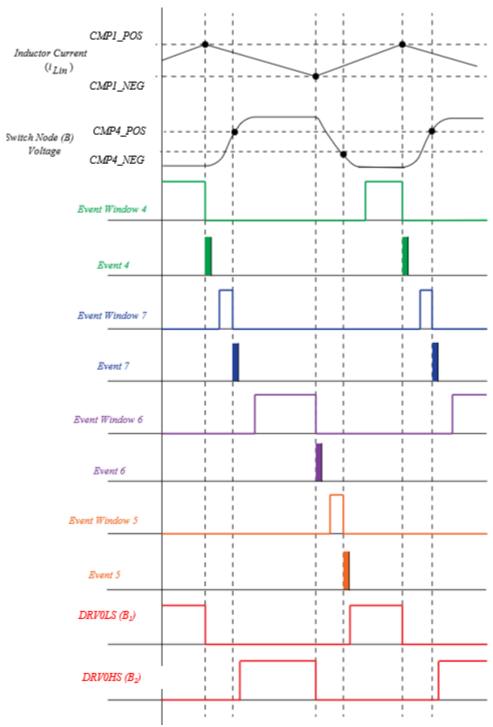

- Four event-driven timing engines with sixteen event processing channels for hysteresis control.

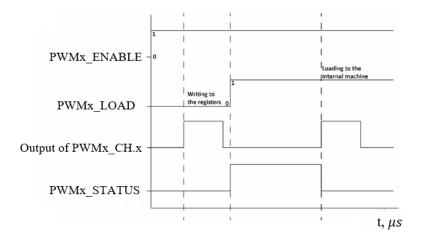

- Four PWM timers (10ns resolution, 625ps fractional)

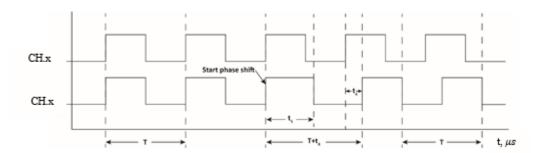

- Up to four interleaved timers with realtime programmable phase shift (any phase shift) with 10ns resolution

- Dedicated high-performance digital AC PLL with a dedicated sensing comparator for grid synchronization

- Simultaneous adjustable real-time update of frequency and duty cycle.

Junction temperature - 40 to 125° C.

# **Applications**

- AC/DC Power-Factor-Corrected- Bridgeless & Interleaved

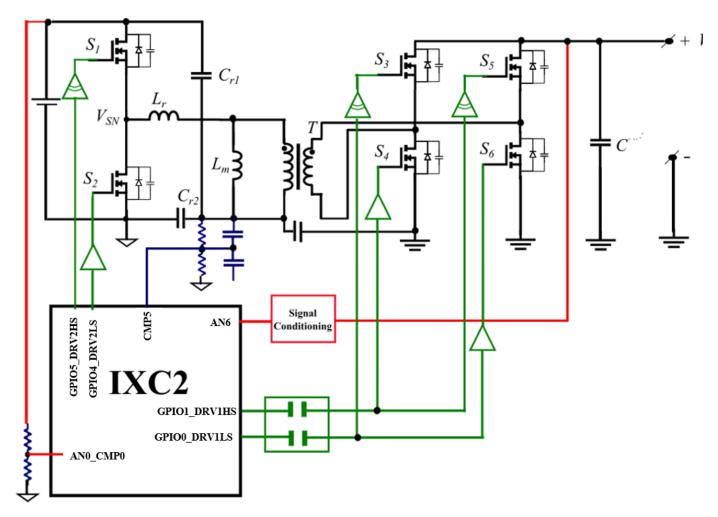

- DC/DC LLC, Half-Bridge, Phase-Shifted Full-Bridge, etc.

- Charging On-board (EV), Charge Stations, Offgrid

- Inverters Bidirectional, Automotive, UPS and Storage

- Heavy Industrial Electrified Equipment, HVAC, Welding

- Single-panel and dual-panel micro-inverters

- Battery and fuel cell inverters (unidirectional and bidirectional)

- VAR compensator

- Interleaved multi-phase battery charger for high-power applications

# **Description**

The SA4041 is a digital power processor. One IC offers high-speed analog peripherals, digital accelerators, event control, and digital processing. Its flexibility and performance enables designers to meet demanding compliance standards. Industrial, automotive, and renewable energy applications can benefit significantly from the enhanced performance and reduced component count it offers. The solution addresses many power conversion applications. It easily fits into advanced topologies for AC-DC inverters, battery chargers, and isolated DC-DC converters.

The SA4041 has an advanced mixed-signal architecture. The core is a 32-bit RISC 50 MHz micro-processor. A rich set of high-performance digital power peripherals supports the core. Communications, data memory, and general-purpose inputs and outputs (GPIO) are also provided.

The SA4041 is a fully software-programmable platform. Programming enables control, monitoring and optimization. Those features allow a design solution to meet aggressive requirements. It also allows for easily differentiated products for competitive markets. Solantro bundles a software development environment with application-specific evaluation hardware to enable customers to achieve faster time-to-market.

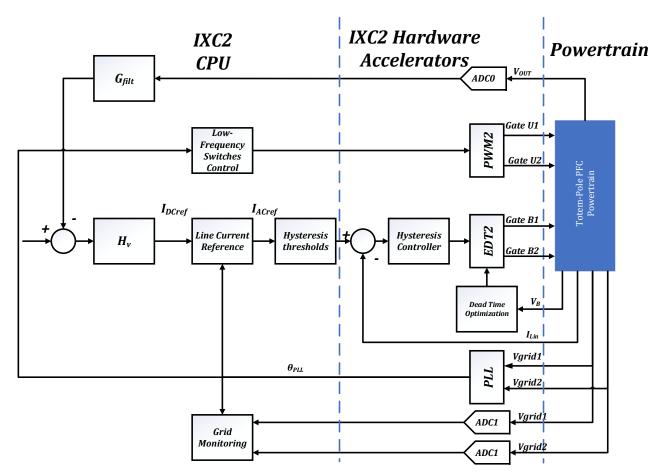

The SA4041 arose from extensive experience in power systems design. Those systems frequently require optimization of multiple voltages through control loops with adaptive dead-time control of multiple power trains and phases. For example, Totem-Pole PFC, LLC, and Interleaved PFC need such complex control schemes. Here, the core architecture optimizes processor usage by using high speed analog peripherals, digital accelerators and a high performance PLL. The peripherals control high speed loop functions leaving the digital core processor free to maintain low-speed functions. Those functions include slower control loops, protection, optimization and housekeeping. The SA4041 peripheral set is the industry's most complete single-chip offering. It includes configurable high-speed voltage/current sensing, and high-speed comparators (10nS), a variety of high-performance ADCs, DACs, programmable filtering, a multi-event interrupt-based timing engine, a high performance digital PLL, and PWM control for up to 8 power devices are integrated into a single digital power processor.

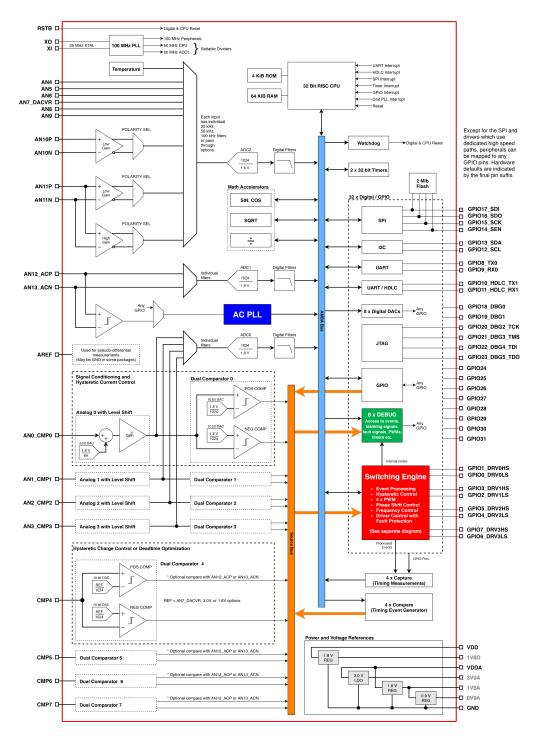

# **Functional Block Diagram**

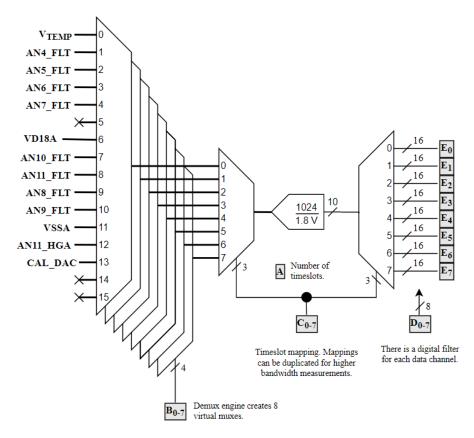

Figure 1 Functional block diagram

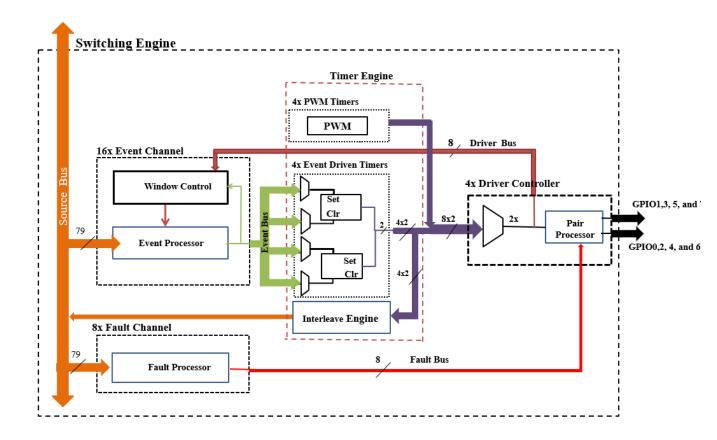

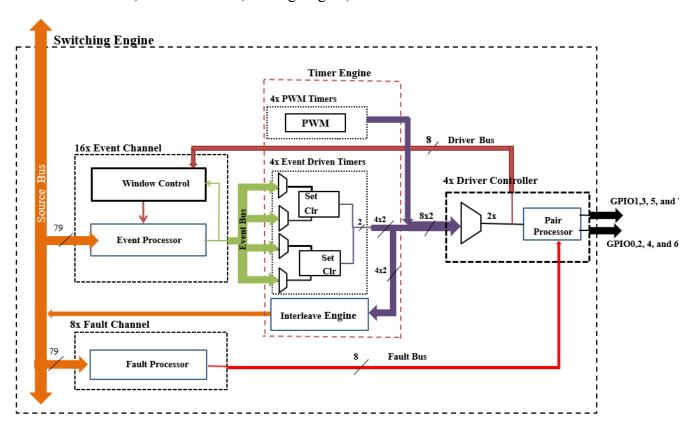

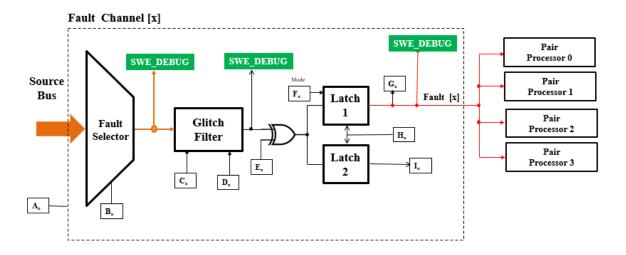

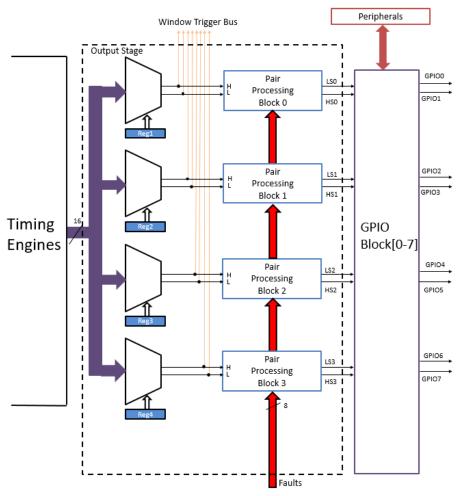

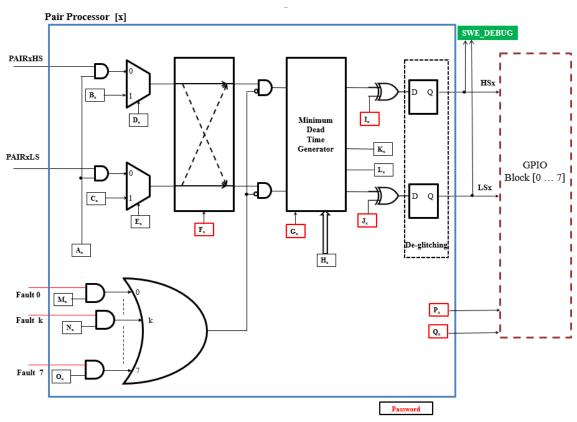

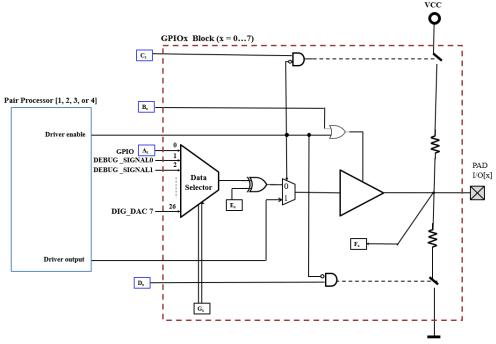

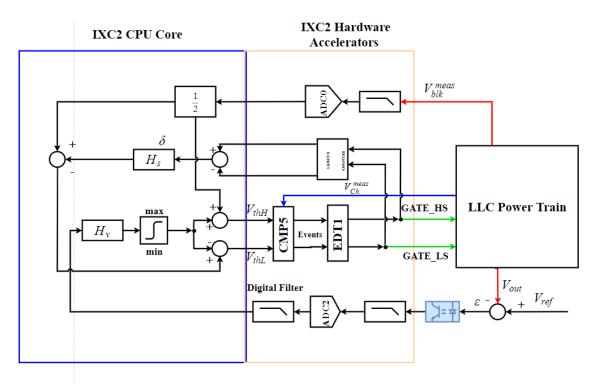

Figure 2 -High level block diagram of SA4041 Switching Engine

# **Contents**

| Device Overview                                                                                                                  | 1  |

|----------------------------------------------------------------------------------------------------------------------------------|----|

| Features                                                                                                                         | 1  |

| Applications                                                                                                                     | 1  |

| Description                                                                                                                      | 2  |

| Functional Block Diagram                                                                                                         | 3  |

| Contents                                                                                                                         |    |

| SA4041 pinout and pin functions                                                                                                  | 7  |

| SA4041 80-LQFP Pinout                                                                                                            | 7  |

| Pin descriptions                                                                                                                 | 8  |

| SA4041 specifications and characteristics.                                                                                       |    |

| Absolute maximum electrical specifications                                                                                       | 11 |

| Electrical characteristics                                                                                                       |    |

| Supply voltages and power consumption                                                                                            | 11 |

| $ANx\_CMPx$ (x = 0 to 3) specifications                                                                                          |    |

| ANx_CMPx (x = 0 t0 3) Variable Gain Amplifier (VGA) Gain 1, 2, 4, and 8                                                          |    |

| $ANx\_CMPx$ (x = 0 to 3) 4 <sup>th</sup> order low pass filter (25 kHz, 50 kHz, or 100 kHz) specifications                       | 12 |

| AN4, AN5, AN6, AN7_DACVR, AN8 and AN9 specifications                                                                             | 13 |

| Subtractor (SUB) for AN4, AN5, AN6, AN7_DACVR, AN8, AN9, AN12_ACP and AN13_AC                                                    | •  |

| Subtractor (SUB) and low pass filter (LPF) for AN4, AN5, AN6, AN7_DACVR, AN8, AN9, AN                                            |    |

| AN13 ACN specifications                                                                                                          |    |

| 4 <sup>th</sup> order low pass filter (25 kHz, 50 kHz, or 100 kHz) for AN4, AN5, AN6, AN7_DACVR, AN8 and AN13 ACN specifications |    |

| AN10P/N and AN11P/N (XCSIx $x = 0$ and 1) specifications                                                                         |    |

| AN10P/N and AN11P/N (XCSIx $x = 0$ and 1) offset and gain specifications                                                         |    |

| 4 <sup>th</sup> order low pass filter (25 kHz, 50 kHz, or 100 kHz) AN10P/N, AN11P/N, specifications                              |    |

| AN11P/N High Gain Amplifier (HGA) specifications                                                                                 |    |

| 4 <sup>th</sup> order low pass filter (25 kHz, 50 kHz, or 100 kHz) AN10P/N, AN11P/N, specifications                              |    |

| DAC Specifications.                                                                                                              |    |

| Analog and digital regulators specifications                                                                                     |    |

| Temperature sensor                                                                                                               |    |

| Power on Reset.                                                                                                                  |    |

| Functional Description                                                                                                           |    |

| Analog Interface                                                                                                                 |    |

| Analog inputs ANx CMPx ( $x = 0$ to 3)                                                                                           |    |

| Analog inputs CMPx $(x = 4 \dots 7)$                                                                                             |    |

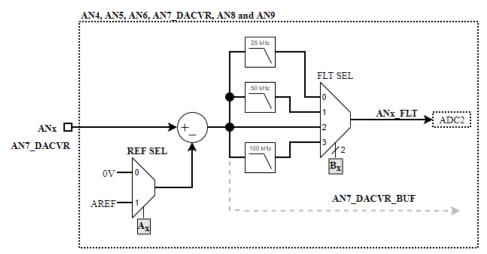

| Analog inputs AN4, AN5, AN6, AN7_DACVR, AN8 and AN9                                                                              |    |

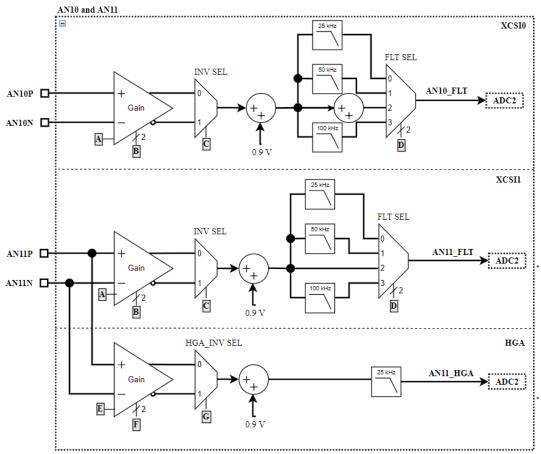

| Analog inputs AN10P/N and AN11P/N                                                                                                |    |

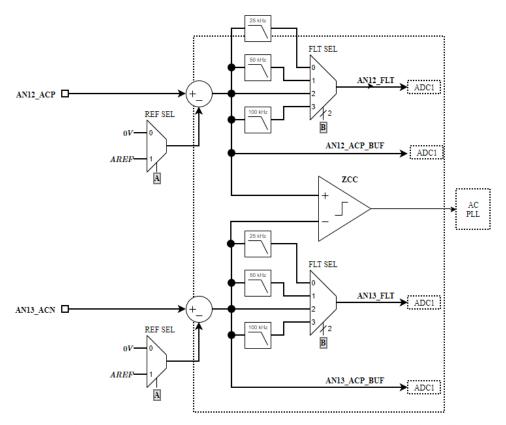

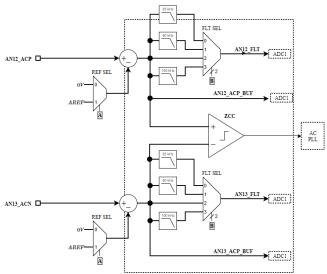

| Analog inputs AN12 ACP and AN13 ACN                                                                                              |    |

| Analog to digital converters ADC0, ADC1 and ADC2                                                                                 |    |

| Analog DACs                                                                                                                      |    |

| Temperature sensor                                                                                                               |    |

| Digital Interface                                                                                                                |    |

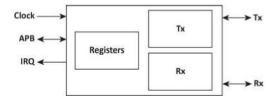

| CPIT                                                                                                                             | 33 |

| Interrupts                                   |     |

|----------------------------------------------|-----|

| ROM and RAM                                  | 35  |

| Memory map                                   | 35  |

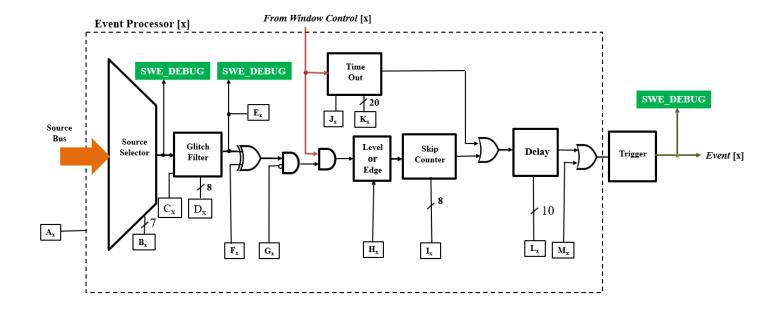

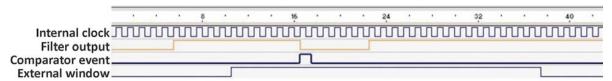

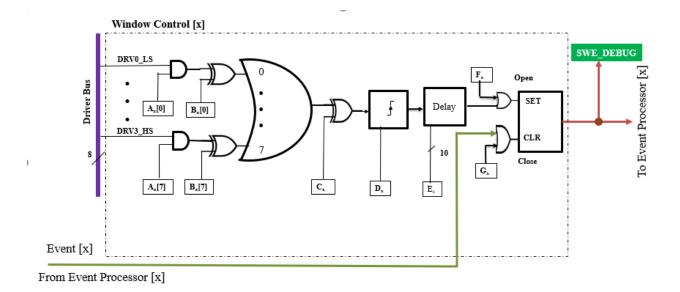

| Switching Engine                             | 36  |

| I/O Block                                    | 57  |

| Timer                                        | 61  |

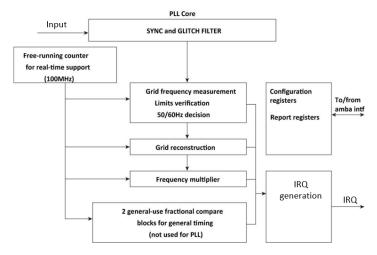

| Grid PLL                                     | 64  |

| Serial Peripheral Interface                  | 73  |

| UART interface                               | 74  |

| I <sup>2</sup> C serial interface            | 77  |

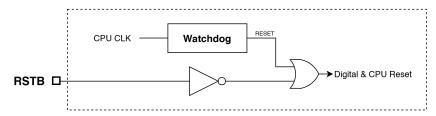

| Watchdog                                     | 78  |

| Math Accelerators Block                      | 79  |

| Timer                                        | 80  |

| Digital DAC                                  | 82  |

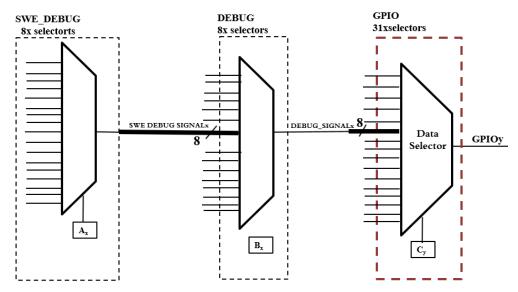

| DEBUG                                        | 83  |

| Applications, Implementation and Layout      | 87  |

| Application                                  | 87  |

| Implementations                              |     |

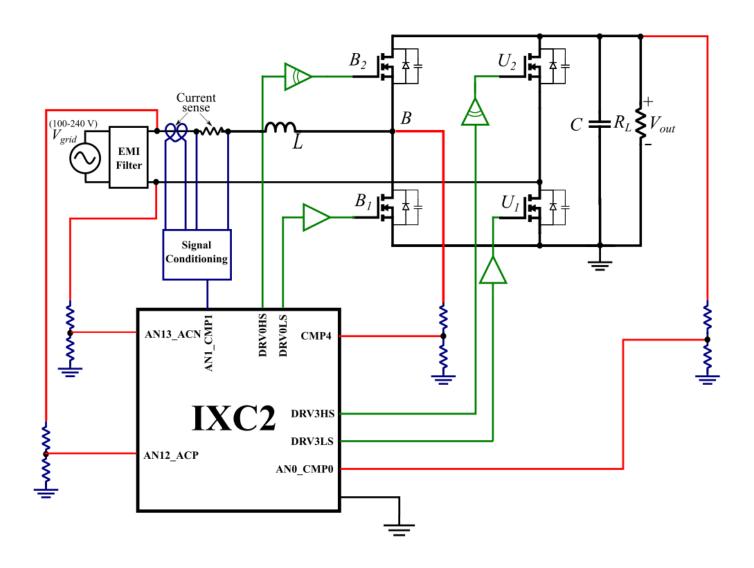

| PFC Architecture based on SA4041             |     |

| LLC Architecture based on SA4041             | 92  |

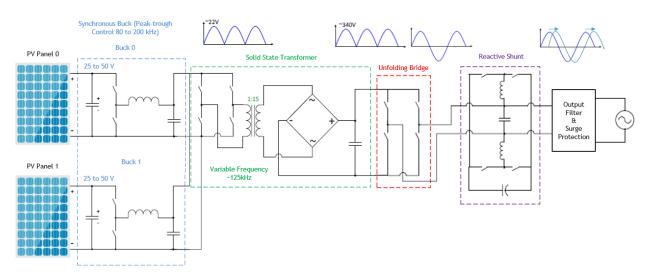

| MI-P700A PV inverter SA4041 based            | 93  |

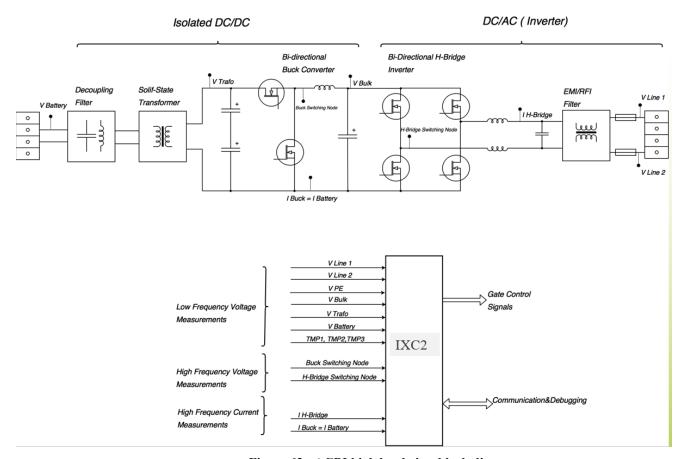

| 1000 W AC battery inverter                   |     |

| SA4041 schematic checklist                   | 96  |

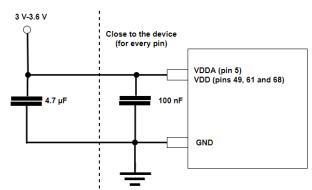

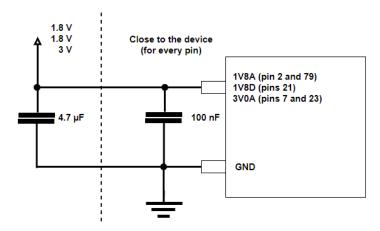

| Power supply connections                     | 96  |

| Regulators connections                       | 97  |

| 0.9 V mid-rail voltage reference connections |     |

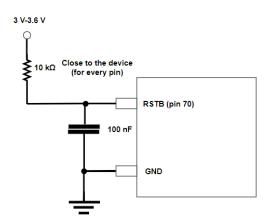

| Reset circuit connections.                   | 97  |

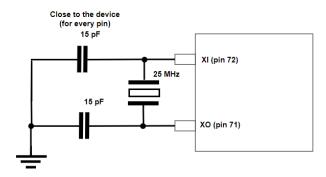

| Crystal oscillator connections               | 98  |

| Unused pins                                  | 98  |

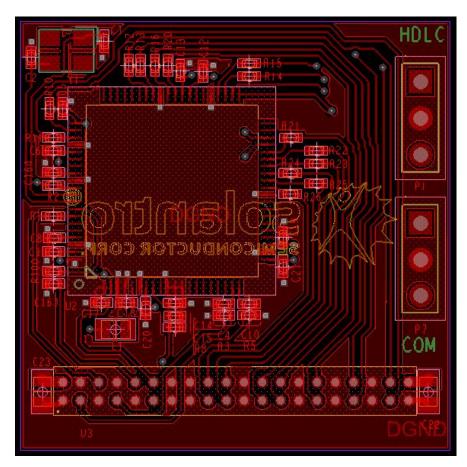

| Layout Example                               | 98  |

| Documentation Support                        | 100 |

| SA4041 Packaging                             | 101 |

| Revision History                             | 104 |

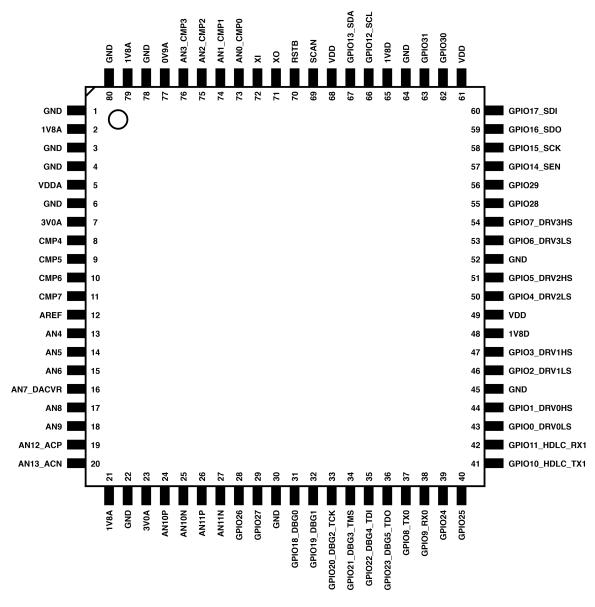

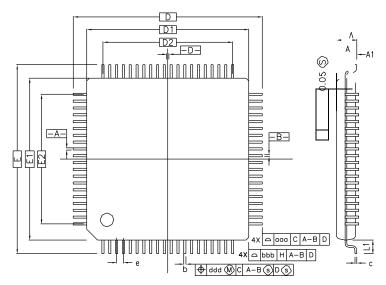

# SA4041 pinout and pin functions

# SA4041 80-LQFP Pinout

Figure 3 - SA4041 80-LQFP Pinout

# Pin descriptions

# **Table 1 - SA4041 Pin functionality**

| Name            | SA4041<br>(80 pin) | Description                                                                                      |

|-----------------|--------------------|--------------------------------------------------------------------------------------------------|

| GND             | 1                  | Analog ground.                                                                                   |

| 1V8A            | 2                  | 1.8 V internally regulated analog supply. External decoupling required.                          |

| GND             | 3                  | Analog ground.                                                                                   |

| GND             | 4                  | Analog ground.                                                                                   |

| VDDA            | 5                  | Analog power supply. External decoupling required.                                               |

| GND             | 6                  | Analog ground.                                                                                   |

| 3V0A            | 7                  | 3.0 V internal analog supply. Connect externally to other 3V0A pins and decouple.                |

| CMP4            | 8                  | Analog dual comparators.                                                                         |

| CMP5            | 9                  | Analog dual comparators.                                                                         |

| CMP6            | 10                 | Analog dual comparators.                                                                         |

| CMP7            | 11                 | Analog dual comparators.                                                                         |

| AREF            | 12                 | Analog reference for pseudo-differential signaling.                                              |

| AN4             | 13                 | Analog input on ADC2.                                                                            |

| AN5             | 14                 | Analog input on ADC2.                                                                            |

| AN6             | 15                 | Analog input on ADC2.                                                                            |

| AN7_DACVR       | 16                 | Analog input on ADC2. Selected DAC voltage references.                                           |

| AN8             | 17                 | Analog input on ADC2.                                                                            |

| AN9             | 18                 | Analog input on ADC2.                                                                            |

| AN12_ACP        | 19                 | Analog input on ADC1. AC PLL input.                                                              |

| AN13_ACN        | 20                 | Analog input on ADC1. AC PLL input.                                                              |

| 1V8A            | 21                 | 1.8 V internally regulated analog supply. External decoupling required.                          |

| GND             | 22                 | Analog ground                                                                                    |

| 3V0A            | 23                 | 3.0 V Power for ADCs. Connect externally to other 3V0A pins and decouple.                        |

| AN10P           | 24                 | Differential analog positive input on ADC2.                                                      |

| AN10N           | 25                 | Differential analog negative input on ADC2.                                                      |

| AN11P           | 26                 | Differential analog positive input on ADC2.                                                      |

| AN11N           | 27                 | Differential analog negative input on ADC2.                                                      |

| GPIO26          | 28                 | GPIO and alternate functions. GPIO input default.                                                |

| GPIO27          | 29                 | GPIO and alternate functions. GPIO input default.                                                |

| GND             | 30                 | Digital ground                                                                                   |

| GPIO18_DBG0     | 31                 | GPIO and alternate functions. Debug Channel 0 default.                                           |

| GPIO19_DBG1     | 32                 | GPIO and alternate functions. Debug Channel 1 default.                                           |

| GPIO20_DBG2_TCK | 33                 | GPIO alternate functions and JTAG. JTAG TCK default. Debug Channel 2 default with JTAG disabled. |

| GPIO21_DBG3_TMS | 34                 | GPIO alternate functions and JTAG. JTAG TMS default. Debug Channel 3 default                     |

| Name            | SA4041<br>(80 pin) | Description                                                                                      |  |  |  |  |  |

|-----------------|--------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                 |                    | with JTAG disabled.                                                                              |  |  |  |  |  |

| GPIO22_DBG4_TDI | 35                 | GPIO alternate functions and JTAG. JTAG TDI default. Debug Channel 4 default with JTAG disabled. |  |  |  |  |  |

| GPIO23_DBG5_TDO | 36                 | GPIO alternate functions and JTAG. JTAG TDO default. Debug Channel 5 default with JTAG disabled. |  |  |  |  |  |

| GPIO8_TX0       | 37                 | GPIO and alternate functions. TX0 Default.                                                       |  |  |  |  |  |

| GPIO9_RX0       | 38                 | GPIO and alternate functions. RX0 Default.                                                       |  |  |  |  |  |

| GPIO24          | 39                 | GPIO and alternate functions. GPIO input default.                                                |  |  |  |  |  |

| GPIO25          | 40                 | GPIO and alternate functions. GPIO input default.                                                |  |  |  |  |  |

| GPIO10_HDLC_TX1 | 41                 | GPIO and alternate functions. TX1 Default. HDLC off by default.                                  |  |  |  |  |  |

| GPIO11_HDLC_RX1 | 42                 | GPIO and alternate functions. RX1 Default. HDLC off by default.                                  |  |  |  |  |  |

| GPIO0_DRV0LS    | 43                 | GPIO, alternate functions and driver control. Driver low output default.                         |  |  |  |  |  |

| GPIO1_DRV0HS    | 44                 | GPIO, alternate functions and driver control. Driver low output default.                         |  |  |  |  |  |

| GND             | 45                 | Digital ground                                                                                   |  |  |  |  |  |

| GPIO2_DRV1LS    | 46                 | GPIO, alternate functions and driver control. Driver low output default.                         |  |  |  |  |  |

| GPIO3 DRV1HS    | 47                 | GPIO, alternate functions and driver control. Driver low output default.                         |  |  |  |  |  |

| 1V8D            | 48                 | 1.8 V internally regulated digital supply. External decoupling required.                         |  |  |  |  |  |

| VDD             | 49                 | Power supply for the digital interface. External decoupling required.                            |  |  |  |  |  |

| GPIO4 DRV2LS    | 50                 | GPIO, alternate functions and driver control. Driver low output default.                         |  |  |  |  |  |

| GPIO5_DRV2HS    | 51                 | GPIO, alternate functions and driver control. Driver low output default.                         |  |  |  |  |  |

| GND             | 52                 | Digital ground                                                                                   |  |  |  |  |  |

| GPIO6 DRV3LS    | 53                 | GPIO, alternate functions and driver control. Driver low output default.                         |  |  |  |  |  |

| GPIO7_DRV3HS    | 54                 | GPIO, alternate functions and driver control. Driver low output default.                         |  |  |  |  |  |

| GPIO28          | 55                 | GPIO and alternate functions. GPIO input default.                                                |  |  |  |  |  |

| GPIO29          | 56                 | GPIO and alternate functions. GPIO input default.                                                |  |  |  |  |  |

| GPIO14_SEN      | 57                 | GPIO and alternate functions. SPI SEN Default.                                                   |  |  |  |  |  |

| GPIO15_SCK      | 58                 | GPIO and alternate functions. SPI SCK Default.                                                   |  |  |  |  |  |

| GPIO16_SDO      | 59                 | GPIO and alternate functions. SPI SDO Default.                                                   |  |  |  |  |  |

| GPIO17_SDI      | 60                 | GPIO and alternate functions. SPI SDI Default.                                                   |  |  |  |  |  |

| VDD             | 61                 | Power supply for the digital interface. External decoupling required.                            |  |  |  |  |  |

| GPIO30          | 62                 | GPIO and alternate functions. GPIO input default.                                                |  |  |  |  |  |

| GPIO31          | 63                 | GPIO and alternate functions. GPIO input default.                                                |  |  |  |  |  |

| GND             | 64                 | Digital ground                                                                                   |  |  |  |  |  |

| 1V8D            | 65                 | 1.8 V internally regulated digital supply. External decoupling required.                         |  |  |  |  |  |

| GPIO12_SCL      | 66                 | GPIO and alternate functions. I2C SCL Default.                                                   |  |  |  |  |  |

| GPIO13_SDA      | 67                 | GPIO and alternate functions. I2C SDA Default.                                                   |  |  |  |  |  |

| VDD             | 68                 | Power supply for the digital interface. External decoupling required.                            |  |  |  |  |  |

| SCAN            | 69                 | Scan test input                                                                                  |  |  |  |  |  |

| Name     | SA4041<br>(80 pin) | Description                                                             |

|----------|--------------------|-------------------------------------------------------------------------|

| RSTB     | 70                 | Bidirectional active low reset. External pull-up resistor to VDD.       |

| XO       | 71                 | Output for external 25 MHz crystal with external loading capacitor.     |

| XI       | 72                 | Input for external 25 MHz crystal with external loading capacitor.      |

| AN0_CMP0 | 73                 | Analog input on ADC0 and dual comparators.                              |

| AN1_CMP1 | 74                 | Analog input on ADC0 and dual comparators.                              |

| AN2_CMP2 | 75                 | Analog input on ADC0 and dual comparators.                              |

| AN3_CMP3 | 76                 | Analog input on ADC0 and dual comparators.                              |

| 0V9A     | 77                 | 0.9 V mid-rail voltage reference. External decoupling required.         |

| GND      | 78                 | Analog ground                                                           |

| 1V8A     | 79                 | 1.8 V internally regulated analog supply. External decoupling required. |

| GND      | 80                 | Analog ground                                                           |

# SA4041 specifications and characteristics

Contact Solantro Semiconductor Corp. for any required specifications or characteristics information.

# Absolute maximum electrical specifications

Table 2 lists the absolute maximum electrical specifications for the SA4041.

Warning! Operating beyond the limits specified in the following table may cause permanent damage to the device. Operating at the limits specified for extended periods may affect device reliability and lifetime.

**Table 2 - SA4041 Absolute Maximum Electrical Specifications**

| Rating                          | Symbol/Pin    | Value        | Units |

|---------------------------------|---------------|--------------|-------|

| Supply voltage                  | VDDA and VDD  | -0.3 to +3.6 | V     |

| Maximum inter-ground potential  | VDD           | -0.3 to +0.3 | V     |

| Low-voltage analog pin voltage  | Vin_LV_analog | -0.3 to VDDA | V     |

| Digital pin voltage             | V_digital     | -0.3 to VDD  | V     |

| Storage temperature range       | T_storage     | - 65 to +150 | °С    |

| ESD immunity (Human body model) | V_ESD         | 4000         | V     |

| Operating temperature           | Та            | -40 to +105  | °С    |

| Junction temperature            | Tj            | -40 to +125  | οС    |

**Note:** Unless otherwise specified, all voltages are with respect to the voltage at the GND. VD) return pins.

Operating ratings are conditions under which operation of the device is specified. For specific operating limits and associated test conditions, see the electrical characteristics.

## **Electrical characteristics**

The following tables list the characterization parameters for the SA4041.

## Supply voltages and power consumption

| Parameter                          | Symbol       | Min | Тур | Max | Unit | Conditions        |

|------------------------------------|--------------|-----|-----|-----|------|-------------------|

| Supply voltage                     | VDDA         | 3   | 3.3 | 3.5 | V    |                   |

| Supply voltage                     | VDD          | 2.7 | 3.3 | 3.5 | V    |                   |

| Internally regulated voltage       | VD3A         |     | 3.0 |     | V    | VDDA > 3.2V       |

| Internally regulated voltage       | V1P8A, V1P8D |     | 1.8 |     | V    | VDDA, VDD > 2.7V  |

| Power consumption (operating mode) | Pw_opmode    |     |     | 300 | mW   | VDDA, VDD = 3.3V  |

| Power consumption (low power mode) | Pw_lpmode    |     |     | 10  | mW   | VDDA, VDD = 3.3 V |

# $ANx\_CMPx$ (x = 0 to 3) specifications

| Parameter                               | Minimum | Typical | Maximum | Unit | Conditions                                              |

|-----------------------------------------|---------|---------|---------|------|---------------------------------------------------------|

| Input signal range at ANx_CMPx pins     | 0       |         | 1.8     | V    |                                                         |

| DAC Full scale output range (absolute)  |         |         | 1.8     | V    | Absolute                                                |

| DAC full scale absolute accuracy        |         |         | 0.25    | %    |                                                         |

| DAC resolution                          | 10      |         |         | bits |                                                         |

| Channel matching (POS and NEG levels)   |         |         | 1       | %    | Between separate channels                               |

| Channel matching (over/under levels)    |         |         | 10      | %    | Between separate channels                               |

| Full scale (ADC) signal window          | 0       |         | 1.8     | V    |                                                         |

| Full scale (ADC) signal window accuracy |         |         | 0.2     | %    | Meter specification driven (ANSI spec of 0.2% and 0.5%) |

| ADC resolution                          | 10      |         |         | bits |                                                         |

| ADC effective sampling rate             | 0.06    |         | 1       | MHz  |                                                         |

# ANx\_CMPx (x = 0 t0 3) Variable Gain Amplifier (VGA) Gain 1, 2, 4, and 8

| Parameter        | Min   | Тур  | Max  | Units  | Conditions   |

|------------------|-------|------|------|--------|--------------|

| VGA_GAIN=1       | 0.96  | 1    | 1.01 | V/V    | 25 °C        |

| VGA DRIFT GAIN=1 | -44   | -20  | 4    | ppm/°C | -40 - 125 °C |

| OFFSET           | -12   | 4    | 22   | mV     | 25 °C        |

| OFFSET_ DRIFT    | -16.5 | 20.2 | 56.9 | uV/°C  | -40 - 125 °C |

| VGA_ GAIN=2      | 1.92  | 2    | 2.03 | V/V    | 25 °C        |

| VGA_DRIFT_GAIN=2 | -133  | -59  | 16   | ppm/°C | -40 - 125 °C |

| OFFSET           | -10   | 3    | 19   | mV     | 25 °C        |

| OFFSET_ DRIFT    | -0.2  | 0.1  | 0.4  | uV/°C  | -40 - 125 °C |

| VGA_GAIN=4       | 3.86  | 4    | 4.06 | V/V    | 25 °C        |

| VGA_DRIFT_GAIN=4 | -295  | -140 | 15   | ppm/°C | -40 - 125 °C |

| OFFSET           | -11   | 3    | 18   | mV     | 25 °C        |

| OFFSET_ DRIFT    | -33.2 | 15.8 | 64.7 | uV/°C  | -40 - 125 °C |

| VGA GAIN=8       | 7.7   | 8    | 8.12 | V/V    | 25 °C        |

| VGA DRIFT GAIN=8 | -622  | -312 | -2   | ppm/°C | -40 - 125 °C |

| OFFSET           | -11   | 3    | 18   | mV     | 25 °C        |

| OFFSET_DRIFT     | -33.8 | 15.7 | 65.2 | uV/°C  | -40 - 125 °C |

# $ANx\_CMPx$ (x = 0 t0 3) 4<sup>th</sup> order low pass filter (25 kHz, 50 kHz, or 100 kHz) specifications

| Parameter           | Min   | Тур | Max   | Units | Conditions    |

|---------------------|-------|-----|-------|-------|---------------|

| LPF_100kHz_BW       | 75    | 100 | 125   | kHz   | 25 °C         |

| LPF_100kHz_BW-Drift | 75    | 111 | 148   | Hz/°C | -40 to 125 °C |

| LPF_50kHz_BW        | 37.5  | 50  | 60.5  | kHz   | 25 °C         |

| LPF_50kHz_BW-Drift  | 39    | 57  | 75    | Hz/°C | -40 to 125 °C |

| LPF_25kHz_BW        | 18.75 | 25  | 31.25 | kHz   | 25 °C         |

| LPF_25Hz_BW-Drift   | 19    | 29  | 40    | Hz/°C | -40 to 125 °C |

# AN4, AN5, AN6, AN7\_DACVR, AN8 and AN9 specifications

| Parameter                               | Minimum | Typical | Maximum | Unit | Conditions                                               |

|-----------------------------------------|---------|---------|---------|------|----------------------------------------------------------|

| Input signal range at the pin           | 0       |         | 1.8     | V    |                                                          |

| Full scale (ADC) signal window          | 0       |         | 1.8     | V    |                                                          |

| Full scale (ADC) signal window accuracy |         |         | 0.2     | %    | Meter specification driven (ANSI spec of 0.2% and 0.5%)) |

| ADC resolution                          | 10      |         |         | bits |                                                          |

| ADC effective sampling rate             | 0.06    |         | 1       | MHz  |                                                          |

| Internal OSR noise reduction            | 12      |         |         | bits | In 5 kHz bandwidth                                       |

|                                         | 16      |         |         | bits | In 60 Hz bandwidth (used for DC offset cancellation)     |

# Subtractor (SUB) for AN4, AN5, AN6, AN7\_DACVR, AN8, AN9, AN12\_ACP and AN13\_ACN specifications

| Parameter        | Min   | Тур    | Max  | Units | Conditions    |

|------------------|-------|--------|------|-------|---------------|

| SUBx_GAIN        | 0.85  | 1      | 1.13 | V/V   | 25 °C         |

| SUBx_GAIN_ DRIFT | -0.51 | -0.005 | 0.50 | %/°C  | -40 to 125 °C |

| OFFSET           | -13   | 2      | 17   | mV    | 25 °C         |

| OFFSET_DRIFT     | -5.97 | -0.31  | 5.36 | mV/°C | -40 - 125 °C  |

# Subtractor (SUB) and low pass filter (LPF) for AN4, AN5, AN6, AN7\_DACVR, AN8, AN9, AN12\_ACP and AN13 ACN specifications

| Parameter             | Min   | Тур   | Max   | Units | Conditions    |

|-----------------------|-------|-------|-------|-------|---------------|

| SUBx+LPFx_GAIN        | 0.988 | 0.993 | 0.996 | V/V   | 25 °C         |

| SUBx+LPFx_GAIN_ DRIFT | -0.4  | -0.09 | 0.02  | %/°C  | -40 to 125 °C |

| OFFSET                | -16.4 | 6.5   | 31.5  | mV    | 25 °C         |

| OFFSET_ DRIFT         | -4.05 | -0.91 | 2.2   | mV/°C | -40 to 125 °C |

# $4^{th}$ order low pass filter (25 kHz, 50 kHz, or 100 kHz) for AN4, AN5, AN6, AN7\_DACVR, AN8, AN9, AN12\_ACP and AN13\_ACN specifications

| Parameter           | Min   | Тур | Max   | Units | Conditions    |

|---------------------|-------|-----|-------|-------|---------------|

| LPF_100kHz_BW       | 75    | 100 | 125   | kHz   | 25 °C         |

| LPF_100kHz_BW-Drift | 75    | 111 | 148   | Hz/°C | -40 to 125 °C |

| LPF_50kHz_BW        | 37.5  | 50  | 60.5  | kHz   | 25 °C         |

| LPF_50kHz_BW-Drift  | 39    | 57  | 75    | Hz/°C | -40 to 125 °C |

| LPF_25kHz_BW        | 18.75 | 25  | 31.25 | kHz   | 25 °C         |

| LPF_25Hz_BW-Drift   | 19    | 29  | 40    | Hz/°C | -40 to 125 °C |

# AN10P/N and AN11P/N (XCSIx x = 0 and 1) specifications

| Parameter                         | Minimum | Typical | Maximum | Unit | Conditions                                       |

|-----------------------------------|---------|---------|---------|------|--------------------------------------------------|

| Input signal range at AN10P/N and | -0.04   | 1.2     | 3       | V    | Absolute range                                   |

| AN11P/N                           |         |         |         |      |                                                  |

| Channel matching                  |         |         |         |      | Maintained by 0.2% absolute accuracy requirement |

# AN10P/N and AN11P/N (XCSIx x = 0 and 1) offset and gain specifications

| Parameter                  | Minimum | Typical | Maximum | Units  | Conditions    |

|----------------------------|---------|---------|---------|--------|---------------|

| XCSIx Gain=0.45 CM         | 0.898   | 0.912   | 0.927   | V      | 25 °C         |

| XCSIx Gain=0.45_CM_Drift   | -51     | 15      | 82      | uV/°C  | -40 to 125 °C |

| XCSIx Gain=0.45_Gain       | 0.416   | 0.45    | 0.46    | V/V    | 25 °C         |

| XCSIx Gain=0.45_Gain_Drift | -64.4   | -1      | 62.5    | ppm/°C | -40 to 125 °C |

| XCSIx Gain=0.40 CM         | 0.873   | 0.905   | 0.938   | V      | 25 °C         |

| XCSIx Gain=0.40_CM_Drift   | -54     | 15      | 85      | uV/°C  | -40 to 125 °C |

| XCSIx Gain=0.40_Gain       | 0.38    | 0.40    | 0.42    | V/V    | 25 °C         |

| XCSIx Gain=0.40_Gain_Drift | -108.8  | -50     | 8.82    | ppm/°C | -40 to 125 °C |

| XCSIx Gain=0.30_CM         | 0.887   | 0.911   | 0.935   | V      | 25 °C         |

| XCSIx Gain=0.30_CM_Drift   | -55     | 19      | 93      | uV/°C  | -40 to 125 °C |

| XCSIx Gain=0.30_Gain       | 0.29    | 0.3     | 0.33    | V/V    | 25 °C         |

| XCSIx Gain=0.30_Gain_Drift | -65.9   | -51     | -35.86  | ppm/°C | -40 to 125 °C |

# 4<sup>th</sup> order low pass filter (25 kHz, 50 kHz, or 100 kHz) AN10P/N, AN11P/N, specifications

| Parameter           | Min   | Тур | Max   | Units | Conditions    |

|---------------------|-------|-----|-------|-------|---------------|

| LPF_100kHz_BW       | 75    | 100 | 125   | kHz   | 25 °C         |

| LPF_100kHz_BW-Drift | 75    | 111 | 148   | Hz/°C | -40 to 125 °C |

| LPF_50kHz_BW        | 37.5  | 50  | 60.5  | kHz   | 25 °C         |

| LPF_50kHz_BW-Drift  | 39    | 57  | 75    | Hz/°C | -40 to 125 °C |

| LPF_25kHz_BW        | 18.75 | 25  | 31.25 | kHz   | 25 °C         |

| LPF_25Hz_BW-Drift   | 19    | 29  | 40    | Hz/°C | -40 to 125 °C |

#### AN11P/N High Gain Amplifier (HGA) specifications

| The triangle of triangle of the triangle of tr |         |         |         |        |               |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|--------|---------------|--|--|--|--|

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Minimum | Typical | Maximum | Units  | Conditions    |  |  |  |  |

| HGA Gain =120_CM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | 0.93    |         | V      | 25 °C         |  |  |  |  |

| HGA Gain =120 CM Drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | 0.09    |         | uV/°C  | -40 to 125 °C |  |  |  |  |

| HGA Gain = 120_Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | 116     |         | V/V    | 25 °C         |  |  |  |  |

| HGA Gain =120_Gain_Drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | 0.19    |         | ppm/°C | -40 to 125 °C |  |  |  |  |

| HGA Gain =60_CM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | 0.93    |         | V      | 25 °C         |  |  |  |  |

| HGA Gain =60_Offset_Drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         | -0.2    |         | uV/°C  | -40 to 125 °C |  |  |  |  |

| HGA Gain =60_Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | 63      |         | V/V    | 25 °C         |  |  |  |  |

| HGA Gain =60_Gain_Drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         | 8.5     |         | ppm/°C | -40 to 125 °C |  |  |  |  |

| HGA Gain =30_CM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | 0.9     |         | V      | 25 °C         |  |  |  |  |

| HGA Gain =30 CM Drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | 5.6     |         | mV/°C  | -40 to 125 °C |  |  |  |  |

| HGA Gain= 30_Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | 32      |         | V/V    | 25 °C         |  |  |  |  |

| HGA Gain =30_Gain_Drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         | -0.09   |         | %/°C   | -40 to 125 °C |  |  |  |  |

# 4<sup>th</sup> order low pass filter (25 kHz, 50 kHz, or 100 kHz) AN10P/N, AN11P/N, specifications

| Parameter             | Min   | Тур | Max   | Units | Conditions     |

|-----------------------|-------|-----|-------|-------|----------------|

| HGA_LPF_25kHz_BW      | 18.75 | 25  | 31.25 | kHz   | 25 °C          |

| HGA_LPF_25Hz_BW-Drift | 19    | 29  | 40    | Hz/°C | - 40 to 125 °C |

# **DAC Specifications**

| Parameter                                | Minimum | Typical | Maximum | Unit  | Conditions                                            |

|------------------------------------------|---------|---------|---------|-------|-------------------------------------------------------|

| Input signal range                       | 0       |         | 1.8     | V     | Referenced to local ground or to separate AREF signal |

| DAC (reference level setting) range      | 0       |         | 1.8     | V     |                                                       |

| DAC full scale accuracy (absolute)       |         |         | 1.0     | %     |                                                       |

| DAC (reference level setting) resolution | 10      |         |         | bits  |                                                       |

| DAC (reference) update rate              | 0       |         | 1       | MHz   |                                                       |

| dv/dt full scale detection range         | 1       |         | 1000    | mV/μs |                                                       |

| dv/dt range accuracy                     | -20     |         | 20      | %     |                                                       |

| dv/dt range resolution                   |         |         | 1024    | steps |                                                       |

| dv/dt threshold update rate              | 0       |         | 1       | MHz   |                                                       |

# Analog and digital regulators specifications

| Parameter                                    | Min   | Тур   | Max    | Unit | Conditions             |

|----------------------------------------------|-------|-------|--------|------|------------------------|

|                                              |       |       |        | S    |                        |

| Digital_1.8V_Linear_Regulator_output_voltage | 1.789 | 1.809 | 1.829  | V    | 25 °C, VDDA=VDD =3.3 V |

| Digital_1.8V_Linear_Regulator_output_voltage |       |       |        |      |                        |

| set to 1.7V                                  | 1.693 | 1.711 | 1.730  | V    | 25 °C, VDDA=VDD =3.3V  |

| Analog_1.8V_Linear_Regulator_output_voltage  | 1.796 | 1.821 | 1.845  | V    | 25 °C, VDDA=VDD =3.3 V |

| Analog_3V_Linear_Regulator_output_voltage    | 2.970 | 3.013 | 3.057  | V    | 25 °C, VDDA=VDD =3.3V  |

| ADCCM output voltage                         | 0.896 | 0.909 | 0.9220 | V    | 25 °C, VDDA=VDD =3.3V  |

| Analog_Core_Current_Consumption              | 35.3  | 35.2  | 37.2   | mA   | 25 °C, VDDA=VDD =3.3V  |

| Digital_Core_Current_Consumption             | 60.2  | 63.9  | 65.6   | mA   | 25 °C, VDDA=VDD =3.3 V |

| Total Supply Current Consumption             | 95.5  | 99.1  | 102.8  | mA   | 25 °C, VDDA=VDD =3.3 V |

# **Temperature sensor**

| Parameter                     | Min | Тур | Max | Unit |

|-------------------------------|-----|-----|-----|------|

| Range                         | -40 |     | 125 | °C   |

| Resolution                    | -5  |     | 5   | °C   |

| Over-temperature detect level | 125 | 100 | 145 | °C   |

| Parameter                          | Min   | Тур   | Max   | Unit | Conditions                    |

|------------------------------------|-------|-------|-------|------|-------------------------------|

|                                    |       |       |       | S    |                               |

| Temperature_Sensor_ output_voltage | 0.937 | 1.156 | 1.748 | V    | 25 °C, VDDA=VDD =3.3 V        |

| Temperature_Sensor_Slop            | 3.605 | 3.624 | 3.643 | mV   | -40 to 125 °C, VDDA=VDD =3.3V |

## **Power on Reset**

| Parameter | Min  | Тур | Max  | Unit | Conditions                                                     |

|-----------|------|-----|------|------|----------------------------------------------------------------|

| Vth0      |      |     | 1.4  | V    | Threshold below which the power on reset circuit is not active |

| Vth1      | 2.62 |     | 2.67 | V    | Threshold at which V <sub>CC</sub> is declared "valid"         |

| Vth2    | 2.54 | 2.61 | V  | Threshold at which V <sub>CC</sub> is declared "lost" |

|---------|------|------|----|-------------------------------------------------------|

| T_Reset |      | 200  | ms |                                                       |

# **Functional Description**

The SA4041 is a mixed-signal integrated circuit optimized for power conversion using digital control methods. The analog inputs can create timing events using high speed comparators while monitoring voltages and currents using three independent ADCs. The digital peripherals of which the Switching Engine is the heart can drive the gate signals of complex power applications. The functional diagram, in Figure 1, gives an overview of the SA4041. The 32-bit RISC core oversees the configuration and monitoring of the peripherals while implementing control algorithms and state machines not possible in purely analog circuits.

# **Analog Interface**

The SA4041 is a highly integrated IC with rich power control-centric analog features:

- 18 analog input pins

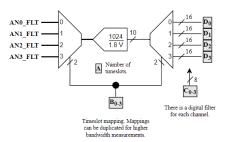

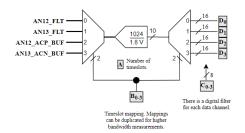

- 1 sixteen-channel, 10-bit, 1.4 MS/s ADC with digital filters

- 2 four-channel, 10-bit, 1.4 MS/s ADCs with digital filters

- 17 10 ns fast comparators for event generation and fault detection

- 16 10-bit analog DACs for comparators internal references

- 1 10-bit analog DAC for debagging

- 4 6-bit analog DACs for level shifting

- 2 differential high-speed current sensing amplifier interfaces

- 1 differential high gain amplifier

- 14 programmable 4<sup>th</sup> order anti-alias low-pass filters

- 1 25 kHz low pass filter

- Internal temperature sensor

All comparator outputs are connected to the Event Bus, whereas all ADCs and DACs are connected to the AMBA bus. SA4041 has 18 analog inputs that can be used for sensing the controls signal for different power applications.

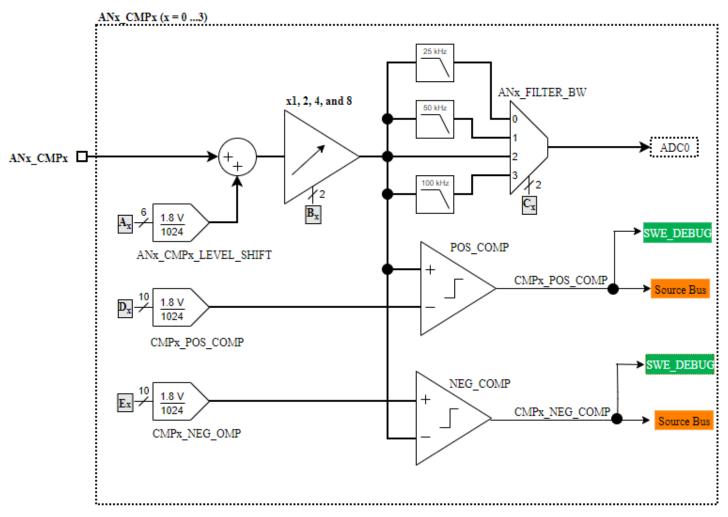

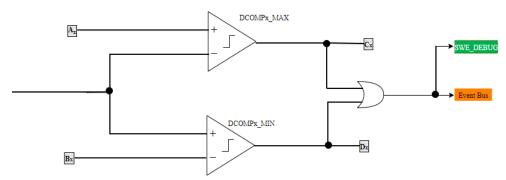

# Analog inputs $ANx\_CMPx$ (x = 0 to 3)

These are dual-function analog inputs feeding ADC0 and two high speed comparators as shown in Figure 4. The level shift and gain stage allows small signals to be scaled to the 0 - 1.8V input range of both the ADC0 and comparators. The shifting is done by the level shift DAC. The amplifier has four gains: 1, 2, 4 or 8. To reduce the impact of the switching ripple common for the power supply signals, the ADC0 input can be optionally filtered by a 4<sup>th</sup> order low pass filter 25 kHz, 50 kHz, 100 kHz or by passed.

For performing hysteretic current or voltage control or fault detection, the amplified signal is also sent to the dual comparator block. The block has two comparators. Each comparator has its own DAC reference which can be set or controlled through software to implement a dynamic behavior and advanced control methods. The comparators' outputs are sent to the Source Bus and to SWE DEBUG.

Figure 4 - Blocks associated with analog inputs ANx CMPx (x = 0...3)

The IC\_CONFIG registers are used to setup the input signal gain and bandwidth as well as the comparator hysteresis ( $\mathbf{x} = 0$  to 3).

|         | PERIPHERAL.FIELD_NAME                   | Default |

|---------|-----------------------------------------|---------|

| $B_x$   | IC_CONFIG->ANx_CMPx_GAINU2 <sup>1</sup> | 00b     |

| $C_{x}$ | IC_CONFIG->ANx_FILTER_BWU2 <sup>2</sup> | 00b     |

<sup>&</sup>lt;sup>1</sup>Amplifier gains:  $00b = \times 1$ ,  $01\overline{b} = \times 2$ ,  $10b = \times 4$ , and  $11b = \times 8$ .

The DAC registers provide the level shifting of the input voltage and comparator references (x=0 to 3).

|         | PERIPHERAL.FIELD_NAME              | Default |

|---------|------------------------------------|---------|

| $A_{x}$ | ANALOG_DAC->ANx_CMPX_LEVEL_SHIFTU6 | 0       |

| $D_x$   | ANALOG_DAC->CMPx_POS_COMPU10       | 0       |

| $E_{x}$ | ANALOG_DAC->CMPx_NEG_COMPU10       | 0       |

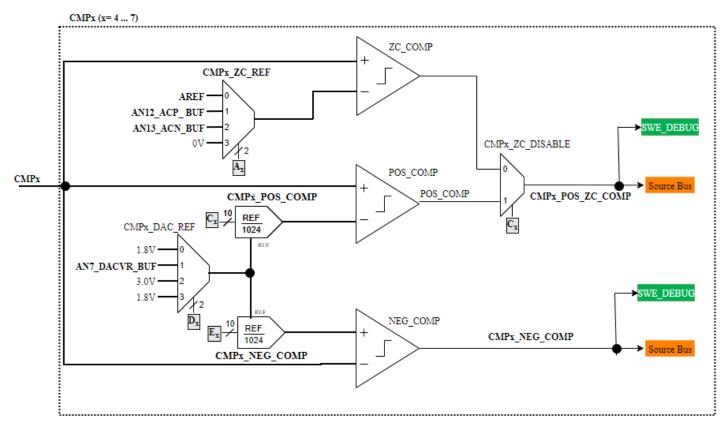

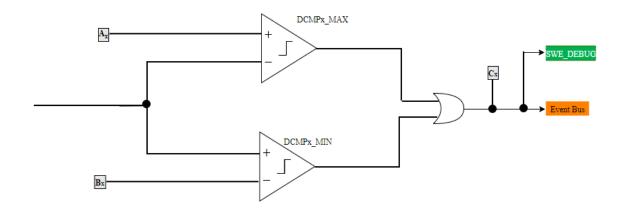

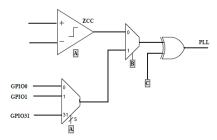

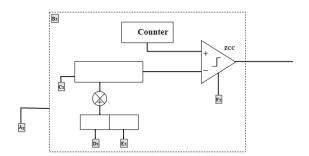

## Analog inputs CMPx (x = 4 ... 7)

These analog inputs are connected to three high speed comparators as shown in Figure 5. The comparators can create events for controlling the event driven timers that are switching the powertrain switches.

For performing hysteretic charge control or dead time optimization, the input signal is sent to two comparators POS\_COMP and NEG\_COMP. The references to the comparators are set by their corresponding DACs. To implement the dynamic behavior and perform advanced control methods, the comparators' references can be set or controlled through the software. The DACs range can be chosen to be 1.8 V, 3V or AN7\_DACVR\_BUF. The CMPx block has also a zero-crossing comparator, ZC\_COMP that compares the input signal with signals applied to AREF pin, AN12 BUF, AN13 BUF or 0 V.

The comparator output CMPx \_NEG\_COMP is sent to the Source Bus while only one output of the comparators POS\_COMP and ZC\_COMP is selected to the Source Bus and SWE\_DEBUG. By default, the comparator POS\_COMP is selected to the Source Bus and SWE\_DEBUG.

<sup>&</sup>lt;sup>2</sup>Low pass filter bandwidth settings: 00b = 25 kHz, 01b = 50 kHz, 10b = bypass, and 11b = 100 kHz

Figure 5- Blocks associated with analog inputs CMPx (x=4...7)

The control of the blocks is done by the CMPx registers fields.

|         | PERIPHERAL.FIELD_NAME                     | Default |

|---------|-------------------------------------------|---------|

| $A_{x}$ | IC_CONFIG-> CMPx_ZC_REFU2 <sup>1</sup>    | 00b     |

| $B_x$   | IC_CONFIG->CMPx_ZC_DESABLEU2 <sup>2</sup> | 01b     |

| $D_{x}$ | IC_CONFIG->CMPx_DAC_REFU2 <sup>3</sup>    | 01b     |

<sup>&</sup>lt;sup>1</sup>ZC comparator reference: 00b = AREF, 01b = AN12\_BUF, 10b = AN13\_BUF, and 11b = 0 V.

The DACs in the CMPx blocks are set by the following fields:

|   |         | PERIPHERAL.FIELD_NAME         | Default |

|---|---------|-------------------------------|---------|

|   | $C_{x}$ | ANALOG_DAC-> CMPx_POS_COMPU10 | 540     |

| ĺ | $E_{x}$ | ANALOG_DAC-> CMPx_NEG_COMPU10 | 540     |

<sup>&</sup>lt;sup>2</sup>Enabls the ZC comparator output to be connected to Source Bus. 0b = ZC comparator, 1b = POS comparator.

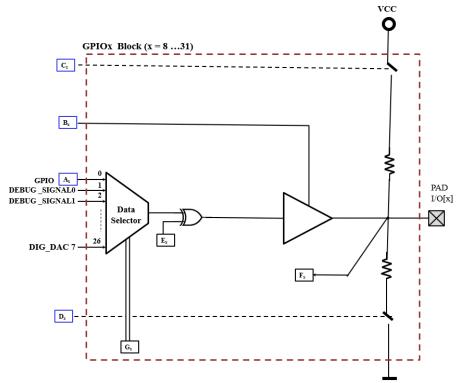

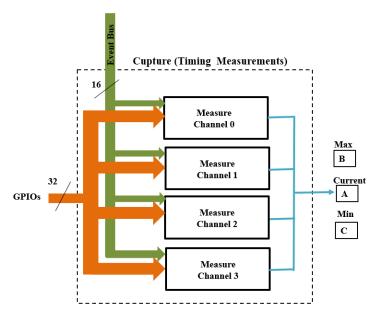

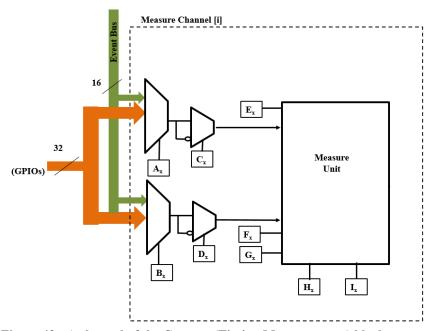

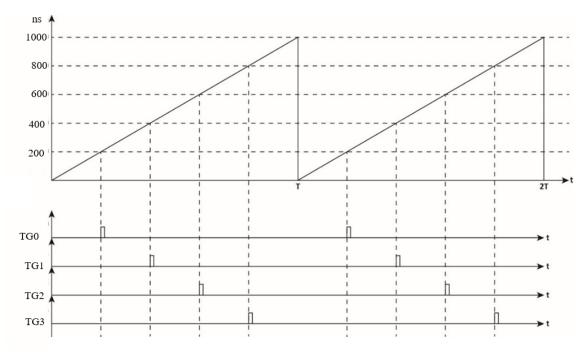

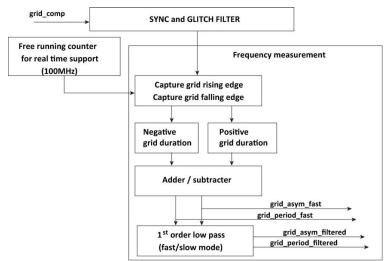

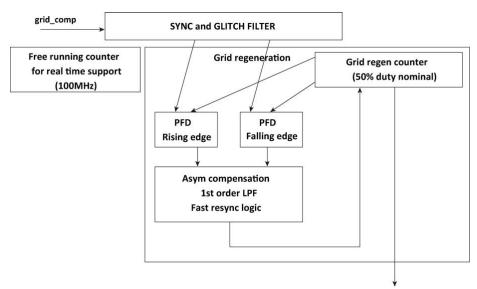

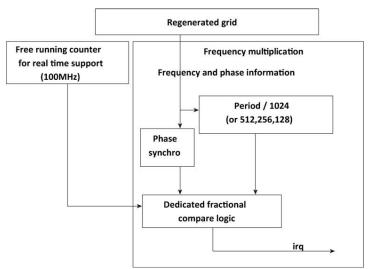

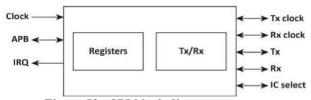

<sup>&</sup>lt;sup>3</sup> DACs' references: 00b = 1.8 V; 01b = AN7\_DACVR\_BUF; 10b = 3 V, and 11b = 1.8 V.