# 2A EcoSpeed™ Synchronous Step-Down Regulator with Optional Ultrasonic Power Save

### **POWER MANAGEMENT**

#### **Features**

- V<sub>IN</sub>: 3V to 5.5V

- $V_{OUT}$ : 0.75V to 95% x  $V_{IN}$

- I<sub>OUT</sub>: Up to 2A

- Low R<sub>DS(ON)</sub> Switches

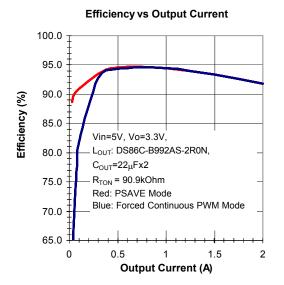

Up to 95% Peak Efficiency

- High Output Accuracy

- Small Ceramic Capacitors

- Power Good Pin (Open-Drain)

- Patented Adaptive On-Time Control:

Excellent Transient Response

Programmable Pseudo-fixed Frequency

■ Fault Protection Features:

Cycle-by-Cycle Current Limit

Short Circuit Protection

Over and Under Output Voltage Protection

Over-Temperature

- Internal Soft start

- Ultrasonic Power Save

- Smart Power Save

- Ultra-Small Lead-Free 3x3mm, 10-Pin MLPD Package

- Fully WEEE and RoHS Compliant

## **Applications**

- Networking Equipment, Embedded Systems

- Medical Equipment, Office Automation

- Instrumentation, Portable Systems

- Consumer Devices (DTV, Set-top Box, ...)

- 5V POL Converters

### **Description**

The SC172 is an integrated, synchronous 2A EcoSpeed<sup>TM</sup> step-down regulator, which incorporates Semtech's advanced, patented adaptive on-time architecture to achieve best-in-class performance in dynamic point-of-load applications. The input voltage range is 3V to 5.5V with a programmable output voltage from 0.75V up to 95% x  $V_{IN}$ . The device features low- $R_{DS(ON)}$  internal switches and optional PSAVE mode for high efficiency across the output load range.

Adaptive on-time control provides programmable pseudo-fixed frequency operation and excellent transient performance. The switching frequency can be set from 200kHz to 1MHz - allowing the designer to reduce external LC filtering and minimize light load (standby) losses. Disabling PSAVE operation reduces output voltage ripple at light load for ceramic output capacitors.

Additional features include cycle-by-cycle current limit, soft start, input UVLO and output OV protection, and over temperature protection. The open-drain PGOOD pin provides output status. Standby current is less than 10µA when disabled.

The device is available in a low profile, thermally enhanced MLPD-3x3mm 10-pin package.

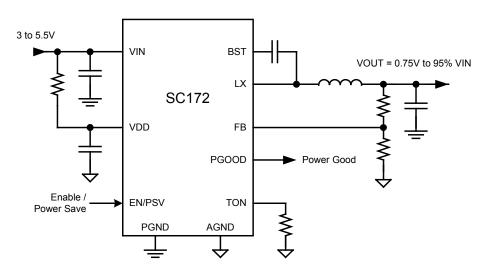

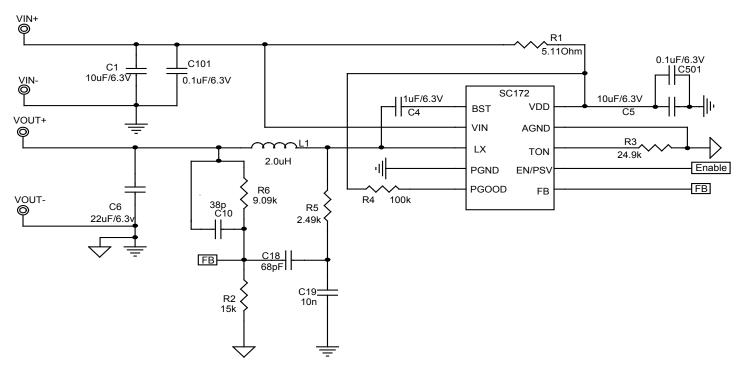

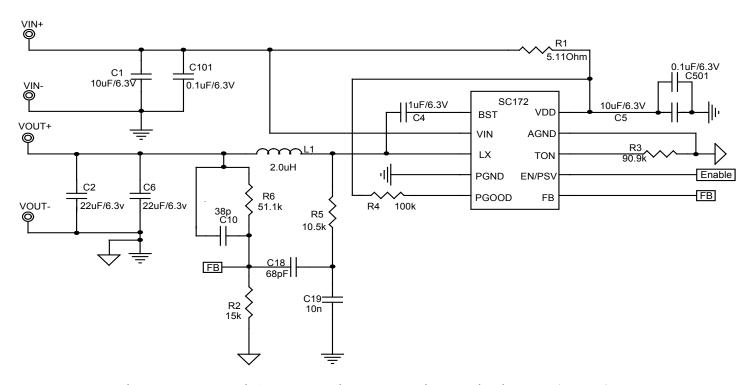

## **Typical Application Circuit**

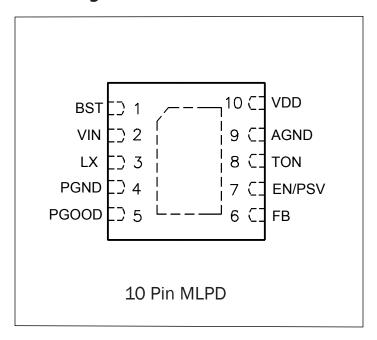

## **Pin Configuration**

$\theta_{JA} = 40 \,^{\circ} \, \text{C/W}.$

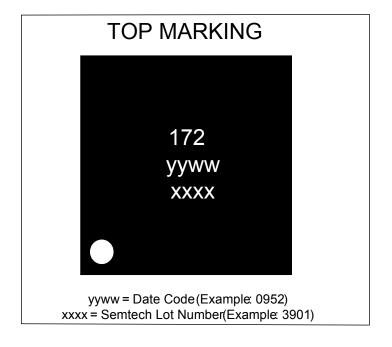

## **Marking Information**

## **Ordering Information**

| Device                    | Top Mark         | Package <sup>(2)</sup> |  |  |

|---------------------------|------------------|------------------------|--|--|

| SC172MLTRT <sup>(1)</sup> | 172              | MLPD-10 3x3            |  |  |

| SC172EVB                  | Evaluation Board |                        |  |  |

#### Notes:

- 1) Available in tape and reel packaging only. A reel contains 3000 devices.

- 2) Available in lead-free packaging only. WEEE compliant and Halogen free. This component and all homogenous sub-components are RoHS compliant.

## **Absolute Maximum Ratings**

| LX to GND <sup>(3)</sup>    | - 0.3(DC) to +6.0V(DC) Max |

|-----------------------------|----------------------------|

| VIN to PGND, EN/PSV to AGND | 0.3 to +6.0V               |

| VIN to VDD                  | +0.3V                      |

| BST to LX                   | 0.3 to +6.0V               |

| BST to PGND                 | -0.3 to +12V               |

| VDD to AGND, VOUT to AGND   | -0.3V to +6.0V             |

| FB, PGOOD, TON              | 0.3 to VDD + 0.3V          |

| AGND to PGND                | -0.3 to +0.3V              |

| Peak IR Reflow Temperature  | 260°C                      |

| ESD Protection Level (2)    | 2kV                        |

### **Recommended Operating Conditions**

| Supply Input Voltage              | 3V to 5.5V |

|-----------------------------------|------------|

| Maximum Continuous Output Current | 2A         |

### **Thermal Information**

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

#### NOTES-

- (1) Calculated from package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

- (2) Tested according to JEDEC standard JESD22-A114-B

- (3) Due to parasitic board inductance, the transient LX pin voltage at the point of measurement may appear larger than that which exists on silicon. The device is designed to tolerate the short duration transient voltages that will appear on the LX pin due to the deadtime diode conduction, for inductor currents up to the current limit setting of the device. See application section for details.

### **Electrical Characteristics**

Unless specified:  $V_{IN} = 5V$ ,  $T_{\Delta} = +25$ °C for Typ, -40°C to +85°C for Min and Max,  $T_{I} < 125$ °C

| Parameter                   | Symbol | Conditions                                                                             | Min    | Тур  | Max    | Units |  |

|-----------------------------|--------|----------------------------------------------------------------------------------------|--------|------|--------|-------|--|

| Input Supplies              |        |                                                                                        |        |      |        |       |  |

| VIN, VDD Input Voltage      |        |                                                                                        | 3      |      | 5.5    | V     |  |

| VDD UVLO Threshold          |        | Rising UVLO V <sub>TH</sub>                                                            | 2.75   | 2.85 | 2.98   | V     |  |

| VDD UVLO Hysteresis         |        |                                                                                        | 100    | 200  |        | mV    |  |

|                             |        | EN/PSV= 0V                                                                             |        | 5    | 15     | μΑ    |  |

| VIN, VDD Supply Current     |        | I <sub>OUT</sub> =0A, PSAVE, f <sub>SW</sub> =25kHz <sup>(1)</sup>                     |        | 744  |        |       |  |

|                             |        | Forced Continuous Conduction Mode<br>EN floating, I <sub>our</sub> =0A , Not Switching |        | 1000 |        |       |  |

| Controller                  |        |                                                                                        |        |      |        |       |  |

| FB On-Time Threshold        |        |                                                                                        | 0.7425 | 0.75 | 0.7575 | V     |  |

| Frequency Programming Range |        | See R <sub>TON</sub> Calculation                                                       | 200    |      | 1000   | kHz   |  |

| FB Input Bias Current       |        | FB=VDD or 0V                                                                           | -1     |      | +1     | μΑ    |  |

## **Electrical Characteristics (continued)**

Unless specified:  $V_{IN}$  =5V,  $T_A$  =+25°C for Typ, -40°C to +85°C for Min and Max,  $T_J$  < 125°C

| Parameter                               | Symbol | Conditions                                                             | Min | Тур | Max | Units               |  |

|-----------------------------------------|--------|------------------------------------------------------------------------|-----|-----|-----|---------------------|--|

| Timing                                  |        |                                                                        |     |     |     |                     |  |

| On-Time                                 |        | Continuous Mode $V_{IN}$ =5V, $V_{OUT}$ =3V, $R_{TON}$ =66.7k $\Omega$ | 0.9 | 1   | 1.1 | μs                  |  |

| Minimum On-Time <sup>(1)</sup>          |        |                                                                        |     | 80  |     | ns                  |  |

| Minimum Off-Time <sup>(1)</sup>         |        |                                                                        |     | 250 |     | ns                  |  |

| Soft start                              |        |                                                                        |     |     |     |                     |  |

| Soft start Time <sup>(1)</sup>          |        | Delay from PWM Switching to Output<br>Regulation                       |     | 850 |     | μs                  |  |

| Ultrasonic Power Save                   |        |                                                                        |     |     |     |                     |  |

| Zero-Crossing Detector Threshold        |        | LX - PGND                                                              |     | 0   |     | mV                  |  |

| Ultrasonic Power Save Frequency         |        |                                                                        |     | 25  |     | kHz                 |  |

| Power Good                              |        |                                                                        |     |     |     |                     |  |

| Power Good Threshold                    |        | Power Good Signal Threshold High                                       | 116 | 120 | 124 | - %V <sub>OUT</sub> |  |

|                                         |        | Power Good Signal Threshold Low                                        | 86  | 90  | 93  |                     |  |

| DCOOD Dolay Time(1)                     |        | VDD=3V                                                                 |     | 1   |     | ms                  |  |

| PGOOD Delay Time <sup>(1)</sup>         |        | VDD=5V                                                                 |     | 2   |     | ms                  |  |

| Noise Immunity Delay Time               |        |                                                                        |     | 5   |     | μs                  |  |

| Leakage                                 |        |                                                                        |     |     | 1   | μΑ                  |  |

| Power Good On-Resistance                |        |                                                                        |     | 10  | 20  | Ω                   |  |

| Fault Protection                        |        |                                                                        |     |     |     |                     |  |

| Output Under-Voltage Fault              |        | FB with Respect to REF,<br>8 Consecutive Clocks                        | -30 | -25 | -20 | %                   |  |

| Output Over-Voltage Fault               |        | FB with Respect to REF                                                 | +16 | +20 | +24 | %                   |  |

| Smart PowerSave<br>Protection Threshold |        | FB with Respect to REF                                                 | +7  | +10 | +13 | %                   |  |

| OV, UV Fault Noise Immunity Delay       |        |                                                                        |     | 5   |     | μs                  |  |

| Over-Temperature Shutdown               |        | OT Latched                                                             |     | 150 |     | °C                  |  |

## **Electrical Characteristics (continued)**

Unless specified:  $V_{IN}$  =5V,  $T_A$  =+25°C for Typ, -40°C to +85°C for Min and Max,  $T_J$  < 125°C

| Parameter                         | Symbol            | Conditions                   | Min | Тур | Max | Units            |  |

|-----------------------------------|-------------------|------------------------------|-----|-----|-----|------------------|--|

| Enable/Power Save                 | Enable/Power Save |                              |     |     |     |                  |  |

| Output Enabled                    |                   |                              | 1   |     |     | V                |  |

| Output Disabled                   |                   |                              |     |     | 0.4 | V                |  |

| EN/PSV Input Bias Current         |                   | EN/PSV = VDD or 0V           |     | 0.5 | 8.0 | μΑ               |  |

| Power Save Enabled                |                   |                              | 60  |     |     | %V <sub>DD</sub> |  |

| Forced Continuous Conduction Mode |                   | EN/PSV floating              | 39  | 41  | 44  | %V <sub>DD</sub> |  |

| Gate Drivers                      |                   |                              | •   |     |     |                  |  |

| BST Switch On resistance          |                   |                              |     | 40  | 75  | Ω                |  |

| Internal Power MOSFETs            |                   |                              |     |     |     |                  |  |

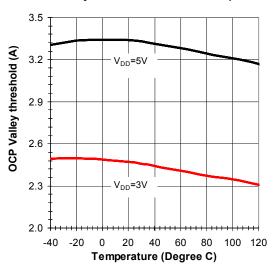

| Compatibility                     |                   | Valley Current Limit, VDD=5V | 2.5 | 3.2 |     |                  |  |

| Current Limit                     |                   | Valley Current Limit, VDD=3V | 2   | 2.4 |     | A                |  |

| LX Leakage Current                |                   | VIN=5.5V, LX=0V, High Side   |     | 1   | 10  | μΑ               |  |

|                                   |                   | High Side                    |     | 95  | 150 |                  |  |

| Switch Resistance                 |                   | Low Side                     |     | 75  | 120 | mΩ               |  |

| Non-overlap time (1)              |                   |                              |     | 30  |     | ns               |  |

#### Note:

(1) Typical value from EVB, not ATE tested.

# Pin Descriptions (MLPD-10)

| Pin # | Pin Name | Pin Function                                                                                                                                                                                                                                                   |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | BST      | Bootstrap pin. A capacitor is connected between BST to LX to develop the floating voltage for the high-side gate drive.                                                                                                                                        |

| 2     | VIN      | Power input supply voltage.                                                                                                                                                                                                                                    |

| 3     | LX       | Switching (Phase) node.                                                                                                                                                                                                                                        |

| 4     | PGND     | Power ground.                                                                                                                                                                                                                                                  |

| 5     | PGOOD    | Open-drain Power Good indicator. High impedance indicates power is good. An external pull-up resistor is required.                                                                                                                                             |

| 6     | FB       | Feedback input for switching regulator. Connect to an external resistor divider from the output to program the output voltage.                                                                                                                                 |

| 7     | EN/PSV   | Tri-state pin. Enable input for switching regulator. Pull EN/PSV high to enable the part with power save mode enabled. Connect EN/PSV to AGND to disable the switching regulator. Leave EN/PSV floating to enable the IC in forced continuous conduction mode. |

| 8     | TON      | On-time set input. Set the on-time by a series resistor to AGND.                                                                                                                                                                                               |

| 9     | AGND     | Analog Ground.                                                                                                                                                                                                                                                 |

| 10    | VDD      | Input power for internal control circuit. Needs 1µF decoupling capacitor from this pin to AGND.                                                                                                                                                                |

|       | PAD      | Thermal pad for heatsinking purposes. Connect to ground plane using multiple vias. Not connected internally.                                                                                                                                                   |

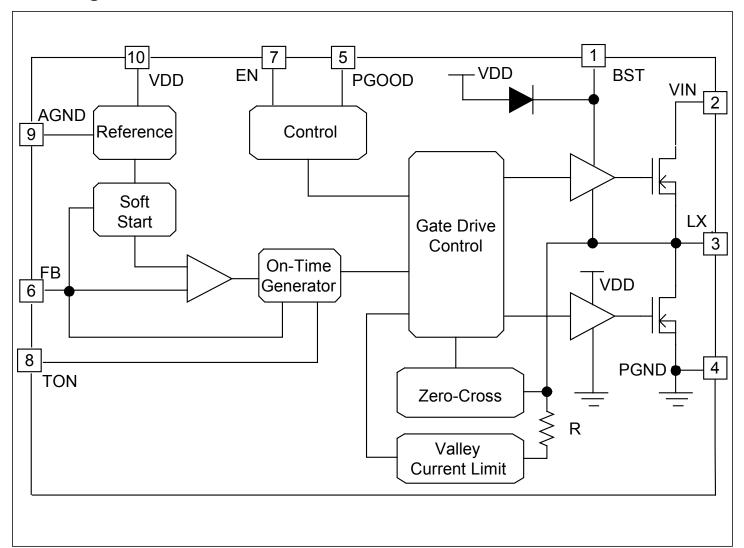

## **Block Diagram**

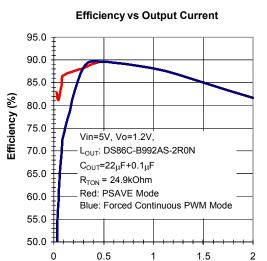

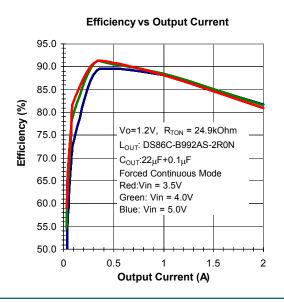

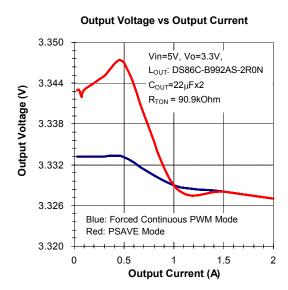

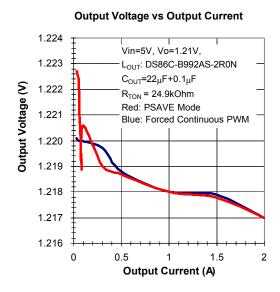

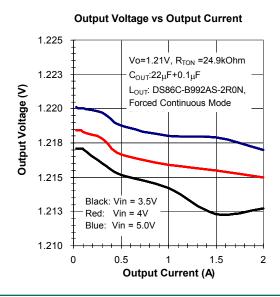

## **Typical Characteristics**

**Output Current (A)**

## **Typical Characteristics**

#### **OCP Valley Threshold vs Ambient Temperature**

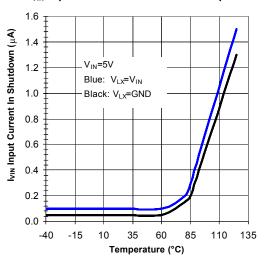

#### IVIN Input Current In Shutdown vs Temperature

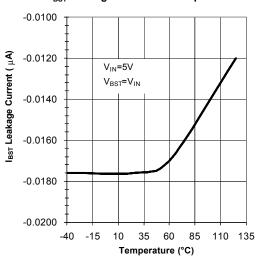

I<sub>BST</sub> Leakage Current vs Temperature

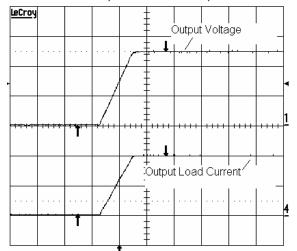

Start up waveform (  $V_{IN}$ =5V,  $V_{OUT}$ =1.2V,  $I_{OUT}$ =2A, Channel 1: 500mV/Div, Channel 4: 1A/Div, Time: 0.5ms/Div )

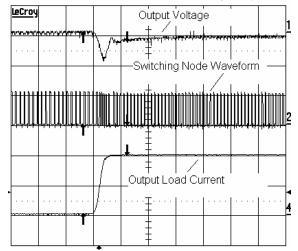

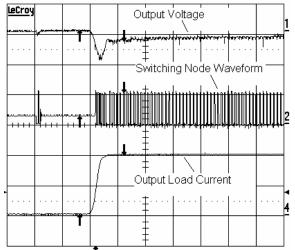

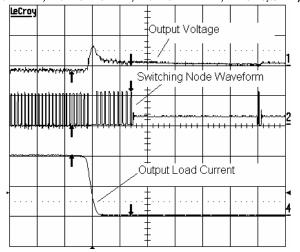

Load Transient Test (V<sub>IN</sub>=5V, V<sub>OUT</sub>=1.2V, I<sub>OUT</sub>= 0A to 2A, Forced Continuous Conduction Mode, L<sub>OUT</sub>=1.3µH, C<sub>OUT</sub>=2x22µF, Channel 1: 50mV/Div, Channel 2:5V/Div,Channel 4: 1A/Div, Time:10µs/Div)

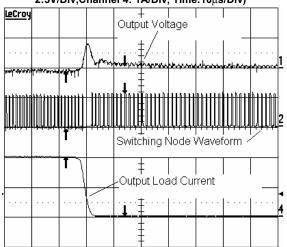

Load Transient Test (V<sub>IN</sub>=5V, V<sub>OUT</sub>=1.2V, I<sub>OUT</sub>= 2A to 0A, Forced Continuous Conduction Mode, L<sub>OUT</sub>=1.3µH, C<sub>OUT</sub>=2x22µF, Channel 1: 50mV/Div, Channel 2:5V/Div,Channel 4: 1A/Div, Time:10µs/Div)

### **Typical Characteristics**

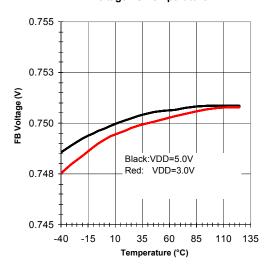

#### FB Voltage vs Temperature

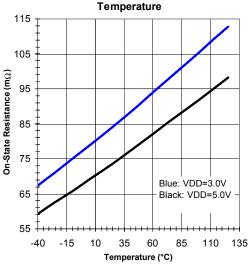

## Low Side Switch On-State Resistance vs

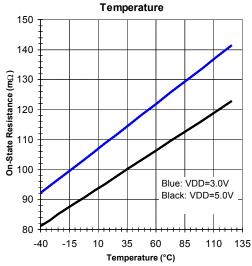

## High Side Switch On-State Resistance vs

Load Transient Test ( $V_{IN}$ =5V,  $V_{OUT}$ =1.2V,  $I_{OUT}$ = 0A to 2A, PSAVE Mode Enabled,  $L_{OUT}$ =1.3 $\mu$ H, $C_{OUT}$ =2x22 $\mu$ F,Channel 1: 50mV/Div, Channel 2:5V/Div,Channel 4:1A/Div,Time:10 $\mu$ s/Div)

Load Transient Test ( $V_{IN}$ =5V,  $V_{OUT}$ =1.2V,  $I_{OUT}$ = 2A to 0A, PSAVE Mode Enabled,  $L_{OUT}$ =1.3 $\mu$ H,  $C_{OUT}$ =2x22 $\mu$ F, Channel 1: 50mV/Div,Channel 2:5V/Div,Channel 4:1A/Div, Time:10 $\mu$ s/Div)

### **Applications Information**

### **SC172 Synchronous Buck Converter**

The SC172 is a step down synchronous buck dc-dc regulator. The SC172 is capable of 2A operation at very high efficiency in a tiny 3x3-10 pin package. The programmable operating frequency range of 200kHz – 1MHz enables the user to optimize the solution for minimum board space and optimum efficiency.

The buck regulator employs pseudo-fixed frequency adaptive on-time control. This control scheme allows fast transient response thereby lowering the size of the power components used in the system.

### **Input Voltage Range**

The SC172 can operate with an input voltage ranging from 3V to 5.5V.

### **Psuedo-fixed Frequency Adaptive On-time Control**

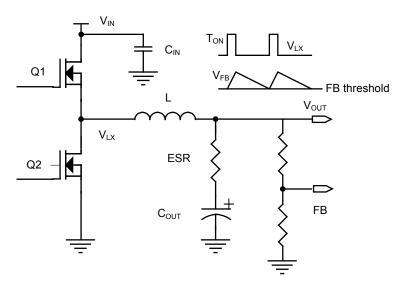

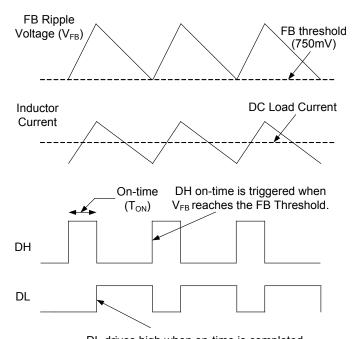

The PWM control method used by the SC172 is pseudo-fixed frequency, adaptive on-time, as shown in Figure 1. The ripple voltage generated at the output capacitor ESR is used as a PWM ramp signal. This ripple is used to trigger the on-time of the controller.

Figure 1 — PWM Control Method,  $V_{OUT}$  Ripple

The adaptive on-time is determined by an internal one-shot timer. When the one-shot is triggered by the output ripple, the device sends a single on-time pulse to the high-side MOSFET. The pulse period is determined by  $V_{\text{OUT}}$  and  $V_{\text{IN}}$ ; the period is proportional to output voltage and inversely proportional to input voltage. With this adaptive on-time arrangement, the device automatically anticipates the on-time needed to regulate  $V_{\text{OUT}}$  for the present  $V_{\text{IN}}$  condition and at the selected frequency.

The advantages of adaptive on-time control are:

- Predictable operating frequency compared to other variable frequency methods.

- Reduced component count by eliminating the error amplifier and compensation components.

- Reduced component count by removing the need to sense and control inductor current.

- Fast transient response the response time is controlled by a fast comparator instead of a typically slow error amplifier.

- Reduced output capacitance due to fast transient response

#### **One-Shot Timer and Operating Frequency**

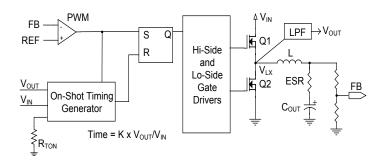

The one-shot timer operates as shown in Figure 2. The FB Comparator output goes high when  $V_{FB}$  is less than the internal 750mV reference. This feeds into the gate drive and turns on the high-side MOSFET, and also starts the one-shot timer. The one-shot timer uses an internal comparator, timing capacitor, and a low pass filter (LPF) which regenerates  $V_{OUT}$  from LX. One comparator input is connected to the filtered LX voltage, the other input is connected to the capacitor. When the on-time begins, the internal capacitor charges from zero volts through a current which is proportional to  $V_{IN}$ . When the capacitor voltage reaches  $V_{OUT}$ , the on-time is completed and the high-side MOSFET turns off.

This method automatically produces an on-time that is proportional to  $V_{\rm OUT}$  and inversely proportional to  $V_{\rm IN}$ . Under steady-state operation conditions, the switching frequency can be determined from the on-time by the following equation.

$$f_{SW} = \frac{V_{OUT}}{T_{ON} \times V_{IN}}$$

Figure 2 — On-Time Generation

The SC172 uses an external resistor to set the on-time which indirectly sets the frequency. The on-time can be programmed to provide operating frequency from 200kHz to 1MHz using a resistor between the TON pin and ground. The resistor value is selected by the following equation.

$$R_{TON} = (\frac{V_{OUT}}{V_{FB}}) \cdot \frac{1}{100pF \cdot f_{SW}}$$

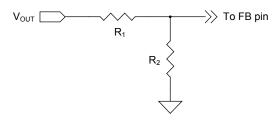

### **V**<sub>out</sub> Voltage Selection

The switcher output voltage is regulated by comparing  $V_{\text{OUT}}$  as seen through a resistor divider at the FB pin to the internal 750mV reference voltage, see Figure 3.

Figure 3 — Output Voltage Selection

Note that this control method regulates the valley of the output ripple voltage, not the DC value. The DC output voltage  $V_{\text{OUT}}$  is offset by the output ripple according to the following equation.

$$V_{\text{OUT}} = 0.75V \cdot \left(1 + \frac{R_1}{R_2}\right) + \frac{V_{\text{RIPPLE}}}{2}$$

### **Enable and Power-save Inputs**

The EN/PSV input is used to enable or disable the switching regulator. When EN/PSV is low (grounded), the switching regulator is off and in its lowest power state. When off, the output power switches are tri-stated. When EN/PSV is allowed to float, the pin voltage will float to 41% of the voltage at  $V_{DD}$ . The switching regulator turns on with power-save disabled and all switching is in forced continuous mode.

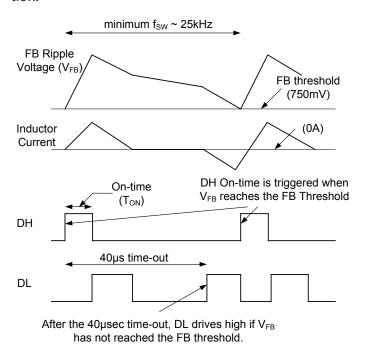

When EN/PSV is high (above 60% of the voltage at  $V_{\rm DD}$ ), the switching regulator turns on with ultrasonic powersave enabled. The SC172 ultrasonic power-save operation maintains a minimum switching frequency of 25kHz, for applications with stringent audio requirements.

### **Forced Continuous Mode Operation**

The SC172 operates in Forced Continuous Mode (FCM) by floating the EN/PSV pin (see Figure 4). In this mode one of the power MOSFETs is always on, with no intentional dead time other than to avoid cross-conduction. This feature results in uniform frequency across the full load range with the trade-off being poor efficiency at light loads due to the high-frequency switching of the MOSFETs.

DL drives high when on-time is completed. DL remains high until  $V_{\text{FB}}$  falls to the FB threshold.

Figure 4 — Forced Continuous Mode Operation

### **Ultrasonic Power Save Operation**

The SC172 provides ultrasonic power save operation at light loads, with the minimum operating frequency fixed at 25kHz. This is accomplished using an internal timer that monitors the time between consecutive high-side gate pulses. If the time exceeds 40µs, DL drives high to turn the low-side MOSFET on. This draws current from  $V_{\text{OUT}}$  through the inductor, forcing both  $V_{\text{OUT}}$  and  $V_{\text{FB}}$  to fall. When  $V_{\text{FB}}$  drops to the 750mV threshold, the next DH on-time is triggered. After the on-time is completed the high-side MOSFET is turned off and the low-side MOSFET turns on. The low-side MOSFET remains on until the inductor current ramps down to zero, at which point the low-side MOSFET is turned off.

Because the on-times are forced to occur at intervals no greater than 40 $\mu$ s, the frequency will not fall below ~25kHz. Figure 5 shows ultrasonic power save operation.

Figure 5 — Ultrasonic Power Save Operation

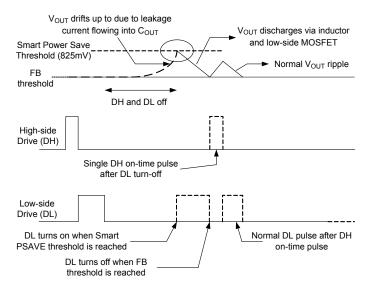

#### **Smart Power Save Protection**

Active loads may leak current from a higher voltage into the switcher output. Under light load conditions with power save enabled, this can force  $V_{OUT}$  to slowly rise and reach the over-voltage threshold, resulting in a hard shutdown. Smart power save prevents this condition. When the FB voltage exceeds 10% above nominal (exceeds 825mV), the device immediately disables power-save, and DL drives high to turn on the low-side MOSFET. This draws current from  $V_{OUT}$  through the inductor and causes  $V_{OUT}$  to fall. When  $V_{FB}$  drops back to the 750mV trip point, a normal  $T_{ON}$  switching cycle begins. This method prevents a hard OVP shutdown and also cycles energy from  $V_{OUT}$  back to  $V_{IN}$ . Figure 6 shows typical waveforms for the Smart Power Save feature.

Figure 6 — Smart Power Save

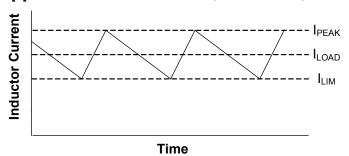

#### **Current Limit Protection**

The device features fixed current limiting, which is accomplished by using the R<sub>DS(ON)</sub> of the lower MOSFET for current sensing. While the low-side MOSFET is on, the inductor current flows through it and creates a voltage across the R<sub>DS(ON)</sub>. During this time, the voltage across the MOSFET is negative with respect to ground. During this time, If this MOSFET voltage drop exceeds the internal reference voltage, the current limit will activate. The current limit then keeps the low-side MOSFET on and will not allow another high side on-time, until the current in the low-side MOSFET reduces enough to drop below the internal reference voltage once more. This method regulates the inductor valley current at the level shown by I<sub>LIM</sub> in Figure 7.

Figure 7 — Valley Current Limit

Setting the valley current limit to a value of  $I_{LIM}$  results in a peak inductor current of ILIM plus the peak-to-peak ripple current. In this situation, the average (load) current through the inductor will be  $I_{LIM}$  plus one half the peak-to-peak ripple current.

### **Soft start of PWM Regulator**

Soft start is achieved in the PWM regulator by using an internal voltage ramp as the reference for the FB comparator. The voltage ramp is generated using an internal charge pump which drives the reference from zero to 750mV in ~1.8mV increments, using an internal ~500kHz oscillator. When the ramp voltage reaches 750mV, the ramp is ignored and the FB comparator switches over to a fixed 750mV threshold. During soft start the output voltage tracks the internal ramp, which limits the start-up inrush current and provides a controlled soft start profile for a wide range of applications. Typical soft start ramp time is 0.85ms.

During soft start the regulator turns off the low-side MOSFET on any cycle if the inductor current falls to zero. This prevents negative inductor current, allowing the device to start into a pre-biased output up to 90% of the targeted output. This soft start operation is implemented even if FCM is selected. FCM operation is allowed only after PGOOD is high.

### **Power Good Output**

The power good (PGOOD) output is an open-drain output which requires a pull-up resistor. When the output voltage is 10% below the nominal voltage, PGOOD is pulled low. It is held low until the output voltage returns to the nominal voltage. PGOOD is held low during soft start and activated approximately 1ms after  $V_{\text{OUT}}$  reaches regulation. The total PGOOD delay is typically 2ms.

PGOOD will transition low if the  $V_{FB}$  pin exceeds +20% of nominal, which is also the over-voltage shutdown threshold (900mV). PGOOD also pulls low if the EN/PSV pin is low when VDD is present.

#### **Output Over-Voltage Protection**

Over-Voltage Protection (OVP) becomes active as soon as the device is enabled. The threshold is set at 750mV + 20% (900mV). When  $V_{FB}$  exceeds the OVP threshold, DL latches high and the low-side MOSFET is turned on. DL remains high and the controller remains off, until the EN/ PSV input is toggled or VDD is cycled. There is a 5 $\mu$ s delay built into the OVP detector to prevent false transitions. PGOOD is also low after an OVP event.

#### **Output Under-Voltage Protection**

When  $V_{FB}$  falls to 75% of its nominal voltage (falls to 562.5mV) for eight consecutive clock cycles, the switcher is shut off and the DH and DL drives are pulled low to turn off the MOSFETs. The controller stays off until EN/PSV is toggled or VDD is cycled.

### VDD UVLO, and POR

Under-Voltage Lock-Out (UVLO) circuitry inhibits switching and tri-states the power FETs until VDD rises above 2.9V. An internal Power-On Reset (POR) occurs when VDD exceeds 2.9V, which resets the fault latch and soft start counter to begin the soft start cycle. The SC172 then begins a soft start cycle. The PWM will shut off if VDD falls below 2.7V.

### **Design Procedure**

When designing a switch mode supply the input voltage range, load current, switching frequency, and inductor ripple current must be specified.

The maximum input voltage  $(V_{INMAX})$  is the highest specified input voltage. The minimum input voltage  $(V_{INMIN})$  is determined by the lowest input voltage after evaluating the voltage drops due to connectors, fuses, switches, and PCB traces.

The following parameters define the design.

- Nominal output voltage (V<sub>OUT</sub>)

- Static or DC output tolerance

- Transient response

- Maximum load current (I<sub>OUT</sub>)

There are two values of load current to evaluate — continuous load current and peak load current. Continuous load current relates to thermal stresses which drive the selection of the inductor and input capacitors. Peak load current determines instantaneous component stresses and filtering requirements such as inductor saturation, output capacitors, and design of the current limit circuit.

The following values are used in this design.

- $V_{IN} = 5V \pm 10\%$

- $V_{OUT} = 1.0V \pm 4\%$

- $f_{sw} = 800 \text{kHz}$

- Load = 2A maximum

### **Frequency Selection**

Selection of the switching frequency requires making a trade-off between the size and cost of the external filter components (inductor and output capacitor) and the power conversion efficiency.

The desired switching frequency is 800kHz which results from using components selected for optimum size and cost .

A resistor ( $R_{TON}$ ) is used to program the on-time (indirectly setting the frequency) using the following equation un-

der zero load condition.

$$R_{TON} = (\frac{V_{OUT}}{V_{FB}}) \cdot \frac{1}{100pF \cdot f_{SW}}$$

Since the  $\rm f_{SW}$  may increase by about 100kHz per Ampere,  $\rm R_{TON}$  should be programmed at 600kHz under zero load to achieve 800kHz at full load.

Calculating  $R_{TON}$  results in the following solution.

$\rm R_{TON}{=}22.2k\Omega,$  we use  $\rm R_{TON}{=}22.1k\Omega$  in real application.

#### **Inductor Selection**

In order to determine the inductance, the ripple current must first be defined. Low inductor values result in smaller size but create higher ripple current which can reduce efficiency. Higher inductor values will reduce the ripple current/voltage and for a given DC resistance are more efficient. However, larger inductance translates directly into larger packages and higher cost. Cost, size, output ripple, and efficiency are all used in the selection process.

The ripple current will also set the boundary for power-save operation. The switching will typically enter power-save mode when the load current decreases to 1/2 of the ripple current. For example, if ripple current is 1A then power-save operation will typically start for loads less than 0.5A. If ripple current is set at 40% of maximum load current, then power-save will start for loads less than 20% of maximum current.

The inductor value is typically selected to provide a ripple current that is between 25% to 50% of the maximum load current. This provides an optimal trade-off between cost, efficiency, and transient performance.

During the DH on-time, voltage across the inductor is  $(V_{IN} - V_{OUT})$ . The equation for determining inductance is shown next.

$$T_{\text{ON}} = \frac{V_{\text{OUT}}}{V_{\text{INMAX}} \cdot f_{\text{SW}}}$$

$$L = \frac{(V_{IN} - V_{OUT}) \times T_{ON}}{I_{RIPPLE}}$$

### **Example**

In this example, the inductor ripple current is set equal to 50% of the maximum load current. Therefore ripple current will be 50% x 2A or 1A. To find the minimum inductance needed, use the  $V_{\rm IN}$  and  $T_{\rm ON}$  values that correspond to  $V_{\rm INMAX}$ .

$$T_{ON\_VINMAX} = \frac{1V}{5.5V \cdot 800kHz} = 227ns$$

$$L = \frac{(5.5V - 1V) \bullet 227ns}{1A} = 1\mu H$$

A larger value of  $2\mu H$  is selected. This will decrease the maximum  $I_{\text{RIPPI}\,F}$  to 0.511A.

Note that the inductor must be rated for the maximum DC load current plus 1/2 of the ripple current.

The ripple current under minimum  $V_{IN}$  conditions is also checked using the following equations.

$$T_{ON\_VINMIN} = \frac{1V}{4.5V \times 800kHz} = 277ns$$

$$I_{RIPPLE} = \frac{(V_{IN} - V_{OUT}) \times T_{ON}}{I}$$

$$I_{\text{RIPPLE\_VINMIN}} = \frac{(4.5V - 1V) \times 277ns}{2\mu H} = 0.485A$$

### **Capacitor Selection**

The output capacitors are chosen based on required ESR and capacitance. The maximum ESR requirement is controlled by the output ripple requirement and the DC tolerance. The output voltage has a DC value that is equal to the valley of the output ripple plus 1/2 of the peakto-peak ripple. Change in the output ripple voltage will lead to a change in DC voltage at the output.

The design goal is for the output voltage regulation to be  $\pm 4\%$  under static conditions. The internal 750mV reference tolerance is 1%. Assuming a 1% tolerance from the FB resistor divider, this allows 2% tolerance due to  $V_{OUT}$  ripple. Since this 2% error comes from 1/2 of the ripple voltage, the allowable ripple is 4%, or 40mV for a 1V output.

The maximum ripple current of 0.511A creates a ripple voltage across the ESR. The maximum ESR value allowed is shown by the following equations.

$$ESR_{MAX} = \frac{V_{RIPPLE}}{I_{RIPPLEMAX}} = \frac{40 \text{mV}}{0.51 \text{A}}$$

$$ESR_{MAX} = 78.4 \text{ m}\Omega$$

The output capacitance is chosen to meet transient requirements. A worst-case load release, from maximum load to no load at the exact moment when inductor current is at the peak, determines the required capacitance. If the load release is instantaneous (load changes from maximum to zero in < 1 $\mu$ s), the output capacitor must absorb all the inductor's stored energy. This will cause a peak voltage on the capacitor according to the following equation.

$$COUT_{MIN} = \frac{L \times (I_{OUT} + \frac{1}{2} \times I_{RIPPLEMAX})^2}{(V_{PEAK})^2 - (V_{OUT})^2}$$

Assuming a peak voltage  $V_{\text{peak}}$  of 1.050V (50mV rise upon load release), and a 2A load release, the required capacitance is shown by the next equation.

COUT<sub>MIN</sub> =

$$\frac{2\mu H \times (2A + \frac{1}{2} \times 0.511A)^{2}}{(1.05V)^{2} - (1.0V)^{2}} = 99\mu F$$

If the load release is relatively slow, the output capacitance can be reduced. At heavy loads during normal switching, when the FB pin is above the 750mV reference, the DL output is high and the low-side MOSFET is on. During this time, the voltage across the inductor is approximately -V<sub>OUT</sub>. This causes a down-slope or falling di/dt in the inductor. If the load di/dt is not much faster than the -di/dt in the inductor, then the inductor current will tend to track the falling load current. This will reduce the excess inductive energy that must be absorbed by the output capacitor, therefore a smaller capacitance can be used.

The following can be used to calculate the needed capacitance for a given  $dl_{LOAD}/dt$ . Peak inductor current is shown by the next equation.

$$I_{LPK} = 2A + \frac{1}{2} \times 0.511A = 2.26A$$

Rate of change of load current is

$$\frac{dI_{LOAD}}{dt} = \frac{0.6A}{1\mu s}$$

$I_{MAX}$  = maximum load release = 2A

$$C_{\text{OUT}} = I_{\text{LPK}} \times \frac{I_{\text{LPK}}}{V_{\text{OUT}}} - \frac{I_{\text{MAX}}}{dI_{\text{LOAD}}} \times dt$$

$$2 \times (V_{\text{PK}} - V_{\text{OUT}})$$

$$C_{OUT} = 2.26A \times \frac{2\mu H \times \frac{2.26A}{1V} - \frac{2A}{0.6A} \times 1\mu s}{2 \times (1.05V - 1V)}$$

$$C_{\text{OUT}} \, = 13 \, \mu F$$

Note that  $C_{OUT}$  is much smaller in this example,  $13\mu F$  compared to  $99\mu F$  based upon a worst-case load release. To meet the two design criteria of minimum  $13\mu F$  and maximum  $78m\Omega$  ESR, select one capacitor rated at  $22\mu F$  and  $15m\Omega$  ESR or less.

It is recommended that an additional small capacitor be placed in parallel with  $C_{\rm OUT}$  in order to filter high frequency switching noise.

### **Stability Considerations**

Unstable operation is possible with adaptive on-time controllers, and usually takes the form of double-pulsing or ESR loop instability.

Double-pulsing occurs due to switching noise seen at the FB input or because the FB ripple voltage is too low. This causes the FB comparator to trigger prematurely after the minimum off-time has expired. In extreme cases the noise can cause three or more successive on-times. Double-pulsing will result in higher ripple voltage at the output, but in most applications it will not affect operation. This form of instability can usually be avoided by providing the FB pin with a smooth, clean ripple signal that is at least 10mVp-p, which may dictate the need to

increase the ESR of the output capacitors. It is also imperative to provide a proper PCB layout as discussed in the Layout Guidelines section.

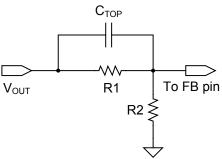

Another way to eliminate doubling-pulsing is to add a small ( $\sim$  10pF) capacitor across the upper feedback resistor, as shown in Figure 8. This capacitor should be left unpopulated unless it can be confirmed that double-pulsing exists. Adding the  $C_{TOP}$  capacitor will couple more ripple into FB to help eliminate the problem. An optional connection on the PCB should be available for this capacitor.

Figure 8 — Capacitor Coupling to FB Pin

ESR loop instability is caused by insufficient ESR. The details of this stability issue are discussed in the ESR Requirements section. The best method for checking stability is to apply a zero-to-full load transient and observe the output voltage ripple envelope for overshoot and ringing. Ringing for more than one cycle after the initial step is an indication that the ESR should be increased.

One simple way to solve this problem is to add trace resistance in the high current output path. A side effect of adding trace resistance is a decrease in load regulation.

### **ESR Requirements**

A minimum ESR is required for two reasons. One reason is to generate enough output ripple voltage to provide 10mVp-p at the FB pin (after the resistor divider) to avoid double-pulsing.

The second reason is to prevent instability due to insufficient ESR. The on-time control regulates the valley of the output ripple voltage. This ripple voltage is the sum of the two voltages. One is the ripple generated by the ESR, the other is the ripple due to capacitive charging

and discharging during the switching cycle. For most applications, the total output ripple voltage is dominated by the output capacitors, typically SP or POSCAP devices. For stability the ESR zero of the output capacitor should be lower than approximately one-third the switching frequency. The formula for minimum ESR is shown by the following equation.

$$\text{ESR}_{\text{MIN}} = \frac{3}{2 \times \pi \times C_{\text{OUT}} \times f_{\text{SW}}}$$

### **Using Ceramic Output Capacitors**

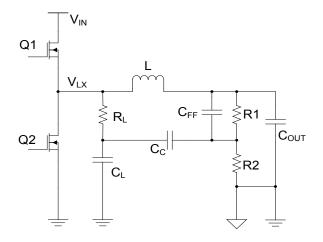

When applications use ceramic output capacitors, the ESR is normally too small to meet the previously stated ESR criteria. In these applications it is necessary to add a small signal injection network as shown in Figure 9. In this network  $R_L$  and  $C_L$  filter the LX switching waveform to generate an in-phase ripple voltage comparable to the ripple seen on higher ESR capacitors.  $C_C$  is a coupling capacitor used to AC couple the generated ripple onto the FB pin. Capacitor  $C_{FF}$  is required for min  $C_{OUT}$  applications. This capacitor introduces a lead/lag into the control with the maximum phase placed at  $1/2 f_{SW}$  for added stability.

Figure 9 — Signal Injection Circuit

The values of R<sub>L</sub>, C<sub>L</sub>, C<sub>C</sub> and C<sub>FF</sub> are dependent on the conditions of the specific application such as V<sub>IN</sub>, V<sub>OUT</sub>, f<sub>SW</sub> and I<sub>OUT</sub>. For switching frequencies ranging from 600kHz to 800kHz, calculations plus experimental test results show that the following combination of R<sub>L</sub>=2.5k $\Omega$ , C<sub>L</sub>=10nF, C<sub>C</sub>=68pF and C<sub>FF</sub>=39pF can be used for many output voltages and loads.

### **Output Voltage Dropout**

The output voltage adjustable range for continuous-conduction operation is limited by the fixed 320ns (typical) minimum off-time. When working with low input voltages, the duty-factor limit must be calculated using worst-case values for on and off times. The duty-factor limitation is shown by the next equation.

$$DUTY = \frac{T_{ON(MIN)}}{T_{ON(MIN)} + T_{OFF(MAX)}}$$

The inductor resistance and MOSFET on-state voltage drops must be included when performing worst-case dropout duty-factor calculations.

### $\textbf{System DC Accuracy} - \textbf{V}_{\texttt{out}} \textbf{Controller}$

Three factors affect  $V_{OUT}$  accuracy: the trip point of the FB error comparator, the ripple voltage variation with line and load, and the external resistor tolerance. The error comparator offset is trimmed so that under static conditions it trips when the feedback pin is 750mV,  $\pm 1\%$ .

The on-time pulse from the SC172 in the design example is calculated to give a pseudo-fixed frequency of 800kHz. Some frequency variation with line and load is expected. This variation changes the output ripple voltage. Because adaptive on-time converters regulate to the valley of the output ripple, ½ of the output ripple appears as a DC regulation error. For example, if the output ripple is 50mV with  $V_{IN} = 5$  volts, then the measured DC output will be 25mV above the comparator trip point. If the ripple increases to 30mV with  $V_{IN} = 5.5$ V, then the measured DC output will be 15mV above the comparator trip. The best way to minimize this effect is to minimize the output ripple.

To compensate for valley regulation, it may be desirable to use passive droop. Take the feedback directly from the output side of the inductor and place a small amount of trace resistance between the inductor and output capacitor. This trace resistance should be optimized so that at full load the output droops to near the lower regulation limit. Passive droop minimizes the required output capacitance because the voltage excursions due to load steps are reduced as seen at the load.

The use of 1% feedback resistors may result in up to an additional 1% error. If tighter DC accuracy is required, resistors with lower tolerances should be used.

The output inductor value may change with current. This will change the output ripple and therefore will have a minor effect on the DC output voltage. The output ESR also affects the output ripple and thus has a minor effect on the DC output voltage.

deadtime diode conduction, as long as the transient voltage on PVIN is less than 6.0V. The time duration of the transient LX pin voltage is measured on the voltage portion which is either over 6.0V for positive voltage spike or under -1V for negative voltage spike. The LX voltage is measured from the LX pin to the PGND pin by using a probing loop which is as short as possible to minimize or eliminate the switching noise pick up.

### **Switching Frequency Variation**

The switching frequency will vary depending on line and load conditions. The line variations are a result of fixed propagation delays in the on-time one-shot, as well as unavoidable delays in the power FET switching. As  $V_{\rm IN}$  increases, these factors make the actual DH on-time slightly longer than the ideal on-time. The net effect is that frequency tends to fall slightly with increasing input voltage.

The switching frequency also varies with load current as a result of the power losses in the MOSFETs and the inductor. For a conventional PWM constant-frequency converter, as load increases the duty cycle also increases slightly to compensate for IR and switching losses in the MOSFETs and inductor. A adaptive on-time converter must also compensate for the same losses by increasing the effective duty cycle (more time is spent drawing energy from  $V_{\rm IN}$  as losses increase). The on-time is essentially constant for a given  $V_{\rm OUT}$  and  $V_{\rm IN}$  combination, to offset the losses the off-time will tend to reduce slightly as load increases. The net effect is that switching frequency increases slightly with increasing load.

### **Switching Node Voltage Spike**

Due to parasitic board inductance, the transient LX pin voltage at the point of measurement may appear larger than that which exists on silicon. With an input multilayer ceramic capacitor of 10uF placed less than 3mm away from the PVIN pin, the device is designed and guaranteed to tolerate the short transient voltages, of maximum 20ns duration, that will appear on the LX pin due to the

### **Layout Guideline**

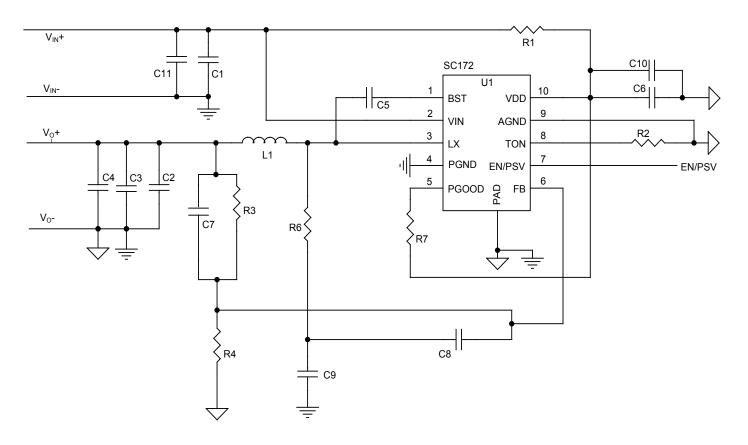

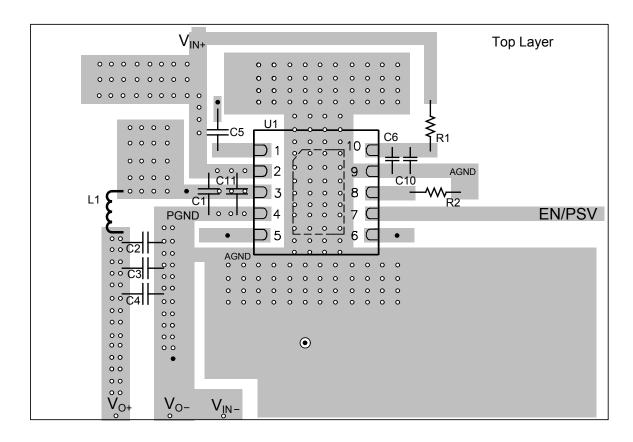

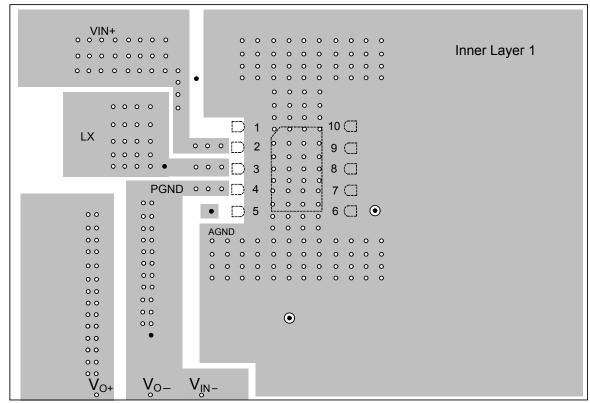

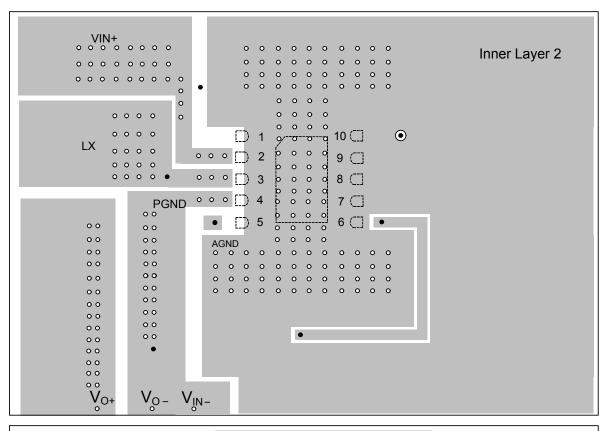

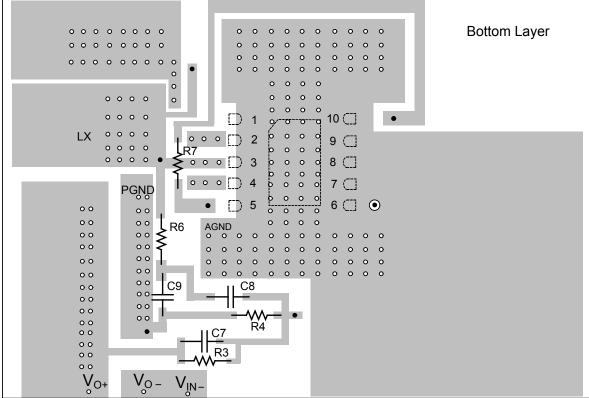

Schematic for layout illustration

Since the SC172 has integrated switches, special consideration should be given to board layout. Let us use the schematic shown above as an example. The board level layout is illustrated in the following four layers.

As shown on the top layer layout, U1 is the switching regulator SC172. C1 and C11 serve as the decoupling capacitor for the buck converter power train. C11, with a value between 1nF and 10nF, is the high frequency filtering capacitor. It is recommended to put C1 and C11 as close as possible to the SC172 to get the best decoupling performance, with C11 closest. C1, with a value of 10uF, should be placed no more than 3mm away from the VIN pin. L1 is the output filtering inductor. C2, C3 and C4 are the output filtering capacitors. C5 is the boostrap capacitor. Pin 10 (VDD) is the input bias power for the internal circuits. It is recommended to get the power from VIN through an RC filtering network consisted of R1, C6 and C10. The value of R1 can be between  $3.01\Omega$  and  $10\Omega$  and the capacitance of C10 should be above 1µF. C6, with a value of 1nF, is the high frequency filtering capacitor. The locations of C6 and C10 should be as close as possible to pins 9 and 10, with C6 closest, to get the best possible filtering result. R2 is the on-time programming resistor. R2 should be located as close as possible to pin 8 and it should return to analog ground. The EN/PSV pin is a tristate pin. Pull EN/PSV high to enable the part with power save mode enabled. Connect EN/PSV to AGND to disable the switching regulator. Leave EN/PSV floating to enable the IC in forced continuous conduction mode.

Since there are two integrated MOSFETs inside the SC172 that will dissipate a lot of power, to help spread the heat out of the IC more efficiently, there is a thermal pad underneath the SC172 serving as a heat sink. To enlarge the heat sinking area, a large copper plane under the thermal pad as shown on the top layer is recommended.

On inner layer 2, a large analog ground plane (AGND) on the right hand side is connected to the thermal pad underneath the SC172 using vias. Thus the heat generated inside the SC172 can be spread through the vias to the

20

inner layers to expand the heat sinking area.

On the bottom layer, the resistor network composed of R3 and R4 determines the output voltage. C7 is the feed forward capacitor which helps to stabilize the circuit. R6 in series with C9 is connected to the LX pin (through the via) to the power ground. C8 is the coupling capacitor which injects the ramp signal generated on C9 to the FB pin of the SC172. R7 is the pull up resistor for the PGOOD pin.

## **Typical Application Circuits**

Application Circuit: Buck Converter with 1.2V out and 0 to 2A load current (Vin= 5V)

Application Circuit: Buck Converter with 3.3V out and 0 to 2A load current (Vin=5V)

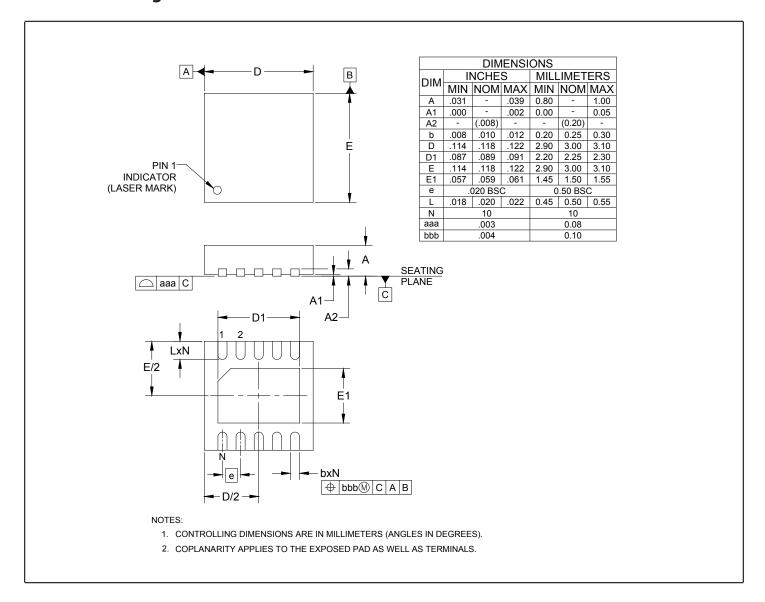

# Outline Drawing - MLPD-10 3x3

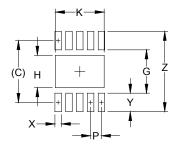

## Land Pattern - MLPD-10 3x3

|     | DIMENSIONS |             |  |  |  |  |

|-----|------------|-------------|--|--|--|--|

| DIM | INCHES     | MILLIMETERS |  |  |  |  |

| С   | (.112)     | (2.85)      |  |  |  |  |

| G   | .079       | 2.00        |  |  |  |  |

| Н   | .059       | 1.50        |  |  |  |  |

| K   | .089       | 2.25        |  |  |  |  |

| Р   | .020       | 0.50        |  |  |  |  |

| X   | .012       | 0.30        |  |  |  |  |

| Υ   | .033       | 0.85        |  |  |  |  |

| Z   | .146       | 3.70        |  |  |  |  |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

- 3. THERMAL VIAS IN THE LAND PATTERN OF THE EXPOSED PAD SHALL BE CONNECTED TO A SYSTEM GROUND PLANE. FAILURE TO DO SO MAY COMPROMISE THE THERMAL AND/OR FUNCTIONAL PERFORMANCE OF THE DEVICE.