# SC194B Selectable 3.6V/3.3V/3.0V/2.5V 1A Synchronous Buck Converter

#### **POWER MANAGEMENT**

#### Description

The SC194B is a synchronous step-down converter with integrated power devices. Four selectable output voltages suitable for portable device interface, memory function blocks, and 5V to 3.3V voltage conversion are available.

Automatic selection of Power Save Mode (PSAVE) is supported which enhances efficiency. A 100% duty cycle mode allows operation for input voltages close to the required output voltage.

The need for external components is minimized by providing internal feedback compensation, and allowing selection of the required output voltage by hard wiring VID code inputs. The maximum current rating of the internal MOSFET switches allows a DC output current of 1A.

The switching frequency is nominally set to 1MHz, allowing the use of small inductors and capacitors. A flexible clocking scheme is used that allows synchronization to an external oscillator or control by the internal oscillator.

The device can operate in either forced PWM mode or in PSAVE mode. If PSAVE mode is enabled the part will automatically enter PSAVE at light loads to maintain maximum efficiency across the full load range. For noise sensitive applications, PSAVE mode can be disabled by synchronizing to an external oscillator, or pulling the SYNC/PWM pin high. Shutdown turns off all the control circuitry to achieve a typical shutdown current of 0.1µA.

#### **Features**

- ◆ Up to 95% efficiency

- PSAVE operation to maximize efficiency

- ◆ Output current 1A

- ◆ Input range 2.7V to 5.5V

- Four selectable output voltages

- Quiescent current 17μA in PSAVE

- Dynamic voltage positioning capability

- Fixed 1MHz frequency or 750kHz to 1.25MHz synchronized operation

- Current mode operation for excellent line and load transient response

- ◆ 100% duty cycle in dropout

- ◆ Soft-start

- Over-temperature and short-circuit protection

- Lead-free package 3mm x 3mm MLPD

#### **Applications**

- ◆ PDA

- ◆ Pocket PC and Smart Phones

- USB Powered Modems

- CPUs and DSPs

- PC Cards and Notebooks

- xDSL Applications

- ◆ Standard 5-V to 3.3-V Conversion

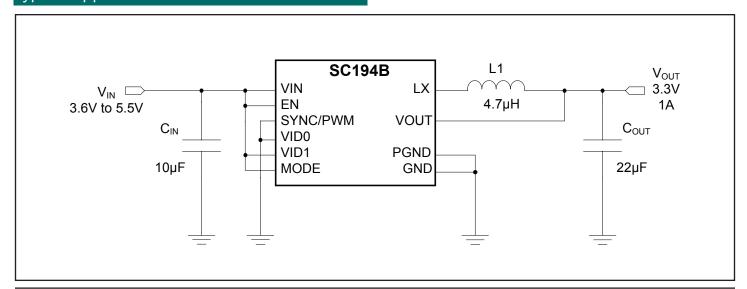

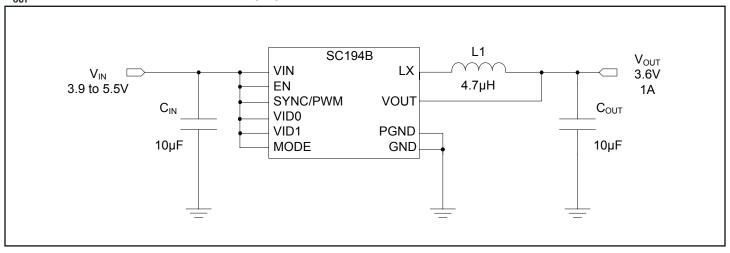

### Typical Application Circuit

### **Absolute Maximum Ratings**

Exceeding the specifications below may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

| Parameter                                            | Symbol           | Maximum                              | Units |

|------------------------------------------------------|------------------|--------------------------------------|-------|

| Input Supply Voltage                                 | V <sub>IN</sub>  | -0.3 to 7                            | V     |

| Logic Inputs (SYNC/PWM, EN, MODE, VID0, VID1)        | V <sub>N</sub>   | -0.3 to V <sub>IN</sub> +0.3, 7V Max | V     |

| Output Voltage                                       | V <sub>out</sub> | -0.3 to V <sub>IN</sub> +0.3, 7V Max | V     |

| LX Voltage                                           | $V_{LX}$         | -1 to V <sub>IN</sub> +1, 7V Max     | V     |

| Thermal Impedance Junction to Ambient <sup>(1)</sup> | $\theta_{JA}$    | 40                                   | °C/W  |

| VOUT Short-Circuit to GND                            | t <sub>sc</sub>  | Continuous                           | s     |

| Operating Ambient Temperature Range                  | T <sub>A</sub>   | -40 to +85                           | °C    |

| Storage Temperature                                  | T <sub>s</sub>   | -60 to +160                          | °C    |

| Junction Temperature                                 | T <sub>JC</sub>  | -40 to +150                          | °C    |

| Peak IR Reflow Temperature                           | T <sub>P</sub>   | 260                                  | °C    |

| ESD Protection Level (2)                             | V <sub>ESD</sub> | 2                                    | kV    |

#### Note:

- (1) Calculated from package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

- (2) Tested according to JEDEC standard JESD22-A114-B.

#### **Electrical Characteristics**

Unless otherwise noted:  $V_{IN} = 5V$ ,  $V_{OUT} = 3.3V$ ,  $EN = V_{IN}$ ,  $SYNC/PWM = V_{IN}$ ,  $MODE = V_{IN}$ ,  $T_A = -40$  to 85 °C. Typical values are at  $T_A = 25$  °C.

| Parameter                 | Symbol                 | Conditions                                                                                           | Min  | Тур          | Max          | Units |

|---------------------------|------------------------|------------------------------------------------------------------------------------------------------|------|--------------|--------------|-------|

| Input Voltage Range       | V <sub>IN</sub>        | V <sub>IN</sub> > V <sub>OUT</sub> + dropout                                                         | 2.7  |              | 5.5          | V     |

| VOUT Accuracy             | V <sub>OUT</sub>       | $I_{OUT} = 0.5A, T_A = 25^{\circ}C$<br>$V_{OUT} = 2.5/3.0/3.3/3.6V$                                  |      |              | ±1           | %     |

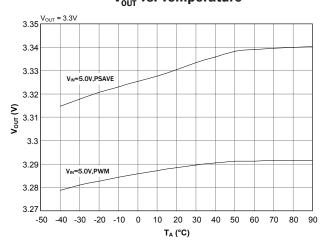

| VOUT Temperature Accuracy | $V_{OUT(T)}$           | $I_{OUT} = 0.5A, T_A = -40^{\circ}C \text{ to } 85^{\circ}C$                                         |      | ±0.3         | ±0.7         | %     |

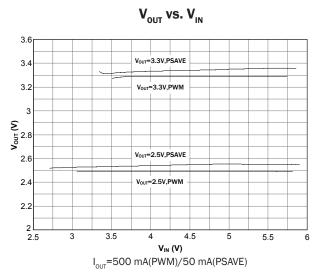

| Line Regulation           | V <sub>OUT LINE</sub>  | $V_{IN} = 2.7V$ to 5.5V, $V_{OUT} = 2.5V$ , $I_{OUT} = 0.5A$ , $T_{A} = -40^{\circ}\text{C}$ to 85°C |      | ±0.4         | ±0.65        | %     |

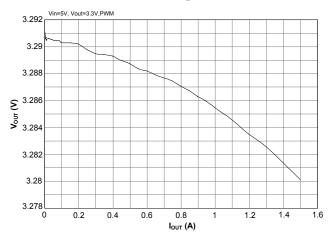

| Load Regulation (PWM)     | V <sub>OUT LOAD</sub>  | I <sub>OUT</sub> = 0A to 1A                                                                          |      | ±0.3         | ±0.65        | %     |

| PSAVE Regulation          | V <sub>OUT PSAVE</sub> | SYNC/PWM = GND, $C_{OUT}$ =22 $\mu$ F                                                                |      | +1.3<br>-0.3 | +1.6<br>-0.6 | %     |

| P-Channel On Resistance   | R <sub>DSP</sub>       | $I_{LX} = 100 \text{mA}, V_{IN} = 3.6 \text{V}$                                                      |      | 0.275        |              | Ω     |

| N-Channel On Resistance   | R <sub>DSN</sub>       | $I_{LX} = 100 \text{mA}, V_{IN} = 3.6 \text{V}$                                                      |      | 0.165        |              | Ω     |

| Start-Up Time             | T <sub>START</sub>     |                                                                                                      |      |              | 5            | ms    |

| P-Channel Current Limit   | I <sub>LIM(P)</sub>    | V <sub>IN</sub> = 2.7V to 5.5V                                                                       | 1.33 | 1.9          | 2.47         | А     |

# Electrical Characteristics (Cont.)

| Parameter                   | Symbol              | Conditions                                                                                  | Min  | Тур  | Max  | Units |

|-----------------------------|---------------------|---------------------------------------------------------------------------------------------|------|------|------|-------|

| Quiescent Current           | Ι <sub>α</sub>      | SYNC/PWM = GND, $I_{OUT} = 0A$ , $V_{OUT} = 1.04 \times V_{OUT(Programmed)}, V_{IN} = 3.6V$ |      | 17   | 28   | μA    |

| Shutdown Current            | I <sub>SD</sub>     | $EN = GND$ , $LX = OPEN$ , $V_{IN} = 3.6V$                                                  |      | 0.1  | 1    | μA    |

| LX Leakage Current PMOS     | I <sub>LXP</sub>    | V <sub>IN</sub> = 3.6V, LX = GND, EN = GND                                                  |      | 0.1  | 2    | μA    |

| LX Leakage Current NMOS     | I <sub>LXN</sub>    | V <sub>IN</sub> = 3.6V, LX = 3.6V, EN = GND                                                 | -2   | 0.1  |      | μA    |

| Oscillator Frequency        | f <sub>osc</sub>    | V <sub>IN</sub> = 3.6V                                                                      | 0.85 | 1.0  | 1.15 | MHz   |

| SYNC Frequency (upper)      | f <sub>SYNCU</sub>  | V <sub>IN</sub> = 3.6V                                                                      | 1.25 |      |      | MHz   |

| SYNC Frequency (lower)      | f <sub>SYNCL</sub>  | V <sub>IN</sub> = 3.6V                                                                      |      |      | 750  | kHz   |

| UVLO Threshold (upper)      | V <sub>UVL</sub>    |                                                                                             | 2.38 | 2.52 | 2.65 | V     |

| UVLO Hysteresis             | V <sub>UVLHYS</sub> |                                                                                             |      | 100  |      | mV    |

| Thermal Shutdown            | T <sub>SD</sub>     |                                                                                             |      | 145  |      | °C    |

| Thermal Shutdown Hysteresis | T <sub>SD-HYS</sub> |                                                                                             |      | 10   |      | °C    |

| Logic Input High            | V <sub>IH</sub>     | EN, SYNC/PWM, VID0, VID1, MODE                                                              | 1.6  |      |      | V     |

| Logic Input Low             | V <sub>IL</sub>     | EN, SYNC/PWM, VID0, VID1, MODE                                                              |      |      | 0.6  | V     |

| Logic Input Current High    | I <sub>IH</sub>     | EN, SYNC/PWM, VID0, VID1, MODE                                                              | -2   | 0.1  | 2    | μA    |

| Logic Input Current Low     | I <sub>IL</sub>     | EN, SYNC/PWM, VID0, VID1, MODE                                                              | -2   | 0.1  | 2    | μA    |

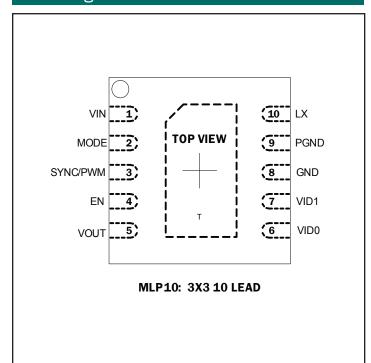

### Pin Configuration

### Ordering Information

| DEVICE                        | PACKAGE          |

|-------------------------------|------------------|

| SC194BMLTRT <sup>(1)(2)</sup> | MLP 3x3-10       |

| SC194BEVB                     | Evaluation Board |

#### Notes:

- 1) Lead-free packaging only. This product is fully WEEE and RoHS compliant.

- 2) Available in tape and reel only. A reel contains 3000 devices.

### Programmable Output Voltage

| VID1 | VID0 | SC194B V <sub>OUT</sub> |

|------|------|-------------------------|

| 0    | 0    | 2.5V                    |

| 0    | 1    | 3.0V                    |

| 1    | 0    | 3.3V                    |

| 1    | 1    | 3.6V                    |

### **Marking Information**

yy = two digit year of manufacture ww = two digit week of manufacture xxxx = lot number

# Pin Descriptions

| Pin # | Pin Name       | Pin Function                                                                                                                                                                                                    |

|-------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VIN            | Input power supply voltage                                                                                                                                                                                      |

| 2     | MODE           | MODE select pin where MODE = V <sub>IN</sub> to select 100% duty cycle function and MODE = GND to disable                                                                                                       |

| 3     | SYNC/PWM       | Oscillator synchronization input — Tie to $V_{\text{IN}}$ for forced PWM mode or GND to allow the part to enter PSAVE mode at light loads. Apply an external clock signal for frequency synchronization.        |

| 4     | EN             | Enable digital input — A high input enables the SC194B, a low disables and reduces quiescent current to less than 1µA. In shutdown, LX becomes high impedance.                                                  |

| 5     | VOUT           | Regulated output voltage and feedback for SC194B                                                                                                                                                                |

| 6     | VID0           | Logic level bit 0 is used in conjunction with VID1 to set the output voltage. Connect high or low as required to select the desired output voltage. If not connected, the output voltage will be indeterminate. |

| 7     | VID1           | Logic level bit 1 is used in conjunction with VID0 to set the output voltage. Connect high or low as required to select the desired output voltage. If not connected, the output voltage will be indeterminate. |

| 8     | GND            | Ground                                                                                                                                                                                                          |

| 9     | PGND           | Power Ground                                                                                                                                                                                                    |

| 10    | LX             | Inductor connection to the switching FETs                                                                                                                                                                       |

| Т     | THERMAL<br>PAD | Pad is for heatsinking purposes — not connected internally. Connect exposed pad to ground plane using multiple vias.                                                                                            |

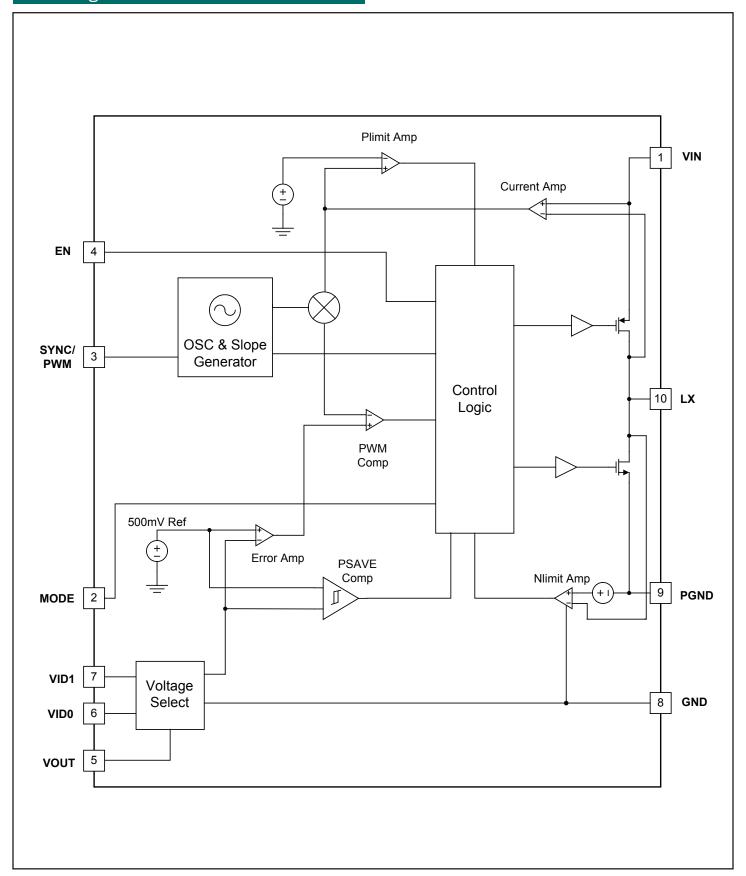

# Block Diagram

### **Applications Information**

#### **SC194B Detailed Description**

The SC194B is a synchronous step-down Pulse Width Modulated (PWM), DC-DC converter utilizing a 1MHz fixed-frequency current mode architecture. The device is designed to operate in fixed-frequency PWM mode across the full load range and can enter power save mode (PSAVE) utilizing Pulse Frequency Modulation (PFM) at light loads to maximize efficiency.

#### **Operation**

During normal operation the PMOS MOSFET is activated on each rising edge of the internal oscillator. Current feedback for the switching regulator is through the PMOS current path, and it is amplified and summed with the internal slope compensation network. The voltage feedback loop uses an internal feedback divider. The ontime is determined by comparing the summed current feedback and the output of the error amplifier. The period is set by the onboard oscillator or by an external clock attached to the SYNC/PWM pin.

The SC194B has an internal synchronous NMOS rectifier and does not require a Schottky diode on the LX pin.

#### **Programmable Output Voltage**

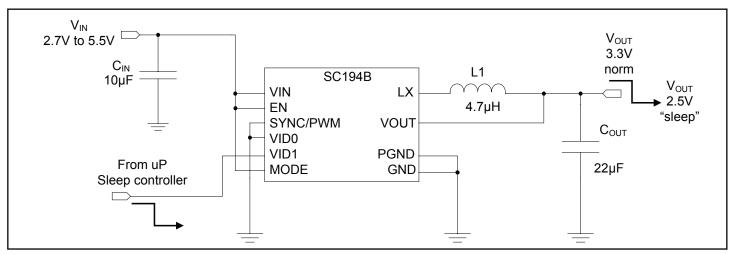

The SC194B has four pre-determined output voltage values which can be individually selected by the correct programming of the VIDO and VID1 pins (see Programmable Output Voltage table on Page 4). This eliminates the need for external programming resistors saving PCB area and inventory. The VID pins can be statically tied to GND or VIN for fixed output configurations or they may be driven by a microprocessor enabling the possibility of dynamic voltage adjustment for host equipment "sleep" states.

#### **Oscillator Synchronization Opotions**

The SC194B is designed to operate in continuous conduction, fixed-frequency mode. When the SYNC/PWM pin is tied high the part runs in PWM mode using the internal oscillator. The part can be synchronized to an external clock by driving a clock signal into the SYNC/PWM pin. The part synchronizes to the rising edge of the clock.

#### **Protection Features**

The SC194B provides the following protection features:

- Thermal shutdown

- Current limit

- Over-voltage protection

- Soft-start

#### **Thermal Shutdown**

The device has a thermal shutdown feature to protect the SC194B if the junction temperature exceeds 145°C. In thermal shutdown the on-chip power devices are disabled, tri-stating the LX output. Switching will resume when the temperature drops by 10°C. During this time if the output voltage decreases by more than 60% of its programmed value, a soft-start will be invoked.

#### **Current Limit**

The PMOS and NMOS power devices of the buck switcher stage are protected by current limit functions. In the case of a short to ground on the output, the part enters frequency foldback mode that causes the switching frequency to divide by a factor determined by the output voltage. This prevents the inductor current from "stair-casing".

#### Over-Voltage Protection

Over-voltage protection is provided on the SC194B. In the event of an over-voltage on the output in switcher mode, the PWM drive is disabled, tri-stating the LX output. The part will not resume switching until the output voltage has fallen below 2% of the regulation voltage.

#### Soft-Start

The soft-start mode is enabled after every shutdown cycle to limit in-rush current. In conjunction with the frequency foldback, this controls the maximum current during start-up. The PMOS current limit is stepped up through seven soft-start levels to the full value by a timer driven from the internal oscillator. During soft-start, the switching frequency is stepped by 1/8, 1/4, and 1/2 of the internal oscillator frequency up to the full value, under control of three output voltage thresholds. As soon as the output voltage is within 2% of the regulation voltage, soft-start mode is disabled.

#### **Power Save Mode Operation**

The PSAVE mode may be selected by tying the SYNC/PWM pin to GND. Selecting PSAVE mode will enable the SC194B to automatically activate/deactivate operation at light loads maximizing efficiency across the full load range. The SC194B automatically detects the load current at which it should enter PSAVE mode. The SC194B is optimized to track maximum efficiency with respect to  $V_{\text{INI}}$ .

#### Applications Information (Cont.)

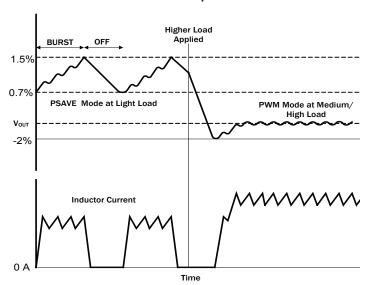

In PSAVE mode  $V_{\rm OUT}$  is driven from a lower level to an upper level by a switching burst. Once the upper level has been reached the switching is stopped and the quiescent current is reduced.  $V_{\rm OUT}$  falls from the upper to lower levels in this low current state as the load current discharges the output capacitor. The burst-to-off period in PSAVE will decrease as the load current reduces.

The PSAVE switching burst frequency is controlled so that the inductor current ripple is similar to that in PWM mode.

The SC194B automatically detects when to exit PSAVE mode by monitoring  $\rm V_{\rm out}$ . For the SC194B to exit PSAVE mode, the load must be increased, causing  $\rm V_{\rm out}$  to decrease until the power save exit threshold is reached. PSAVE levels are set high to minimize the undershoot when exiting PSAVE. The lower PSAVE comparator level is set +0.7% above  $\rm V_{\rm out}$ , and the upper comparator level at +1.5% above  $\rm V_{\rm out}$ , with the exit threshold at -2% below  $\rm V_{\rm out}$

If PSAVE operation is required then a  $22\mu F$  output capacitor must be used.

#### **Power Save Operation**

#### **100% Duty Cycle Operation**

The 100% duty cycle mode may be selected by connecting the MODE pin high. This will allow the SC194B to maintain output regulation under low input voltage/high output voltage conditions.

In 100% duty cycle operation, as the input supply drops toward the output voltage, the PMOS on-time increases linearly above the maximum value in fixed-frequency operation until the PMOS is active continuously. Once the PMOS is switched on continuously, the output voltage tracks the input voltage minus the voltage drop across the PMOS power device and inductor according to the following relationship:

$$V_{\text{out}} = V_{\text{in}} - I_{\text{out}} \cdot (R_{\text{dsp}} + R_{\text{ind}})$$

where,

$V_{OUT}$  = Output voltage  $V_{IN}$  = Input voltage  $I_{OUT}$  = Output current

R<sub>DSP</sub> = PMOS switch ON resistance R<sub>IND</sub> = Series resistance of the inductor

#### **Inductor Selection**

The SC194B is designed for use with a  $4.7\mu H$  inductor. The magnitude of the inductor current ripple is dependent on the inductor value and can be determined by the following equation:

$$\Delta I_{L} = \frac{V_{OUT}}{L \times f_{osc}} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

This equation demonstrates the relationship between input voltage, output voltage, and inductor ripple current.

The inductor should have a low DCR to minimize the conduction losses and maximize efficiency. As a minimum requirement, the DC current rating of the inductor should be equal to the maximum load current plus half of the inductor current ripple as shown by the following equation:

$$I_{L(PK)} = I_{\text{OUT(MAX)}} + \frac{\Delta I_L}{2}$$

### Applications Information (Cont.)

Final inductor selection will depend on various design considerations such as efficiency, EMI, size and cost. Table 1 lists the manufacturers of practical inductor options.

Table 1 — Recommended Inductors

| Manufacturer/Part No.        | Value<br>(µH) | DCR<br>(Ω) | Saturation<br>Current<br>(A) | Tolerance<br>( <u>+</u> %) | Dimensions<br>LxWxH<br>(mm) |

|------------------------------|---------------|------------|------------------------------|----------------------------|-----------------------------|

| BI Technologies<br>HM66304R7 | 4.7           | 0.072      | 1.32                         | 20                         | 4.7 × 4.7 ×3.0              |

| Coilcraft<br>D01608C-472ML   | 4.7           | 0.09       | 1.5                          | 20                         | 6.6 × 4.5 ×3.0              |

| TDK<br>VLCF4018T- 4R7N1R0-2  | 4.7           | 0.101      | 1.07                         | 30                         | 4.3 × 4.0 ×1.8              |

### $\mathbf{C}_{\scriptscriptstyle \mathrm{IN}}$ Selection

The source input current to a buck converter is non-continuous. To prevent large input voltage ripple a low ESR ceramic capacitor is required. A minimum value of  $10\mu F$  should be used for sufficient input voltage filtering and a  $22\mu F$  should be used for improved input voltage filtering.

### $\mathbf{C}_{\mathrm{out}}$ Selection

The internal compensation is designed to work with a certain output filter corner frequency defined by the equation:

$$\mathbf{f}_{\text{C}} = \frac{1}{2\pi\sqrt{L \times C_{\text{OUT}}}}$$

This single pole filter is designed to operate with a minimum output capacitor value of  $10\mu F$ . Larger output capacitor values will improve transient performance. If PSAVE operation is required the minimum capacitor value is  $22\mu F$ .

Output voltage ripple is a combination of the voltage ripple from the inductor current charging and discharging the output capacitor and the voltage created from the inductor current ripple through the output capacitor ESR. Selecting an output capacitor with a low ESR will reduce the output voltage ripple component, as can be seen in the following equation:

$$\Delta V_{OUT(ESR)} = \Delta I_{L(ripple)} \times ESR_{COUT}$$

Capacitors with X7R or X5R ceramic dielectric are strongly recommended for their low ESR and superior temperature and voltage characteristics. Y5V capacitors should not be used as their temperature coefficients make them unsuitable for this application. Table 2 lists the manufacturers of recommended capacitor options.

Table 2 — Recommended Capacitors

| Manufacturer/Part No.        | Value<br>(μF) | Rated<br>Voltage<br>(VDC) | Temperature<br>Characteristic | Case Size |

|------------------------------|---------------|---------------------------|-------------------------------|-----------|

| Murata<br>GRM21BR60J226ME39L | 22            | 6.3                       | X5R                           | 0805      |

| Murata<br>GRM188R60J106MKE19 | 10            | 6.3                       | X5R                           | 0603      |

| TDK<br>C2012X5R0J106K        | 10            | 6.3                       | X5R                           | 0603      |

Note: Where PSAVE operation is required  $22\mu F$  must be used for  $C_{out}$ .

### Applications Information (Cont.)

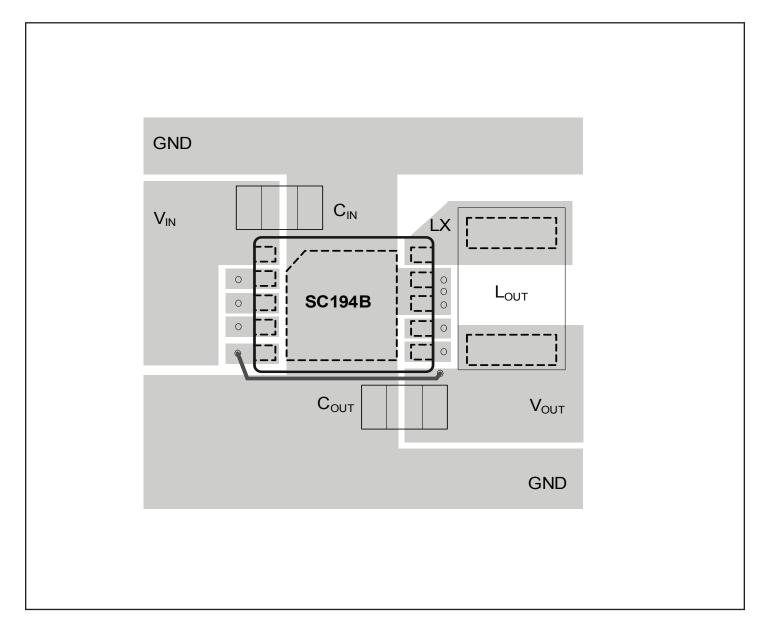

#### **PCB Layout Considerations**

Poor layout can degrade the performance of the DC-DC converter and can contribute to EMI problems, ground bounce and resistive voltage losses. Poor regulation and instability can result.

A few simple design rules can be implemented to ensure good layout:

- Place the inductor and filter capacitors as close to the device as possible and use short wide traces between the power components.

- 2. Route the output voltage feedback path away from the inductor and LX node to minimize noise and magnetic interference.

- Maximize ground metal on the component side to improve the return connection and thermal dissipation.

Separation between the LX node and GND should be maintained to avoid coupling of switching noise to the ground plane.

- 4. Use a ground plane with several vias connecting to the component side ground to further reduce noise interference on sensitive circuit nodes.

### **Typical Characteristics**

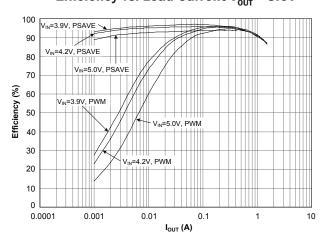

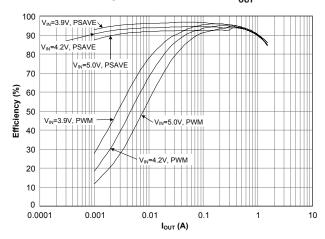

### Efficiency vs. Load Current $V_{out} = 3.6V$

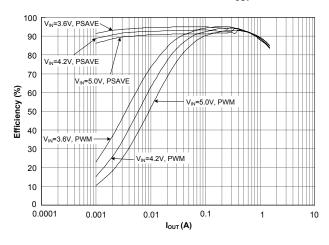

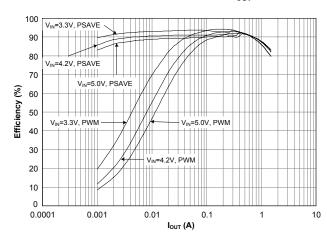

# Efficiency vs. Load Current $V_{\text{OUT}} = 3.0V$

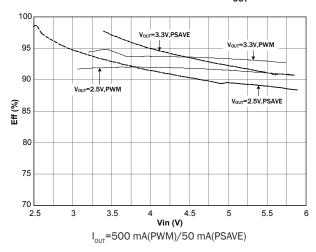

### Efficiency vs. Input Voltage $V_{OUT} = 3.3V$

### Efficiency vs. Load Current $V_{out} = 3.3V$

# Efficiency vs. Load Current $V_{OUT} = 2.5V$

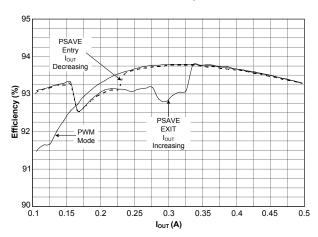

#### **PWM to PSAVE Hysteresis**

### **Typical Characteristics**

# V<sub>out</sub> vs. Temperature

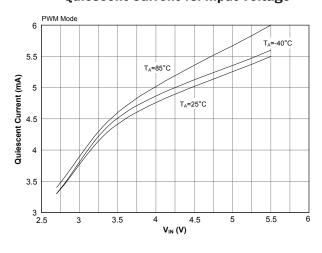

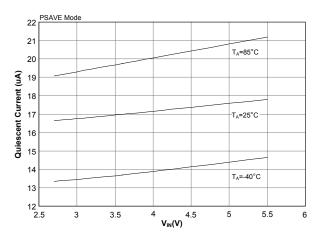

### **Quiescent Current vs. Input Voltage**

#### **Load Regulation**

#### **Quiescent Current vs. Input Voltage**

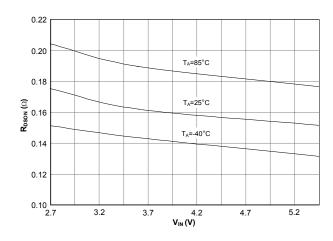

### N-Channel $R_{\rm DSON}$ vs. Input Voltage

### Typical Characteristics (Cont.)

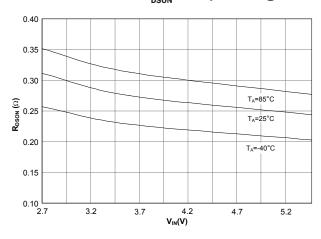

### P-Channel $R_{DSON}$ vs. Input Voltage

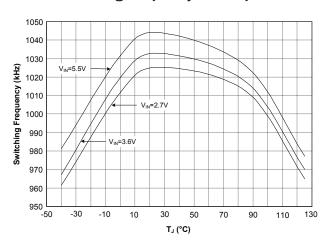

#### **Switching Frequency vs. Temperature**

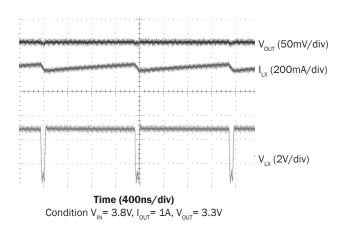

#### **100% Duty Cycle Mode**

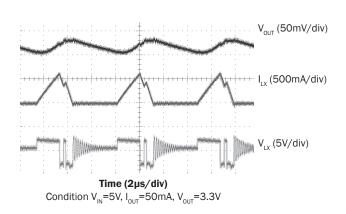

### **PSAVE Operation**

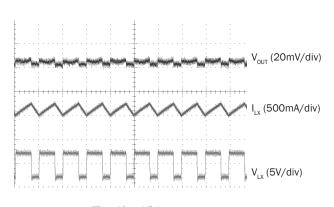

#### **PWM Operation**

$\label{eq:time of the condition V_IN} \begin{aligned} &\text{Time (1}\mu\text{s/div)}\\ &\text{Condition V}_{\text{IN}}\text{=}5\text{V, I}_{\text{OUT}}\text{=}50\text{mA, V}_{\text{OUT}}\text{=}3.3\text{V} \end{aligned}$

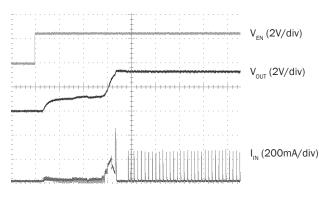

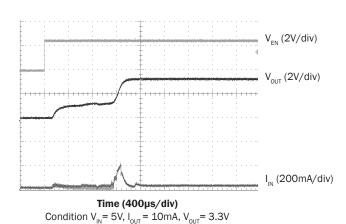

#### **PSAVE Start-UP**

### Typical Characteristics (Cont.)

#### **PWM Start-Up**

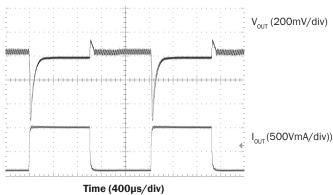

#### **Load Transient Response PSAVE**

**Time (400\mus/div)** Condition V<sub>IN</sub>= 5V, I<sub>OUT</sub> = 1A to 100mA, V<sub>OUT</sub> = 3.3V

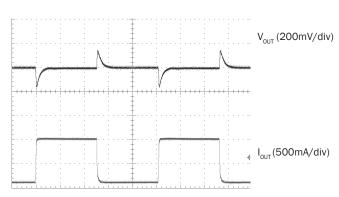

#### **Load Transient Response PWM**

Time (400 $\mu$ s/div) Condition V<sub>IN</sub>= 5V, I<sub>OUT</sub> = 1A to 100mA, V<sub>OUT</sub> = 3.3V

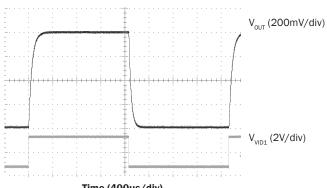

#### **VID Code Change PWM**

Time (400 $\mu$ s/div) Condition V<sub>IN</sub>= 5V, I<sub>OUT</sub> = 1A, V<sub>OUT</sub> = 2.5 to 3.3V

### Applications Circuits

### $V_{out}$ = 3.6V Forced PWM and 100% Duty Cycle

#### Dynamic Voltage Positioning for Reduced System Dissipation in "Sleep" Modes

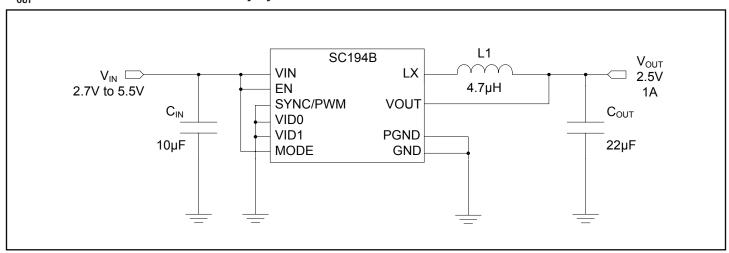

# $V_{\text{OUT}}$ = 2.5V with PSAVE and 100% Duty Cycle

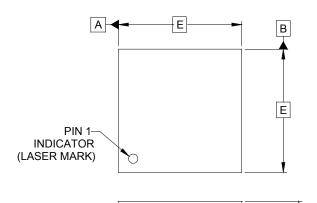

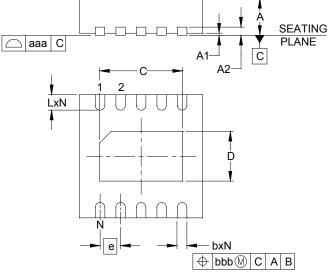

# Outline Drawing - MLP-10

| DIMENSIONS |      |        |      |             |        |      |  |  |

|------------|------|--------|------|-------------|--------|------|--|--|

| DIM        | 11   | NCHE   | S    | MILLIMETERS |        |      |  |  |

| ווועו      | MIN  | NOM    | MAX  | MIN         | NOM    | MAX  |  |  |

| Α          | .031 | -      | .039 | 0.80        | -      | 1.00 |  |  |

| A1         | .000 | -      | .002 | 0.00        | -      | 0.05 |  |  |

| A2         | -    | (800.) | -    | 1           | (0.20) | 1    |  |  |

| b          | .007 | .009   | .011 | 0.18        | 0.23   | 0.30 |  |  |

| С          | .074 | .079   | .083 | 1.87        | 2.02   | 2.12 |  |  |

| D          | .042 | .048   | .052 | 1.06        | 1.21   | 1.31 |  |  |

| Е          | .114 | .118   | .122 | 2.90        | 3.00   | 3.10 |  |  |

| е          | .0   | 020 BS | С    | C           | .50 BS | С    |  |  |

| L          | .012 | .016   | .020 | 0.30        | 0.40   | 0.50 |  |  |

| N          | 10   |        |      |             | 10     |      |  |  |

| aaa        | .003 |        |      |             | 0.08   |      |  |  |

| bbb        | .004 |        |      |             | 0.10   |      |  |  |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS TERMINALS.