# POWER MANAGEMENT Features

- V<sub>IN</sub> Range: 2.9 5.5V

- Preset V<sub>OUT</sub> Range: 1.0V to 3.3V

- Up to 2A Output Current

- Ultra-Small Footprint, <1mm Height</li>

- 1.5MHz Switching Frequency

- Selectable Forced PSAVE or Forced PWM Operation

- Efficiency Up to 95%

- Low Output Noise Across Load Range

- Excellent Transient Response

- Start Up into Pre-Bias Output

- 100% Duty-Cycle Low Dropout Operation

- <1µA Shutdown Current</p>

- Externally Programmable Soft-Start Time

- Power Good indicator

- Input Under-Voltage Lockout

- Output Over-Voltage, Current Limit Protection

- Over-Temperature Protection

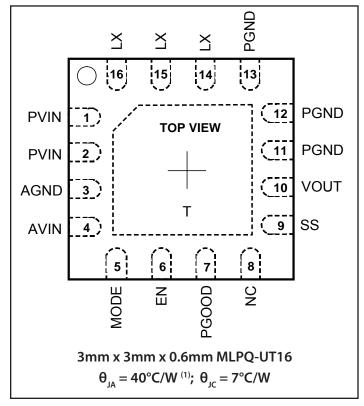

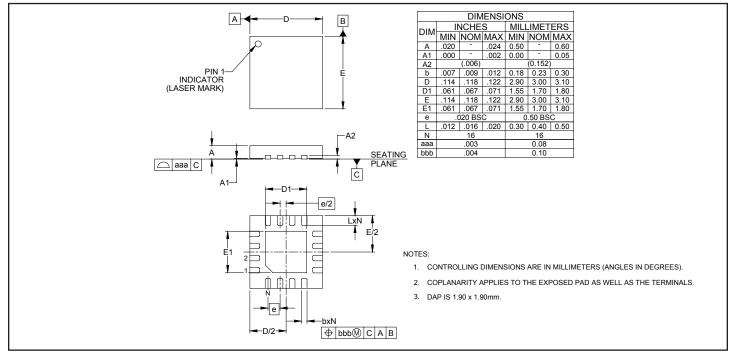

- 3mm x 3mm x 0.6mm thermally enhanced MLPQ-UT16 package

- -40 to +85°C Temperature Range

- Pb-free, Halogen free, and RoHS/WEEE compliant

# **Applications**

- Office Automation

- Switches and Routers

- Network Cards

- LCD TV

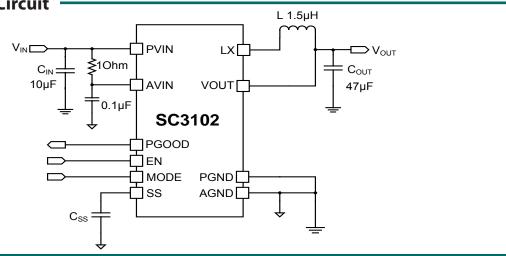

# **Typical Application Circuit**

# SC3102 2A Synchronous Step-Down Regulator

# Description

The SC3102 is a 2A synchronous step-down regulator designed to operate with an input voltage range of 2.9V to 5.5V. The device requires minimal external components for a complete step down regulator solution. The output voltage is factory predetermined with an available range of 1.0V to 3.3V.

The SC3102 is optimized for maximum efficiency over a wide range of load currents. During full load operation, the SC3102 operates in forced PWM mode with a fixed 1.5MHz oscillator frequency, allowing the use of small surface mount external components. As the load decreases, the regulator has the option to transition, via the MODE pin, into forced Power Save mode to maximize efficiency or to stay in forced PWM mode.

The SC3102 offers output short circuit and thermal protection to safe guard the device under extreme operating conditions. The enable pin provides on/off control of the regulator. When connected to logic low, the device enters shutdown and consumes less than  $1\mu$ A of current. Other protection features include programmable soft-start with Power Good indicator, over voltage protection and under voltage lockout.

The SC3102 is available in a thermally-enhanced, 3mm x 3mm x 0.6mm MLPQ-UT16 package and has a rated temperature range of -40 to  $+85^{\circ}$ C.

# **Pin Configuration**

# **Ordering Information**

| Device                            | Package                     |

|-----------------------------------|-----------------------------|

| SC3102xULTRT <sup>(2)(3)(4)</sup> | 3mm x 3mm x 0.6mm MLPQ-UT16 |

| SC3102xEVB <sup>(5)</sup>         | Evaluation Board            |

Notes:

(1) Calculated from package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

- (2) Available in tape and reel only. A reel contains 3,000 devices.

- (3) Device is Pb-free, Halogen free, and RoHS/WEEE compliant.

- (4) "x" is the code of the output voltage. See Table 1 for the code. For example, the device number for VOUT= 1.50V is SC3102HULTRT.

- (5) "x" is the code of the output voltage. See Table 1 for the code. For example, the EVB with VOUT= 1.50V is SC3102HEVB.

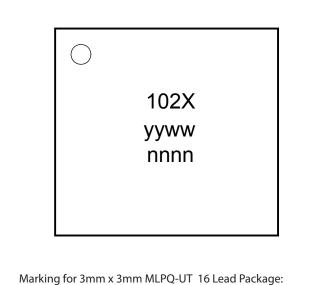

# **Marking Information**

x = Code of the output voltage (Example: H for VOUT=1.50V) yyww = Datecode (Example: 0852)nnnn = Semtech Lot number (Example: E901)

# **Table 1: Available Output Voltages**

| Code | VOUT <sup>(6)</sup> |

|------|---------------------|

| D    | 1.10                |

| E    | 1.20                |

| Н    | 1.50                |

Notes:

(6) Contact Semtech marketing for alternative output voltage options.

### **Absolute Maximum Ratings**

| PVIN and AVIN Supply Voltages0.3 to 6.0V          |

|---------------------------------------------------|

| LX Voltage <sup>(9)</sup>                         |

| VOUT Voltage                                      |

| CTLx pins Voltages0.3 to AVIN+0.3V                |

| Peak IR Reflow Temperature                        |

| ESD Protection Level $^{\scriptscriptstyle{(8)}}$ |

### **Recommended Operating Conditions**

| Supply Voltage PVIN and AVIN                         |  |  |  |  |

|------------------------------------------------------|--|--|--|--|

| Maximum DC Output Current 2.0                        |  |  |  |  |

| Maximum DC Output Current in Forced PSAVE Mode 0.35A |  |  |  |  |

| Temperature Range40 to +85 °C                        |  |  |  |  |

| Input Capacitor                                      |  |  |  |  |

| Output Capacitor                                     |  |  |  |  |

| Output Inductor $1.5 \ \mu H$                        |  |  |  |  |

### **Thermal Information**

| Thermal Resistance, Junction to Ambient <sup>(7)</sup> | 40 °C/W |

|--------------------------------------------------------|---------|

| Thermal Resistance, Junction to Case                   | 7 °C/W  |

| Maximum Junction Temperature                           | +150°C  |

| Storage Temperature Range                              | +150 °C |

Exceeding the absolute maximum ratings may result in permanent damage to the device and/or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

Notes:

- (7) Calculated from package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

- (8) Tested according to JEDEC standard JESD22-A114-B.

- (9) Due to parasitic board inductance, the transient LX pin voltage at the point of measurement may appear larger than that which exists on silicon. The device is designed to tolerate the short duration transient voltages that will appear on the LX pin due to the deadtime diode conduction, for inductor currents up to the current limit setting of the device.

# Electrical Characteristics -

Unless specified: PVIN= AVIN= 5.0V, VOUT= 1.50V,  $C_{IN}$ = 10µF,  $C_{OUT}$ = 2 x 22µF; L= 1.5µH; -40°C ≤ T<sub>J</sub> ≤ +125 °C; Unless otherwise noted typical values are T<sub>A</sub>= +25 °C.

| Parameter                                      | Symbol                | Conditions                                               | Min   | Тур  | Мах   | Units |

|------------------------------------------------|-----------------------|----------------------------------------------------------|-------|------|-------|-------|

|                                                | UVLO                  | Rising AVIN, PVIN=AVIN                                   | 2.70  | 2.80 | 2.90  | V     |

| Under-Voltage Lockout                          |                       | Hysteresis                                               |       | 300  |       | mV    |

| Output Voltage Tolerance <sup>(10)</sup>       | Δν <sub>ουτ</sub>     | PVIN= AVIN= 2.9 to 5.5V; I <sub>OUT</sub> =0A            | -1.25 |      | +1.25 | %     |

| Current Limit                                  | I                     | Peak LX current                                          | 2.5   | 3.0  | 3.75  | А     |

| Supply Current                                 | Ι <sub>Q</sub>        | No load, MODE= High                                      |       | 12   |       | mA    |

|                                                |                       | No load, MODE= Low                                       |       | 60   |       | μΑ    |

| Shutdown Current                               | I <sub>shdn</sub>     | EN= AGND                                                 |       | 1    | 10    | μΑ    |

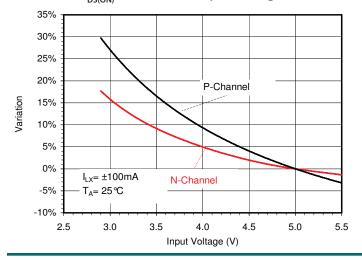

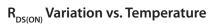

| High Side Switch Resistance <sup>(11)</sup>    | R <sub>DSON_P</sub>   | I <sub>LX</sub> = 100mA, T <sub>J</sub> = 25 °C          |       | 50   | 85    |       |

| Low Side Switch Resistance <sup>(11)</sup>     | R <sub>DSON_N</sub>   | I <sub>LX</sub> = -100mA, Τ <sub>J</sub> = 25 °C         |       | 35   | 60    | mΩ    |

| L <sub>x</sub> Leakage Current <sup>(11)</sup> | I <sub>LK(LX)</sub>   | PVIN= AVIN= 5.5V; LX= 0V; EN= AGND                       |       | 1    | 10    | μΑ    |

|                                                |                       | PVIN= AVIN= 5.5V; LX= 5.0V; EN= AGND                     | -20   | -1   |       |       |

| Load Regulation                                | $\Delta V_{LOAD-REG}$ | PVIN= AVIN= 5.0V, MODE=High, I <sub>our</sub> =1mA to 2A |       | ±0.3 |       | %     |

| Oscillator Frequency                           | f <sub>osc</sub>      |                                                          | 1.275 | 1.5  | 1.725 | MHz   |

| Soft-Start Charging Current <sup>(11)</sup>    | I <sub>ss</sub>       |                                                          |       | +5   |       | μA    |

| Foldback Holding Current                       | I <sub>CL_HOLD</sub>  | Average LX Current                                       |       | 1    |       | A     |

# **Electrical Characteristics (continued)**

| Parameter                                | Symbol                | Conditions                             | Min  | Тур | Мах | Units |

|------------------------------------------|-----------------------|----------------------------------------|------|-----|-----|-------|

| Forced PSAVE Mode Current                |                       | Maximum output current loading         | 350  |     |     | mA    |

| Impedence of PGOOD Low                   | R <sub>pgood_lo</sub> |                                        |      | 10  |     | Ω     |

| PGOOD Threshold                          | V <sub>pg_th</sub>    | VOUT rising                            |      | 90  |     | %     |

| PGOOD Delay                              | N/                    | Asserted                               |      | 2   |     | ms    |

|                                          | V <sub>PG_DLY</sub>   | PGOOD= Low                             |      | 20  |     | μs    |

| EN Delay                                 | t <sub>en_DLY</sub>   | From EN Input High to SS starts rising |      | 50  |     | μs    |

| EN Input Current <sup>(11)</sup>         | I <sub>en</sub>       | EN=AVIN or AGND                        | -2.0 |     | 2.0 | μA    |

| EN Input High Threshold                  | V <sub>EN_HI</sub>    |                                        | 1.2  |     |     | V     |

| EN Input Low Threshold                   | V <sub>EN_LO</sub>    |                                        |      |     | 0.4 | V     |

| MODE Input Current <sup>(11)</sup>       | I <sub>MODE</sub>     | MODE= AVIN or AGND                     | -2.0 |     | 2.0 | μA    |

| MODE Input High Threshold                | V <sub>MODE_HI</sub>  |                                        | 1.2  |     |     | V     |

| MODE Input Low Threshold                 | V <sub>MODE_LO</sub>  |                                        |      |     | 0.4 | V     |

| V <sub>out</sub> Over Voltage Protection | V <sub>OVP</sub>      |                                        | 110  | 115 | 120 | %     |

| Thermal Shutdown Temperature             | T <sub>sD</sub>       |                                        |      | 160 |     | °C    |

| Thermal Shutdown Hysteresis              | T <sub>SD_HYS</sub>   |                                        |      | 10  |     | °C    |

Notes:

(10) The "Output Voltage Tolerance" includes output voltage accuracy, voltage drift over temperature and line regulation.

(11) A negative current means the current flows into the pin and a positive current means the current flows out from the pin.

# **Pin Descriptions**

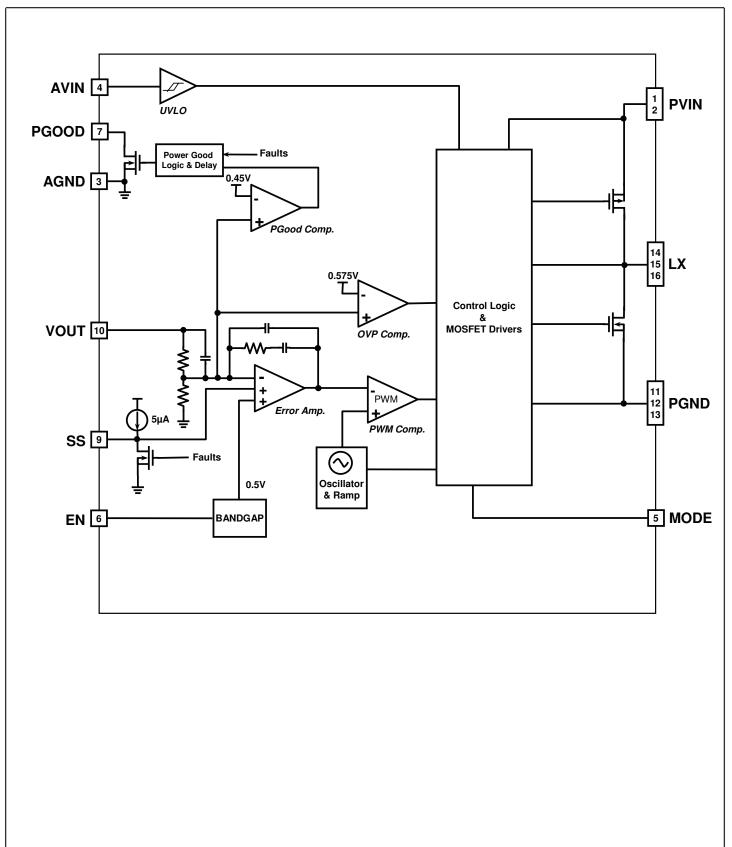

| Pin #    | Pin Name    | Pin Function                                                                                                                                                                                                                                                                                                                                                        |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,2      | PVIN        | Input supply voltage for the converter power stage.                                                                                                                                                                                                                                                                                                                 |

| 3        | AGND        | Ground connection for the internal circuitry. AGND needs to be connected to PGND directly.                                                                                                                                                                                                                                                                          |

| 4        | AVIN        | Power supply for the internal circuitry. AVIN is required to be connected to PVIN through an R-C filter of $1\Omega$ and 100nF.                                                                                                                                                                                                                                     |

| 5        | MODE        | MODE select pin. When connected to logic high, the device operates in forced PWM mode. When connected to logic low, it operates in forced PSAVE mode at light load. The MODE pin has a 500k $\Omega$ internal pulldown resistor. This resistor is switched in circuit whenever the MODE pin is "Low" or when the part is in undervoltage lockout or disabled.       |

| 6        | EN          | Enable pin. When connected to logic high or tied to the AVIN pin, the SC3102 is on. When connected to logic low, the device enters shutdown and consumes less than 1µA current (typ.). The enable pin has a $500k\Omega$ internal pulldown resistor. This resistor is switched in circuit whenever the EN pin is "Low" or when the part is in undervoltage lockout. |

| 7        | PGOOD       | Power good indicator. When the output voltage reaches the PGOOD threshold, this pin will be open-drain (after the PGOOD delay), otherwise it is pulled low internally.                                                                                                                                                                                              |

| 8        | NC          | No connection.                                                                                                                                                                                                                                                                                                                                                      |

| 9        | SS          | Soft-Start. Connect a soft-start capacitor to program the soft-start time. There is a 5µA charging current flow-<br>ing out of the pin.                                                                                                                                                                                                                             |

| 10       | VOUT        | Output voltage sense pin.                                                                                                                                                                                                                                                                                                                                           |

| 11,12,13 | PGND        | Ground connection for converter power stage.                                                                                                                                                                                                                                                                                                                        |

| 14,15,16 | LX          | Switching node - connect an inductor between this pin and the output capacitor.                                                                                                                                                                                                                                                                                     |

| Т        | Thermal Pad | Thermal pad for heatsinking purposes. Connection to PGND is recommended. It is not connected internally.                                                                                                                                                                                                                                                            |

# **Block Diagram**

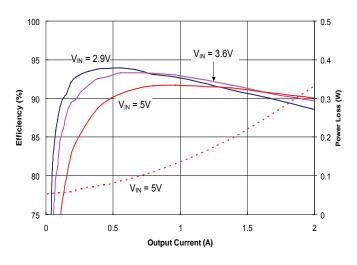

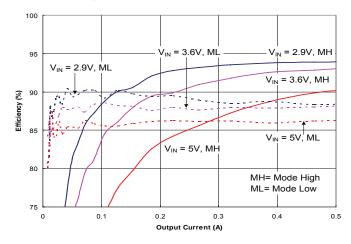

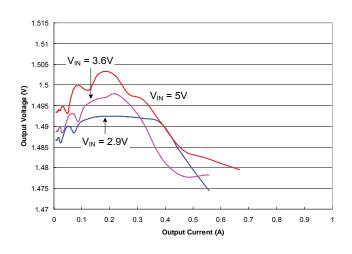

# **Typical Characteristics**

Circuit Conditions:  $C_{IN} = 10\mu F/6.3V$ ,  $C_{OUT} = 2 \times 22\mu F/6.3V$ ,  $C_{ss} = 2.2nF$ ,  $L = 1.5\mu H$ .

Efficiency and Power Loss: MODE = High

Efficiency Comparison: MODE - High vs Low

R<sub>DS(ON)</sub> Variation vs. Input Voltage

Load Regulation: MODE = Low

1

Output Current (A)

Load Regulation: MODE = High

V<sub>IN</sub> = 3.6V

1.5

2

1.515

1.51

1.505

1.5

1 4 9 5

1.49

1.485

0

V<sub>IN</sub> = 5V

V<sub>IN</sub> = 2.9V

0.5

Output Voltage (V)

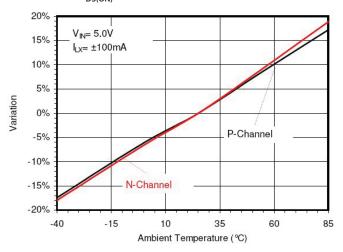

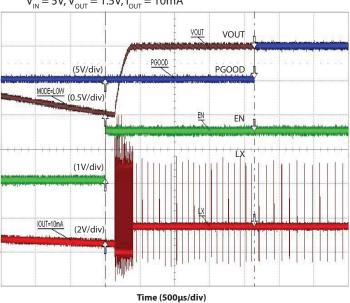

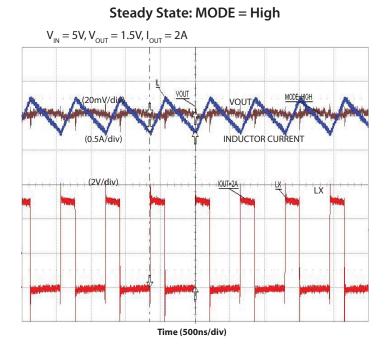

# **Typical Waveforms**

Circuit Conditions:  $C_{IN} = 10\mu F/6.3V$ ,  $C_{OUT} = 2 \times 22\mu F/6.3V$ ,  $C_{ss} = 2.2nF$ ,  $L = 1.5\mu H$ .

IOUT=50mA

(1V/div)

(2V/div)

Time (500µs/div)

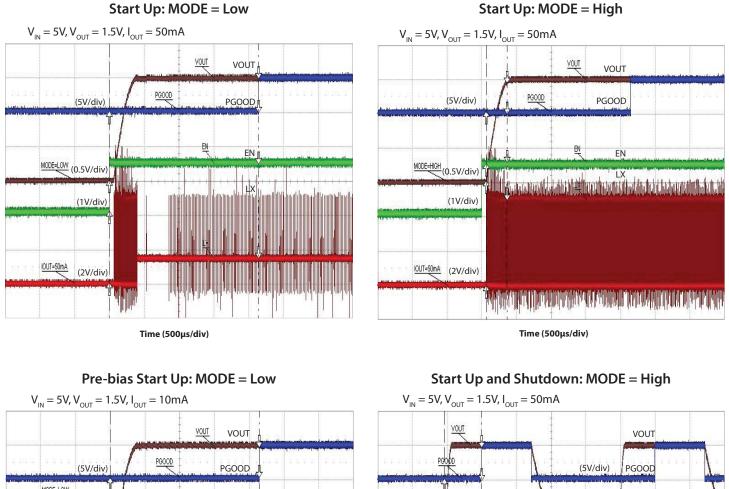

# **Typical Waveforms (continued)**

Circuit Conditions:  $C_{IN} = 10\mu F/6.3V$ ,  $C_{OUT} = 2 \times 22\mu F/6.3V$ ,  $C_{SS} = 2.2nF$ ,  $L = 1.5\mu H$ .

Time (500ns/div)

Steady State: MODE = Low

Time (1µs/div)

#### Steady State: MODE = Low

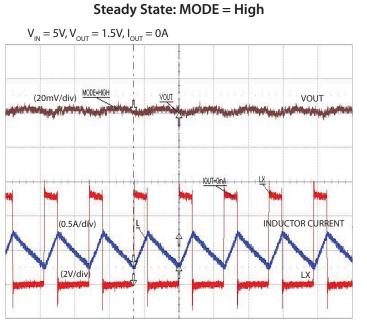

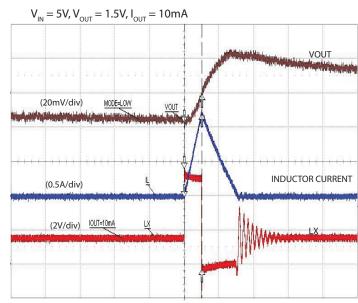

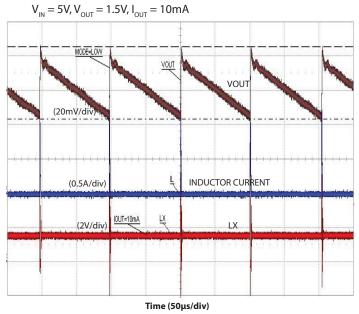

# **Typical Waveforms (continued)**

Circuit Conditions:  $C_{IN} = 10\mu F/6.3V$ ,  $C_{OUT} = 2 \times 22\mu F/6.3V$ ,  $C_{ss} = 2.2nF$ ,  $L = 1.5\mu H$ .

Time (500µs/div)

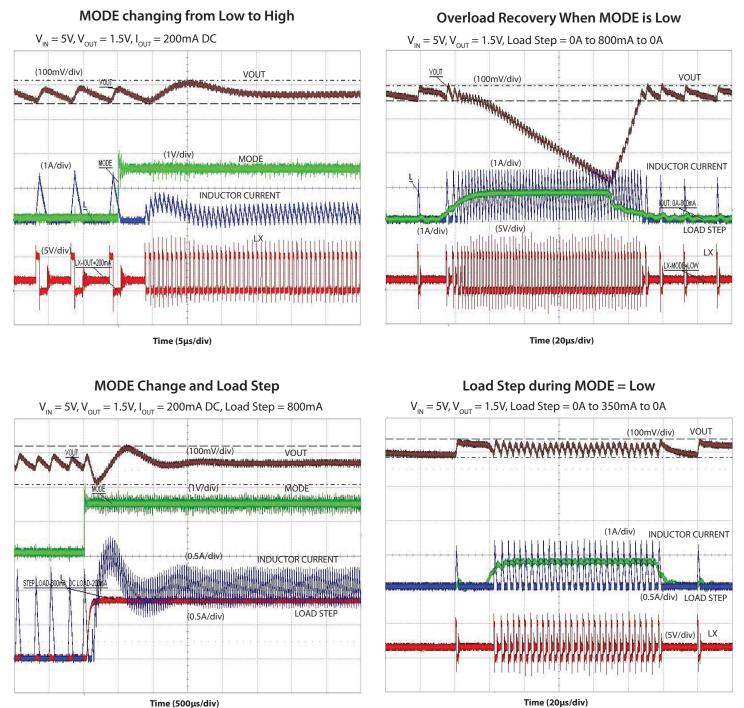

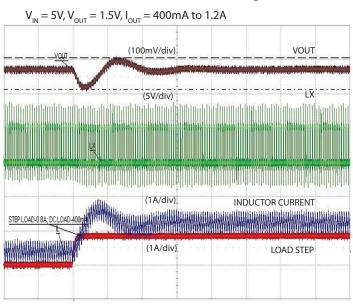

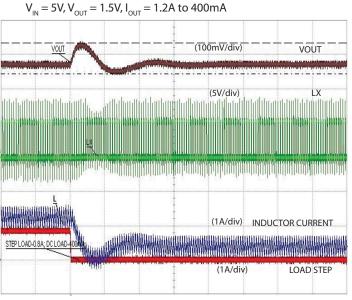

# **Typical Waveforms (continued)**

Circuit Conditions:  $C_{IN} = 10\mu$ F/6.3V,  $C_{OUT} = 2 \times 22\mu$ F/6.3V,  $C_{ss} = 2.2$ nF, L= 1.5 $\mu$ H.

Load Transient: MODE = High

Time (10µs/div)

### Load Transient: MODE = High

Time (10µs/div)

#### ....e (Jµ3/uiV)

#### **Detailed Description**

The SC3102 is a synchronous step-down Pulse Width Modulated (PWM), DC-DC converter utilizing a 1.5MHz fixed-frequency voltage mode architecture. The device is designed to operate in fixed-frequency PWM mode and has the option to enter forced power save mode (PSAVE) at light loads to improve efficiency. The switching frequency is chosen to minimize the size of the external inductor and capacitors while maintaining high efficiency.

#### Operation

During normal operation, the PMOS MOSFET is activated on each rising edge of the internal oscillator. The period is set by the onboard oscillator when in PWM mode. The device has an internal synchronous NMOS rectifier and does not require a Schottky diode on the LX pin. The device operates as a buck converter in PWM mode with a fixed frequency of 1.5MHz at medium to high loads. The MODE input is used to select between forced PWM and forced PSAVE modes. To improve the efficiency at light loads, the MODE pin can be set low to force PSAVE operation. When the MODE pin is held high, the device operates in forced continuous PWM mode regardless of the output load condition.

#### **Forced Power Save Mode Operation**

Connect the MODE pin to ground to force PSAVE mode. The maximum load current supported in forced PSAVE mode is 350mA.

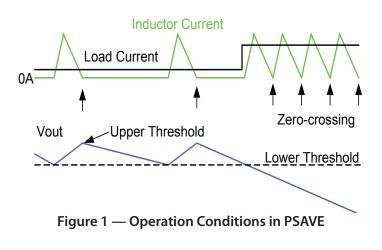

#### **Operation in PSAVE:**

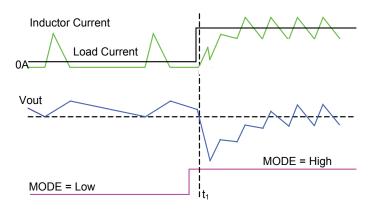

When the MODE pin toggles low, SC3102 operates in PSAVE mode after waiting for 64 switching cycles. Figure 1 shows the operating conditions in this mode. When the output current is less than 350mA, the switching frequency depends upon the load, and the output voltage does not fall below its regulation threshold. When the output current is higher than 350mA, the switching frequency depends upon the zero current crossing timing and the output voltage droops below its regulation threshold. The output voltage recovers when the load current is less than 350mA.

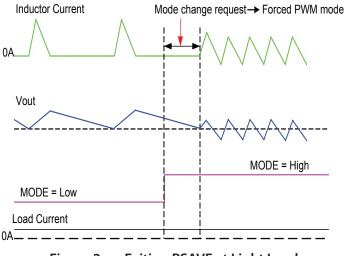

#### Exiting from PSAVE:

Figure 2 shows the case of no change in the output current and the MODE pin toggling from low to high. SC3102 enters PWM mode at the end of the PSAVE cycle, where the output voltage crosses the lower PSAVE threshold.

Figure 2 — Exiting PSAVE at Light Load

Figure 3 shows the behavior when there is a step increase in output current right after the MODE pin toggles high. The output voltage decreases initially due to the output capacitor supplying the load current. SC3102 changes the operation to PWM mode at  $t_1$  and recovers the output voltage.

Figure 3 — Exiting PSAVE with Heavy Load

### **Protection Features**

The SC3102 provides the following protection features:

- Current Limit

- Over-Voltage Protection

- Soft-Start Operation

- Thermal Shutdown

- UVLO

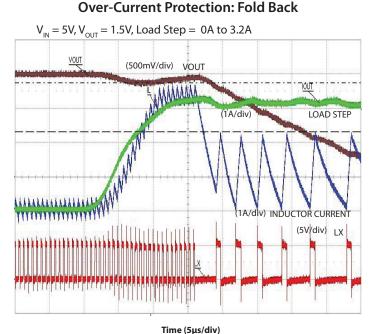

### **Current Limit & OCP**

The internal PMOS power device in the switching stage is protected by a current limit feature. If the inductor current is above the PMOS current limit for 8 consecutive cycles, the part enters foldback current limit mode and the output current is limited to the current limit holding current (I<sub>CL HOLD</sub>) which is approximately 900mA. Under this condition, the output voltage will be the product of I<sub>CL HOLD</sub> and the load resistance. When the load presented falls below the current limit holding level, the output will charge to the upper PSAVE voltage threshold and return to normal operation. The SC3102 is capable of sustaining an indefinite short circuit without damage. During soft-start, if current limit has occurred before the SS voltage has reached 400mV, the part enters foldback current limit mode. Foldback current limit mode will be disabled during soft-start after the SS voltage is higher than 400mV.

#### **Over-Voltage Protection**

In the event of a 15% over-voltage on the output, the PWM drive is disabled with the LX pin floating. Switching does not resume until the output voltage falls below the nominal Vout regulation voltage.

#### Soft-Start

The soft-start mode is activated after AVIN reaches it's UVLO voltage threshold and EN is set high to enable the part. A thermal shutdown event will also activate the softstart sequence. The soft-start mode controls the slew-rate of the output voltage during startup thus limiting in-rush current on the input supply. During start up, the reference voltage for the error amplifier is clamped by the voltage on the SS pin. The output voltage slew rate during softstart is determined by the value of the external capacitor connected to the SS pin and the internal 5µA charging current. The SC3102 requires a minimum soft-start time from enable to final regulation in the order of 200µs, including the 50µs enable delay. As a result the soft-start capacitor, Css, should be higher than 1.5nF. During start up, the chip operates in forced PWM mode. The value of Css for the desired soft-start time, tss, can be determined by Equation 1.

$$t_{ss} = C_{ss} \times \frac{0.5V}{5\mu A} \tag{1}$$

The SC3102 is capable of starting up into a pre-biased output. When the output is pre-charged by another supply rail, the SC3102 will not discharge the output during the soft-start period.

#### **Thermal Shutdown**

The device has a thermal shutdown feature to protect the SC3102 if the junction temperature exceeds 160°C. During thermal shutdown, the on-chip power devices are disabled, floating the LX output. When the temperature drops by 10°C, it will initial a soft-start cycle to resume normal operation.

#### **Under-Voltage Lockout**

Under-Voltage Lockout (UVLO) is enabled when the input voltage drops below the UVLO threshold. This prevents the device from entering an ambiguous state in which regulation cannot be maintained. Hysteresis of approximately 300mV is included to prevent chattering near the threshold. When the AVIN voltage rises back to the turn-on threshold and EN is high, a soft-start sequence is initiated.

#### **Power Good**

The power good (PGOOD) is an open-drain output. When

the output voltage drops below 10% of nominal, the PGOOD pin is pulled low after a 20µs delay. During startup, PGOOD will be asserted 2ms (typical) after the output voltage reaches 90% of the final regulation voltage. The faults of over voltage, fold-back current limit mode and thermal shutdown will force PGOOD low after a 20µsdelay. When recovering from a fault, PGOOD will be asserted 2ms (typical) after Vout reaches 90% of the final regulation voltage.

#### Enable

The EN input is used to enable or disable the device when the device is not in UVLO. When EN is low (grounded), the device enters shutdown mode and consumes less than 1µA of current. In shutdown mode, the device tri-states the LX pin and pulls down the SS pin. The EN pin has a 500k $\Omega$  internal pull-down resistor. This resistor is switched in circuit whenever the EN pin is below its threshold, or when the device is in under voltage lockout and AVIN exceeds 0.8V. When the device is enabled, it takes about 50µs for the internal circuitry to wake up and begin the soft-start sequence.

#### **100% Duty-Cycle Operation**

The SC3102 is capable of operating at 100% duty-cycle. When the difference between the input voltage and output voltage is less than the minimum dropout voltage, the PMOS switch turns completely on, operating in 100% duty-cycle. The minimum dropout voltage is the output current multiplied by the on-resistance of the internal PMOS switch and the DC-resistance of the inductor when the PMOS switch is on continuously.

#### **Output L-C filter Selection**

The SC3102 has fixed internal loop-gain compensation. It is optimized for X5R or X7R ceramic output capacitors and an output L-C filter corner frequency of less than 34kHz. The output L-C corner frequency can be determined by Equation 2.

$$f_C = \frac{1}{2\pi\sqrt{L \cdot C_{OUT}}} \tag{2}$$

In general, the inductor is chosen to set the inductor ripple current to approximately 30% of the maximum output current. It is recommended to use a typical inductor value of 1 $\mu$ H to 2.2 $\mu$ H with output ceramic capacitors of 44 $\mu$ F or higher. Lower inductance should be considered

in applications where faster transient response is required. More output capacitance will reduce the output deviation for a particular load transient. When using low inductance, the maximum peak inductor current at any condition (normal operation and start up) can not exceed 2.5A which is the guaranteed minimum current limit. The saturation current rating of the inductor needs to be at least larger than the peak inductor current which is the maximum output current plus half of the inductor ripple current.

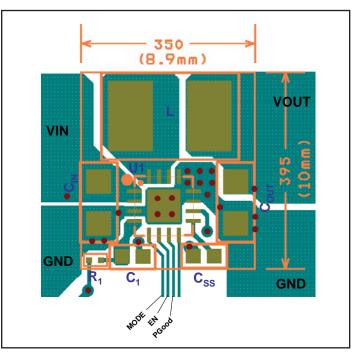

#### **PCB Layout Considerations**

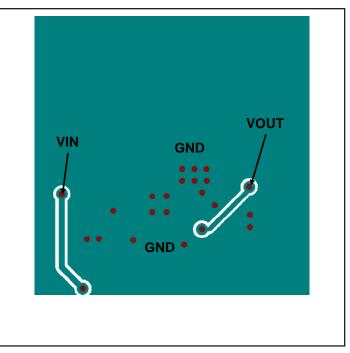

The layout diagram in Figure 4 shows a recommended top-layer PCB for the SC3102 and supporting components. Figure 5 shows the bottom layer for this PCB. Fundamental layout rules must be followed since the layout is critical for achieving the performance specified in the Electrical Characteristics table. Poor layout can degrade the performance of a DC-DC converter and can contribute to EMI problems, ground bounce, and resistive voltage losses. Poor regulation and instability can result.

The following guidelines are recommended when developing a PCB layout:

- The input capacitor, C<sub>IN</sub> should be placed as close to the PVIN and PGND pins as possible. This capacitor provides a low impedance loop for the pulsed currents present at the buck converter's input. Use short wide traces to connect as closely to the IC as possible. This will minimize EMI and input voltage ripple by localizing the high frequency current pulses.

- Keep the LX pin traces as short as possible to minimize pickup of high frequency switching edges to other parts of the circuit. C<sub>out</sub> and L should be connected as close as possible between the LX and PGND pins, with a direct return to the PGND pin from C<sub>out</sub>.

- 3. Route the output voltage feedback/sense path away from the inductor and LX node to minimize noise and magnetic interference.

- 4. Use a ground plane referenced to the SC3102 PGND pin. Use several vias to connect to the component side ground to further reduce noise and interference on sensitive circuit nodes.

- 5. If possible, minimize the resistance from the VOUT and PGND pins to the load. This will reduce the voltage drop on the ground plane and improve the load regulation. And it will also improve the overall efficiency by reducing the copper losses on the output and ground planes.

Figure 4 — Recommended PCB Layout (Top Layer)

Figure 5 — Bottom Layer Detail

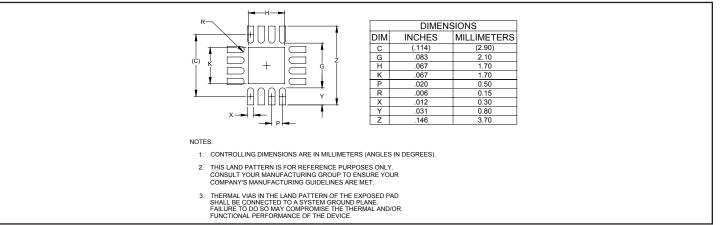

# Outline Drawing – 3x3 MLPQ-UT16

# Land Pattern – 3x3 MLPQ-UT16