# Si4362-C

Si4362

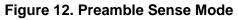

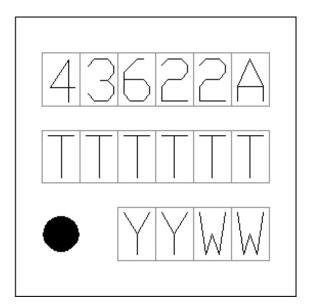

14 SDI

13 SDO

12 SCLK

11 nIRQ

## HIGH-PERFORMANCE, LOW-CURRENT RECEIVER

#### Features

- Frequency range = 142-1050 MHz

- Receive sensitivity = -129 dBm

- Modulation

- (G)FSK, 4(G)FSK, (G)MSK

- OOK

- Low active power consumption RX 129 byte FIFO

- 10/13 mA RX

- Ultra low current powerdown modes

- 30 nA shutdown, 40 nA standby

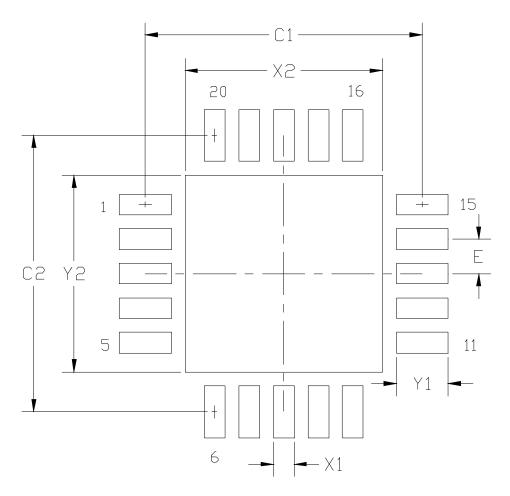

- Preamble Sense Mode

- 6 mA average Rx current at 1.2 kbs

- Fast preamble detection

- 1 byte preamble detection

- Fast wake and hop times

- Power supply = 1.8 to 3.8 V

### **Applications**

- Smart metering (802.15.4g and MBus)

Remote keyless entry

- Remote control

- Home security and alarm

- Telemetry

- Garage and gate openers

- Excellent selectivity performance • 69 dB adjacent channel

- 79 dB blocking at 1 MHz

- Antenna diversity and T/R switch control

- Highly configurable packet handler

- Auto frequency control (AFC)

- Automatic gain control (AGC)

- Low BOM

- Low battery detector

- Temperature sensor

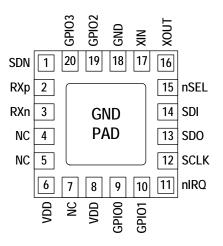

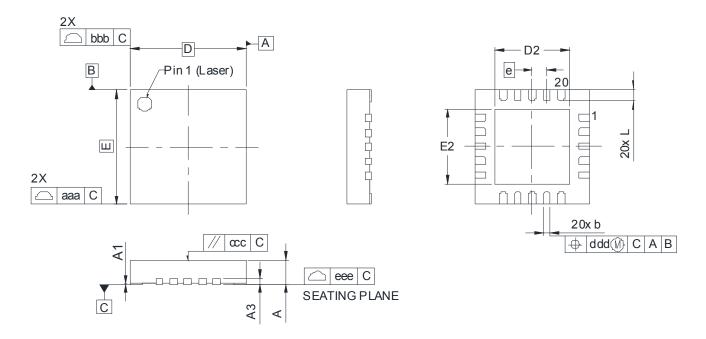

- 20-Pin QFN package

- IEEE 802.15.4g and WMBus compliant

- Data rate = 100 bps to 1 Mbps

Suitable FCC Part 90 Mask D, FCC part 15.247,15,231, 15,249, ARIB T-108, T-96, T-67, RCR STD-30, China regulatory, ETSI EN 300 220, ETSI Category 1 Operation

- Home automation

- Industrial control

- Electronic shelf labels

### Description

Silicon Labs Si4362 devices are high-performance, low-current receivers covering the sub-GHz frequency bands from 142 to 1050 MHz. The radios are part of the EZRadioPRO<sup>®</sup> family, which includes a complete line of transmitters, receivers, and transceivers covering a wide range of applications. All parts offer outstanding sensitivity of -129 dBm while achieving extremely low active and standby current consumption. The 69 dB adjacent channel selectivity with 12.5 kHz channel spacing ensures robust receive operation in harsh RF conditions, which is particularly important for narrowband operation. RX current of 10 mA coupled with extremely low standby current and fast wake times ensure extended battery life in the most demanding applications.

3 RXn

6

9 З ő

7 8 9

NC 4

NC 5 GND

PAD

GP100

10

GPI01

**Rev 1.0** Copyright © 2014 by Silicon Laboratories Si4362-C This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

- Sensor networks

- Health monitors

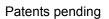

## **Functional Block Diagram**

## TABLE OF CONTENTS

## Section Page

## 1. Electrical Specifications

## Table 1. DC Characteristics<sup>\*</sup>

| RC Oscillator, Main Digital Regulator,<br>and Low Power Digital Regulator OFF<br>Register values maintained and RC<br>oscillator/WUT OFF<br>RC Oscillator/WUT ON and all register values main-<br>tained, and all other blocks OFF<br>Sleep current using an external 32 kHz crystal.<br>Low battery detector ON, register values maintained, | 1.8<br>—<br>—<br>—                                                                                                | 3.3<br>30<br>40<br>740                                                                                   | 3.8<br>—<br>—<br>—                                                                                                                                                                                       | V<br>nA<br>nA<br>nA                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| and Low Power Digital Regulator OFF<br>Register values maintained and RC<br>oscillator/WUT OFF<br>RC Oscillator/WUT ON and all register values main-<br>tained, and all other blocks OFF<br>Sleep current using an external 32 kHz crystal.<br>Low battery detector ON, register values maintained,                                           | -                                                                                                                 | 40<br>740                                                                                                |                                                                                                                                                                                                          | nA                                                                                   |

| oscillator/WUT OFF<br>RC Oscillator/WUT ON and all register values main-<br>tained, and all other blocks OFF<br>Sleep current using an external 32 kHz crystal.<br>Low battery detector ON, register values maintained,                                                                                                                       | -                                                                                                                 | 740                                                                                                      | _                                                                                                                                                                                                        |                                                                                      |

| tained, and all other blocks OFF<br>Sleep current using an external 32 kHz crystal.<br>Low battery detector ON, register values maintained,                                                                                                                                                                                                   |                                                                                                                   |                                                                                                          |                                                                                                                                                                                                          | nA                                                                                   |

| Low battery detector ON, register values maintained,                                                                                                                                                                                                                                                                                          | _                                                                                                                 | 1.7                                                                                                      |                                                                                                                                                                                                          |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   | 1                                                                                                        | —                                                                                                                                                                                                        | μA                                                                                   |

| and all other blocks OFF                                                                                                                                                                                                                                                                                                                      | -                                                                                                                 | 1                                                                                                        | -                                                                                                                                                                                                        | μA                                                                                   |

| Crystal Oscillator and Main Digital Regulator ON,<br>all other blocks OFF                                                                                                                                                                                                                                                                     | _                                                                                                                 | 1.8                                                                                                      | _                                                                                                                                                                                                        | mA                                                                                   |

| Duty cycling during preamble search,<br>1.2 kbps, 4 byte preamble                                                                                                                                                                                                                                                                             | -                                                                                                                 | 6                                                                                                        | _                                                                                                                                                                                                        | mA                                                                                   |

| RX Tune, High Performance Mode                                                                                                                                                                                                                                                                                                                | —                                                                                                                 | 7.6                                                                                                      | —                                                                                                                                                                                                        | mA                                                                                   |

| High Performance Mode<br>(measured at 915 MHz and 40 kbps)                                                                                                                                                                                                                                                                                    | -                                                                                                                 | 13.7                                                                                                     | —                                                                                                                                                                                                        | mA                                                                                   |

| Low Power Mode<br>(measured at 315 MHz and 40 kbps)                                                                                                                                                                                                                                                                                           | -                                                                                                                 | 10.9                                                                                                     | —                                                                                                                                                                                                        | mA                                                                                   |

|                                                                                                                                                                                                                                                                                                                                               | High Performance Mode<br>(measured at 915 MHz and 40 kbps)<br>Low Power Mode<br>(measured at 315 MHz and 40 kbps) | High Performance Mode—(measured at 915 MHz and 40 kbps)—Low Power Mode—(measured at 315 MHz and 40 kbps) | High Performance Mode<br>(measured at 915 MHz and 40 kbps)—13.7Low Power Mode<br>(measured at 315 MHz and 40 kbps)—10.9low sare guaranteed across the recommended operating conditions of supplementary— | High Performance Mode<br>(measured at 915 MHz and 40 kbps)—13.7—Low Power Mode—10.9— |

| Table 2. Synthesizer AC Electrical Characteristics* |  |

|-----------------------------------------------------|--|

|-----------------------------------------------------|--|

| N                                                                                                       | 142<br>284                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                         | 175<br>350                                                                                                                                                                                                                                                                                                                                                                                            | MHz                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                         | 284                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                           | 350                                                                                                                                                                                                                                                                                                                                                                                                   | N 41 1-                                                                                                                                                                                                                                                                                                            |

|                                                                                                         |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                           | 000                                                                                                                                                                                                                                                                                                                                                                                                   | MHz                                                                                                                                                                                                                                                                                                                |

|                                                                                                         | 350                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                         | 525                                                                                                                                                                                                                                                                                                                                                                                                   | MHz                                                                                                                                                                                                                                                                                                                |

|                                                                                                         | 850                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                         | 1050                                                                                                                                                                                                                                                                                                                                                                                                  | MHz                                                                                                                                                                                                                                                                                                                |

| 960 850–1050 MHz                                                                                        | _                                                                                                                                                                                       | 28.6                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                       | Hz                                                                                                                                                                                                                                                                                                                 |

| <sup>525</sup> 420–525 MHz                                                                              | _                                                                                                                                                                                       | 14.3                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                     | Hz                                                                                                                                                                                                                                                                                                                 |

| <sup>420</sup> 350–420 MHz                                                                              | —                                                                                                                                                                                       | 11.4                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                     | Hz                                                                                                                                                                                                                                                                                                                 |

| <sup>350</sup> 284–350 MHz                                                                              | _                                                                                                                                                                                       | 9.5                                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                                                                                                                                     | Hz                                                                                                                                                                                                                                                                                                                 |

| 175 142–175 MHz                                                                                         | _                                                                                                                                                                                       | 4.7                                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                                                                                                                                     | Hz                                                                                                                                                                                                                                                                                                                 |

| K Measured from exiting Ready mode with<br>XOSC running to any frequency.<br>Including VCO Calibration. | —                                                                                                                                                                                       | 50                                                                                                                                                                                                                                                                                        | —                                                                                                                                                                                                                                                                                                                                                                                                     | μs                                                                                                                                                                                                                                                                                                                 |

|                                                                                                         | -525     420–525 MHz       -420     350–420 MHz       -350     284–350 MHz       -175     142–175 MHz       CK     Measured from exiting Ready mode with XOSC running to any frequency. | -960       850–1050 MHz       —         -525       420–525 MHz       —         -420       350–420 MHz       —         -350       284–350 MHz       —         -175       142–175 MHz       —         CK       Measured from exiting Ready mode with XOSC running to any frequency.       — | -960         850–1050 MHz         —         28.6           -525         420–525 MHz         —         14.3           -420         350–420 MHz         —         11.4           -350         284–350 MHz         —         9.5           -175         142–175 MHz         —         4.7           CK         Measured from exiting Ready mode with XOSC running to any frequency.         —         50 | -960       850–1050 MHz        28.6          -525       420–525 MHz        14.3          -420       350–420 MHz        11.4          -350       284–350 MHz        9.5          -175       142–175 MHz        4.7          CK       Measured from exiting Ready mode with XOSC running to any frequency.        50 |

## Table 3. Receiver AC Electrical Characteristics<sup>1,2</sup>

| Parameter                           | Symbol              | Test Condition                                                       | Min | Тур  | Max  | Unit |

|-------------------------------------|---------------------|----------------------------------------------------------------------|-----|------|------|------|

| RX Frequency Range                  | F <sub>RX</sub>     |                                                                      | 850 |      | 1050 | MHz  |

|                                     |                     |                                                                      | 350 |      | 525  | MHz  |

|                                     |                     |                                                                      | 284 | —    | 350  | MHz  |

|                                     |                     |                                                                      | 142 |      | 175  | MHz  |

| RX Sensitivity 169 MHz <sup>3</sup> | P <sub>RX_0.5</sub> | (BER < 0.1%)<br>(500 bps, GFSK, BT = 0.5,<br>∆f = ±250Hz)            |     | -129 | —    | dBm  |

|                                     | P <sub>RX_40</sub>  | (BER < 0.1%)<br>(40 kbps, GFSK, BT = 0.5,<br>∆f = ±20 kHz)           | _   | -110 | _    | dBm  |

|                                     | P <sub>RX_100</sub> | (BER < 0.1%)<br>(100 kbps, GFSK, BT = 0.5,<br>∆f = ±50 kHz)          |     | -106 | —    | dBm  |

|                                     | P <sub>RX_500</sub> | (BER < 0.1%)<br>(500 kbps, GFSK, BT = 0.5,<br>∆f = ±250 kHz)         |     | -98  | —    | dBm  |

|                                     | P <sub>RX_9.6</sub> | (PER 1%)<br>(9.6 kbps, 4GFSK, BT = 0.5,<br>∆f = ±2.4 kHz)            |     | -110 | —    | dBm  |

|                                     | P <sub>RX_1M</sub>  | (PER 1%)<br>(1 Mbps, 4GFSK, BT = 0.5,<br>inner deviation = 83.3 kHz) |     | -89  | —    | dBm  |

|                                     | P <sub>RX_OOK</sub> | (BER < 0.1%, 4.8 kbps, 350 kHz BW,<br>OOK, PN15 data)                | _   | -110 |      | dBm  |

|                                     |                     | (BER < 0.1%, 40 kbps, 350 kHz BW,<br>OOK, PN15 data)                 |     | -103 |      | dBm  |

|                                     |                     | (BER < 0.1%, 120 kbps, 350 kHz BW,<br>OOK, PN15 data)                | _   | -97  | —    | dBm  |

Notes:

All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and from -40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

2. For PER tests, 48 preamble symbols, 4 byte sync word, 10 byte payload and CRC-32 was used.

3. Measured over 50000 bits using PN9 data sequence and data and clock on GPIOs. Sensitivity is expected to be better if reading data from packet handler FIFO especially at higher data rates.

| Table 3. Receiver AC Electrical Charact | teristics <sup>1,2</sup> (Continued) |

|-----------------------------------------|--------------------------------------|

|-----------------------------------------|--------------------------------------|

| Parameter                                               | Symbol              | Test Condition                                                                                                                                       | Min | Тур  | Max | Unit |

|---------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| RX Sensitivity<br>915/868 MHz <sup>3</sup>              | P <sub>RX_0.5</sub> | (BER < 0.1%)<br>(500 bps, GFSK, BT = 0.5,<br>∆f = ±250Hz)                                                                                            | —   | -127 |     | dBm  |

|                                                         | P <sub>RX_40</sub>  | (BER < 0.1%)<br>(40 kbps, GFSK, BT = 0.5,<br>∆f = ±20 kHz)                                                                                           | _   | -109 |     | dBm  |

|                                                         | P <sub>RX_100</sub> | (BER < 0.1%)<br>(100 kbps, GFSK, BT = 0.5,<br>∆f = ±50 kHz)                                                                                          | _   | -104 |     | dBm  |

|                                                         | P <sub>RX_500</sub> | (BER < 0.1%)<br>(500 kbps, GFSK, BT = 0.5,<br>∆f = ±250 kHz)                                                                                         | _   | -97  |     | dBm  |

|                                                         | P <sub>RX_9.6</sub> | (PER 1%)<br>(9.6 kbps, 4GFSK, BT = 0.5,<br>∆f = ±2.4 kHz)                                                                                            | —   | -109 |     | dBm  |

|                                                         | P <sub>RX_1M</sub>  | (PER 1%)<br>(1 Mbps, 4GFSK, BT = 0.5,<br>inner deviation = 83.3 kHz)                                                                                 | —   | -88  |     | dBm  |

|                                                         | P <sub>RX_OOK</sub> | (BER < 0.1%, 4.8 kbps, 350 kHz BW,<br>OOK, PN15 data)                                                                                                | _   | -108 |     | dBm  |

|                                                         |                     | (BER < 0.1%, 40 kbps, 350 kHz BW,<br>OOK, PN15 data)                                                                                                 | _   | -101 |     | dBm  |

|                                                         |                     | (BER < 0.1%, 120 kbps, 350 kHz BW,<br>OOK, PN15 data)                                                                                                | —   | -96  |     | dBm  |

| RX Channel Bandwidth                                    | BW                  |                                                                                                                                                      | 1.1 | _    | 850 | kHz  |

| RSSI Resolution                                         | RES <sub>RSSI</sub> | Valid from –110 dBm to –90 dBm                                                                                                                       | _   | ±0.5 | _   | dB   |

| ±1-Ch Offset Selectivity,<br>169 MHz <sup>3</sup>       | C/I <sub>1-CH</sub> | Desired Ref Signal 3 dB above sensitiv-<br>ity, BER < 0.1%. Interferer is CW, and                                                                    | —   | -69  |     | dB   |

| ±1-Ch Offset Selectivity,<br>450 MHz <sup>3</sup>       | C/I <sub>1-CH</sub> | desired is modulated with 2.4 kbps<br>$\Delta F = 1.2 \text{ kHz} \text{ GFSK}$ with BT = 0.5, RX<br>channel BW = 4.8 kHz,                           | _   | -60  |     | dB   |

| ±1-Ch Offset Selectivity,<br>868 / 915 MHz <sup>3</sup> | C/I <sub>1-CH</sub> | channel spacing = 12.5 kHz                                                                                                                           | _   | -55  |     | dB   |

| Blocking 1 MHz Offset                                   | 1M <sub>BLOCK</sub> | Desired Ref Signal 3 dB above sensitiv-                                                                                                              |     | -79  | —   | dB   |

| Blocking 8 MHz Offset                                   | 8M <sub>BLOCK</sub> | ity, BER = 0.1%. Interferer is CW, and<br>desired is modulated with 2.4 kbps,<br>$\Delta F$ = 1.2 kHz GFSK with BT = 0.5,<br>RX channel BW = 4.8 kHz | _   | -86  |     | dB   |

Notes:

All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and from -40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

For PER tests, 48 preamble symbols, 4 byte sync word, 10 byte payload and CRC-32 was used.

Measured over 50000 bits using PN9 data sequence and data and clock on GPIOs. Sensitivity is expected to be better if reading data from packet handler FIFO especially at higher data rates.

| Parameter                            | Symbol            | Test Condition                                                                                     | Min | Тур | Max | Unit |

|--------------------------------------|-------------------|----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Image Rejection<br>(IF = 468.75 kHz) | Im <sub>REJ</sub> | No image rejection calibration. Rejec-<br>tion at the image frequency.<br>RF = 460 MHz             | —   | 40  | _   | dB   |

|                                      |                   | With image rejection calibration in<br>Si4362. Rejection at the image fre-<br>quency. RF = 460 MHz | —   | 55  | _   | dB   |

|                                      |                   | No image rejection calibration. Rejec-<br>tion at the image frequency.<br>RF = 915 MHz             | _   | 45  | _   | dB   |

|                                      |                   | With image rejection calibration in<br>Si4362. Rejection at the image fre-<br>quency. RF = 915 MHz | _   | 52  | _   | dB   |

|                                      |                   | No image rejection calibration. Rejec-<br>tion at the image frequency.<br>RF = 169 MHz             | —   | 45  | _   | dB   |

|                                      |                   | With image rejection calibration in<br>Si4362. Rejection at the image fre-<br>quency. RF = 169 MHz | —   | 60  | _   | dB   |

Notes:

1. All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and from -40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

2. For PER tests, 48 preamble symbols, 4 byte sync word, 10 byte payload and CRC-32 was used.

3. Measured over 50000 bits using PN9 data sequence and data and clock on GPIOs. Sensitivity is expected to be better if reading data from packet handler FIFO especially at higher data rates.

## Table 4. Auxiliary Block Specifications<sup>1</sup>

| Parameter                                                    | Symbol                | Test Condition                                                                                                                                                         | Min     | Тур  | Мах   | Unit                |

|--------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|---------------------|

| Temperature Sensor<br>Sensitivity <sup>1</sup>               | TS <sub>S</sub>       |                                                                                                                                                                        |         | 4.5  | _     | ADC<br>Codes/<br>°C |

| Low Battery Detector<br>Resolution                           | LBD <sub>RES</sub>    |                                                                                                                                                                        | _       | 50   |       | mV                  |

| Microcontroller Clock<br>Output Frequency Range <sup>2</sup> | F <sub>MC</sub>       | Configurable to Fxtal or Fxtal<br>divided by 2, 3, 7.5, 10, 15, or<br>30 where Fxtal is the reference<br>XTAL frequency. In addition,<br>32.768 kHz is also supported. | 32.768K | _    | Fxtal | Hz                  |

| Temperature Sensor<br>Conversion <sup>1</sup>                | TEMP <sub>CT</sub>    | Programmable setting                                                                                                                                                   | —       | 3    |       | ms                  |

| XTAL Range <sup>3</sup>                                      | XTAL <sub>Range</sub> |                                                                                                                                                                        | 25      | _    | 32    | MHz                 |

| 30 MHz XTAL Start-Up Time                                    | t <sub>30M</sub>      | Using XTAL and board layout in<br>reference design. Start-up time<br>will vary with XTAL type and<br>board layout.                                                     |         | 300  |       | μs                  |

| 30 MHz XTAL Cap<br>Resolution <sup>1</sup>                   | 30M <sub>RES</sub>    |                                                                                                                                                                        | —       | 70   | _     | fF                  |

| 32 kHz XTAL Start-Up Time <sup>1</sup>                       | t <sub>32k</sub>      |                                                                                                                                                                        |         | 2    |       | sec                 |

| 32 kHz Accuracy using<br>Internal RC Oscillator <sup>1</sup> | 32KRC <sub>RES</sub>  |                                                                                                                                                                        | —       | 2500 | _     | ppm                 |

| POR Reset Time                                               | t <sub>POR</sub>      |                                                                                                                                                                        |         | _    | 6     | ms                  |

| POR Reset Time                                               | t <sub>POR</sub>      |                                                                                                                                                                        | —       |      | 6     | ms                  |

Notes:

1. All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and from -40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

2. Microcontroller clock frequency tested in production at 1 MHz, 30 MHz, 32 MHz, and 32.768 kHz. Other frequencies tested in bench characterization.

3. XTAL Range tested in production using an external clock source (similar to using a TCXO).

| Table 5. Digital IO | <b>Specifications</b> | (GPIO x.    | SCLK. SDO. | SDI. nSEL. | nIRQ, SDN) <sup>1</sup> |

|---------------------|-----------------------|-------------|------------|------------|-------------------------|

|                     |                       | <b>\_</b> , |            | ,,,        |                         |

| Parameter                              | Symbol              | Test Condition                                                                             | Min                   | Тур  | Max                   | Unit |

|----------------------------------------|---------------------|--------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| Rise Time <sup>2,3</sup>               | T <sub>RISE</sub>   | $0.1 \times V_{DD}$ to $0.9 \times V_{DD}$ ,<br>$C_{L} = 10 \text{ pF}$ ,<br>DRV<1:0> = LL | _                     | 2.3  | _                     | ns   |

| Fall Time <sup>3,4</sup>               | T <sub>FALL</sub>   | $0.9 \times V_{DD}$ to 0.1 x V <sub>DD</sub> ,<br>C <sub>L</sub> = 10 pF,<br>DRV<1:0> = LL | _                     | 2    | _                     | ns   |

| Input Capacitance                      | C <sub>IN</sub>     |                                                                                            | —                     | 2    | —                     | pF   |

| Logic High Level Input Voltage         | V <sub>IH</sub>     |                                                                                            | V <sub>DD</sub> x 0.7 |      | _                     | V    |

| Logic Low Level Input Voltage          | V <sub>IL</sub>     |                                                                                            | _                     | -    | V <sub>DD</sub> x 0.3 | V    |

| Input Current                          | I <sub>IN</sub>     | 0 <v<sub>IN&lt; V<sub>DD</sub></v<sub>                                                     | -1                    | _    | 1                     | μA   |

| Input Current If Pullup is Activated   | I <sub>INP</sub>    | V <sub>IL</sub> = 0 V                                                                      | 1                     | -    | 4                     | μA   |

| Drive Strength for Output Low<br>Level | I <sub>OmaxLL</sub> | DRV[1:0] = LL <sup>3</sup>                                                                 | _                     | 6.66 | _                     | mA   |

|                                        | I <sub>OmaxLH</sub> | DRV[1:0] = LH <sup>3</sup>                                                                 |                       | 5.03 | _                     | mA   |

|                                        | I <sub>OmaxHL</sub> | DRV[1:0] = HL <sup>3</sup>                                                                 | _                     | 3.16 | _                     | mA   |

|                                        | I <sub>OmaxHH</sub> | DRV[1:0] = HH <sup>3</sup>                                                                 | _                     | 1.13 | _                     | mA   |

| Drive Strength for Output High         | I <sub>OmaxLL</sub> | DRV[1:0] = LL <sup>3</sup>                                                                 | —                     | 5.75 | —                     | mA   |

| Level                                  | I <sub>OmaxLH</sub> | DRV[1:0] = LH <sup>3</sup>                                                                 | _                     | 4.37 | _                     | mA   |

|                                        | I <sub>OmaxHL</sub> | DRV[1:0] = HL <sup>3</sup>                                                                 | _                     | 2.73 | _                     | mA   |

|                                        | I <sub>OmaxHH</sub> | DRV[1:0] = HH <sup>3</sup>                                                                 | —                     | 0.96 | —                     | mA   |

| Drive Strength for Output High         | I <sub>OmaxLL</sub> | DRV[1:0] = LL <sup>3</sup>                                                                 | _                     | 2.53 | _                     | mA   |

| Level for GPIO0                        | I <sub>OmaxLH</sub> | DRV[1:0] = LH <sup>3</sup>                                                                 | _                     | 2.21 | _                     | mA   |

|                                        | I <sub>OmaxHL</sub> | DRV[1:0] = HL <sup>3</sup>                                                                 | —                     | 1.70 | —                     | mA   |

|                                        | I <sub>OmaxHH</sub> | DRV[1:0] = HH <sup>3</sup>                                                                 |                       | 0.80 | —                     | mA   |

| Logic High Level Output Voltage        | V <sub>OH</sub>     | DRV[1:0] = HL                                                                              | V <sub>DD</sub> x 0.8 |      | —                     | V    |

| Logic Low Level Output Voltage         | V <sub>OL</sub>     | DRV[1:0] = HL                                                                              |                       | _    | V <sub>DD</sub> x 0.2 | V    |

Notes:

1. All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and from -40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

2. 6.7 ns is typical for GPIO0 rise time.

3. Assuming VDD = 3.3 V, drive strength is specified at Voh (min) = 2.64 V and Vol(max) = 0.66 V at room temperature.

4. 2.4 ns is typical for GPIO0 fall time.

## **Table 6. Thermal Characteristics**

| Parameter                             | Symbol           | Value       | Unit |

|---------------------------------------|------------------|-------------|------|

| Operating Ambient Temperature Range   | T <sub>A</sub>   | -40 to +85  | °C   |

| Thermal Impedance Junction to Ambient | $\theta_{JA}$    | 25          | °C/W |

| Junction Temperature Maximum Value    | Тj               | +105        | °C   |

| Storage Temperature Range             | T <sub>STG</sub> | –55 to +150 | °C   |

## Table 7. Absolute Maximum Ratings

| Parameter                                                                                                           | Value                       | Unit |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------|------|--|--|--|--|

| V <sub>DD</sub> to GND                                                                                              | -0.3, +3.8                  | V    |  |  |  |  |

| Voltage on Digital Inputs                                                                                           | -0.3, V <sub>DD</sub> + 0.3 | V    |  |  |  |  |

| Voltage on Analog Inputs                                                                                            | -0.7, V <sub>DD</sub> + 0.3 | V    |  |  |  |  |

| RX Input Power                                                                                                      | +10                         | dBm  |  |  |  |  |

| Note: Stresses beyond these listed under "Absolute Maximum Patings" may asuse permanent damage to the device. These |                             |      |  |  |  |  |

**Note:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at or beyond these ratings in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Power Amplifier may be damaged if switched on without proper load or termination connected. Caution: ESD sensitive device.

## 2. Functional Description

The Si4362 is a high performance, low current, wireless ISM receiver that covers major sub-GHz bands. The wide operating voltage range of 1.8–3.8 V and low current consumption make the Si4362 an ideal solution for battery powered applications. The device uses a single-conversion mixer to downconvert the 2/4-level FSK/GFSK or OOK modulated receive signal to a low IF frequency. Following a programmable gain amplifier (PGA) the signal is converted to the digital domain by a high performance  $\Delta\Sigma$  ADC allowing filtering, demodulation, slicing, and packet handling to be performed in the built-in DSP increasing the receiver's performance and flexibility versus analog based architectures. The demodulated signal is output to the system MCU through a programmable GPIO or via the standard SPI bus by reading the 64-byte RX FIFO.

A single high precision local oscillator (LO) is used for receive mode. The LO is generated by an integrated VCO and  $\Delta\Sigma$  Fractional-N PLL synthesizer. The synthesizer is designed to support configurable data rates from 100 bps to 1 Mbps. The Si4362 operates in the frequency bands of 142–175, 283–350, 350–525, and 850–1050 MHz with a maximum frequency accuracy step size of 28.6 Hz.

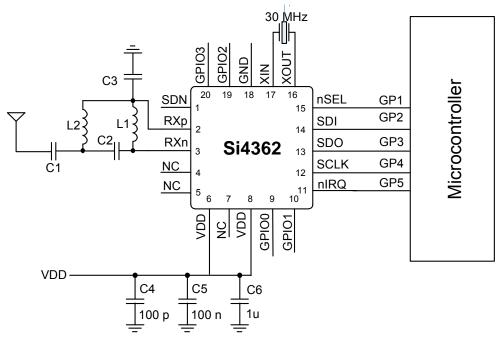

The Si4362 supports frequency hopping and antenna diversity switch control to extend the link range and improve performance. Built-in antenna diversity and support for frequency hopping can be used to further extend range and enhance performance. Antenna diversity is completely integrated into the Si4362 and can improve the system link budget by 8–10 dB, resulting in substantial range increases under adverse environmental conditions. A highly configurable packet handler allows for autonomous encoding/decoding of nearly any packet structure. Additional system features, such as an automatic wake-up timer, low battery detector, 64 byte RX FIFOs, and preamble detection, reduce overall current consumption and allows for the use of lower-cost system MCUs. An integrated temperature sensor, power-on-reset (POR), and GPIOs further reduce overall system cost and size. The Si4362 is designed to work with an MCU, crystal, and a few passive components to create a very low-cost system.

Figure 1. Si4362 Application Example

## 3. Controller Interface

## 3.1. Serial Peripheral Interface (SPI)

The Si4362 communicates with the host MCU over a standard 4-wire serial peripheral interface (SPI): SCLK, SDI, SDO, and nSEL. The SPI interface is designed to operate at a maximum of 10 MHz. The SPI timing parameters are demonstrated in Table 8. The host MCU writes data over the SDI pin and can read data from the device on the SDO output pin. Figure 2 demonstrates an SPI write command. The nSEL pin should go low to initiate the SPI command. The first byte of SDI data will be one of the firmware commands followed by n bytes of parameter data which will be variable depending on the specific command. The rising edges of SCLK should be aligned with the center of the SDI data.

| Symbol          | Parameter                  | Min<br>(ns) | Max<br>(ns) | Diagram      |

|-----------------|----------------------------|-------------|-------------|--------------|

| t <sub>CH</sub> | Clock high time            | 40          |             |              |

| t <sub>CL</sub> | Clock low time             | 40          |             |              |

| t <sub>DS</sub> | Data setup time            | 20          |             |              |

| t <sub>DH</sub> | Data hold time             | 20          |             |              |

| t <sub>DD</sub> | Output data delay time     |             | 43          |              |

| t <sub>DE</sub> | Output disable time        |             | 45          |              |

| t <sub>SS</sub> | Select setup time          | 20          |             |              |

| t <sub>SH</sub> | Select hold time           | 50          |             |              |

| t <sub>SW</sub> | Select high period         | 80          |             |              |

| *Note: Cl       | _ = 10 pF; VDD = 1.8 V; SD | O Drive s   | strength s  | etting = 10. |

Table 8. Serial Interface Timing Parameters

| nSEL |                                                      |

|------|------------------------------------------------------|

| SDO  |                                                      |

| SDI  | FW Command     Param Byte 0     • • • • Param Byte n |

| SCLK |                                                      |

#### Figure 2. SPI Write Command

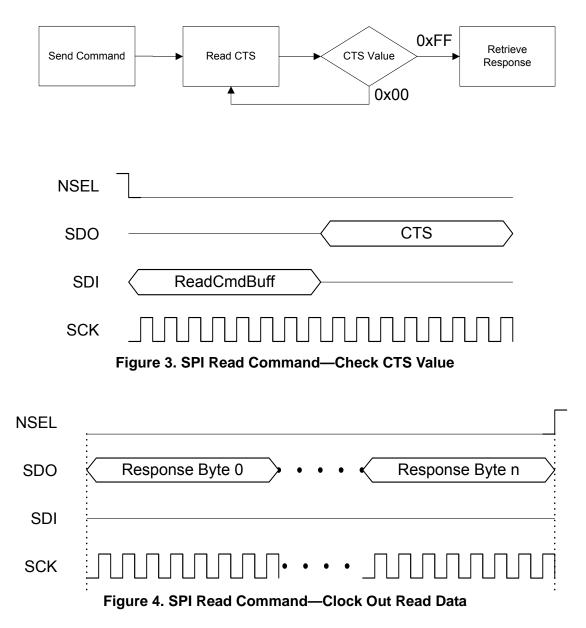

The Si4362 contains an internal MCU that controls all the internal functions of the radio. For SPI read commands a typical MCU flow of checking clear-to-send (CTS) is used to make sure the internal MCU has executed the command and prepared the data to be output over the SDO pin. Figure 3 demonstrates the general flow of an SPI read command. Once the CTS value reads FFh then the read data is ready to be clocked out to the host MCU. The typical time for a valid FFh CTS reading is 20  $\mu$ s. Figure 4 demonstrates the remaining read cycle after CTS is set to FFh. The internal MCU will clock out the SDO data on the negative edge so the host MCU should process the SDO data on the rising edge of SCLK.

## **Firmware Flow**

## 3.2. Fast Response Registers

The fast response registers are registers that can be read immediately without the requirement to monitor and check CTS. There are four fast response registers that can be programmed for a specific function. The fast response registers can be read through API commands, 0x50 for Fast Response A, 0x51 for Fast Response B, 0x53 for Fast Response C, and 0x57 for Fast Response D. The fast response registers can be configured by the "FRR\_CTL\_X\_MODE" properties.

The fast response registers may be read in a burst fashion. After the initial 16 clock cycles, each additional eight clock cycles will clock out the contents of the next fast response register in a circular fashion. The value of the FRRs will not be updated unless NSEL is toggled.

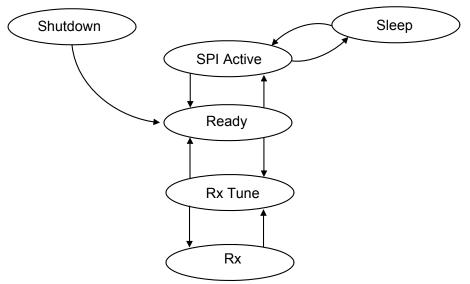

### 3.3. Operating Modes and Timing

The primary states of the Si4362 are shown in Figure 5. The shutdown state completely shuts down the radio to minimize current consumption. Standby/Sleep, SPI Active, Ready, and RX tune are available to optimize the current consumption and response time to RX for a given application. API commands START\_RX, and CHANGE\_STATE control the operating state with the exception of shutdown which is controlled by SDN, pin 1. Table 9 shows each of the operating modes with the time required to reach RX mode as well as the current consumption of each mode. The times in Table 9 are measured from the rising edge of nSEL until the chip is in the desired state. Note that these times are indicative of state transition timing but are not guaranteed and should only be used as a reference data point. An automatic sequencer will put the chip into RX from any state. It is not necessary to manually step through the states. To simplify the diagram it is not shown but any of the lower power states can be returned to automatically after RX.

Figure 5. State Machine Diagram

| State/Mode       | Response Time to RX | Current in State/Mode |  |  |

|------------------|---------------------|-----------------------|--|--|

| Shutdown State   | 15 ms               | 30 nA                 |  |  |

| Standby State    | 440 µs              | 40 nA                 |  |  |

| Sleep State      | 440 µs              | 740 nA                |  |  |

| SPI Active State | 340 µs              | 1.35 mA               |  |  |

| Ready State      | 100 µs              | 1.8 mA                |  |  |

| RX Tune State    | 60 µs               | 7.6 mA                |  |  |

| RX State         | 75 µs               | 10.9 or 13.7 mA       |  |  |

## Table 9. Operating State Response Time and Current Consumption\*

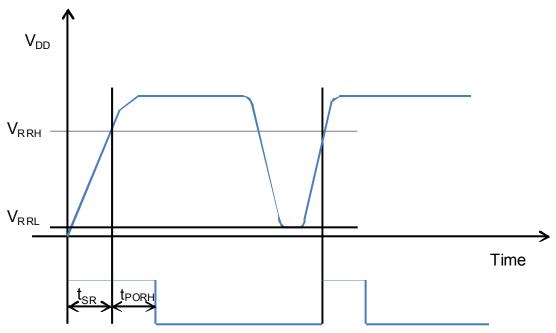

Figure 6 shows the POR timing and voltage requirements. The power consumption (battery life) depends on the duty cycle of the application or how often the part is in either Rx state. In most applications the utilization of the standby state will be most advantageous for battery life but for very low duty cycle applications shutdown will have an advantage. For the fastest timing the next state can be selected in the START\_RX API command to minimize SPI transactions and internal MCU processing.

#### 3.3.1. Power on Reset (POR)

A power on reset (POR) sequence is used to boot the device up from a fully off or shutdown state. To execute this process, VDD must ramp within 1ms and must remain applied to the device for at least 10 ms. If VDD is removed, then it must stay below 0.15 V for at least 10 ms before being applied again. See Figure 6 and Table 10 for details.

Figure 6. POR Timing Diagram

| Variable          | Description                                    | Min                   | Тур | Max | Units |

|-------------------|------------------------------------------------|-----------------------|-----|-----|-------|

| t <sub>PORH</sub> | High time for VDD to fully settle POR circuit. | 10                    |     |     | ms    |

| t <sub>PORL</sub> | Low time for VDD to enable POR.                | 10                    |     |     | ms    |

| V <sub>RRH</sub>  | Voltage for successful POR                     | 90% x V <sub>DD</sub> |     |     | V     |

| V <sub>RRL</sub>  | Starting Voltage for successful POR            | 0                     |     | 150 | mV    |

| t <sub>SR</sub>   | Slew rate of VDD for successful POR            |                       |     | 1   | ms    |

## Table 10. POR Timing

### 3.3.2. Shutdown State

The shutdown state is the lowest current consumption state of the device with nominally less than 30 nA of current consumption. The shutdown state may be entered by driving the SDN pin (Pin 1) high. The SDN pin should be held low in all states except the shutdown state. In the shutdown state, the contents of the registers are lost and there is no SPI access. When coming out of the shutdown state a power on reset (POR) will be initiated along with the internal calibrations. After the POR the POWER\_UP command is required to initialize the radio. The SDN pin needs to be held high for at least 10 µs before driving low again so that internal capacitors can discharge. Not holding the SDN high for this period of time may cause the POR to be missed and the device to boot up incorrectly. If POR timing and voltage requirements cannot be met, it is highly recommended that SDN be controlled using the host processor rather than tying it to GND on the board.

#### 3.3.3. Standby State

Standby state has the lowest current consumption with the exception of shutdown but has much faster response time to RX mode. In most cases standby should be used as the low power state. In this state the register values are maintained with all other blocks disabled. The SPI is accessible during this mode but any SPI event, including FIFO R/W, will enable an internal boot oscillator and automatically move the part to SPI active state. After an SPI event the host will need to re-command the device back to standby through the "Change State" API command to achieve the 40 nA current consumption. If an interrupt has occurred (i.e., the nIRQ pin = 0) the interrupt registers must be read to achieve the minimum current consumption of this mode.

#### 3.3.4. Sleep State

Sleep state is the same as standby state but the wake-up-timer and a 32 kHz clock source are enabled. The source of the 32 kHz clock can either be an internal 32 kHz RC oscillator which is periodically calibrated or a 32 kHz oscillator using an external XTAL. The SPI is accessible during this mode but an SPI event will enable an internal boot oscillator and automatically move the part to SPI active mode. After an SPI event the host will need to re-command the device back to sleep. If an interrupt has occurred (i.e., the nIRQ pin = 0) the interrupt registers must be read to achieve the minimum current consumption of this mode.

#### 3.3.5. SPI Active State

In SPI active state the SPI and a boot up oscillator are enabled. After SPI transactions during either standby or sleep the device will not automatically return to these states. A "Change State" API command will be required to return to either the standby or sleep modes.

#### 3.3.6. Ready State

Ready state is designed to give a fast transition time to RX state with reasonable current consumption. In this mode the Crystal oscillator remains enabled reducing the time required to switch to RX mode by eliminating the crystal start-up time.

#### 3.3.7. RX State

The RX state may be entered from any of the other states by using the "Start RX" or "Change State" API command. A built-in sequencer takes care of all the actions required to transition between states. The following sequence of events will occur automatically to get the chip into RX mode when going from standby to RX state:

- 1. Enable the digital LDO and the analog LDOs.

- 2. Start up crystal oscillator and wait until ready (controlled by an internal timer).

- 3. Enable PLL.

- 4. Calibrate VCO

- 5. Wait until PLL settles to required receive frequency (controlled by an internal timer).

- 6. Enable receiver circuits: LNA, mixers, and ADC.

- 7. Enable receive mode in the digital modem.

Depending on the configuration of the radio, all or some of the following functions will be performed automatically by the digital modem: AGC, AFC (optional), update status registers, bit synchronization, packet handling (optional) including sync word, header check, and CRC. The next state after RX may be defined in the "Start RX" API command. The START\_RX commands and timing will be equivalent to the timing shown in Figure 7.

## 3.4. Application Programming Interface (API)

An application programming interface (API), which the host MCU will communicate with, is embedded inside the device. The API is divided into two sections, commands and properties. The commands are used to control the chip and retrieve its status. The properties are general configurations which will change infrequently. The API descriptions can be found on the Silicon Labs web site.

### 3.5. Interrupts

The Si4362 is capable of generating an interrupt signal when certain events occur. The chip notifies the microcontroller that an interrupt event has occurred by setting the nIRQ output pin LOW = 0. This interrupt signal will be generated when any one (or more) of the interrupt events (corresponding to the Interrupt Status bits) occur. The nIRQ pin will remain low until the microcontroller reads the Interrupt Status Registers. The nIRQ output signal will then be reset until the next change in status is detected.

The interrupts sources are grouped into three groups: packet handler, chip status, and modem. The individual interrupts in these groups can be enabled/disabled in the interrupt property registers. An interrupt must be enabled for it to trigger an event on the nIRQ pin. The interrupt group and the individual interrupts must be enabled.

Once an interrupt event occurs and the nIRQ pin is low there are two ways to read and clear the interrupts. All of the interrupts may be read and cleared in the "GET\_INT\_STATUS" API command. By default all interrupts will be cleared once read. If only specific interrupts want to be read in the fastest possible method the individual interrupt groups (Packet Handler, Chip Status, Modem) may be read and cleared by the "GET\_MODEM\_STATUS", "GET\_PH\_STATUS" (packet handler), and "GET\_CHIP\_STATUS" API commands.

The instantaneous status of a specific function maybe read if the specific interrupt is enabled or disabled. The status results are provided after the interrupts and can be read with the same commands as the interrupts. The status bits will give the current state of the function whether the interrupt is enabled or not.

The fast response registers can also give information about the interrupt groups but reading the fast response registers will not clear the interrupt and reset the nIRQ pin.

## 3.6. GPIO

Four general purpose IO pins are available to utilize in the application. The GPIO are configured by the GPIO\_PIN\_CFG command in address 13h. For a complete list of the GPIO options please see the API guide. GPIO pins 0 and 1 should be used for active signals such as data or clock. GPIO pins 2 and 3 have more susceptibility to generating spurious in the synthesizer than pins 0 and 1. The drive strength of the GPIOs can be adjusted with the GEN\_CONFIG parameter in the GPIO\_PIN\_CFG command. By default the drive strength is set to minimum. The default configuration for the GPIOs and the state during SDN is shown below in Table 11. The state of the IO during shutdown is also shown in Table 11. As indicated previously in Table 5, GPIO 0 has lower drive strength than the other GPIOs.

| Pin   | SDN State             | POR Default |

|-------|-----------------------|-------------|

| GPIO0 | 0                     | POR         |

| GPIO1 | 0                     | CTS         |

| GPIO2 | 0                     | POR         |

| GPIO3 | 0                     | POR         |

| nIRQ  | resistive VDD pull-up | nIRQ        |

| SDO   | resistive VDD pull-up | SDO         |

| SDI   | High Z                | SDI         |

| SCLK  | High Z                | SCLK        |

| NSEL  | High Z                | NSEL        |

| Table | 11. | GPIOs |  |

|-------|-----|-------|--|

|-------|-----|-------|--|

## 4. Modulation and Hardware Configuration Options

The Si4362 supports different modulation options and can be used in various configurations to tailor the device to any specific application or legacy system for drop in replacement. The modulation and configuration options are set in API property, MODEM\_MOD\_TYPE. Refer to the API documentation for details on modem-related properties.

## 4.1. Hardware Configuration Options

There are different receive demodulator options to optimize the performance and mutually-exclusive options for how the RX data is transferred from the host MCU to the RF device.

#### 4.1.1. Receive Demodulator Options

There are multiple demodulators integrated into the device to optimize the performance for different applications, modulation formats, and packet structures. The calculator built into WDS will choose the optimal demodulator based on the input criteria.

#### 4.1.1.1. Synchronous Demodulator

The synchronous demodulator's internal frequency error estimator acquires the frequency error based on a 101010 preamble structure. The bit clock recovery circuit locks to the incoming data stream within four transactions of a "10" or "01" bit stream. The synchronous demodulator gives optimal performance for 2- or 4-level FSK or GFSK modulation that has a modulation index less than 2.

#### 4.1.1.2. Asynchronous Demodulator

The asynchronous demodulator should be used OOK modulation and for FSK/GFSK under one or more of the following conditions:

- Modulation index ≥ 2

- Non-standard preamble (not 1010101... pattern)

When the modulation index exceeds 2, the asynchronous demodulator has better sensitivity compared to the synchronous demodulator. An internal deglitch circuit provides a glitch-free data output and a data clock signal to simplify the interface to the host. There is no requirement to perform deglitching in the host MCU. The asynchronous demodulator will typically be utilized for legacy systems and will have many performance benefits over devices used in legacy designs. Unlike the Si4432/31 solution for non-standard packet structures, there is no requirement to perform deglitching on the data in the host MCU. Glitch-free data is output from the Si4362, and a sample clock for the asynchronous data can also be supplied to the host MCU; so, oversampling or bit clock recovery is not required by the host MCU. There are multiple detector options in the asynchronous demodulator block, which will be selected based upon the options entered into the WDS calculator. The asynchronous demodulator's internal frequency error estimator is able to acquire the frequency error based on any preamble structure.

#### 4.1.2. RX Data Interface With MCU

There are two different options for transferring the data from the RF device to the host MCU. FIFO mode uses the SPI interface to transfer the data, while direct mode transfers the data in real time over GPIO.

#### 4.1.2.1. FIFO Mode

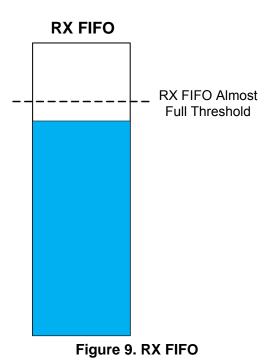

In FIFO mode, the receive data are stored in integrated FIFO register memory. The RX FIFO is accessed by writing command 77h followed by the number of clock cycles of data the host would like to read out of the RX FIFO. The RX data will be clocked out onto the SDO pin.

In RX mode, the Packet Handler must be enabled to allow storage of received data bytes into RX FIFO memory. The Packet Handler is required to detect the Sync Word, and proper detection of the Sync Word is required to determine the start of the Payload. All bytes after the Sync Word are stored in RX FIFO memory except the CRC checksum and (optionally) the variable packet length byte(s). When the FIFO is being used in RX mode, all of the received data may still be observed directly (in realtime) by properly programming a GPIO pin as the RXDATA output pin; this can be quite useful during application development.

When in FIFO mode, the chip will automatically exit the RX State when PACKET\_RX interrupt occurs. The chip will return to the IDLE state programmed in the argument of the "START RX" API command, RXVALID\_STATE[3:0].

#### 4.1.2.2. FIFO Direct Mode (Infinite Receive)

In some applications, there is a need to receive extremely long packets (greater than 40 kB) while relying on preamble and sync word detection from the on-chip packet handler. In these cases, the packet length is unknown, and the device will load the bits after the sync word into the RX FIFO forever. Other features, such as Data Whitening, CRC, Manchester, etc., are supported in this mode, but CRC calculation is not because the end of packet is unknown to the device. The RX data and clock are also available on GPIO pins. The host MCU will need to reset the packet handler by issuing a START\_RX to begin searching for a new packet.

#### 4.1.2.3. Direct Mode

For legacy systems that perform packet handling within the host MCU or other baseband chip, it may not be desirable to use the FIFO. For this scenario, a Direct mode is provided, which bypasses the FIFOs entirely. In RX Direct mode, the RX Data and RX Clock can be programmed for direct (real-time) output to GPIO pins. The microcontroller may then process the RX data without using the FIFO or packet handler functions of the RFIC.

#### 4.2. Preamble Length

#### 4.2.1. Digital Signal Arrival Detector (DSA)

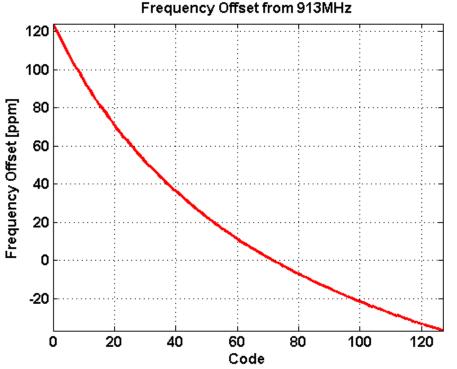

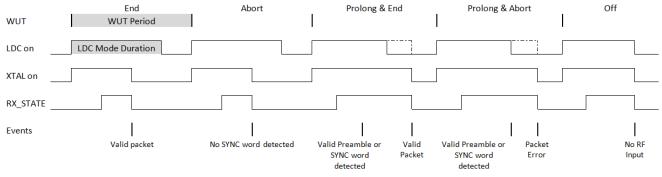

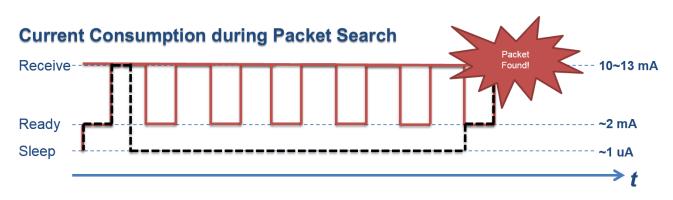

Traditional preamble detection requires 20 bits to detect preamble. This device introduces a new approach to signal detection that can detect a preamble pattern in as little as one byte. If AFC is enabled a preamble length of two bytes is sufficient to reliably detect signal arrival and settle a one shot AFC. The impact of this is significant for low-power solutions as it reduces the amount of time the receiver has to stay active to detect the preamble. This feature is used with Preamble Sense Mode (see "8.6. Preamble Sense Mode" on page 34) and the latest WMBus N modes as well as with features, such as frequency hopping, which may use signal arrival as a condition to hop. The traditional preamble detector is also available to maintain backward compatibility. Note that the DSA is using the RSSI jump detector. When used for collision detection, the RSSI jump detector may need to be reconfigured after preamble detector. Refer to the API documentation for details on how to configure the device to use the signal arrival detector.