# Si52144 EVALUATION BOARD USER'S GUIDE

### **Description**

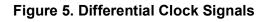

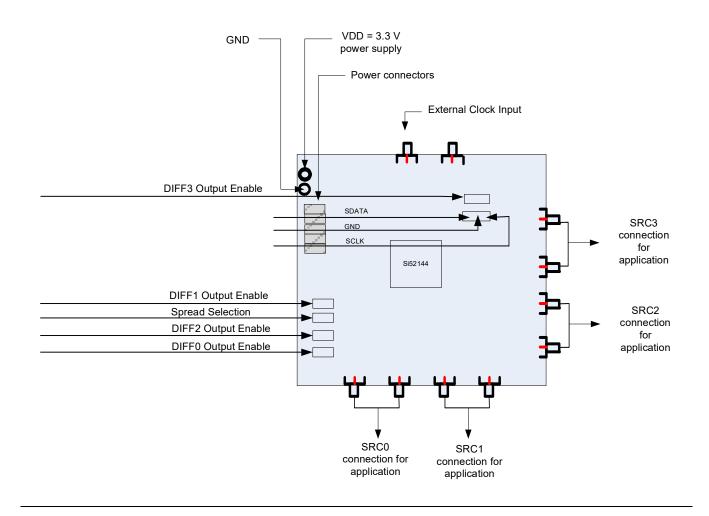

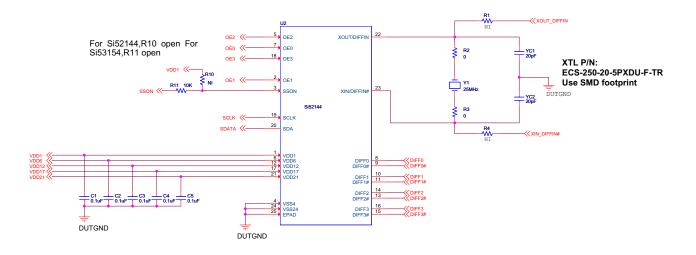

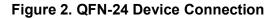

The Si52144 is a four port PCIe clock generator compliant with the PCIe Gen1, Gen2 and Gen3 standards. The Si52144 is a 24-pin QFN device that operates on a 3.3 V power supply and can be controlled using SMBus signals along with hardware control input pins. The differential outputs support spread spectrum and can be controlled through SSON input pin. The Si52144 needs a crystal or clock input of 25 MHz. The connections are described in this document.

## **EVB** Features

This document is intended to be used in conjunction with the Si52144 device and data sheet for the following tests:

- PCIe Gen1, Gen2, Gen3 compliancy

- Power consumption test

- Jitter performance

- Testing out I<sup>2</sup>C code for signal tuning

- In-system validation where SMA connectors are present

## 1. Front Panel

| Table | 1. | Input | Jumper | Settings |

|-------|----|-------|--------|----------|

|-------|----|-------|--------|----------|

| Jumper Label | Туре | Description                                                                                                          |  |

|--------------|------|----------------------------------------------------------------------------------------------------------------------|--|

| OE0          | Ι    | <b>OE0, 3.3 V Input for Enabling DIFF0 Clock Output</b> .<br>1 = DIFF0 enabled, 0 = DIFF0 disabled.                  |  |

| OE1          | I    | <b>OE1, 3.3 V Input for Enabling DIFF1 Clock Output</b> .<br>1 = DIFF1 enabled, 0 = DIFF1 disabled.                  |  |

| OE2          | I    | <b>OE2, 3.3 V Input for Enabling DIFF2 Clock Output</b> .<br>1 = DIFF2 enabled, 0 = DIFF2 disabled.                  |  |

| OE3          | I    | <b>OE3, 3.3 V Input for Enabling DIFF3 Clock Output</b> .<br>1 = DIFF3 enabled, 0 = DIFF3 disabled.                  |  |

| SSON         | I    | SSON Input, 3.3 V-Tolerant Active Input for Spread Selection.<br>Internal 100 k $\Omega$ pulldown. Refer to Table 2. |  |

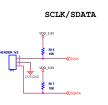

| SDATA        | I/O  | SMBus-Compatible SDATA.                                                                                              |  |

| SCLK         | I    | SMBus-Compatible SCLOCK.                                                                                             |  |

<sup>2</sup> Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com Rev. 0.1 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • December 10, 2021

### Table 2. Spread Selection

| SSON | Frequency<br>(MHz) | Spread<br>(%) | Note                     |

|------|--------------------|---------------|--------------------------|

| 0    | 100.00             | OFF           | Default Value for SSON=0 |

| 1    | 100.00             | -0.5          |                          |

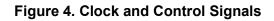

## 1.1. Generating DIFF Outputs from the Si52144

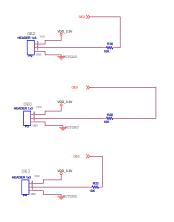

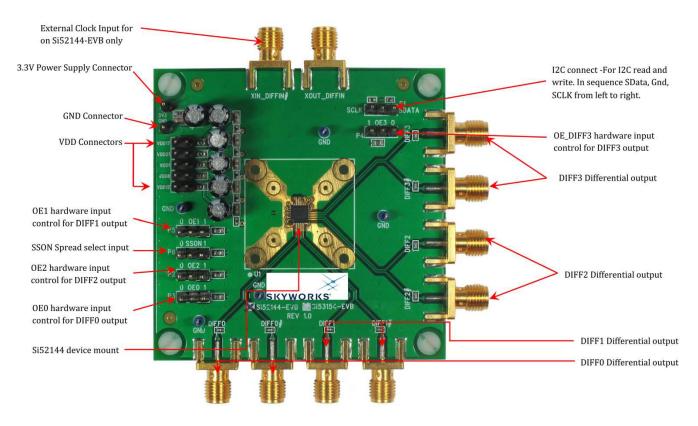

If the input pins are left floating upon power-on of the device, by default all DIFF outputs DIFF[0:3] are ON with 100 MHz and with spread spectrum disabled. The input pin headers have clear indication of jumper settings for setting logic LOW (0) and HIGH (1) as shown below. The jumper placed on the middle and left pin will set input OE0 to LOW; the jumper placed on the middle and right pin will set input OE0 to HIGH.

The output enable pins can be changed on the fly to observe outputs stopped cleanly. To enable the spread spectrum, the SSON input needs to change from a logic level low to high. Input functionality is explained in detail below.

#### 1.1.1. SSON Input

Apply the appropriate logic level to SSON input to achieve clock frequency selection. When the SSON is HIGH, –0.5% down spread is enabled on all differential outputs with a saw-tooth spread profile. When the SSON is LOW, spread profile is disabled.

#### 1.1.2. OE [0:3] Input

The output enable pins can change on the fly when the device is on. Deasserting (valid low) results in corresponding DIFF output to be stopped after their next transition with final state low/low. Asserting (valid high) results in corresponding output that was stopped are to resume normal operation in a glitch-free manner.

Each of the hardware OE [0:3] pins are mapped via  $I^2C$  to control bit in Control register. The hardware pin and the Register Control Bit both need to be high to enable the output. Both of these form an "AND" function to disable or enable the DIFF output. The DIFF outputs and their corresponding  $I^2C$  control bits and hardware pins are listed in Table 3.

| I <sup>2</sup> C Control Bit | Output | Hardware Control Input |

|------------------------------|--------|------------------------|

| Byte1 [bit 2]                | DIFF0  | OE0                    |

| Byte1 [bit 0]                | DIFF1  | OE1                    |

| Byte2 [bit 7]                | DIFF2  | OE2                    |

| Byte2 [bit 6]                | DIFF3  | OE3                    |

#### Table 3. Output Enable Control

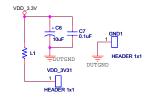

## 2. Schematics

4 Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com Rev. 0.1 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • December 10, 2021